Паралельний аналого-цифровий перетворювач

Номер патенту: 89367

Опубліковано: 25.04.2014

Автори: Васильківський Микола Володимирович, Стальченко Олександр Володимирович, Бортник Геннадій Григорович

Формула / Реферат

Паралельний аналого-цифровий перетворювач, який містить резистивну матрицю, вхід якої під'єднано до шини джерела опорної напруги, 2n-1 компаратори, інвертувальні входи яких під'єднано до відповідних виходів резистивної матриці, а виходи компараторів під'єднано до відповідних входів кодувальної логіки, який відрізняється тим, що введено резистор, один вивід якого під'єднано до неінвертувальних входів 2n-1 компараторів та виходу першого аналогового ключа, а другий вивід резистора під'єднано до виходу другого аналогового ключа та до вхідної шини джерела вхідного сигналу, керувальний вхід першого аналогового ключа під'єднано до шини напруги зміщення, а вхід - до виходу генератора струму та входу другого аналогового ключа, керувальний вхід якого під'єднано до входу синхронізації блока буферної пам'яті та виходу подільника частоти, вхід якого під'єднано до шини джерела синхросигналу та входу синхронізації кодувальної логіки, виходи якої під'єднано до відповідних входів блока буферної пам'яті, а вихід, що відповідає молодшому розряду, з'єднано з першим входом елемента «Виключне АБО», другий вхід якого під'єднано до виходу блока буферної пам'яті, що відповідає молодшому розряду, а всі інші виходи блока буферної пам'яті під'єднано до відповідних розрядів вихідної шини аналого-цифрового перетворювача, причому до молодшого розряду вихідної шини під'єднано вихід елемента «Виключне АБО».

Текст

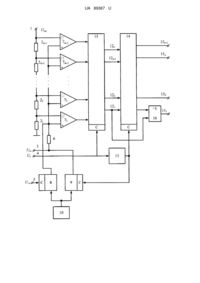

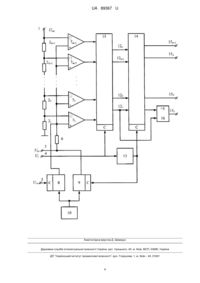

Реферат: Паралельний аналого-цифровий перетворювач містить резистивну матрицю, шини джерела n опорної напруги, 2 -1 компаратори, кодувальну логіку. Додатково введено резистор, n неінвертувальні входи 2 -1 компараторів, перший та другий аналоговий ключ, шини джерела вхідного сигналу, шини напруги зміщення, генератор струму, синхронізацію блока буферної пам'яті, шини джерела синхросигналу та синхронізації кодувальної логіки, блок буферної пам'яті, елемент «Виключне АБО» та шини аналого-цифрового перетворювача. UA 89367 U (54) ПАРАЛЕЛЬНИЙ АНАЛОГО-ЦИФРОВИЙ ПЕРЕТВОРЮВАЧ UA 89367 U UA 89367 U 5 10 15 20 25 30 35 40 45 50 55 Корисна модель належить до імпульсної техніки і призначена для використання в системах обробки швидкоплинної інформації. Відомий паралельний аналого-цифровий перетворювач, який містить у випадку n розрядів m груп компараторів, елементів пам'яті, причому загальне число компараторів в цьому випадку n n складає 2 -1, а елементів пам'яті 2 -1, виходи компараторів підключені до керуючих виходів елементів пам'яті, тактові входи яких підключені до джерела стробуючого сигналу, а виходи під'єднані до розрядних шин (патент США № 3829853, М.КЛ. Η03Μ 1/36). Недоліком цього пристрою є низька роздільна здатність. Відомий аналого-цифровий перетворювач паралельної дії, який містить групу компараторів старших розрядів і групу компараторів молодших розрядів, перші входи яких підключені до джерел опорних напруг, сигнальні входи групи компараторів старших розрядів підключені до джерела сигналу, який перетворюється, а виходи компараторів в кожній групі, крім компараторів старших розрядів, об'єднані попарно і підключені до керуючих входів елементів пам'яті, і резистивні підсилювачі, перші входи яких підключені до джерел струмів зміщення, другі через повторювач та інвертор підключені до джерела сигналу, який перетворюється, а виходи попарно зі зсувом на один підключені до входів елемента, виходи яких через елемент АБО з'єднані з сигнальними входами компараторів молодших розрядів, входи стробування елементів пам'яті підключені до джерела стробуючого сигналу (А.с. СРСР №879771, М.КЛ. Η03К 5/22, бюлетень № 41, 1981р.). Недоліками даного перетворювача є низька роздільна здатність і надійність перетворення. Найбільш близьким є паралельний аналого-цифровий перетворювач, який містить у випадку n розрядів резистивну матрицю, вхід якої під'єднано до шини джерела опорної напруги, 2"-1 компараторів, Інвертувальні входи яких під'єднано до відповідних виходів резистивної матриці, а неінвертувальні входи з'єднано з шиною джерела напруги, яка підлягає перетворенню, виходи компараторів під'єднано до відповідних входів кодувальної логіки, виходи якої є вихідною розрядною шиною аналого-цифрового перетворювача (АЦП). (Гельман Μ.Μ. Системные аналого-цифровые преобразователи и процессоры сигналов.- М.: Мир, 1996. - С. 142, рис. 2.4). Недоліком даного пристрою є низька роздільна здатність, оскільки при підвищенні роздільної здатності, тобто збільшенні числа двійкових розрядів, число компараторів, n резисторів матриці та елементів кодувальної логіки збільшується пропорційно 2 -1, де n - число розрядів АЦП, що різко ускладнює реалізацію такого АЦП, а це обмежує функціональні можливості. В основу корисної моделі поставлена задача створення паралельного аналого-цифрового перетворювача, в якому за рахунок введення нових блоків та зв'язків підвищується роздільна здатність, що призводить до спрощення реалізації пристрою та розширення функціональних можливостей. Поставлена задача вирішується тим, що в паралельний аналого-цифровий перетворювач, який містить у випадку n розрядів резистивну матрицю, вхід якої під'єднано до шини джерела n опорної напруги, 2 -1 компараторів, інвертувальні входи яких під'єднано до відповідних виходів резистивної матриці, а виходи компараторів під'єднано до відповідних входів кодувальної логіки, вихідну розрядну шину введено резистор, перший аналоговий ключ, другий аналоговий ключ, подільник частоти, блок буферної пам'яті, елемент "Виключне АБО", причому один вивід n резистора під'єднано до неінвертувальних входів 2 -1 компараторів та виходу першого аналогового ключа, а другий вивід резистора під'єднано до виходу другого аналогового ключа та до шини джерела напруги, яка підлягає перетворенню, керувальний вхід першого аналогового ключа під'єднано до шини напруги зміщення, а вхід - до виходу генератора струму та входу другого аналогового ключа, керувальний вхід якого під'єднано до входу синхронізації блока буферної пам'яті та виходу подільника частоти, вхід якого під'єднано до шини джерела синхросигналів та входу синхронізації кодувальної логіки, виходи якої під'єднано до відповідних входів блока буферної пам'яті, а вихід, що відповідає молодшому розряду з'єднано з першим входом елемента «Виключне АБО», другий вхід якого під'єднано до виходу блока буферної пам'яті, що відповідає молодшому розряду, а всі інші виходи блока буферної пам'яті під'єднано до відповідних розрядів вихідної шини аналого-цифрового перетворювача, причому до молодшого розряду вихідної розрядної шини під'єднано вихід елемента «Виключне АБО», що дає при однаковій кількості компараторів та елементів кодувальної логіки як і в прототипі, збільшення розрядності паралельного аналого-цифрового перетворювача до значення n+1, а отже і до підвищення його роздільної здатності. На кресленні наведена структурна електрична схема паралельного аналого-цифрового перетворювача. 1 UA 89367 U 5 10 15 20 25 Пристрій містить шину 1 джерела опорної напруги Uon резистивну матрицю 2, що n складається з m-1 послідовно ввімкнених резисторів, де m=2 , шину 3 джерела вхідного сигналу Uвx, що підлягає перетворенню, шину 4 джерела синхросигналу Uc, вхід 5 джерела сигналу зміщення Uзм, вхідний резистор 6, лінійку з m-1 компараторів 7, перший аналоговий ключ 8, другий аналоговий ключ 9, генератор струму 10, кодувальну логіку 11, n-розрядний вхід 12 кодувальної логіки, де 121 - молодший розряд кодувальної логіки, подільник частоти 13, блок буферної пам'яті 14, n+1-розрядну вихідну шину 15 аналого-цифрового перетворювача, елемент "Виключне АБО" 16. Аналого-цифровий перетворювач працює наступним чином. Вхідна напруга, яка перетворюється Uвx через шину 3 джерела вхідного сигналу та резистор 6 надходить на неінвертувальні входи компараторів 7, де відбувається її порівняння з опорними рівнями сформованими з напруги джерела опорної напруги Uon за допомогою резистивної матриці 2. За допомогою кодувальної логіки 11 відбувається перетворення m-1-розрядного унітарного коду з виходів компараторів 7 у n-розрядний позиційний двійковий код з частотою , що дорівнює частоті сигналу синхронізації Uc, який подається з шини джерела синхросигналів 4 на вхід синхронізації кодувальної логіки 11. Двійковий код з виходу 12 кодувальної логіки 11 подається на вхід блока буферної пам'яті 14, де він зберігається протягом періоду синхронізації, який формується за допомогою поділки частоти 13 шляхом подачі синхросигналу з його виходу на синхровхід блока буферної пам'яті 14. Частота синхронізації блока буферної пам'яті 14 у 2 рази менша, ніж частота синхронізації кодувальної логіки 11 за рахунок використання подільника частоти 13. Вхідний сигнал кодувальної логіки 11 зберігається у блоці буферній пам'яті 14 доки не почнеться наступний період синхросигналу. У другій половині цього періоду за допомогою елемента "Виключне АБО" 16 виконується логічна операція порівняння молодшого розряду цього цифрового сигналу з молодшим розрядом нового цифрового сигналу, що з'являється на виходах 12 кодувальної логіки 11. Після цього, протягом другого періоду синхросигналу, напруга на неінвертуючих входах компараторів змінюється на величину U 30 U on 2 n1 Таким чином, в кінці кожного другого періоду синхросигналу відбувається приріст на один розряд вихідного коду аналого-цифрового перетворювача. Значення напруги Uзм від джерела зміщення 5 і резистора 6 задається так, щоб відбувалось почергове перемикання аналогових ключів 8 і 9 під дією сигналу синхронізації з подільника частоти 13. Для цього значення резистора 6, через який протікає струм I від генератора струму 10 через ключ 8 задається відповідно до виразу R 35 40 45 50 . U on 2 n1 . У першу половину циклу перетворення відкрито ключ 9 і струм І від генератора струму протікає безпосередньо до джерела вхідного сигналу 3. А в другу половину циклу перетворення струм I через відкритий ключ 8 протікає до джерела сигналу 3 через резистор 6. Таким чином вхідний сигнал зміщується на значення ±0,5 одиниці молодшого розряду аналого-цифрового перетворювача. Виконання паралельного аналого-цифрового перетворювача згідно зі схемою корисної моделі з використанням двох аналогових ключів, які змінюють послідовне зміщення вхідного сигналу Uвx у межах половини молодшого розряду та елемента "Виключне АБО", що порівнює молодші розряди кодувальної логіки та блока буферної пам'яті, дозволяє підвищити роздільну здатність паралельного аналого-цифрового перетворювача без збільшення числа компараторів. Для реалізації паралельного аналого-цифрового перетворювача, який заявляється, що має роздільну здатність 10-розрядного перетворювача необхідно використати 511 компараторів та елементів кодувальної логіки, а для отримання такої ж роздільної здатності прототипа необхідно 1023 компаратора та елементи кодувальної логіки, що призводить до неможливості практичного виконання прототипу. Таким чином збільшення роздільної здатності прототипу обмежене 68 розрядами, тоді як паралельний аналого-цифровий перетворювач, який заявляється, дозволяє підвищити роздільну здатність, що еквівалентна 910-розрядному перетворенню. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 55 Паралельний аналого-цифровий перетворювач, який містить резистивну матрицю, вхід якої n під'єднано до шини джерела опорної напруги, 2 -1 компаратори, інвертувальні входи яких під'єднано до відповідних виходів резистивної матриці, а виходи компараторів під'єднано до відповідних входів кодувальної логіки, який відрізняється тим, що введено резистор, один 2 UA 89367 U n 5 10 вивід якого під'єднано до неінвертувальних входів 2 -1 компараторів та виходу першого аналогового ключа, а другий вивід резистора під'єднано до виходу другого аналогового ключа та до вхідної шини джерела вхідного сигналу, керувальний вхід першого аналогового ключа під'єднано до шини напруги зміщення, а вхід - до виходу генератора струму та входу другого аналогового ключа, керувальний вхід якого під'єднано до входу синхронізації блока буферної пам'яті та виходу подільника частоти, вхід якого під'єднано до шини джерела синхросигналу та входу синхронізації кодувальної логіки, виходи якої під'єднано до відповідних входів блока буферної пам'яті, а вихід, що відповідає молодшому розряду, з'єднано з першим входом елемента «Виключне АБО», другий вхід якого під'єднано до виходу блока буферної пам'яті, що відповідає молодшому розряду, а всі інші виходи блока буферної пам'яті під'єднано до відповідних розрядів вихідної шини аналого-цифрового перетворювача, причому до молодшого розряду вихідної шини під'єднано вихід елемента «Виключне АБО». 3 UA 89367 U Комп’ютерна верстка Д. Шеверун Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 4

ДивитисяДодаткова інформація

Автори англійськоюBortnyk Hennadii Hryhorovych, Stalchenko Oleksandr Volodymyrovych

Автори російськоюБортник Геннадий Григорьевич, Стальченко Александр Владимирович

МПК / Мітки

МПК: H03K 5/00

Мітки: паралельний, перетворювач, аналого-цифровий

Код посилання

<a href="https://ua.patents.su/6-89367-paralelnijj-analogo-cifrovijj-peretvoryuvach.html" target="_blank" rel="follow" title="База патентів України">Паралельний аналого-цифровий перетворювач</a>

Попередній патент: Паралельно-послідовний аналого-цифровий перетворювач

Наступний патент: Логічний елемент і-ні

Випадковий патент: Спосіб виготовлення і складання планетарного редуктора