Пристрій для регулювання потужності

Номер патенту: 12918

Опубліковано: 28.02.1997

Автори: Сіренко Сергій Миколайович, Суботін Володимир Анатолійович

Формула / Реферат

(57) Устройство для регулирования мощности, содержащее тиристорный коммутирующий блок, включенный между выводами, предназначенными для последовательного подключения сети переменного тока и нагрузки, формирователь тактовых импульсов, входы которого подключены к той же сети переменного тока, что и нагрузка, блок задания мощности, N выходов которого подключены к N установочным входам велителя частоты с переменным коэффициентом деления, отличающееся тем, что в него введены элемет И-НЕ, инвертор, первуй элемент ИЛИ, делитель частоты на два, сдвоенный селоктор-мультиплексор, второй элемент ИЛИ, 1-я и 2-я связи, соединяющие соответственно N+1 и N+2 выходы блока задания мощности с адресными входами сдвоенного селектора-мультиплексора, в котором первый вход первого канала соединен с выходом первого элемента ИЛИ, второй вход первого канала соединен с первым, третьим, четвертым входами второго канала мультиплексора, первым входом первого элемента ИЛИ, входом делителя частоты на два, вторым входом элемента И-НЕ, входом инвертора и выходом формирователя тактовых импульсов, третий вход первого канала мультиплексора соединен с выходом элемента И-НЕ и со вторым входом первого элемента ИЛИ, четвертый вход первого канала мультиплексора соединен с общей шиной, второй вход второго канала мультиплексора соединен с выходом инвертора, выход первого канала мультиплексора соединен с разрешающим входом второго канала мультиплексора и первым входом второго элемента ИЛИ, разрешающий вход первого канала мультиплексора соединен с общей шиной, выход второго канала мультиплексора соединен с счетным входом делителя частоты с переменным коэффициентом деления, выход которого соединен с вторым входом второго элемента ИЛИ. а выход второго элемента ИЛИ соединен с входом тиристорного коммутирующего блока, выход делителя частоты на два соединен с первым входом элемента И-НЕ.

Текст

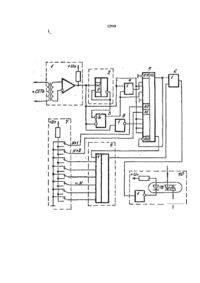

УстроГїСтво д ля регу лирования мощно сти, содержащ ее тирис торний комму тирую щий блок, включенный межд у вывод ами, пред назначенными д ля послед овательного подключения с е™ переменного тока и на грузки, формирователь тактовых импульсов, вход ы которого подключены к той же с ети переменного тока, что и нагру зка, блок за дания мощнос ти, Ы вых од ов которого под ключены к N установочным входам делителя час тоты с переменным коэ ффициентом д е ления, о т л и ч а ю щ е е с я тем, что в него введены элемеуп И-НЕ , инвертор, первый э лемент ИЛ И, д елитель час тоты на д ва, сдвоенный селоктор-мультиплексор, второй элемент ИЛ И, 1-я и 2-я связи, соед иняющие соответс твенно N+1 и N+ 2 вых од ы блока Изобретение относится к облас ти автоматики. Наиболее близким по технической сущ нос ти к заявляемому ус тройс тву являетс я ус тройс тво д ля регу лирования мощнос ти, зад ания мощнос ти с ад рес ными вх одами сдвоенного с електора-му льтиплекс ора, в котором первый вход первого канала с оединен с выходом первого элемента ИЛ И, второ й вх од п е рвог о ка на л а с о ед и не н с первым, третьим, четвертым входами второго канала мультиплексора, первым вх одом первого элемента ИЛИ, входом д елителя частоты на два, вторым вх одом э лемента ИНЕ , вх од ом и н ве р то р з и в ых од о м формирователя тактовых импу льсов, третий вход первого канала мультиплексора соединен с выход ом элемента И-НЕ и со вторым вход ом первого э лемента ИЛ И, четвертый вход первого канала мультиплексора соединен с общей ш иной, второй вход второго канала мультиплексора соед инен с выходом инвертора, выход первого канала му льтиплексора соединен с разреш ающим входом второго канала му льтиплекс ора и первым вход ом второго э лемента ИЛ И, разреш ающий оход первого канала му льтиплексора соед инен с общей шиной, вых од второго канала му льтиплексора соединен с счетным входом делителя час тоты с переменным коэ ффициентом деления, выход которого соединен с вторым вх одом второго э лемента ИЛИ. а вых од второго э лемента ИЛИ соединен с вход ом тирис торного комму тирующего блока, выход делителя час тоты на два соединен с первым входом элемента И-НЕ. содержащее формирователь тактовых импульсоо, входы которого подсоединены к сети, а выход соединен с вход ом делителя час тоты с переменным коэ ффициентом деления. Установочные N входов делителя ча ю 00 О 12918 стоты подключены к N пыход ам блока зад ания мощнос ти, а вых од э того ж е делителя час тоты соед инен с вход ом тирис торного комму тирующего блока [ 3]. Недос татком известного устройс тва для регулирования мощнос ти является следующее: дискретное значение регулиру емой величины мощнос ти в нагрузке зависит только от максимального значения коэ ффициента деления примененного д елителя час тоты и в процессе регу лирования изменяться не может, что о свою очередь не позволяе т повыс ить точнос ть регу лирования. Зад ача повыш ения точнос ти регу лирования решается тем, что разбивают диапазон регу л иров ани я на че тыре поддиапазона, чт о д ает возможность, не меняя максимального значения коэ ффициента деления примененного делителя час тоты, уменьшить д искретное значение регу лируемой пег. ичины мощ нос ти в наїру зке. Для выполнения пос тавленной задачи в устройс тво д ля регу лирования мощнос ти, содерж ащ ее тирис торпый комму тиру ющий Ьлок, включенный между выводами, предназначенными д ля пос лед овательного подк л юч е н ия с е ти п е ре м е нн ог о то к а и нагрузки, формирователь тактовых импу льсов, вход ы которого под ключены к той же сеги переменного тока что и нагрузка, блок задания мощнос ти, N выход ов которого подключены к N установочным входам делителя час тоты с переменным коэ ффициентом деления, с огласно изобретению, введен э лемент И -НЕ , инвертор, первый э лемен т ИЛ И, делитель час тоты на два, сдвоенный селектор-му льтиплексор, второй э лемент ИЛИ, 1-Й и 2-я связи, соединяющие соответственно N+1 и N+2 вых од ы блока зад ания мощности с адресными входами сдвоэнного селектора-му льтиплексора, в котором первый вх од первого канала соед инен с вых одом первого э лемента ИЛ И, второй вход первого канала соед инен с первым, третьим, четвертым вх од ами второго канала му льтиплекс ора, первым вх од ом первого элемента ПЛИ, оходом делителя частоты на два, вторым входом элемента И-НЕ, входом инвертора и выходом формирователя тактовых пмпульсоо, третий вход первого канала мультиплекс ора соед инен С выход ом э лемента И-НЕ и со аторым входом первого элемента ИЛ И, четвертый вход первого канала му льтиплексора соединен с общей шино й, в то р о й вх од в то р ог о к з на л а мультиплексора соед инен с выходом инвертора, сыхед первого капала му льтиплексора соединен с разреш ающим вх од ом второго канала му льтиплекс ора и первым вх од ом второго э лемента ИЛ И, разреш ающий вход первого канала му льтиплекс ора с оед инен с общей ш иной, выход второго канала мультиплекс ора с оед инен с счетным ох о5 дом д елителя час тоты с переменным к оэ ффи ц и ен том д е ле ния, в ых од ко тор ого соединен с вторым вх одом второго э лемента ИЛ И, а выход второго э лемента ИЛ И соед инен с вх од ом тирис тор ног о 10 комму тирующего блока, выход делителя частоты на два с оед инен с первым вх од ом элемента И-НЕ. Устройс тво д ля регу лирования мощности (фиг.1) содержит формирователь такто15 аых импу льсов 1, делитель час тоты на два 2, елемент И-НЕ 3, первый Элемент ИЛИ 4, сдвоенный селектор-му льтиплекс ор 5, второй э лемент ИЛ И 6, блок мощнос ти 7, делитель частоты с переменным коэ ффициентом 20 деления 8, инвертор 9, тирис торний коммутирующий блок 10. Входы формирователя 1 тактовых импульс ов подсоед инены к с ети переменного тока, а выход соединен с входом делителя 2 25 час тоты на два, выход которого соед инен с первым входом э лемента 3 И-НЕ, Вход формирователя 1 тактовых импульс ов также соединен с о вторым вх одом элемента 3 И-НЕ, первым входом э лемента 30 4 ИЛ И, вторым вход ом первого канала и первым, третьим, четвертым входами второго канала сд военного селгктора-му льтиплексора 5, вх од ом инвертора 9. Вых од элемента 3 И-НЕ соединен со вторым входом 35 э лемента 4 ИЛ И и третьим вх одом первого канала сдвоенного селектора-мультиплексора 5. Выход первого элемента 4 ИЛИ соединен с первым вх од ом первого кана ла сдвоенного селектора-мультиплексора 5. Вы40 ход инвертора 9 соединен с вторым входом второго канала сдвоенного селектора-му льтиплексора 5. N вых одов блока 7 задания мощнос ти соединены с N ус тановочными входами д елителя 8 час тоты с переменным 45 коэ ффициентом деления. N-И выход блока 7 зад ания мощнос ти соед инен с первым адресным входом сдвоенного селектора-му льтиплекс ора 5, N+2 вых од блока 7 зад ания мощнос ти с оед инен с о вторым ад рес ным 50 вход ом сдвоенного селектора-му льтиплек сора 5. Р азреш ающ ий вход и четвертый сход первого канала селектора-му льтиплексора 5 соед инены с общей ш иной, В ых од первого канала сдвоенного селектора-му ль55 типлексора 5 соед инен с разреш ающим входом второго канала э того же мультиплексора и с первым входом второго элемента 6 ИЛ И. Выход второго канала сдвоенного селектора-му льтиплекс ора 5 с оед инен с четным входом делителя 8 час тоты с переменным і 12918 коэ ффициентом д еления. Выход д елителя 8 час тоты с переменным коэ ффициентом д еления. Выход делителя 8 час тоты с переменным коэ ффициентом д еления с оединен с вторым вход ом второго э лемента б ИЛ И, Выход второго э лемента 6 ИЛИ соединен с входом тирис торного комму тирующего блока 10. Ус тройс тво д ля регу лирования мощности работает с леду ющим образом. При подаче с инус оидального напряжения с ети на вход ы формирователя 1 тактовых импу ль соо, на выходе э того формирователя появятс я прямоу голь ны е импу льс ы с той ж е час тотой с ледования, что и вх одное напряжение, причем, фронт и спад вых одных импульсов совпадают по времени с переходом вход ного напряжения через ну левое значение. С выхода формирователя 1 тактовых импу льсов прямоугольные импу льс ы, проходя через делитель 2 час тоты на два, увеличивают с вою д лительнос ть в д ва раза, которая буд ет с ортветс твовать од ному периоду с инус оид ального напряжения с ети. Элемент З И-НЕ на своем вых оде формиру ет послед овательнос ть положительных импу льс ов, с ов п ад ающ их то л ьк о с отрицательной полу волной и пауз между импу льс ами, с овпад ающ их по д лительности с дву мя положительными полуволнами и од ной отрицательной полуволной, Первый элемент 4 ИЛИ на своем выходе формиру ет пос лед овательнос ть положительных импульсов, совпадающих по д лительности с д ву мя полож ительными и од ной отрицательной полуволной и пауз между импульсами, совпад ающих только с отрицательной полу волной. Взаимное временное соотношение между импульс ами с выхода элемента 3 И-НЕ и с выход а первого э лемента 4 ИЛ И таково, что положительный импу льс с выхода э лемента 3 И-НЕ расположен по серед ине положительного импу льса с выхода первого э лемента 4 ИЛИ. Взаимное рас положение между с обой у казанных выш е импу льсов показано на фиг.З. При под аче с вых ода N+1 и N+2 блока 7 зад ания мощности на адресные вход ы АО, А1 сдвоенного селектора-му льтиплексора 5 у ровней логической единицы, с четвертого входа первого канала сдвоенного с електора-му льтиплек сора 5 уровень логического нуля пос тупит на выход первого канала, далее на первый вход второго элемента 6 ИЛ И и на разрешающий вход второго канала э того же мультиплексора, ч то позволит пропускать импульс ы с выхода формирователя 1 тактовых импу льсов через четвертый вход на выход второго канала сдвоенного селектора-мультиплекс ора 5 к с четному вх од у д елителя час тоты 8 с переменным коэ ффициентом д еления. С выхода делителя час тоты 8 импу льсы пос тупаю т через второй вх од второго э лемента 6 ИЛ И на вых од э того э лемента и далее на 5 вх од тирис торного комму тирующего блока 10. В завис имос ти от логического с ос тояния вых од ов блока 7 задания мощнос ти, в нагрузку будет пропускатьс я мощнос ть от ну ля до пятид ес яти процентов от 10 максимальной величины (эпю ра V фиг.2). При под аче с вых од а N+ 1 у ровня логического нуля и с выхода ІМ+2 уровня логичес кой ед иницы блока 7 зад ания мощнос ти на адресные входы АО, А1 сдвоенного селек15 тора-му льтиплексора 5, с третьего вх ода первого канала сдвоенного селектора-муль типлексора 5 импульс ы, с формированные с выход а э лемента 3 в с оответс твии с д иаграммой фиг. З, пос ту пят на вых од первого 20 канала, далее - на первый сход второго э лемента 6 ИЛ И и па разруш ающий вход второго канала э того же мультиплексора. При пос туплении с выхода первого канала сдвоенного селектора-мультиплексора 5 логиче25 с кой ед и ни цы в торо й кана л э тог о же селектора блокируется, а на выходе второго элемента ИЛ И 6 потаитс я логическая ед иница, что при пос туплении ее на вх од тирис торн ого комму тиру ющ его блока 10 30 вызовет его открывание и формирование тока в нагрузке в с оответс твии с эпюрой 11 фиг. 2. При пос туплении с вых ода первою канала сдвоенного с електора-мудьтиплексора 5 логического нуля второй канал э того 35 же с електора включается, и в завис имос ти от коэ ффициента деления делителя частоты 8. импульс ы пос тупившие с выхода формирователя 1 тактооых импу льсов и прошед ш ие через второй канал с д военног о 40 селектора-му льтиплекс ора, делитель час тоты 8 и второй э лемент ИЛ И 6, импу льс ы уровня логической единицы вызову т открывание тирис торного комму тирующего блока 10 и д обавят п нагрузку д ополнительные 45 полуволны тока (эпю ра V I фиг.2). При подаче с пых ода N+1 уровня логической ед иницы и с вых од а N+ 2 уровня логического ну ля блока 7 зад ания мощнос ти на адресные входы АО, /И сдвоенного селек50 тора-му льтиплекс ора 5, импу льс ы пос ту пают с вых ода формирователя 1 тактовых импу льсов через второй сход первого канала сдвоенного с електора-му льтиплекс ора 5 на его выход и далее через второй элемент 55 ИЛ И 6 на вх од тирис торного комму тирую щего блока 10. В случае, когд а делитель 8 час тоты не пропускает через себя импульсы, ток о нагрузке будет формироваться соглас но эпюре Ш фиг. 2, а в с лучае, когда делитель 8 час тоты производит деление чэ 12918 сюты пос тупающих импу льсов, то произойдет добавление в нагрузку тока на количес тво импульсов, полученных поело деления делителем 8 частоты (эпюра V I! фиг. 2). При подаче с выходов N+1, N+2 уровней логического нуля блока 7 задания мощности на адресные входы ЛО, А1 сдвоенного селектора-му льтиплекс ора 5, импу льсы пос ту пают с выход а первого элемента ИЛ И А через первый вход первого канала сдвоенного селектора-мультиплексора на его оыход и далее через второй э лемент ИЛИ 6 на вход тирис торного комму тирующего блока 10. В случае, когд а делитель 8 час тоты не пропускает через с ебя импу льс ы, ток в нагрузке буд ет формироваться с оглас но э пюре IV фиг.2, а в случае, когда делитель 8 частоты производит деление час тоты пос тупающих импульсов, то произойдет добавление в нагрузку тока на количес тво импу льс ов, полученных после деления делителем 8 частоты (эпюра VIII фиг.2). В соответс твии с вышеизложенным следует, что если на выходах N+1, N+2 блока 7 задания мощнос ти прису тс тпуютуровни логической единицы, то будет обеспеч иваться регу лировка а диапазоне от нуля д о 50% номинальной мощ нос ти нагрузки с дискретнос тью, которая определяется в соответс твии с мак с им а льн ым к оэ ффи ци ен том деления делителя 8 частоты. Когда но оыходе N+1 уровень логического пу ля и на выходе N+2 уровень логической единицы, то будет обеспечиваться регулировка о диапазоне от 25% до 75% номинальной мощности нагрузки. Если на оыходо N+1 уровень логическ ой ед иницы и па вых од е N+2 у ровень 8 логического ну ля, то буд ет обеспечиватьс я регу лировка а д иапазоне от 50 д о 100% * номинальной мощнос ти нагрузки. Ес ли на выход ах N+ 1, N+2 уровни логического ну ля, 5 то буд ет обес печиваться регу лировка в д иапазоне от 75 до 100% номинальной мощ нос ти нагру зки. Формирователь 1 тактовых импу льс ов пред с тавляет собой, например, понижаю10 щ ий транс форматор и компаратор К 554 САЗ в ш татном вк лючении. Делитель 2 частоты на два может быть предс тавлен, наприме р-, 1 / 2 микрос х ем ы К 155 ТМ 2, инверс ный вых од которой с оед инен с вх о15 дом данных. Делитель 8 час тоты с переменным коэ ффициентом деления предс тавлен микросх емой К155 ИЕ8 в ш татном включении. Б лок 10 зад ания мощнос ти предс тавлен п вид е наборного поля из ту мблеров и 20 д пух шин с уровнями напряжения логического ну ля и логической ед иницы. Тирис торный комму тирующий блок 10 предс тавлен в оиде микросхемы К155 ЛА18 подпоенного о птотирис торного блока МТО25 ТО 80. Элемент ЗИ-НЕ предс тавлен микросхемой К 155 ЛЕ 1. Элементы А, 6 ИЛ И предс тавлены микросх емой К 155 ЛЛ 1. Инвертор 9 предс тавлен микросх емой К155 ЛН1. Сдвоенный селектор-му льтиплексор 5 30 предс тавлен микросхемой К 155 К П2. При э том возм ожно р егу лиров ани е мощнос ти в д иапазонах 0-50%, 25-75%, 50-100% с д искретным значением регу лиру емой величины равным 1/ 128 от номи35 пальмой мощнос ти, а в д иапазоне 75-100% дискретное значение измеряемой величины равно 1/ 256 от номинальной мощнос ти. i_ 12918 __________ I 12918 /Л Г\ /Л /Л ґ\ /Л V V V V V 257* V/ V/ ЛУ \У 50% Г \ ґ \ ґ \ ґ \ Г \ ґ \У 47 ХУ \ Г \ / \ & \/ \7 o-mj. Х7 СХ Ї5-Ш \7 Г\ ґ\ Г\ Г\ Щ ^7" Г\ Г\ Г\ Пі Г\ v/ \J Г\ ґ\ \У ґ\ V/ Се ть Вых. бателя 8ш ел ЛЯ £ дых. те 3 Вых Фиг 3 Упорядник Замовлення 4089 Техред М.Моргентал_ Коректор М.Куль Тираж Підписне Державне патентне відомство УкраТни, 254G55, ГСП, Київ-53, Львівська пл., 8 Відкрите акціонерне товариство "Патент", м. Ужгород. вул.ГагарІна, 101

ДивитисяДодаткова інформація

Назва патенту англійськоюPower control device

Автори англійськоюSubotin Volodymyr Anatoliiovych, Sirenko Serhii Mykolaiovych

Назва патенту російськоюУстройство для регулирования мощности

Автори російськоюСуботин Владимир Анатольевич, Сиренко Сергей Николаевич

МПК / Мітки

Мітки: потужності, пристрій, регулювання

Код посилання

<a href="https://ua.patents.su/7-12918-pristrijj-dlya-regulyuvannya-potuzhnosti.html" target="_blank" rel="follow" title="База патентів України">Пристрій для регулювання потужності</a>

Попередній патент: Спосіб визначення похибки термоелектричних термометрів

Наступний патент: Фільтр

Випадковий патент: Спосіб отримання твердих розчинів pbte-csi