Арифметичний пристрій

Номер патенту: 38903

Опубліковано: 26.01.2009

Автори: Бойко Оксана Аркадіївна, Мартинюк Тетяна Борисівна, Кожем'яко Володимир Прокопович

Формула / Реферат

Арифметичний пристрій, який містить регістр, суматор, генератор кратних множеного, вузол формування знака, лічильник, програмний блок керування, суматор аналізу положення коми, вузол аналізу цифр множника, причому вхід другого операнда пристрою з'єднаний з інформаційним входом регістра, вихід знакового розряду регістра підключений до першого входу вузла формування знака, виходи програмного блока керування з першого по третій підключені відповідно до входів обнулення регістра, суматора і лічильника, четвертий і п'ятий виходи програмного блока керування підключені до входів керування записом регістра і суматора, вихід старшого інформаційного розряду суматора підключений до інформаційного входу молодшого інформаційного розряду регістра, шостий вихід програмного блока керування підключений до входу керування записом лічильника, вихід ознаки рівності нулю якого підключений до входу ознаки закінчення лічби програмного блока керування, сьомий, восьмий і дев'ятий виходи якого підключені відповідно до входу керування зсувом регістра, входу лічби лічильника, входу керування зсувом суматора, вхід запуску програмного блока керування з'єднаний з входом запуску пристрою, інформаційний вхід лічильника є входом розрядності другого операнда пристрою, десятий і одинадцятий виходи програмного блока керування з'єднані з входами керування записом знака і обнулення старшого k-го розряду регістра, вихід ознаки нуля старшого k-го розряду регістра підключений до входу ознаки виконання додавання в даному такті програмного блока керування, виходи розрядів суматора з'єднані з виходами молодших розрядів добутку пристрою, виходи розрядів регістра з'єднані з виходами старших розрядів добутку пристрою, дванадцятий, тринадцятий, чотирнадцятий і п'ятнадцятий виходи програмного блока керування з'єднані з входом встановлення у початковий стан, входом керування записом, входом керування зчитуванням і входом керування формуванням кратних генератора кратних множеного відповідно, два інформаційних входи суматора аналізу положення коми з'єднані з входами розрядності дробових частин першого і другого операндів пристрою відповідно, виходи суматора аналізу положення коми підключені до виходів індикації положення коми пристрою, шістнадцятий і сімнадцятий виходи програмного блока керування з'єднані з входом встановлення у початковий стан і входом керування записом суматора аналізу положення коми, вхід вузла аналізу цифр множника з'єднаний з виходом старшого k-го розряду регістра, вхід керування значенням кратності генератора кратних множеного з'єднаний з виходом вузла аналізу цифр множника, причому двадцять перший і двадцять другий виходи програмного блока керування з'єднані з входами керування зчитуванням регістра і суматора відповідно, вихід вузла формування знака з'єднано зі знаковим розрядом регістра, який відрізняється тим, що в нього введено суматор-віднімач, причому вхід першого операнда з'єднаний з інформаційним входом суматора, вихід якого з'єднаний з входом генератора кратних множеного, вісімнадцятий, дев'ятнадцятий і двадцятий виходи програмного блока керування підключені відповідно до входу обнулення, входу керування записом і входу керування зчитуванням суматора-віднімача, вихід регістра з'єднаний з інформаційним входом суматора-віднімача, який також з'єднаний з виходом суматора, вихід суматора-віднімача з'єднаний з інформаційним входом суматора, виходи розрядів суматора-віднімача з'єднані з виходами розрядів результату операції додавання або віднімання, інформаційний вихід генератора кратних множеного з'єднаний з входом суматора-віднімача, вихід знакового розряду суматора з'єднаний з другим входом вузла формування знака, вихід якого з'єднаний зі знаковим розрядом суматора-віднімача і регістра, входи кодів операцій додавання, віднімання і множення з'єднані з відповідними входами програмного блока керування.

Текст

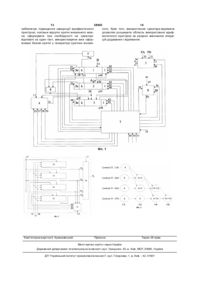

Арифметичний пристрій, який містить регістр, суматор, генератор кратних множеного, вузол формування знака, лічильник, програмний блок керування, суматор аналізу положення коми, вузол аналізу цифр множника, причому вхід др угого операнда пристрою з'єднаний з інформаційним входом регістра, вихід знакового розряду регістра підключений до першого входу вузла формування знака, виходи програмного блока керування з першого по третій підключені відповідно до входів обнулення регістра, суматора і лічильника, четвертий і п'ятий виходи програмного блока керування підключені до входів керування записом регістра і суматора, вихід старшого інформаційного розряду суматора підключений до інформаційного входу молодшого інформаційного розряду регістра, шостий вихід програмного блока керування підключений до входу керування записом лічильника, вихід ознаки рівності нулю якого підключений до входу ознаки закінчення лічби програмного блока керування, сьомий, восьмий і дев'ятий виходи якого підключені відповідно до входу керування зсувом регістра, входу лічби лічильника, входу керування зсувом суматора, вхід запуску програмного блока керування з'єднаний з входом запуску пристрою, інформаційний вхід лічильника є входом розрядності другого операнда пристрою, десятий і одинадцятий виходи програмного блока керування з'єднані з входами керування записом знака і обнулення старшого k-го розряду регістра, вихід ознаки нуля старшого k-го розряду регістра підключений до входу ознаки виконання додавання в даному такті програмного блока керування, виходи розрядів суматора з'єднані з виходами молодших розрядів добутку пристрою, виходи розрядів регістра з'єднані з виходами старших розрядів добутку пристрою, дванадцятий, тринадцятий, чотирнад 2 (19) 1 3 38903 Корисна модель відноситься до обчислювальної техніки і може бути використана в оптоелектронних обчислювальних пристроях, що виконують операції над десятковими числами з природним положенням коми. Відомий пристрій для множення [А. с. СРСР №1136151, кл. G06 F7/49, Бюл. № 3, 1985 p.], який містить регістр множника, накопичувальний суматор, вузол формування знака, генератор кратних множеного, вузол підрахунку кількості значущих розрядів у кодовому слові множника, лічильник, регістр розрядності множника, програмний блок керування, дешифратор і комутатор, причому інформаційний вхід комутатора підключений до виходу генератора кратних множеного, а вихід з'єднаний з інформаційним входом накопичувального суматора, вихід старшого інформаційного розряду регістра множника з'єднаний з входом дешифратора, нульовий вихід якого підключений до третього входу програмного блока керування, а решта виходів - до керуючих входів комутатора, ви хід регістра розрядності множника з'єднаний з четвертим входом програмного блока керування, вхід множника пристрою з'єднаний з інформаційним входом регістра множника, вхід множеного пристрою підключений до інформаційного входу генератора кратних множеного, виходи знакових розрядів регістра множника і накопичувального суматора підключені відповідно до входів вузла формування знака, вихід якого з'єднаний з входом знакового розряду накопичувального суматора, вихід інформаційних розрядів регістра множника з'єднаний з входом вузла підрахунку кількості значущи х розрядів в кодовому слові множника, вихід якого з'єднаний з інформаційними входами регістра розрядності множника і лічильника, виходи програмного блока керування з першого по третій підключені відповідно до входів обнулення регістра множника, накопичувального суматора, лічильника, четвертий і п'ятий виходи програмного блока керування підключені до входів керування записом регістра множника і накопичувального суматора, вихід старшого інформаційного розряду накопичувального суматора підключений до інформаційного входу молодшого інформаційного розряду регістра множника, шостий і сьомий виходи програмного блока керування підключені відповідно до входів керування записом лічильника і регістра розрядності множника, вихід ознаки рівності нулю лічильника підключений до першого входу програмного блока керування, восьмий вихід якого підключений до входу керування записом у знаковий розряд накопичувального суматора, дев'ятий і десятий виходи програмного блока керування підключені відповідно до входу керування зсувом регістра множника і входу лічби лічильника, одинадцятий вихід програмного блока керування підключений до входу керування зсувом накопичувального суматора, дванадцятий вихід програмного блока керування підключений до керуючого входу генератора кратних множеного, другий вхід програмного блока керування з'єднаний з входом запуску пристрою. 4 Недоліком даного пристрою є вузька область застосування і недостатня швидкодія, що пов'язано з процесом послідовного формування кратних множеного за вісім тактів. Відомий пристрій для множення двійководесяткових чисел [А. с. СРСР № 510714 кл. G06 F7/52, Бюл. № 14, 1976 p.], який містить регістр множника, регістр множеного, блок зсуву, ви хід якого з'єднано з входом блока додавання часткових добутків, блок послідовного накопичення чисел, кратних множеному, блок визначення послідовності цифр, причому вихід регістра множеному з'єднано з входом блока послідовного накопичення чисел, кратних множеному, інформаційний вихід якого з'єднано з входом блока зсуву, керуючі входи блока зсуву і блока послідовного накопичення чисел, кратних множеному, з'єднано з відповідними виходами блока визначення послідовності цифр, інформаційний вхід якого з'єднано з виходом регістра множника, а керуючий - з керуючим виходом блока послідовного накопичення чисел, кратних множеному. Недоліком даного пристрою є вузька область застосування і незначна швидкодія пристрою в зв'язку з необхідністю виконання операції послідовного накопичення чисел. Найбільш близьким за технічною суттю є пристрій для множення [Патент України №17282, кл. G06 F7/00, Бюл. №9, 2006 p.], який містить регістр множника, в подальшому регістр, накопичувальний суматор, в подальшому суматор, другий накопичувальний суматор, генератор кратних множеного, вузол формування знака, лічильник, програмний блок керування, суматор аналізу положення коми, вузол аналізу цифр множника, причому вхід множника, в подальшому другого операнда, пристрою з'єднаний з інформаційним входом регістра, вхід множеного, в подальшому першого операнда, пристрою підключений до інформаційного входу генератора кратних множеного, вихід знакового розряду регістра підключений до першого входу вузла формування знака, виходи програмного блока керування з першого по третій підключені відповідно до входів обнулення регістра, суматора і лічильника, четвертий і п'ятий виходи програмного блока керування підключені до входів керування записом регістра і суматора, вихід старшого інформаційного розряду суматора підключений до інформаційного входу молодшого інформаційного розряду регістра, шостий вихід програмного блока керування підключений до входу керування записом лічильника, вихід ознаки рівності нулю якого підключений до входу ознаки закінчення лічби програмного блока керування, сьомий, восьмий і дев'ятий виходи якого підключені відповідно до входу керування зсувом регістра, входу лічби лічильника, входу керування зсувом суматора, вхід запуску програмного блока керування з'єднаний з входом запуску пристрою, інформаційний вхід лічильника є входом розрядності другого операнда пристрою, десятий і одинадцятий виходи програмного блока керування з'єднані з входами керування записом знака і обнулення старшого k-гo розряду регістра відповідно, вихід 5 38903 6 ознаки нуля старшого k-го розряду регістра підний до входу керування записом лічильника, вихід ключений до входу ознаки виконання додавання в ознаки рівності нулю якого підключений до входу даному такті програмного блока керування, другий ознаки закінчення лічби програмного блока керувхід вузла формування знака з'єднаний з входом вання, сьомий, восьмий і дев'ятий виходи якого знака першого операнда пристрою, виходи розряпідключені відповідно до входу керування зсувом дів суматора з'єднані з виходами молодших розрегістра, входу лічби лічильника, входу керування рядів добутку пристрою, виходи розрядів регістра зсувом суматора, вхід запуску програмного блока з'єднані з виходами старших розрядів добутку керування з'єднаний з входом запуску пристрою, пристрою, дванадцятий, тринадцятий, чотирнадінформаційний вхід лічильника є входом розрядцятий і п'ятнадцятий виходи програмного блока ності другого операнда пристрою, десятий і одикерування з'єднані з входом встановлення у почанадцятий виходи програмного блока керування тковий стан, входом керування записом, входом з'єднані з входами керування записом знака і обкерування зчитуванням і входом керування форнулення старшого k-го розряду регістра, вихід муванням кратних генератора кратних множеного ознаки нуля старшого k-го розряду регістра підвідповідно, два інформаційних входи суматора ключений до входу ознаки виконання додавання в аналізу положення коми з'єднані з входами розряданому такті програмного блока керування, виходи дності дробових частин першого і другого операнрозрядів суматора з'єднані з виходами молодших дів пристрою відповідно, виходи суматора аналізу розрядів добутку пристрою, виходи розрядів регісположення коми підключені до виходів індикації тра з'єднані з виходами старших розрядів добутку положення коми пристрою, шістнадцятий і сімнадпристрою, дванадцятий, тринадцятий, чотирнадцятий виходи програмного блока керування з'єдцятий і п'ятнадцятий виходи програмного блока нані з входом встановлення в початковий стан і керування з'єднані з входом встановлення у почавходом керування записом суматора аналізу потковий стан, входом керування записом, входом ложення коми, входи обнулення, керування запикерування зчитуванням і входом керування форсом і керування зчитуванням другого накопичувамуванням кратних генератора кратних множеного льного суматора з'єднані відповідно з відповідно, два інформаційних входи суматора вісімнадцятим, дев'ятнадцятим і двадцятим вихоаналізу положення коми з'єднані з входами розрядами програмного блока керування, вхід вузла дності дробових частин першого і другого оперананалізу цифр множника з'єднаний з виходом дів пристрою відповідно, виходи суматора аналізу старшого k-го розряду регістра, вхід керування положення коми підключені до виходів індикації значенням кратності генератора кратних множеноположення коми пристрою, шістнадцятий і сімнадго з'єднаний з виходом вузла аналізу цифр множцятий виходи програмного блока керування з'єдника, а інформаційний вихід генератора кратних нані з входом встановлення у початковий стан і множеного з'єднаний з входом другого накопичувходом керування записом суматора аналізу повального суматора, вихід якого з'єднаний з інфорложення коми, вхід вузла аналізу цифр множника маційним входом суматора, причому двадцять з'єднаний з виходом старшого k-го розряду регістперший і двадцять другий виходи програмного ра, вхід керування значенням кратності генератоблока керування з'єднані з входами керування ра кратних множеного з'єднаний з виходом вузла зчитуванням регістра і суматора відповідно. аналізу цифр множника, причому двадцять перНедоліком такого пристрою є вузька область ший і двадцять другий виходи програмного блока застосування, через те, що забезпечується лише керування з'єднані з входами керування зчитуванвиконання операції множення. ням регістра і суматора відповідно, вихід вузла В основу корисної моделі поставлено задачу формування знака з'єднано зі знаковим розрядом створення арифметичного пристрою, в якому за регістра, введено суматор-віднімач, причому вхід рахунок введення нових блоків та зв'язків розшипершого операнда з'єднаний з інформаційним рено область застосування і досягнуто можливість входом суматора, вихід якого з'єднаний з входом виконання арифметичних операцій додавання, генератора кратних множеного, вісімнадцятий, віднімання і множення десяткових чисел. дев'ятнадцятий і двадцятий виходи програмного Поставлена задача досягається тим, що в блока керування підключені відповідно до входу арифметичний пристрій, який містить регістр, суобнулення, входу керування записом і входу керуматор, генератор кратних множеного, вузол форвання зчитуванням суматора-віднімача, вихід регімування знака, лічильник, програмний блок керустра з'єднаний з інформаційним входом суматоравання, суматор аналізу положення коми, вузол віднімача, який також з'єднаний з виходом суматоаналізу цифр множника, причому вхід др угого опера, вихід суматора-віднімача з'єднаний з інформаранда пристрою з'єднаний з інформаційним вхоційним входом суматора, виходи розрядів суматодом регістра, вихід знакового розряду регістра ра-віднімача з'єднані з виходами розрядів підключений до першого входу вузла формування результату операції додавання або віднімання, знака, виходи програмного блока керування з інформаційний вихід генератора кратних множенопершого по третій підключені відповідно до входів го з'єднаний з входом суматора-віднімача, вихід обнулення регістра, суматора і лічильника, четвезнакового розряду суматора з'єднаний з другим ртий і п'ятий виходи програмного блока керування входом вузла формування знака, вихід якого з'єдпідключені до входів керування записом регістра і наний зі знаковим розрядом суматора-віднімача і суматора, вихід старшого інформаційного розряду регістра, входи кодів операцій додавання, віднісуматора підключений до інформаційного входу мання і множення з'єднані з відповідними входами молодшого інформаційного розряду регістра, шоспрограмного блока керування. тий вихід програмного блока керування підключе 7 38903 8 На Фіг.1 представлена структурна схема ариблока 7 керування і є входом обнулення і входом фметичного пристрою; на Фіг.2 - функціональна керування записом відповідно, його інформаційні схема генератора кратних; на Фіг.3 - процес форвходи 32 і 33 є входами розрядності дробової часмування кратних. тини множеного РА і множника РВ відповідно, а Арифметичний пристрій (Фіг.1) містить регістр виходи з'єднані з виходами 34 і 35 індикації поло1, суматор 2, суматор-віднімач 3, генератор 4 краження коми пристрою відповідно. тних множеного, суматор 5 аналізу положення Керуючий вхід 36 лічильника 6 з'єднаний з відкоми, лічильник 6, програмний блок 7 керування, повідним виходом програмного блока 7 керування вузол 8 формування знака, вузол 9 аналізу цифр і є входом керування записом розрядності М мномножника. жника по інформаційному входу 37 лічильника 6, а Керуючі входи 10 і 11 регістра 1 з'єднані з відйого керуючі входи 38 і 39 з'єднані з відповідними повідними виходами програмного блока 7 керувиходами програмного блока 7 керування і є відвання і є відповідно входами керування записом і повідно входом обнулення і входом лічби на змезсувом ліворуч вмісту регістра 1, вхід другого опеншення лічильника 6. Вихід ознаки нуля Р0 лічильранда пристрою підключений до інформаційного ника 6 з'єднаний з відповідним входом входу 12 регістра 1, ви хід старшого розряду сумапрограмного блока 7 керування, вихід 40 регістра тора 2 з'єднаний з інформаційним входом молод1 і вихід 41 суматора 2 є виходами відповідно сташого розряду регістра 1, а керуючий вхід 13 регісрших і молодших розрядів добутку, керуючі входи тра 1 і керуючий вхід 14 знакового розряду 42-44 суматора-віднімача 3 з'єднані з відповідними регістра 1 з'єднані з відповідними виходами провиходами програмного блока 7 керування і є відграмного блока 7 керування і є відповідно входом повідно входом обнулення, входом керування заобнулення регістра 1 і входом керування записом писом і входом керуванням зчитуванням суматознака в знаковий розряд регістра 1. ра-віднімача 3, а керуючий вхід 45 регістра 1 і Інформаційний вхід знакового розряду регісткеруючий вхід 46 суматора 2 з'єднані з відповіднира 1 і суматора-віднімача 3 з'єднані з виходом вуми виходами програмного блока 7 керування і є зла 8 формування знака, один з входів якого з'єдвідповідно входами керування зчитуванням регістнаний з виходом знакового розряду регістра 1, а ра 1 і суматора 2. Вхід першого операнда придругий вхід з'єднаний з виходом знакового розряду строю з'єднаний з інформаційним входом 47 сумасуматора 2. Керуючий вхід 15 старшого k-го розтора 2, вихід 48 суматора-віднімача 3 є виходом ряду регістра 1 з'єднаний з відповідним виходом розрядів результату операції додавання або відніпрограмного блока 7 керування і є відповідно вхомання, входи кодів операцій додавання 49, віднідом обнулення цього розряду. Ін формаційний вимання 50, множення 51 з'єднані з відповідними хід старшого k-го розряду регістра 1 з'єднаний з входами програмного блока 7 керування. входом 16 вузла 9 аналізу цифр множника, вихід Генератор 4 кратних множеного (Фіг.2) містить якого з'єднаний з входом 17 керування значенням суматори 52-55, комутатор 56 і блок 57 формуванкратності генератора 4 кратних множеного, а вихід ня кратних, його інформаційний вхід з'єднаний з 18 ознаки нуля в старшому k-му розряді регістра 1 виходом 26 суматора-віднімача 2, керуючий вхід з'єднаний з відповідним входом програмного блока 25 з'єднаний з входом керування записом множе7 керування. Керуючий вхід 19 суматора 2 з'єднаного до суматорів 52-55, керуючий вхід 27 з'єднаний з відповідним виходом програмного блока 7 ний з входом керування зчитуванням суматорів 52керування і є входом керування записом інформа55, керуючий вхід 28 з'єднаний з входом встановції в суматор 2, а його інформаційний вхід 20 з'єдлення у початковий стан суматорів 52-55, інфорнаний з інформаційним виходом суматорамаційні виходи суматорів 52-55 з'єднані відповідно віднімача 3, вхід якого з'єднаний також з інформаз інформаційними входами 58-61 комутатора 56. У ційним виходом 21 генератора 4 кратних множеноблоці 57 формування кратних виходи 62-64 з'єдго. нані відповідно з інформаційними входами сумаКеруючі входи 22 і 23 суматора 2 з'єднані з торів 53-55, керуючий вхід 29 є входом керування відповідними виходами програмного блока 7 керуформуванням кратних множеного в блоці 57 форвання і є відповідно входом обнулення і входом мування кратних, вхід 17 керування значенням керування зсувом ліворуч інформації в суматорі 2, кратності генератора 4 кратних множеного є керувхід 24 запуску програмного блока 7 керування є ючим входом комутатора 56, інформаційний вихід входом запуску пристрою, а керуючий вхід 25 геякого є інформаційним виходом 21 генератора 4 нератора 4 кратних множеного з'єднаний з відпократних множеного. відним виходом програмного блока 7 керування і є Арифметичний пристрій (Фіг.1) реалізує три входом керування записом множеного. Інформаарифметичні операції: додавання, віднімання, ційний вхід генератора 4 кратних множеного з'єдмноження десяткових чисел і працює в такий спонаний з виходом 26 суматора 2, а керуючі входи сіб. 27-29 з'єднані з відповідними виходами програмДодавання й віднімання десяткових чисел в ного блока 7 керування і є входом керування зчиарифметичному пристрої здійснюється за наявністуванням відповідного кратного множеного в суматю кодів цих операцій на входах 49 або 50 програтор-віднімач 3, входом встановлення у початковий много блока 7 керування. Спочатку відбувається стан генератора 4 кратних множеного і входом встановлення у початковий стан регістра 1, сумакерування формуванням кратних множеного в гетора 2 і суматора-віднімача 3 по сигналах, що нераторі 4 кратних множеного відповідно. Керуючі надходять на керуючі входи 13, 22, 42 цих вузлів входи 30 і 31 суматора 5 аналізу положення коми відповідно. Потім відбувається запис операндів А і з'єднані з відповідними виходами програмного В послідовно у суматор 2 і регістр 1 відповідно по 9 38903 10 входа х 47 і 12 за наявністю сигналів керування на неправильним дробом, тобто коли після коми і вході 19 керування записом інформації в суматор перед старшою значущою цифрою множника зна2 і вході 10 керування записом інформації в регістр ходиться деяка кількість нулів, то виконується но1 відповідно. Знак результату визначається з урармалізація дробу шляхом послідовного зсуву лівохуванням знаків операндів у вузлі 8 формування руч інформації в регістрі 1 на один десятковий знака, куди інформація подається з відповідних розряд і одночасне зменшення вмісту лічильника 6 виходів знакових розрядів регістра 1 і суматора 2, і на одиницю при наявності сигналів зсуву ліворуч і по виходу з вузла 8 формування знака записуєтьлічби на зменшення, що надходять на відповідні ся в знаковий розряд суматора-віднімача 3 за накеруючі входи 11 і 39 з програмного блока 7 керуявністю сигналу на вході 43 керування записом вання. Зсув продовжується доти, поки у старшому суматора-віднімача 3. Операція додавання або k-му розряді регістра 1 не з'явиться старша цифра віднімання виконується в залежності від наявності множника, про що свідчить встановлення нульовокоду операції на входах 49 або 50 програмного го сигналу ознаки нуля на його виході 18. блока 7 керування у суматорі-віднімачі 3 шляхом З інформаційного виходу старшого k-го розряперезапису операнда А з суматора 2 по його виходу регістра 1 значення десяткової цифри множниду 26 при наявності сигналу на його вході 46 керука В надходить на вхід 16 вузла 9 аналізу цифр вання зчитуванням та додавання або віднімання множника, звідки надходить сигнал на вхід 17 кевмісту регістра 1 з його виходу при наявності сигрування значенням кратності генератора 4 кратних налу на його вході 45 керування зчитуванням. Ремноженого, який вибирає кратне, що відповідає зультат операції додавання або віднімання зчитузначенню десяткової цифри в старшому k-му розється з суматора-віднімача 3 з його виходу 48. ряді регістра 1. Відповідне часткове кратне мноОперація множення виконується за наявністю женого подається з виходу 21 генератора 4 краткоду цієї операції на вході 51 програмного блока 7 них множеного на інформаційний вхід суматоракерування. Спочатку відбувається встановлення у віднімача 3 при наявності сигналу керування запипочатковий стан регістра 1, суматора 2, суматорасом на керуючому вході 43 суматора-віднімача 3 і віднімача 3, генератора 4 кратних множеного, сусигналу керування зчитуванням на керуючому матора 5 аналізу положення коми і лічильника 6 по вході 27 генератора 4 кратних множеного. У сумасигналах, що надходять на керуючі входи 13, 22, торі-віднімачі 3 формується остаточне кратне 42, 28, 30 і 38 цих блоків відповідно. Перший опемноженого, звідки по інформаційному входу 20 ранд - множене А записується у суматор 2 по інподається на суматор 2, де сумується з вмістом формаційному входу 46 за наявності сигналу на суматора 2 при наявності сигналу керування запийого вході 19 керування записом, у суматор 5 анасом на його керуючому вході 19. Значення лічильлізу положення коми по інформаційному входу 32 ника 6 при цьому зменшується на одиницю після виконується запис значення розрядності РА дроприходу сигналу лічби на зменшення на його кебової частини множеного А при наявності сигналу руючий вхід 39. керування записом на його керуючому вході 31. Потім відбувається зсув ліворуч на десятковий Потім виконується запис другого операнда - множрозряд інформації в регістрі 1 і суматорі 2 під дією ника В в регістр 1 по інформаційному входу 12 при сигналів керування зсувом, що надходять на кенаявності сигналу керування записом на його керуючі входи 11 і 23 регістра 1 і суматора 2 відповіруючому вході 10. Причому множник В записуєтьдно. При цьому інформація зі старшого розряду ся так, що в старшому k-му розряді регістра 1 знасуматора 2 зсувається у молодший розряд регістходиться його старша значуща цифра. Одночасно ра 1 по його інформаційному входу, значення в лічильник 6 по інформаційному входу 37 записустаршого розряду регістра 1 губиться, а молодший ється значення розрядності М множника при наяврозряд суматора 2 приймає нульове значення. У ності сигналу на його керуючому вході 36. У сумавипадку наявності значущого нуля в k-му старшотор 5 аналізу положення коми по інформаційному му розряді регістра 1, тобто з появою одиничного входу 33 записується значення розрядності РВ сигналу ознаки нуля на його виході 18, відбуваєтьдробової частини множника при наявності сигналу ся лише зсув ліворуч на один десятковий розряд на його керуючому вході 31. інформації в регістрі 1 й у суматорі 2 і зменшення Одночасно з записом другого операнда В зназначення лічильника 6 на одиницю. Якщо вміст ки множеного А і множника В надходять на входи лічильника 6 приймає нульове значення, про що вузла 8 формування знака, який формує знак досвідчить поява одиничного сигналу Р0 на відповідбутк у, що надходить у знаковий розряд регістра 1 ному вході програмного блока 7 керування, то при наявності сигналу керування записом на його операція множення завершується і відбувається керуючому вході 14. Потім множене А переписуобнулення старшого розряду регістра 1 по сигналу ється у генератор 4 кратних множеного з виходу обнулення на керуючому вході 15 цього розряду. 26 суматора 2 при наявності сигналу керування Знак і старші розряди добутку знаходяться в регісзаписом на керуючому вході 25 генератора 4 краттрі 1, а к-ті молодші розряди зберігаються в суманих множеного і сигналу керування зчитуванням торі 2. Зчитування результату відбувається по на вході 46 суматора 2. інформаційних вихода х 40 і 41 відповідно регістра Формування кратних множеного відбувається 1 і суматора 2 при наявності сигналу керування в генераторі 4 при наявності сигналів, що надхозчитуванням на їх відповідних керуючих входах 45 дять з програмного блока 7 керування на керуючі і 46. входи 25, 27 і 29 генератора 4 кратних множеного. У таблиці 1 наведено співвідношення між ноМноження відбувається, починаючи зі старших мерами виводів, задіяними вузлами і виконуванирозрядів множника В. У випадку, якщо множник є ми мікроопераціями, а також кодування сигналів 11 38903 12 керування і прийнято такі позначення: ПБК 7 - проСм3 - суматор-віднімач 3; См5 - суматор 5 аналізу грамний блок 7 керування; Рг1 - регістр 1; См2 положення коми; Лк6 - лічильник 6. суматор 2; ГК4 - генератор 4 кратних множеного; Сигнал У1 У2 У3 У4 У5 У6 У7 У8 У9 У 10 У 11 У 12 У 13 У 14 У 15 У 16 У 17 У 18 У 19 У 20 У 21 У 22 Вивід 10 11 13 14 15 19 22 23 25 27 28 29 30 31 36 38 39 42 43 44 45 46 Задіяний вузол Рг1 Рг1 Рг1 Рг1 Рг1 См2 См2 См2 ПС4 ГК4 ГК4 ГК4 См5 См5 Лк6 Лк6 Лк6 См3 См3 См3 Рг1 См2 Генератор 4 кратних множеного (Фіг.2) працює в такий спосіб. На початку виконання операції множення інформація в усіх суматорах 52-55 дорівнює нулю за сигналом встановлення у початковий стан на керуючому вході 28 генератора 4 кратних множеного. По інформаційному входу 26 у суматори 52-55 записується множене А за наявністю сигналу керування записом на керуючому вході 25 генератора 4 кратних множеного. Після запису множеного А в суматори 52-55 дані з суматорів 52-54 по інформаційних ви ходах передаються на входи блока 57 формування кратних за сигналом керування зчитуванням на керуючому вході 27 генератора 4 кратних множеного. По інформаційних виходах 62-64 блока 57 формування кратних в кожен з суматорів 53-55 додається множене А таким чином, що послідовно за чотири такти формуються базові кратні множеного відповідно в кожному з суматорів 52-55. На суматорі 52 необхідне кратне А множеного буде сформоване на першому такті, тобто при записі множеного А. На суматорі 53 формується кратне 2А множеного на 2-му такті шляхом додавання множеного А, що подається через вихід 62 блока 57 формування кратних і є вихідною інформацією першого суматора 52, яка також одночасно додається в суматор 54 з виходу 63 блока 57 формування кратних. При цьому в суматорі 54 формується на 2-му такті кратне 2А множеного аналогічно, як і в суматорі 53, а на 3-му такті формується кратне 4А множеного як сума вмісту суматорів 54 і 53, оскільки з останнього інформація подається через вихід 63 блока 57 формування кратних. Одночасно на 3-му такті вміст суматора 53 з виходу 64 блока 57 формування кратних подається в суматор 55, де формується кратне 3А множеного. Сформоване на суматорі 54 кратне 4А Мікрооперації Таблиця 1 Запис Зсув ліворуч Обнулення Запис знака Обнулення старшого розряду Запис Обнулення Зсув ліворуч Запис Зчитування Встановлення у початковий стан Керування формуванням кратних Обнулення Запис Запис Обнулення Лічба на зменшення Обнулення Запис Зчитування Зчитування Зчитування множеного через інформаційний вихід 64 блока 57 формування кратних подається на суматор 55 і сумується з кратним ЗА множеного, тобто в суматорі 55 формується кратне 7А множеного на 4-му такті. Сформовані відповідні кратні у суматорах 5255 по їх інформаційних вихода х подаються на входи 58-61 комутатора 56, який визначає необхідне кратне за сигналом керування значенням кратності на своєму керуючому вході 17 і подає його на свій інформаційний вихід 21. Таким чином, вміст відповідного суматора 52-55 зчитується через комутатор 56 при наявності сигналу керування зчитуванням інформації на керуючому вході 27 генератора 4 кратних множеного. Сформовані чотири кратні множеного використовуються для формування за допомогою суматора-віднімача 3 решти кратних множеного у вигляді 3А, 5А, 6А, 8А, 9А, що значно підвищує швидкодію. Процес формування кратних множеного (Фіг.3) відбувається за чотири такти з формуванням чотирьох базових кратних множеного А, а саме А, 2А, 4А, 7А. Формування базових кратних множеного відбувається таким чином. В кожен з суматорів 52-55 на 1-му такті записується множене А. На 2му такті формується кратне 2А множеного шляхом додавання множеного А з суматора 52 у суматори 53 і 54. На 3-му такті формується кратне 4А множеного у суматорі 54 і кратне 3А множеного у суматорі 55, що є результатом додавання кратного 2А множеного з суматора 53. На 4-му такті формується кратне 7А множеного у суматорі 55, що є результатом додавання кратного 4А множеного з суматора 54. Можливість зменшення часу формування базових кратних множеного до чотирьох тактів замість необхідних восьми для десяткових чисел 13 38903 14 забезпечує підвищення швидкодії арифметичного ного. Крім того, використання суматора-віднімача пристрою, оскільки відсутні кратні множеного мождозволяє розширити область використання арифна сформувати при необхідності на суматоріметичного пристрою за рахунок виконання операвіднімачі за один такт, використовуючи вже сфорцій додавання і віднімання. мовані базові кратні у генераторі кратних множе Комп’ютерна в ерстка А. Крижанівський Підписне Тираж 28 прим. Міністерство осв іт и і науки України Держав ний департамент інтелектуальної в ласності, вул. Урицького, 45, м. Київ , МСП, 03680, Україна ДП “Український інститут промислов ої в ласності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюArithmetical device

Автори англійськоюKozhemiako Volodymyr Prokopovych, Martyniuk Tetiana Borysivna, Boiko Oksana Arkadiivna

Назва патенту російськоюАрифметическое устройство

Автори російськоюКожемяко Владимир Прокофьевич, Мартынюк Татьяна Борисовна, Бойко Оксана Аркадиевна

МПК / Мітки

МПК: G06F 7/00

Мітки: арифметичний, пристрій

Код посилання

<a href="https://ua.patents.su/7-38903-arifmetichnijj-pristrijj.html" target="_blank" rel="follow" title="База патентів України">Арифметичний пристрій</a>

Попередній патент: Валок валкових машин

Наступний патент: Спосіб виготовлення кільцевих деталей

Випадковий патент: Складений елемент (варіанти) і панельний елемент для формування цього складеного елемента