Напівпровідниковий запам’ятовуючий пристрій з енергонезалежними двотранзисторними запам’ятовуючими комірками

Номер патенту: 59400

Опубліковано: 15.09.2003

Автори: Віманн Ханс-Хайнріх, Зедлак Хольгер, Поккрандт Вольфганг

Формула / Реферат

1. Напівпровідниковий запам'ятовуючий пристрій, що містить щонайменше одну запам'ятовуючу комірку, яка характеризується такими ознаками:

- вона містить n-канальний транзистор (АТ1, АТ2; АТ11, АТ12) вибору і n-канальний запам'ятовуючий транзистор (ST1, ST2; ST11, ST12),

- n-канальний транзистор (АТ1, АТ2; АТ11, АТ12) вибору має вивід затвора, а також два виводи каналу, причому вивід затвора з'єднаний з шиною рядка (AG1), яка веде до запам'ятовуючої комірки (Z1, Z2; Z11, Z12),

- n-канальний запам'ятовуючий транзистор (ST1, ST2; ST11, ST12) має вивід затвора (KG1, KG2; KG 11, KG 12), а також два виводи каналу,

- другий вивід каналу запам'ятовуючого транзистора і перший вивід каналу транзистора вибору з'єднані між собою, причому перший вивід каналу запам'ятовуючого транзистора та другий вивід каналу транзистора вибору з'єднані з відповідною шиною (SP1) стовпця, що веде до запам'ятовуючої комірки (Z1, Z2; Z11, Z12), причому напівпровідниковий запам'ятовуючий пристрій містить щонайменше один передавальний транзистор (ТТ1, ТТ2; ТТ11, ТТ12), що має перший і другий виводи каналу, причому перший вивід каналу передавального транзистора з'єднано з виводом (KG1, KG2; KG11, KG12) затвора запам'ятовуючого транзистора, який відрізняється тим, що

- передавальний транзистор (ТТ1, ТТ2; ТТ11, ТТ12) виконаний у вигляді р-канального польового транзистора,

- другий вивід каналу передавального транзистора з'єднаний з шиною (AG1, AG2; AG 11, AG12) рядка, що веде до запам'ятовуючої комірки (Z1, Z2; Z11, Z12).

2. Напівпровідниковий запам'ятовуючий пристрій за п. 1, який відрізняється тим, що він містить шину керування (SCHRX), з'єднану з затвором передавального транзистора (ТТ1, ТТ2; ТТ11, ТТ12) таким чином, що керування передавальним транзистором може бути здійснене через шину керування (SCHRX).

3. Напівпровідниковий запам'ятовуючий пристрій за п. 2, який відрізняється тим, що він містить n-канальний розрядний транзистор (ЕТ1, ЕТ2; ЕТ11, ЕТ12), який має затвор, а також перший і другий виводи каналу, причому перший вивід каналу розрядного транзистора з'єднаний з виводом (KG1, KG2; KG 11, KG 12) затвора запам'ятовуючого транзистора, другий вивід каналу розрядного транзистора з'єднаний з корпусом, а затвор розрядного транзистора з'єднаний з шиною керування (SCHRX).

4. Напівпровідниковий запам'ятовуючий пристрій за будь-яким із попередніх пунктів, який відрізняється тим, що він виконаний у вигляді рядків і стовпців, причому всередині рядків

- виводи затворів транзисторів вибору групи запам'ятовуючих комірок (Z1, Z3; Z2, Z4; Z11, Z13; Z12, Z14) з'єднані паралельно,

- виводи затворів запам'ятовуючих транзисторів групи запам'ятовуючих комірок (Z1, Z3; Z2, Z4; Z11, Z13; Z12, Z14) з'єднані паралельно, причому всередині стовпців перші виводи каналів запам'ятовуючих транзисторів і другі виводи каналів транзисторів вибору з'єднані паралельно.

5. Напівпровідниковий запам'ятовуючий пристрій за п. 4, який відрізняється тим, що він має схему керування щонайменше одним стовпцем, яка містить по одному р-канальному транзистору (ВТ11, ВТ12) вибору блока, що має вивід затвора вибору блока і два виводи каналу вибору блока, причому перший вивід каналу вибору блока з'єднаний з шиною (AG1, AG2) рядка, що веде до запам'ятовуючої комірки, і другий вивід каналу вибору блока з'єднаний з першим виводом каналу передавального транзистора.

6. Напівпровідниковий запам'ятовуючий пристрій за п. 5, який відрізняється тим, що він містить шину керування вибором блока, з'єднану із затворами транзисторів вибору блока таким чином, що керування транзисторами (ВТ11, ВТ12) вибору блока може бути здійснене через шину (BLKN) керування вибором блока.

Текст

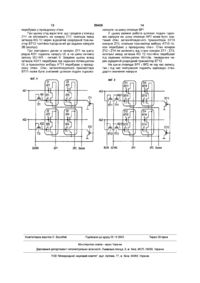

1 Напівпровідниковий запам'ятовуючий пристрій, що містить щонайменше одну запам'ятовуючу комірку, яка характеризується такими ознаками - вона містить n-канальний транзистор (АТ1, АТ2, АТ11, АТ12) вибору і n-канальний запам'ятовуючий транзистор (ST1, ST2, ST11, ST12), - n-канальний транзистор (АТ1, АТ2, АТ11, АТ12) вибору має вивід затвора, а також два виводи каналу, причому вивід затвора з'єднаний з шиною рядка (AG1), яка веде до запам'ятовуючої комірки (Z1.Z2, Z11.Z12), - n-канальний запам'ятовуючий транзистор (ST1, ST2, ST11, ST12) має вивід затвора (KG1, KG2, KG 11, KG 12), а також два виводи каналу, - другий вивід каналу запам'ятовуючого транзистора і перший вивід каналу транзистора вибору з'єднані між собою, причому перший вивід каналу запам'ятовуючого транзистора та другий вивід каналу транзистора вибору з'єднані з ВІДПОВІДНОЮ шиною (SP1) стовпця, що веде до запам'ятовуючої комірки (Z1, Z2, Z11, Z12), причому напівпровідниковий запам'ятовуючий пристрій містить щонайменше один передавальний транзистор (ТИ, ТТ2, ТТ11, ТТ12), що має перший і другий виводи каналу, причому перший вивід каналу передавального транзистора з'єднано з виводом (KG1, KG2, KG11, KG12) затвора запам'ятовуючого транзистора, який відрізняється тим, що - передавальний транзистор (ТИ, ТТ2, ТТ11, ТТ12) виконаний у вигляді р-канального польового транзистора, - другий вивід каналу передавального транзистора з'єднаний з шиною (AG1, AG2, AG 11, AG12) рядка, що веде до запам'ятовуючої комірки (Z1, Z2, Z11.Z12) 2 Напівпровідниковий запам'ятовуючий пристрій за п 1, який відрізняється тим, що він містить шину керування (SCHRX), з'єднану з затвором передавального транзистора (ТИ, ТТ2, ТТ11, ТТ12) таким чином, що керування передавальним транзистором може бути здійснене через шину керування (SCHRX) 3 Напівпровідниковий запам'ятовуючий пристрій за п 2, який відрізняється тим, що він містить пканальний розрядний транзистор (ЕТ1, ЕТ2, ЕТ11, ЕТ12), який має затвор, а також перший і другий виводи каналу, причому перший вивід каналу розрядного транзистора з'єднаний з виводом (KG1, KG2, KG 11, KG 12) затвора запам'ятовуючого транзистора, другий вивід каналу розрядного транзистора з'єднаний з корпусом, а затвор розрядного транзистора з'єднаний з шиною керування (SCHRX) 4 Напівпровідниковий запам'ятовуючий пристрій за будь-яким із попередніх пунктів, який відрізняється тим, що він виконаний у вигляді рядків і стовпців, причому всередині рядків - виводи затворів транзисторів вибору групи запам'ятовуючих комірок (Z1, Z3, Z2, Z4, Z11, Z13, Z12, Z14) з'єднані паралельно, - виводи затворів запам'ятовуючих транзисторів групи запам'ятовуючих комірок (Z1, Z3, Z2, Z4, Z11, Z13, Z12, Z14) з'єднані паралельно, причому всередині стовпців перші виводи каналів запам'ятовуючих транзисторів і другі виводи каналів транзисторів вибору з'єднані паралельно 5 Напівпровідниковий запам'ятовуючий пристрій за п 4, який відрізняється тим, що він має схему керування щонайменше одним стовпцем, яка містить по одному р-канальному транзистору (ВТ11, ВТ12) вибору блока, що має вивід затвора вибору блока і два виводи каналу вибору блока, причому перший вивід каналу вибору блока з'єднаний з шиною (AG1, AG2) рядка, що веде до запам'ятовуючої комірки, і другий вивід каналу вибору блока з'єднаний з першим виводом каналу передавального транзистора 6 Напівпровідниковий запам'ятовуючий пристрій за п 5, який відрізняється тим, що він містить О о о о> ю 59400 шину керування вибором блока, з'єднану із затворами транзисторів вибору блока таким чином, що керування транзисторами (ВТ11, ВТ12) вибору блока може бути здійснене через шину (BLKN) керування вибором блока Винахід стосується напівпровідникового запам'ятовуючого пристрою (ЗП), що містить щонайменше одну, зокрема, енергонезалежну запам'ятовуючу комірку, яка характеризується такими ознаками вона містить n-канальний транзистор вибору і n-канальний запам'ятовуючий транзистор, n-канальний транзистор вибору має вивід затвора, а також два виводи каналу, причому вивід затвора з'єднаний з шиною рядка, яка веде до запам'ятовуючої комірки, n-канальний запам'ятовуючий транзистор має вивід затвора або управляючий затвор, а також два виводи каналу, другий вивід каналу запам'ятовуючого транзистора і перший вивід каналу транзистора вибору з'єднані між собою, причому інший вивід каналу запам'ятовуючого транзистора та інший вивід каналу транзистора вибору з'єднані з шиною стовпця, що веде до запам'ятовуючої комірки, причому напівпровідниковий ЗП містить щонайменше один передавальний транзистор, що має перший і другий виводи каналу, причому перший вивід каналу передавального транзистора з'єднано з виводом затвора запам'ятовуючого транзистора У напівпровідникових ЗП такого роду окремі транзистори виконані за польовою технологією на напівпровідниковій підкладці При цьому запам'ятовуючий транзистор має плаваючий затвор, завдяки чому при подачі ВІДПОВІДНИХ напруг на виводи каналу і вивід затвора він програмується таким чином, що може перебувати у бажаному стані тривалий час або незалежно від наявності напруги живлення Для зчитування даних із запам'ятовуючої комірки один вивід каналу запам'ятовуючого транзистора і один вивід каналу транзистора вибору з'єднані між собою, причому інший вільний вивід каналу запам'ятовуючого транзистора і інший вільний вивід каналу транзистора вибору з'єднано з шиною стовпця, що веде до запам'ятовуючої комірки Якщо при подачі напруги на відповідну шину стовпця протікає струм, значить запам'ятовуючий транзистор при програмуванні був переведений у стан «відкритий» Якщо ж при подачі цієї напруги на відповідну шину стовпця струм не протікає, значить запам'ятовуючий транзистор при програмуванні був переведений у стан «закритий», тобто дані були зітерті У європейському патенті ЕР 0317 443 А1 описана двотранзисторна запам'ятовуюча комірка, що містить транзистор вибору і транзистор із плаваючим затвором Для керування транзистором із плаваючим затвором формують спеціальну напругу Тому в основу винаходу покладено задачу розробки запам'ятовуючої комірки із вказаними вище родовими ознаками, а також напівпровідникового запам'ятовуючого пристрою із вказаними вище родовими ознаками, в якому з низькими технологічними витратами забезпечується бездефектне програмування Ця задача вирішена тим, що передавальний транзистор виконаний у вигляді р-канального транзистора, причому другий вивід каналу передавального транзистора з'єднаний на відміну від рівня техніки не із ЗОВНІШНІМ джерелом управляючої напруги, а з шиною рядка, що веде до запам'ятовуючої комірки В основу винаходу покладено знання того факту, що у схемах вказаного вище роду має бути подолана втрата порогової напруги у транзисторі передачі, для чого має бути сформована більша напруга затвора передавального транзистора Ця проблема може бути вирішена за рахунок виконання передавального транзистора у вигляді транзистора зі зниженою пороговою напругою, що, одначе, може бути досягнуто лише за рахунок збільшення технологічних витрат При реалізації структури і схеми під'єднання передавального транзистора для програмування запам'ятовуючого транзистора більше немає потреби у подоланні порогової напруги, завдяки чому з низькими технологічними витратами забезпечується бездефектне програмування Крім того, в основу винаходу покладено знання того факту, що, за рівнем техніки, внаслідок особливої схеми під'єднання передавального транзистора напруга управляючих затворів запам'ятовуючих комірок, не залучених в даний момент до процесу програмування, має не визначене, довільне «плаваюче» значення, що може призвести до ємнісних перехресних паразитних зв'язків між напругами програмування Такі перехресні паразитні зв'язки у напівпровідниковому ЗП за винаходом відсутні, бо при програмуванні винайденого ЗП стан виводу затвора кожної запам'ятовуючої комірки задано однозначно Згідно з винаходом, на вивід затвора передавального транзистора може бути поданий логічний сигнал, перетворений у високу напругу Доцільно для цього застосувати логічний сигнал, що використовується для керування станом запам'ятовуючої комірки під час програмування При цьому, завдяки виконанню передавального транзистора у вигляді р-канального транзистора, можна відмовитись від витратного у виготовленні інвертора для керування затвором У напівпровідникових ЗП такого роду проблему становить той факт, що формування необхідних для програмування напруг пов'язано зі значними технологічними витратами До того ж, при програмуванні запам'ятовуючої комірки часто виникають помилки у інших запам'ятовуючих комірках, які під час даного процесу програмування не були вибрані для програмування 59400 передавального транзистора, оскільки рканальний транзистор запирається при подачі сигналу на затвор і навпаки Одначе, в принципі передавальний транзистор може бути виконаний також n-канальним з інвертором При програмуванні ЗП за винаходом вся напруга програмування через канал передавального транзистора без втрат і без додаткових спеціальних заходів може бути передана на затвори запам'ятовуючих транзисторів Принагідне слід згадати, що винахід може бути реалізований також у ЗП, в яких транзистори вибору і транзистори пам'яті виконано р-канальними, при цьому передавальний транзистор має бути пканальним Хоча така структура скоріше не матиме застосування, вона може мати переваги, коли необхідно створити так званий «діркопровід» для передачі носив заряду У вдосконаленому варіанті винаходу схема керування містить n-канальний розрядний транзистор, який має вивід затвора, а також перший і другий виводи розрядного каналу, причому перший вивід розрядного каналу з'єднаний з виводом затвора запам'ятовуючого транзистора, другий вивід розрядного каналу з'єднаний з корпусом, а вивід затвора з'єднаний з тією управляючою шиною, через яку здійснюється керування передавальним транзистором Такий розрядний транзистор під час програмування забезпечує подачу на затвор транзистора пам'яті заданого потенціалу, зокрема, потенціалу корпусу Завдяки цьому, саме при запертому транзисторі передачі забезпечується перебування затвора запам'ятовуючого транзистора під потенціалом 0В Напівпровідниковий ЗП за винаходом організований у рядки і стовпці, причому всередині рядків виводи затворів транзисторів вибору і виводи затворів запам'ятовуючих транзисторів кількох запам'ятовуючих комірок з'єднані паралельно і, причому всередині стовпців перші виводи каналів запам'ятовуючих транзисторів і другі виводи каналів транзисторів вибору з'єднані паралельно Таким чином можна дуже просто організувати винайдений ЗП у рядки і стовпці При цьому передбачений щонайменше один стовпець, схема керування яким містить передавальний транзистор, під'єднаний за винаходом Додатково схема керування може містити по одному р-канальному транзистору вибору блока, що має вивід затвора вибору блока і два виводи каналу вибору блока, причому перший вивід каналу вибору блока з'єднаний з шиною рядка, що веде до запам'ятовуючої комірки, а другий вивід каналу вибору блока з'єднаний з першим виводом каналу передавального транзистора Завдяки цьому, напівпровідниковий ЗП для програмування може бути розділений на окремі блоки, що є особливо вигідним, оскільки більше немає потреби програмувати певні стани для всього рядка ЗП, а лише для одного блока, вибраного із цього рядка Завдяки цьому, тепер є можливість, зокрема, стирати дані у окремому блоці Для цього передбачена шина керування вибором блоків, з'єднана з виводами затворів транзисторів вибору блоків таким чином, що керування транзисторами вибору блоків здійснюється через шину керування вибору блоків Винахід стосується також загалом схеми керування щонайменше однією запам'ятовуючою коміркою, що містить під'єднаний описаним вище чином передавальний транзистор Нижче винахід детальніше пояснюється на двох прикладах здійснення з використанням ілюстрацій, на яких зображені Фіг 1 схема першого варіанту напівпровідникового ЗП за винаходом, Фіг 2 схема другого варіанту напівпровідникового ЗП за винаходом На фіг 1 зображена схема першого варіанту напівпровідникового ЗП за винаходом, виконаного на напівпровідниковій підкладці На фіг 1 зображено лише фрагмент напівпровідникового запам'ятовуючого пристрою, який містить запам'ятовуючі комірки Z1, Z2, Z3 і Z4 Управління запам'ятовуючими комірками Z1, Z2, Z3 і Z4 може бути здійснене за допомогою двох шин рядків AG1, AG2 і двох шин стовпців SP1, SP2 Для керування запам'ятовуючими комірками Z1, Z2, Z3 і Z4 служить схема управління, що містить передавальний транзистор ТИ, розрядний транзистор ЕТ1, передавальний транзистор ТТ2, а також розрядний транзистор ЕТ2, керування якими здійснюється через шину сигналу запису SCHRX На шину сигналу запису SCHRX подано перетворений у високу напругу сигнал, сформований із логічного сигналу, який здійснює керування процесом запису Транзистор передачі ТТ1 і передавальний транзистор ТТ2 виготовлені за польовою технологією у вигляді р-канальних транзисторів, а розрядний транзистор ЕТ1 і розрядний транзистор ЕТ2 виготовлені за польовою технологією у вигляді пканальних транзисторів Запам'ятовуюча комірка Z1 містить транзистор вибору АТ1 і запам'ятовуючий транзистор ST1 Транзистор вибору АТ1 виготовлений у вигляді звичайного польового n-канального транзистора, тоді як запам'ятовуючий транзистор ST1 виготовлений у вигляді n-канального транзистора із так званим "плаваючим затвором" Перший вивід каналу транзистора вибору АТ1 з'єднаний з шиною стовпця SP1, а другий вивід каналу транзистора вибору АТ1 з'єднаний з першим виводом каналу запам'ятовуючого транзистора ST1 Другий вивід каналу запам'ятовуючого транзистора ST1 з'єднаний зі спільною шиною Source Вивід затвора транзистора вибору АТ1 з'єднаний із шиною рядка AG1 До шини вибору рядка AG1 під'єднаний також другий вивід каналу передавального транзистора ТТ1 Перший вивід каналу передавального транзистора ТТ1 з'єднаний з виводом затвора KG1 запам'ятовуючого транзистора ST1 При цьому ВІДПОВІДНИЙ виводові затвора KG1 затвор запам'ятовуючого транзистора ST1 виконаний у вигляді так званого "плаваючого затвора" Вивід затвора передавального транзистора ТТ1 з'єднаний з шиною сигналу запису SCHRX Вивід затвора розрядного транзистора ЕТ1 також з'єднаний з шиною сигналу запису SCHRX Перший вивід каналу розрядного транзистора ЕТ1 з'єднаний з виводом затвора KG1 запам'ятовуючо 59400 го транзистора ST1, а другий вивід каналу розрядного транзистора ЕТ1 безпосередньо з'єднаний з корпусом Запам'ятовуюча комірка Z3 відносно шини рядка AG1 під'єднана паралельно запам'ятовуючій комірці Z1 При цьому запам'ятовуюча комірка Z3 містить транзистор вибору АТЗ, виконаний у вигляді звичайного польового п-канального транзистора, і запам'ятовуючий транзистор ST3, виконаний у вигляді п-канального транзистора з "плаваючим затвором" Перший вивід каналу транзистора вибору АТЗ з'єднаний з шиною стовпця SP2, а другий вивід каналу транзистора вибору АТЗ з'єднаний з першим виводом каналу запам'ятовуючого транзистора ST3 Другий вивід каналу запам'ятовуючого транзистора ST3 з'єднаний з шиною Source Вивід затвора транзистора вибору АТЗ під'єднаний паралельно виводу затвора транзистора вибору АТ1 і з'єднаний з шиною рядка AG1 Вивід затвора запам'ятовуючого транзистора ST3 під'єднаний паралельно виводу затвора запам'ятовуючого транзистора ST1 і з'єднаний з другим виводом каналу передавального транзистора ТТ1 Внаслідок цього вивід затвора запам'ятовуючого транзистора ST3 також з'єднаний з першим виводом каналу розрядного транзистора ЕТ1 Запам'ятовуюча комірка Z2 містить транзистор вибору АТ2 і запам'ятовуючий транзистор ST2 Транзистор вибору АТ2 виконаний у вигляді звичайного польового п-канального транзистора, а запам'ятовуючий транзистор виконаний у вигляді пканального транзистора з "плаваючим затвором" Перший вивід каналу транзистора вибору АТ2 з'єднаний з шиною стовпця SP2, а другий вивід каналу транзистора вибору АТ2 з'єднаний з першим виводом каналу запам'ятовуючого транзистора ST2 Другий вивід каналу запам'ятовуючого транзистора ST2 з'єднаний зі спільною шиною Source Вивід затвора транзистора вибору АТ2 з'єднаний з шиною рядка AG2 Другий вивід каналу передавального транзистора ТТ2 також з'єднаний з шиною рядка AG2 Перший вивід каналу передавального транзистора ТТ2 з'єднаний з виводом затвора KG2 запам'ятовуючого транзистора ST2 При цьому ВІДПОВІДНИЙ виводу затвора KG2 затвор запам'ятовуючого транзистора ST2 виконаний у вигляді "плаваючого затвора" Вивід затвора передавального транзистора ТТ2 і вивід затвора розрядного транзистора ЕТ2 з'єднані з шиною сигналу запису SCHRX Перший вивід каналу розрядного транзистора ЕТ2 з'єднаний з виводом затвора KG2, а другий вивід каналу розрядного транзистора безпосередньо з'єднаний з корпусом Комірка Z4 відносно шини рядка AG2 під'єднана паралельно комірці Z2 При цьому комірка Z4 містить транзистор вибору АТ4, виконаний у вигляді звичайного польового п-канального транзистора, а також запам'ятовуючий транзистор ST4, виконаний у вигляді транзистора з "плаваючим затвором" Перший вивід каналу транзистора вибору АТ4 з'єднаний з шиною стовпця SP2, а другий вивід каналу транзистора вибору АТ4 з'єднаний з першим виводом каналу запам'ятовуючого транзистора ST4 Другий вивід каналу запам'ято 8 вуючого транзистора ST4 з'єднаний зі спільною шиною Source Вивід затвора транзистора вибору АТ4 під'єднаний паралельно виводу затвора транзистора вибору AT" і з'єднаний з шиною рядка AG2 Вивід затвора запам'ятовуючого транзистора ST4 під'єднаний паралельно виводу затвора запам'ятовуючого транзистора ST2 і з'єднаний з другим виводом каналу передавального транзистора ТТ2 Внаслідок цього вивід затвора запам'ятовуючого транзистора ST4 також з'єднаний з першим виводом каналу розрядного транзистора ЕТ2 Відносно ШИНИ СТОВПЦЯ SP1 комірки Z1, Z2 під'єднані паралельно, а комірки Z3, Z4 під'єднані паралельно відносно шини стовпця Нижче пояснюються три режими запам'ятовуючої комірки "стирання", "запис" і "зчитування" для запам'ятовуючої комірки Z1 При цьому, в режимі "стирання" на шину стовпця SP1 не подається жоден сигнал, оскільки для цього він не потрібен Лише при записі і при зчитуванні вмісту комірки Z1 на шину стовпця SP1 подається сигнал Одначе, в цьому описі цей процес детальніше не відображено, оскільки для суті винаходу він має другорядне значення У наведеній нижче таблиці відображені стани шин рядків AG1, AG2, виводів затворів KG1, KG2 і шини сигналу запису SCHRX для окремих режимів Стирання Запис Зчитування AG1 Up Up Ul KG1 Up 0 Ul AG2 KG2 SCHRX 0 O+Utp 0 0 0 Up 0 O+Utp 0 При цьому напруга "Up" означає напругу програмування (наприклад, 18В), напруга "UI" означає напругу зчитування, а напруга "Utp" означає додатне абсолютне значення порогової напруги рканального транзистора (близько 1В) Як видно із таблиці, при стиранні рядка запам'ятовуючого пристрою, в якому знаходиться комірка Z1, на шину рядка AG1 подають напругу програмування Up При цьому на перший вивід каналу передавального транзистора ТТ1 також подається напруга програмування Up На шину сигналу запису SCHRX подають напругу 0В, завдяки чому передавальний транзистор ТТ1 перебуває у провідному стані, оскільки він є р-канальним транзистором І навпаки, розрядний транзистор ЕТ1 виконаний п-канальним, внаслідок чого подана на шину сигналу запису SCHRX напруга 0В, прикладена до його затвора, переводить його у непровідний стан Внаслідок цього на вивід затвора KG1 подається напруга програмування Up, що переводить "плаваючий затвор" запам'ятовуючого транзистора ST1 у стан "дані зітерто" На комірку Z2 процеси на шині рядка AG1, а також на шині сигналу запису SCHRX не впливають, оскільки вивід затвора KG2 постійно перебуває під заданим потенціалом шини рядка AG2 OB+Utp Оскільки комірки Z3 і Z4 відносно шин рядків AG1 і AG2 під'єднані паралельно коміркам Z1 і Z2, у них відбуваються ті ж процеси, що й у комірках Z1 і Z2 Тому в режимі "стирання" здійснюється стирання даних у всіх тих комірках, що приводять 59400 10 ся у дію шиною рядка AG1 Запам'ятовуюча комірка Z11 містить транзистор вибору АТ11 і запам'ятовуючий транзистор Стирання даних у комірках Z2 і Z4 здійснюють ST11 Транзистор вибору АТ11 виготовлений як аналогічно до комірок Z1 і Z3 звичайний польовий транзистор з n-каналом, а При записі даних у комірку Z1 на шину рядка запам'ятовуючий транзистор ST11 виготовлений у AG1 і на шину сигналу запису SCHRX подають вигляді n-канального транзистора із так званим напругу Up Завдяки такому стану шини сигналу "плаваючим затвором" Перший вивід каналу тразапису SCHRX, n-канальний розрядний транзистор нзистора вибору АТ11 з'єднаний з шиною стовпця ЕТ1 стає провідним, а р-канальний передавальний SP1, а другий вивід каналу транзистора вибору транзистор ТТ1 запирається Внаслідок цього на АТ11 з'єднаний з першим виводом каналу запам'явиводі затвора KG1 присутній потенціал корпусу, а товуючого транзистора ST11 Другий вивід каналу саме 0В Подачею потрібного сигналу на шину запам'ятовуючого транзистора ST11 з'єднаний зі стовпця SP1 здійснюють запис інформації у запаспільною шиною Source м'ятовуючий транзистор ST1, оскільки транзистор вибору АТ1, на затвор якого подано сигнал Up, Вивід затвора транзистора вибору АТ11 з'єдперебуває у провідному стані наний з шиною рядка AG1 3 шиною рядка AG1 з'єднаний також другий вивід каналу транзистора При цьому слід ВІДМІТИТИ, що процеси у комірці вибору блока ВТ11 Другий вивід каналу передаZ1 не впливають на комірку Z2, оскільки вивід завального транзистора ТТ11 з'єднаний з першим твора KG2 через відкритий розрядний транзистор виводом каналу транзистора вибору блока ВТ11, а ЕТ2 постійно під'єднаний до заданої напруги 0В перший вивід каналу передавального транзистора (корпус) ТТ11 з'єднаний з виводом затвора KG 11 запам'яПри зчитуванні даних із комірки Z1 на шину товуючого транзистора ST11 ВІДПОВІДНИЙ виводу рядка AG1 подають напругу UI, а на шину сигналу KG 11 затвор запам'ятовуючого транзистора ST11 запису сигнал 0 Завдяки цьому вивід затвора KG1 виконаний у вигляді так званого "плаваючого заперебуває під заданим потенціалом UI, а транзиствора" Вивід затвора передавального транзистотор вибору АТ1 перебуває у провідному стані ра ТТ11 з'єднаний з шиною сигналу запису Стан запам'ятовуючого транзистора ST1 може SCHRX бути зчитаний шляхом подачі підхожої напруги на шину стовпця SP1 Вивід затвора розрядного транзистора ЕТ11 з'єднаний з шиною сигналу запису SCHRX ПерУ цьому режимі роботи шляхом подачі підхоший вивід каналу розрядного транзистора ЕТ11 жої напруги на шину стовпця SP2 може бути зчиз'єднаний з виводом затвора KG 11 запам'ятовуютаний стан запам'ятовуючого транзистора ST3 чого транзистора ST11, а другий вивід каналу розкомірки Z3, оскільки транзистор вибору АТЗ також рядного транзистора ЕТ11 безпосередньо з'єднаперебуває у провідному стані Стан комірок Z2 і Z4 ний з корпусом не залежить від стану комірок Z1 і Z3, оскільки вивід затвора KG2 постійно перебуває під заданим Відносно ШИНИ рядка AG1 запам'ятовуюча копотенціалом OB+Utp, переданим через відкритий мірка Z13 під'єднана паралельно комірці Z11 Корозрядний транзистор ЕТ2 мірка Z13 містить транзистор вибору АТ13, виконаний у вигляді звичайного n-канального польовоНа шини стовпців SP1 і SP2 як під час запису, го транзистора, і запам'ятовуючий транзистор так і під час зчитування подають ВІДПОВІДНІ станST13, виконаний у вигляді n-канального транзисдартні значення напруги тора з "плаваючим затвором" Перший вивід канаНа фіг 2 зображена схема іншого напівпровідлу транзистора вибору АТ13 з'єднаний з шиною никового запам'ятовуючого пристрою за винахостовпця SP2, а другий вивід каналу транзистора дом, виконаного на напівпровідниковій підкладинвибору АТ13 з'єднаний з першим виводом каналу ці Наведено лише фрагмент ЗП, що охоплює чозапам'ятовуючого транзистора ST3 Другий вивід тири запам'ятовуючі комірки Z11, Z12, Z13 і Z14 каналу запам'ятовуючого транзистора ST3 з'єднаУправління комірками Z11, Z12, Z13 і Z14 здійснюний зі спільною шиною Source Вивід затвора трається за допомогою двох шин рядків AG1, AG2 і нзистора вибору АТ13 під'єднаний паралельно до двох шин стовпців SP1, SP2 вводу затвора транзистора вибору АТ11 і з'єднаДля керування комірками Z11, Z12, Z13 і Z14 ний з шиною рядка AG1 Вивід затвора транзистослужить схема керування, що містить передавальра ST13 під'єднаний паралельно до вводу затвора ний транзистор ТТ11, розрядний транзистор ЕТ11, транзистора ST11 і з'єднаний з другим виводом передавальний транзистор ТТ12 і розрядний транканалу передавального транзистора ТТ11 Внаслізистор ЕТ12, керування якими здійснюється через док цього вивід затвора запам'ятовуючого транзишину сигналу запису SCHRX На шину сигналу стора ST13 також з'єднаний з першим виводом запису SCHRX подають перетворений у сигнал каналу розрядного транзистора ЕТ11 високої напруги логічний сигнал, що управляє процесом запису Крім того, схема керування місЗапам'ятовуюча комірка Z12 містить транзистить транзистор вибору блока ВТ11 і транзистор тор вибору АТ12 і запам'ятовуючий транзистор вибору блока ВТ12 Виводи затворів транзисторів ST12 Транзистор вибору АТ12 виконаний у виглявибору блока з'єднані з шиною сигналу вибору ді звичайного n-канального польового транзистоблока BLKN На шину вибору блока подають перера, а запам'ятовуючий транзистор ST12 виконаний творений у сигнал високої напруги логічний сигу вигляді n-канального транзистора з так званим нал, що управляє поблочним програмуванням "плаваючим затвором" Перший вивід каналу транзистора вибору АТ12 з'єднаний з шиною стовпця Транзистори передачі ТТ11 і ТТ12 і транзистоSP2, а другий вивід каналу транзистора вибору ри вибору блока ВТ11 і ВТ12 виготовлені як звиАТ12 з'єднаний з першим виводом каналу запам'ячайні польові транзистори з р-каналом 12 11 59400 товуючого транзистора ST12 Другий вивід каналу шин рядків AG1, AG2, виводів затворів KG11, KG запам'ятовуючого транзистора ST12 з'єднаний зі 12 і шини сигналу запису SCHRX для окремих респільною шиною Source жимів Вивід затвора транзистора вибору АТ12 з'єднаний з шиною рядка AG2 3 шиною рядка AG2 AG1 KG11 AG2 KG12 SCHRX з'єднаний також другий вивід каналу транзистора Стирання Up Up 0 O+Utp 0 вибору блока ВТ12 Другий вивід каналу передаЗапис Up 0 0 0 Up вального транзистора Т И 2 з'єднаний з першим Зчитування Ul Ul 0 O+Utp 0 виводом каналу транзистора вибору блока ВТ12, а перший вивід каналу передавального транзистора На шину сигналу вибору блока BLKN - в залеТТ12 з'єднаний з виводом затвора KG 12 запам'яжності від того, вибрано чи ні блок, у якому знахотовуючого транзистора ST12 При цьому ВІДПОВІДдяться комірки Z11-Z14, - подають напруги 0В НИЙ виводу затвора KG12 затвор запам'ятовуючо("вибрано") або Up ("не вибрано") го транзистора ST12 виконаний у вигляді так зваПри цьому напруга "Up" означає напругу проного "плаваючого затвора" грамування (наприклад, 18В), напруга "UI" означає Вивід затвора транзистора з'єднаний з шиною напругу зчитування, а напруга "Utp" означає додасигналу запису SCHRX Вивід затвора транзистора тне абсолютне значення порогової напруги рвибору блока ВТ12 з'єднаний з шиною вибору канального транзистора (близько 1В) блока BLKN Для подальшого опису принципу роботи наВивід затвора розрядного транзистора ЕТ12 півпровідникового ЗП приймається, що шина сигз'єднаний з шиною сигналу запису SCHRX Перналу запису SCHRX постійно перебуває під потенший вивід каналу розрядного транзистора ЕТ12 ціалом 0В, внаслідок чого канали транзисторів з'єднаний з виводом затвора KG12 запам'ятовуювибору блока перебувають у провідному стані і чого транзистора, а другий вивід каналу розрядносигнали, подані на шини рядків, передаються на го транзистора ЕТ12 безпосередньо з'єднаний з канали транзисторів передачі ТТ11 і ТТ12 корпусом Як видно із таблиці, при стиранні рядка запаВідносно ШИНИ рядка AG2 запам'ятовуюча ком'ятовуючого пристрою, в якому знаходиться комімірка Z14 під'єднана паралельно до запам'ятовурка Z11, на шину рядка AG1 подають напругу проючої комірки Z12 Запам'ятовуюча комірка Z14 грамування Up При цьому на перший вивід каналу містить транзистор вибору АТ14, виконаний за передавального транзистора ТТ11 також подаєтьзвичайною технологією у вигляді п-канального ся напруга програмування Up На шину сигналу польового транзистора, а також запам'ятовуючий запису SCHRX подають напругу 0В, завдяки чому транзистор ST14, виконаний у вигляді ппередавальний транзистор ТТ11 перебуває у проканального транзистора з "плаваючим затвором" відному стані, оскільки він є р-канальним транзисПерший вивід каналу транзистора вибору АТ14 тором І навпаки, розрядний транзистор ЕТ11 виз'єднаний з шиною стовпця SP2, а другий вивід конаний n-канальним, внаслідок чого подана на каналу транзистора вибору АТ14 з'єднаний з першину сигналу запису SCHRX напруга 0В, приклашим виводом каналу запам'ятовуючого транзистодена до його затвора, переводить його у непровідра ST14 Другий вивід каналу запам'ятовуючого ний стан Внаслідок цього на вивід затвора KG11 транзистора ST4 з'єднаний із спільною шиною подається напруга програмування Up, що перевоSource Вивід затвора транзистора вибору АТ14 дить "плаваючий затвор" запам'ятовуючого транпід'єднаний паралельно до виводу затвора транзистора ST11 у стан "дані стерто" зистора вибору АТ12 і з'єднаний з шиною рядка На комірку Z12 процеси на шині рядка AG1, а AG2 Вивід затвора запам'ятовуючого транзистора також на шині сигналу запису SCHRX не впливаST14 під'єднаний паралельно до виводу затвора ють, оскільки вивід затвора KG 12 постійно перезапам'ятовуючого транзистора ST12 і з'єднаний з буває під заданим потенціалом шини рядка AG2 другим виводом каналу передавального транзисOB+Utp тора ТТ12 Внаслідок цього вивід затвора запам'яОскільки комірки Z13 і Z14 відносно шин рядків товуючого транзистора ST14 також з'єднаний з AG1 і AG2 під'єднані паралельно коміркам Z11 і першим виводом каналу розрядного транзистора Z12, у них відбуваються ті ж процеси, що й у коміЕТ12 рках Z11 і Z12 Тому в режимі "стирання" здійснюЗапам'ятовуючі комірки Z11 і Z12 під'єднані ється стирання даних у всіх тих комірках, що припаралельно відносно шини стовпця SP1, а запаводяться у дію шиною рядка AG1 м'ятовуючі комірки Z13 і Z14 під'єднані паралельно Стирання даних у комірках Z12 і Z14 здійснювідносно шини стовпця SP2 ють аналогічно до комірок Z11 і Z13 Нижче пояснюються три режими запам'ятовуПри записі даних у комірку Z11 на шину рядка ючої комірки "стирання", "запис" і "зчитування" AG1 і на шину сигналу запису SCHRX подають для запам'ятовуючої комірки Z11 При цьому, в напругу Up Завдяки такому стану шини сигналу режимі "стирання" на шину стовпця SP1 не подазапису SCHRX, n-канальний розрядний транзистор ється жоден сигнал, оскільки для цього він не поЕТ1 стає провідним, а р-канальний передавальний трібен Лише при записі і при зчитуванні вмісту транзистор ТТ11 запирається Внаслідок цього на комірки Z11 на шину стовпця SP1 подається сигвиводі затвора KG 11 присутній потенціал корпусу, нал Одначе, в цьому описі цей процес детальніше а саме 0В Подачею потрібного сигналу на шину не відображено, оскільки для суті винаходу він має стовпця SP1 здійснюють запис інформації у западругорядне значення м'ятовуючий транзистор ST11, оскільки транзистор У наведеній нижче таблиці відображені стани вибору АТ11, на затвор якого подано сигнал Up, 14 13 59400 перебуває у провідному стані напруги на шину стовпця SP1 При цьому слід ВІДМІТИТИ, що процеси у комірці У цьому режимі роботи шляхом подачі підхоZ11 не впливають на комірку Z12, оскільки вивід жої напруги на шину стовпця SP2 може бути зчизатвора KG 12 через відкритий розрядний транзитаний стан запам'ятовуючого транзистора ST13 стор ЕТ12 постійно під'єднаний до заданої напруги комірки Z13, оскільки транзистор вибору АТ13 та0В (корпус) кож перебуває у провідному стані Стан комірок Z12 і Z14 не залежить від стану комірок Z11 і Z13, При зчитуванні даних із комірки Z11 на шину оскільки вивід затвора KG 12 постійно перебуває рядка AG1 подають напругу UI, а на шину сигналу під заданим потенціалом OB+Utp, переданим чезапису SCHRX - сигнал 0 Завдяки цьому вивід рез відкритий розрядний транзистор ЕТ12 затвора KG11 перебуває під заданим потенціалом UI, а транзистор вибору АТ11 перебуває у провідНа шини стовпців SP1 і SP2 як під час запису, ному стані Стан запам'ятовуючого транзистора так і під час зчитування подають ВІДПОВІДНІ станST11 може бути зчитаний шляхом подачі підхожої дартні значення напруги ФІГ. 1 ФІГ. 2 SP2 Source SCHfiX Комп'ютерна верстка О Воробей Підписано до друку 06 10 2003 Тираж39 прим Міністерство освіти і науки України Державний департамент інтелектуальної власності, Львівська площа, 8, м Київ, МСП, 04655, Україна ТОВ "Міжнародний науковий комітет", вул Артема, 77, м Київ, 04050, Україна

ДивитисяДодаткова інформація

Назва патенту англійськоюSemiconductor memory with nonvolatile dual-transistor memory cells

Назва патенту російськоюПолупроводниковое запоминающее устройство с энергонезависимыми двухтранзисторными запоминающими элементами

МПК / Мітки

МПК: G11C 16/04

Мітки: запам'ятовуючими, двотранзисторними, енергонезалежними, комірками, запам'ятовуючий, напівпровідниковий, пристрій

Код посилання

<a href="https://ua.patents.su/7-59400-napivprovidnikovijj-zapamyatovuyuchijj-pristrijj-z-energonezalezhnimi-dvotranzistornimi-zapamyatovuyuchimi-komirkami.html" target="_blank" rel="follow" title="База патентів України">Напівпровідниковий запам’ятовуючий пристрій з енергонезалежними двотранзисторними запам’ятовуючими комірками</a>

Попередній патент: Спосіб мікрохвильової терапії

Наступний патент: Вимірювальна секція витратоміра змінного перепаду тиску

Випадковий патент: Механізм хитання кристалізатора