Інвертор квазісинусоїдальної напруги

Формула / Реферат

1. Інвертор квазісинусоїдальної напруги, який містить імпульсний стабілізатор напруги з випрямлячами, блок керування, двотактні вихідні інвертори, вихідний трансформатор, вихідні ланцюги блока керування з'єднані з відповідними входами двотактних вихідних інверторів, виходи яких навантажені на крайні виводи обмоток вихідного трансформатора, середні виводи якого з'єднані з виходами випрямлячів, входи яких підключені до відповідних виходів імпульсного стабілізатора напруги, який відрізняється тим, що блок керування складається з формувача мережних імпульсів напруги, блока генерації частот і блока квантування за часом, входи якого з'єднані з виходами блока генерації частот, вхід якого з'єднаний з виходом формувача мережних імпульсів напруги, вхід якого підключений до мережі.

2. Інвертор квазісинусоїдальної напруги за п. 1, який відрізняється тим, що формувач мережних імпульсів напруги містить блок безтрансформаторного мостового випрямляча, вхід перемінної напруги якого з'єднаний через гасильні конденсатори з мережею, а вихід постійної напруги з'єднаний з паралельно включеними конденсатором і стабілітроном, при цьому позитивний полюс мостового випрямляча з'єднаний з резисторним подільником напруги, що з'єднаний із входом, який інвертує, компаратора, виконаного на операційному підсилювачі, а прямий вхід компаратора з'єднаний із симетричним діодно-резистивним обмежником, виконаним на двох резисторах і двох паралельно включених діодах, при цьому вихід компаратора через оптронну пару з'єднаний з логічним елементом Виключне АБО, причому діоди діодно-резистивного обмежника включені між прямим і інверсним входами компаратора, а резисторний подільник напруги містить потенціометр, включений між двома резисторами, при цьому движок потенціометра з'єднаний з інверсним входом компаратора.

3. Інвертор квазісинусоїдальної напруги за п. 1, який відрізняється тим, що блок генерації частот містить задавальний генератор, виконаний у вигляді функціонального генератора, що складається з генератора трикутних імпульсів, виконаного за схемою інтегратора, і синхронізованого з ним генератора прямокутних імпульсів, виконаного за схемою компаратора, причому блок генерації частот містить n блоків, з'єднаних послідовно один з одним, а кожний з n блоків містить додатково вузол контролю фази, причому вхідна напруга надходить на вхід, що інвертує, генератора трикутних імпульсів і на перший вхід вузла контролю фази, на другий вхід якого надходить вихідна напруга генератора прямокутних імпульсів, а вихід вузла контролю фази з'єднаний із входом наступного n блока, крім того, вузол контролю фази реалізований на логічному елементі Виключне АБО, а генератори трикутних і прямокутних імпульсів реалізовані на здвоєному операційному підсилювачі, при цьому блок генерації частот має вихідні фіксовані частоти – 50 Гц, 800 Гц і 1600 Гц, синфазні з частотою напруги мережi.

4. Інвертор квазісинусоїдальної напруги за п. 1, який відрізняється тим, що блок квантування за часом містить блок початкової установки, що виконаний у вигляді логічного інвертора, на вході якого встановлений RC-ланцюжок, блок синхронізації, виконаний у вигляді двох логічних інверторів, вихід одного через RC-ланцюжок підключений у першому вході логічного елемента І, на другий вхід якого подається напруга мережі, розподільник імпульсів, виконаний у вигляді лічильника-дешифратора на дев'ять виходів, дешифратор, виконаний шістнадцятиканальним, формувач початкової ділянки квазісинусоїдального сигналу, виконаний у вигляді логічних елементів, входи яких з'єднані з виходами блока генерації частоти, вихідний безконтактний перемикач напівперіодів квазісиносоїдального сигналу, виконаний на 16-ти 2-входових елементах Виключне І.

5. Інвертор квазісинусоїдальної напруги за п. 1, який відрізняється тим, що пристрій містить вісім двотактних вихідних інверторів, підключених до відповідних обмоток вихідного трансформатора.

Текст

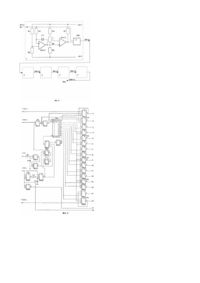

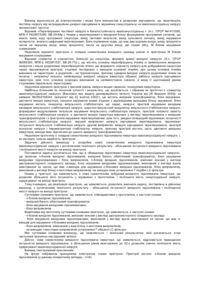

Винахід відноситься до електротехніки і може бути використай в джерелах харчування, що перетворюють постійну напругу від нетрадиційних джерел харчування в перемінну синусоїдальну чи квазісинусоїдальну напругу промислової частоти. Відомий «Інвертор зі східчастою, близької до синусоїди, формою кривої вихідної напруги» (А.с. СРСР №565365, МПК-2Н02М7/537, БВ-26-77p.), якій містить основний преобразуючій осередок із прямокутною вихідною напругою і кілька додаткових преобразуючіх осередків, що формують східчасту напругу для добудування синусоїди через підсумовуючий пристрій, з'єднана послідовно з виходом основного осередку, при цьому основний осередок виконаний на тиристорах, а додаткові - на транзисторах, причому сумарна вихідна напруга додаткових осередків на початку і наприкінці кожного напівперіоду вихідної напруги інвертора обраної великим напруги харчування інвертора, крім того, основний осередок виконаний за напівмостовою схемою, а вихід його шунтован двома з'єднаними паралельно тиристорами. Недоліком відомого пристрою є високий рівень напруги вищих гармонік, генеруємих інвертором. Найбільш близьким по технічній сутності і результату, який досягається, і обраним як прототип є «Інвертор квазісинусоїдальної напруги» (Висновок про видачу деклараційного патенту України за заявкою №2002108344, пріоритет від 22 жовтня 2002p.), якій містить вихідний трансформатор, блок керування, двотактні вихідні інвертори, ланцюги керування якими з'єднані з відповідними виходами блоку керування, блок керування містить генератор, що задає, імпульсного стабілізатора напруги, пристрій керування вихідним каскадом імпульсного стабілізатора напруги, широтно-імпульсний модулятор імпульсного стабілізатора напруги, формувач модульованих імпульсів керування імпульсного стабілізатора напруги, пристрій струмового захисту імпульсного стабілізатора напруги, а двотактні вихідні інвертори виконані у вигляді перетворювача з вихідним трансформатором і з пристроєм керування перетворювачем, крім того, уведені попередній підсилювач потужності імпульсного стабілізатора напруги, перший випрямляч напруги харчування перетворювача, підсилювач потужності імпульсного стабілізатора напруги, другий випрямляч напруги харчування перетворювача, пристрій контролю напруги і параметричний стабілізатор напруги, причому пристрій містить шість двотактні вихідних інверторів, виходи яких підключені до одного вихідного трансформатора. Недоліком прототипу є складна схемотехника пристрою. Задачею дійсного винаходу є розробка нового інвертора квазісинусоїдальної напруги з досягненням технічного результату - спрощення схемотехники пристрої і підвищення надійності роботи пристрою в цілому. Поставлена задача досягається тим, що в «Інверторі квазісинусоїдальної напруги», який містить імпульсний стабілізатор напруги з випрямлячами, блок керування, двотактні вихідні інвертори, вихідний трансформатор, вихідні ланцюги блоку керування з'єднані з відповідними входами двотактних вихідних інверторів, виходи яких навантажені на крайні виводи обмоток вихідного трансформатора, середні виводи якого з'єднані з виходами випрямлячів, входи яких підключені до відповідних виходів імпульсного стабілізатора напруги, блок керування складається з формувача мережних імпульсів напруги, блоку генерації частот і блоку квантування за часом, входи якого з'єднані з виходами блоку генерації частот, вхід якого з'єднаний з виходом формувача мережних імпульсів напруги, вхід якого підключений до мережі, крім того, формувач мережних імпульсів напруги містить блок безстрансформаторного мостового випрямляча, вхід перемінної напруги якого з'єднаний через конденсатори, що гасять, з мережею, а вихід постійної напруги з'єднаний з паралельно включеними конденсатором і стабілітроном, при цьому позитивний полюс мостового випрямляча з'єднаний з резисторним дільником напруги, що з'єднаний із входом, що інвертує, компаратора, виконаного на операційному підсилювачі, а прямий вхід компаратора з'єднаний із симетричним діодно-резистивним обмежником, виконаним на двох резисторах і двох паралельно включених діодах, при цьому вихід компаратора через оптронную пару з'єднаний з логічним елементом «виключне «АБО», причому діоди діодно-резистивного обмежника включені між прямим і інверсним входами компаратора, а резисторний дільник напруги містить потенціометр, включений між двома резисторами, при цьому движок потенціометра з'єднаний з інверсним входом компаратора, блок генерації частот містить генератор, що задає, виконаний у вигляді функціонального генератора, що складає з генератора трикутних імпульсів, виконаного за схемою інтегратора, і синхронізованого з ним генератора прямокутних імпульсів, виконаного за схемою компаратора, причому блок генерації частоти містить n-блоків, з'єднаних послідовно один з одним, а кожний з n-блоків містить додатково вузол контролю фази, причому вхідна напруга надходить на вхід генератора, що інвертує, трикутних імпульсів і на перший вхід вузла контролю фази, на другий вхід якого надходить вихідна напруга генератора прямокутних імпульсів, а вихід вузла контролю фази з'єднаний із входом наступного n-блоку, крім того, вузол контролю фази реалізований на логічному елементі «виключне «АБО», а генератори трикутних і прямокутних імпульсів реалізовані на здвоєному операційному підсилювачі, при цьому блок генерації частоти має вихідні фіксовані частоти - 50Гц, 800Гц і 1600Гц, синфазні з частотою напруги мережі, при цьому блок квантування за часом містить блок початкової установки, виконаний у вигляді логічного інвертора, на вході якого встановлений RC-ланцюжок, блок синхронізації, виконаний у вигляді двох логічних інверторів, вихід одного через RC-ланцюжок підключений до першого входу логічного елемента «І», на другий вхід якого подається напруга мережі, розподільник імпульсів, виконаний у вигляді лічильника-дешифратора на дев'ять виходів, дешифратор, виконаний шістнадцятиканальним, формувач початкової ділянки квазісинусоїдального сигналу, виконаний у вигляді логічних елементів, входи яких з'єднані з виходами блоку генерації частоти, вихідний безконтактний перемикач напівперіодів квазісинусоїдального сигналу, виконаний на 16-ти 2-х входових елементах «виключне «І», а пристрій містить вісім двотактних вихідних інверторів, підключених до відповідних обмоток вихідного трансформатора. Новим у пристрої, що заявляється, є нова схемотехника побудови інвертора, що дозволяє значно спростити пристрій по прототипі і підвищити надійність його роботи. Тому очевидно, що реалізація пристрою, що заявляється, дозволить виконати задачу, поставлену в дійсному винаході, з досягненням технічного результату - спрощення схемотехники пристрою і підвищення надійності роботи пристрою в цілому. Суттєвими ознаками пристрою, що заявляється, співпадаючими з прототипом, є наступні ознаки: - імпульсний стабілізатор напруги з випрямлячами; - блок керування; двотактні вихідні інвертори; вихідний трансформатор; - вихідні ланцюги блоку керування з'єднані з відповідними входами двотактних вихідних інверторів; - виходи двотактних вихідних інверторів навантажені на крайні виводи обмоток вихідного трансформатора; - середні виводи вихідного трансформатора з'єднані з виходами випрямлячів; - входи випрямлячів підключені до відповідним виходам імпульсного стабілізатора напруги. Відмітними від прототипу суттєвими ознаками пристрою, що заявляється, є наступні ознаки: - блок керування складається з формувача мережних імпульсів напруги, блоку генерації частоти і блоку квантування за часом; - входи блоку квантування за часом з'єднані з виходами блоку генерації частоти; - вхід блоку генерації частоти з'єднаний з виходом формувача мережних імпульсів напруги; - вхід формувача мережних імпульсів напруги підключений до мережі. Приватними відмітними від прототипу суттєвими ознаками пристрою, що заявляється, є наступні ознаки: - формувач мережних імпульсів напруги містить блок безтрансформаторного мостового випрямляча; - вхід перемінної напруги безтрансформаторного мостового випрямляча з'єднаний через конденсатори, що гасять, з мережею, а вихід постійної напруги з'єднаний з паралельно включеними конденсатором і стабілітроном; - позитивний полюс мостового випрямляча з'єднаний з резисторным дільником напруги; - резисторный дільник напруги з'єднаний із входом, що інвертує, компаратора; компаратор виконаний на операційному підсилювачі; прямий вхід компаратора з'єднаний із симетричним діодно-резистивним обмежником; - симетричний діодно-резистивний обмежник виконаний на двох резисторах і двох паралельно включених діодах; - вихід компаратора через оптронную пару з'єднаний з логічним елементом «виключне «АБО»; - діоди діодно-резистивного обмежника включені між прямим і інверсним входами компаратора; - резисторный дільник напруги містить потенціометр, включений між двома резисторами, при цьому движок потенціометра з'єднаний з інверсним входом компаратора; - блок генерації частоти містить генератор, що задає, виконаний у вигляді функціонального генератора, що складає з генератора трикутних імпульсів, виконаного за схемою інтегратора, і синхронізованого з ним генератора прямокутних імпульсів, виконаного за схемою компаратора; - блок генерації частоти містить n-блоків, з'єднаних послідовно один з одним; кожний з n-блоків містить додатково вузол контролю фази; - вхідна напруга надходить на вхід генератора, що інвертує, трикутних імпульсів і на перший вхід вузла контролю фази, на другий вхід якого надходить вихідна напруга генератора прямокутних імпульсів, а вихід вузла контролю фази з'єднаний із входом наступного n-блоку; - вузол контролю фази реалізований на логічному елементі «виключне «АБО»; генератори трикутних і прямокутних імпульсів реалізовані на здвоєному операційному підсилювачі; - блок генерації частоти має вихідні фіксовані частоти - 50Гц, 800Гц і 1600Гц, синфазні з частотою напруги мережі; - блок квантування за часом містить блок початкової установки, виконаний у вигляді логічного інвертора, на вході якого встановлений RC-ланцюжок; - блок синхронізації, виконаний у вигляді двох логічних інверторів, вихід одного через RC-ланцюжок підключений у першому входу логічного елемента «І», на другий вхід якого подається напруга мережі; - розподільник імпульсів, виконаний у вигляді лічильника-дешифратора на дев'ять виходів; - дешифратор, виконаний шестнадцатиканальним; - формувач початкової ділянки квазісинусоїдального сигналу, виконаний у вигляді логічних елементів, входи яких з'єднані з виходами блоку генерації частоти; вихідний безконтактний перемикач напівперіодів квазісинусоїдального сигналу, виконаний на 16-ти 2-х входових елементах «виключне «І»; - пристрій містить вісім двотактних вихідних інверторів, підключених до відповідних обмоток вихідного трансформатора. Між суттєвими ознаками винаходу, що заявляється, і технічним результатом, що досягається, існує наступний причинно-наслідковий зв'язок. Дійсно, нова схемотехника інвертора, що заявляється, відрізняється простотою і надійністю, що дозволяє підвищити якість квазісинусоїдальної напруги, одержуваної на виході пристрою, зменшити массо-габаритними показники пристрою, що заявляється, і підвищити надійність роботи його в порівнянні з прототипом. Винахід ілюстрований кресленнями. На фіг.1 зображена структурна блок-схема пристрою; на фіг.2 показані структурна і принципова схеми блоку генерації частот; на фіг.3 і фіг.4 показана принципова електрична схема блоку квантування за часом; на фіг.5 показана принципова електрична схема формувача мережних імпульсів напруги. Структурна схема пристрою складається з наступних функціональних блоків: Блок керування - складається з формувача мережних імпульсів напруги, блоку генерації частот і блоку квантування за часом. Формувач мережних імпульсів напруги - призначений для одержання прямокутних імпульсів, що відповідають частоті і фазі напруги мережи (далі по тексту -ФМІН). Блок генерації частот - призначений для одержання частот, кратних і синфазних частоті живильної мережі (далі по тексту - БГЧ). Блок квантування за часом - далі по тексту - БКзЧ - призначений для одержання 32-х імпульсів керування блоками 1-8, що здійснюють формування квазісинусоїдальної напруги, що вірогідно відображає синусоїдальну форму сигналу. Блоки 1-8 - вісім двотактних вихідних інверторів. Імпульсний стабілізатор напруги - умовно не показаний - перетворюєть постійну напругу 40-90 В від нетрадиційного джерела харчування (далі по тексту - НДХ), наприклад, від сонячних батарей, у постійну напругу 15 В для харчування схеми керування інвертора. Крім того, імпульсний стабілізатор напруги (далі по тексту - ІСН) перетворюєть постійну напругу від НДХ у вісім рівнів перемінної напруги для харчування блоків 1-8 через блок мостових випрямлячів (далі по тексту - БМВ). Блок мостових випрямлячів - умовно не показаний - перетворюєть вісім рівнів перемінної напруги з вихідного трансформатора ІСН у вісім рівнів постійної напруги для харчування блоків 1-8. Вихідний трансформатор - багатообмотковий трансформатор, що має вісім обмоток з виводами від середньої крапки для формування квазісинусоїдальної напруги. Розглянемо роботу кожного блоку пристрою, що заявляється, причому нумерація елементів кожного блоку виконана незалежної від нумерації інших елементів інших блоків. Формувач мережних імпульсів напруги. ФМІН (див. фіг.5) призначений для одержання прямокутних імпульсів, що відповідають частоті і фазі напруги мережи, і зібраний на елементах: конденсаторах С1 і С2, мостовому випрямлячі VD1-VD4, стабілітроні VD5 і конденсаторі фільтра С3, параметричному стабілізаторі VD5 на стабілітроні 2С527А (напруга - 27В), на компараторі DA1, оптоєлектронной парі VHS 1 (оптронном перетворювачі) і логічному елементі «виключне «АБО» DD1. Для оптимального режиму роботи компаратора DA1 формувача його напруга харчування повинен бути прямокутної і симетричний, який одержують за допомогою двостороннього перетворювача (обмежника), виконаного на елементах - С1,С2, R1, R2, VD6, VD7. Синусоїдальна перемінна напруга мережі 220 В надходить на реактивний баластовий опір, виконаний у вигляді конденсаторів С1 і С2, за допомогою яких напруга харчування формувача симметруєтся відносно «0» синусоїдальної напруги мережі, тому що С1=С2, і на двосторонній обмежник напруги мережі, що симметруєтся відносно «0» синусоїдальної напруги резисторами R1 і R2, тому що R1=R2. На С1 і С2 не відбувається розсіювання енергії. Випрямлена за допомогою мостової схеми на діодах VD1-VD4 напруга стабілізується за допомогою стабілітрона VD5. Джерело харчування компаратора DA1 формувача симетричне щодо прямокутних імпульсів, сформованих R1, R2, VD6, VD7, відносно «мнимої» нульові шини формувача на операційному підсилювачі DA1. VD6, VD7 призначені для двостороннього обмежника, щоб сформувати імпульси із синусоїди. Напруга, рівна половині напруги джерела харчування надходить на інверсний вхід DA1, на прямий вхід якого надходять прямокутні імпульси, сформовані двостороннім симетричним обмежником R1, R2, VD6, VD7. Синусоїдальна напруга на DA1 надходить з мережі через обмежник VD6, VD7. Штучна середня крапка харчування мікросхеми DA1 створена резисторами R3, R4 і R5 і служить для забезпечення роботи DA1 як у режимі посилення, так і в режимі компаратора. За допомогою підгінного резистора R4 виконується точний розподіл на дві стабілізовані напруги. На виході DA1, реалізованому на мікросхемі K140YD6A, присутні прямокутні імпульси амплітудою ~26В відносно «-» джерела харчування, що через оптронную пару VHS 1, реалізовану на 30D129A, надходять на вхід DD1. Через буферний резистор R6 ці імпульси надходять на світлодіод оптронной пари, що розв'язує напругу мережі ~220В перемінного струму з входом формувача тривалості періоду імпульсів мережі. Формувач тривалості періоду імпульсів мережі зібраний на DD1. Узгодження фотодіода оптронной пари і входу формувача виконується схемою: R6 - навантаження фотодіода, фото діод оптронного перетворювача і DD1, що виконує функцію інвертора. Початкова установка формувача здійснюється через логічний елемент «виключне «АБО» DD1, що працює в режимі негативної логіки, що дозволяє скоротити кількість елементів схеми. При роботі формувача на виході DD1 присутні прямокутні імпульси, сфазировані з напругою мережі. Блок генерації частот. На фіг.2 пунктирними лініями зображена функціональна схема БГЧ, а суцільними лініями показана принципова електрична схема БГЧ, причому показаний 9 варіант БГЧ, у якому n=5, вхідна напруга має частоту f=50Гц, а вихідна синфазна напруга має частоту f=1600Гц. Структурна схема БГЧ складається з n-блоків, з'єднаних послідовно один з одним. Частота вихідної синфазної напруги кожного наступного блоку удвічі вище частоти вхідної напруги і кратна частоті живильної мережі. Кожний з n-блоків складається з функціонального генератора і вузла контролю фази. Функціональний генератор є релаксационной системою, що складається з інтегратора DA1-1 і компаратора DA1-2. Постійна часу інтегратора і, отже, частота генерируємих коливань залежать від ємності конденсатора С1 і резистора R3, включених у ланцюг негативного зворотнього зв'язку. Напруга з виходу інтегратора DA1-1 подається на вхід, що інвертує, двухполярного компаратора DA1-2 і, по досягненні порога спрацьовування DA1-2, полярність напруги на виході компаратора DA1-2 змінюється на протилежну, і цикл повторюється. Плавне регулювання частоти здійснюється резистором R5. Отже, якщо на виході компаратора DA1 -2 є присутнім позитивна напівхвиля, то на виході інтегратора DA1-1 наростання фронту трикутного імпульсу напруги, а при переключенні компаратора DA1-2 - на виході інтегратора DA1-1 є присутнім негативний спад трикутного імпульсу. Вхідна напруга живильної мережі надходить на вхід інтегратора DA1-1, на виході якого ми маємо калібровані імпульси трикутної форми, зрушені на 90° щодо вхідних. Ці трикутні імпульси надходять на вхід компаратора, що інвертує, DA1-2. Інтегратор DA1-1 і компаратор DA1-2 виконані на мікросхемі K574YD2 (здвоєний операційний підсилювач). На мікросхемі DD1 реалізованийвузол контролю фази, виконаний на логічному елементі «виключне «АБО». Вхідна напруга живильної мережі також надходить на вхід мікросхеми DD1, другий вхід якої з'єднаний з виходом DA1-2. На виході DD1 присутні імпульси подвоєної частоти, тобто 100Гц. Таким чином, на базі інтегратора DA1-1, компаратора DA1-2 і вузла контролю фази DD1 побудований підсумовуючий синфазний формувач і помножувач прямокутних імпульсів, що формує імпульси від 50Гц до 1600Гц (при числі блоків n=5). При цьому варто особливо підкреслити, що отримані на виході n-блоків частоти синфазні частоті живильної мережі, що важливо при побудові інверторів квазісинусоїдальної напруги, вихідна напруга яких по частоті і фазі повинна завжди збігатися з частотою і фазою напруги живильної мережі. Блок квантування за часом. На фіг.3 і фіг.4 зображена принципова електрична схема БКзЧ. Для того, щоб одержати квазісинусоїдальну напругу, що вірогідно відображає синусоїдальну форму сигналу, необхідно виконати квантування за рівнем і за часом, тобто необхідно одержати квантування по 32-м рівнях напруги і за часом. Для одержання цих рівнів квантування на схему БКзЧ необхідно подати три напруги різних частот, синхронні з частотою напруги мережі, а саме: f=50Гц - для синхронізації по фазі вихідного сигналу перетворювача, f=800Гц і 1600Гц - щоб одержати початкову 1/4 і кінцеву 3/4 частина синусоїди тимчасового інтервалу для квантування за часом. БГЧ формує напруги цих трьох частот, синхронні з частотою напруги мережі. Сигнали з БГЧ із частотами f=50Гц, f=800Гц, f=1600Гц надходять на входи мікросхем DD2-1, DD2-3, DD3-3, DD1-1, DD5-1, DD9-2 відповідно. Напруга 15В с ІСН надходить на блок початкової установки, виконаний у вигляді логічного інвертора DD1-3, на вході якого встановлений RC-ланцюжок, виконаний на резисторі R1 і конденсаторі С1. З виходу DD1-3 сигнал надходить на інвертор DD1-4. Інвертори DD1-3 і DD1-4 служать для початкової установки при подачі харчування на пристрій. Вхідний дільник-формувач виконаний у вигляді тригера на мікросхемах DD3-1 і DD3-2, що виконують роль комутатора. Блок синхронізації виконаний у вигляді двох логічних інверторів на мікросхемах DD2-1 і DD2-3, причому вихід DD2-1 через RC-ланцюжок на резисторі R2 і конденсаторі С2 підключений до першого входу логічного елемента «І» на мікросхемі DD2-3, на другий вхід якого подається напруга мережі частотою 50Гц. Мікросхеми DD2 і DD3 призначені для синхронізації з напругою мережі напруги перетворювача, до складу якого входить БКзЧ. Розподільник імпульсів виконаний у вигляді лічильника-дешифратора на дев'ять виходів і реалізований на мікросхемі DD4. Дешифратор виконаний шістнадцятиканальним і реалізований на мікросхемах DD5-DD9,DD10-DD13. Формувач початкової ділянки квазісинусоїдального сигналу виконаний у вигляді логічних елементів DD5-1, DD5-2 і DD9-1, DD9-2, на входи яких подають чотири частотних сигнали, синфазних з частотою сіткової напруги f=800Гц і 1600Гц (прямої й інверсний сигнали), а також сигнали з виходів «0» і «7» лічильника-дешифратора DD4. Виходи DD10...DD3 приєднані до входів DD14...DD17 - комутатору напівперіодів квазісинусоїдального сигналу з частотою мережі. Виходи DD14...DD17 с 1 - го по 16 - тий подаються на бази транзисторів VT1 блоків 1-8, що входять до складу вихідних підсилювачів інвертора, що дозволяє одержати потужність вихідного квазісинусоїдального сигналу до 1квт. БКзЧпрацює в такий спосіб. При подачі напруги харчування на пристрій відбувається початкова установка вхідного дільника-формувача на мікросхемі DD3-1 і DD3-2, що встановлює в нуль лічильник-дешифратор на мікросхемі DD4. Від БГЧ імпульси з частотами f=50Гц, f=800Гц, f=1600Гц надходять на входи БКзЧ, на виході якого формуються 32 імпульсу напруги, послідовно розподілених у часі. Ці імпульси напруги по черзі надходять на входи блоків 1-8 вихідних підсилювачів інвертора, що по черзі формують чергову сходинку квазісинусоїдальної напруги. Крім того, важливою обставиною, що поліпшує якість напруги на виході інвертора, є те, що початкові ділянки квазісинусоїдального сигналу формуються на підвищеній частоті, тобто число сходинок на початку і наприкінці напівхвилі квазісинусоїдального сигналу значно більше, ніж у середині напівхвилі. Це дозволяє більш точно відтворити на виході інвертора синусоїдальну напругу. А тому що всі частотні імпульси, подавані на пристрій, синхронізовані з частотою живильної мережі, то вихідна квазісинусоїдальна напруга також синфазна частоті живильної мережі, тобто частота і фаза вихідної квазісинусоїдальної напруги точно відповідають частоті і фазі напруги мережі. Блоки 1-8. На фіг.1 показана принципова електрична схема блоку 1 - інші блоки 2-8 -аналогічні. Пристрій містить n-блоків вихідних підсилювачів (у даному конкретному випадку - n=8). Кожний з n-блоків вихідних підсилювачів містить дві аналогічні схеми, виконані у вигляді двухтранзисторних складених каскадів - на транзисторах VT1 (типу КТ 972А), VT2 (типу КТ 812А) і резисторах R1-R4 і на транзисторах VT3 (типу КТ 972А) , VT4 (типу КТ 812А) і резисторах R5-R8. На бази транзисторів кожного з n-блоків надходять керуючі сигнали з БКзЧ. Колектори вихідних транзисторів кожного з n-блоків підключені до своєї n-обмотки багатообмоткового трансформатора TV1, виконаних із середнімі виводами. На середні виводи кожної з n-обмоток трансформатора TV1 подається своя напруга від БМВ, на виходах яких установлені Г-образні LC-фільтри. Схема БМВ умовно не приведена в даному описі. Пристрій, що заявляється, працює в такий спосіб. Для квантування за рівнем і за часом необхідне одержання 1/16 напівхвилі, тобто 32 квантування за часом 32 рівнів напруги напівхвилі синусоїди. Ці сигнали квантування надходять із БКзЧ на бази транзисторів кожного з n-блоків вихідного підсилювача в строго визначені моменти часу. Прямокутні синфазні з мережею імпульси з ФМІН надходять на БГЧ, де вони перетворяться в синфазні з мережею імпульси з частотою від 50Гц до 1600Гц, а далі надходять через комутатор на входи лічильникадешифратора. Потім на елементах БКзЧ формуються імпульси керування блоками 1-8 вихідного підсилювача інвертора квазісинусоїдальної напруги. Далі ці імпульси надходять на комутатор напівперіодів квазісинусоїдального сигналу, з виходу якого вони подаються на бази силових транзисторів блоків 1-8 вихідного підсилювача. Колектори вихідних транзисторів блоків 1-8 підключені до обмоток силового трансформатора TV1, що мають по трьох виводу кожна. До першого і третього виводу цих обмоток підключені колектори вихідних транзисторів блоків 1-8, а на середній (другий) вивод подається постійна напруга з виходів БМВ - від +60V до +240V. При формуванні квазісинусоїдального сигналу імпульси з БКзЧ надходять на базу транзистора VT1 блоку 8, що відкривається і відмикає транзистор VT2. Відкритий транзистор VT2 підключає перший вивід обмотки 8 трансформатора TV1 до мінуса постійної напруги 60 V. При цьому по напівобмотці І обмотки 8 протікає струм, що формує першу сходинку позитивної напівхвилі квазісинусоїдальної напруги. Потім із БКзЧ надходять по черзі сигнали на бази транзисторів VT1 блоків 7-1, що по черзі відкриваються і відмикають транзистори VT2 своїх блоків 7-1. По черзі відкриті транзистори VT2 блоків 7-1 підключають перші виводи обмоток 7-1 трансформатора TV1 до мінуса постійної напруги 110V, 160V, 190V, 210V, 225V, 234V і 240V. У такий спосіб за вісім тактів роботи БКзЧ формується наростаючий фронт позитивної напівхвилі квазісинусоїдальної напруги. Потім із БКзЧ, вже в зворотному порядку, подаються сигнали на бази транзисторів VT1 блоків 1-8, що по черзі відкриваються і відмикають транзистори VT2 своїх блоків 1-8 По черзі відкриті транзистори VT2 блоків 1-8 підключають треті виводи обмоток 1-8 трансформатора TV1 до мінуса постійної напруги 240V, 234V, 225V, 210V, 190V, 160V, 110V і 60V. У такий спосіб за вісім тактів роботи БКзЧ формується спадаючий фронт позитивної напівхвилі квазісинусоїдальної напруги. Аналогічно відбувається робота пристрою при формуванні негативної напівхвилі квазісинусоїдальної напруги. Таким чином, на підставі вищевикладеного можна зробити висновок, що задача, поставлена в дійсному винаході - розробка нового інвертора квазісинусоїдальної напруги - виконана з досягненням технічного результату - спрощенням схемотехники пристрою і підвищенням надійності роботи пристрою в цілому.

ДивитисяДодаткова інформація

Назва патенту англійськоюInverter with output quasi-sinusoidal voltage

Автори англійськоюBekirov Eskender Alimovych

Назва патенту російськоюИнвертор с выходным квазисинусоидальным напряжением

Автори російськоюБекиров Эскендер Алимович

МПК / Мітки

МПК: H02M 7/539

Мітки: інвертор, напруги, квазісинусоїдальної

Код посилання

<a href="https://ua.patents.su/7-64388-invertor-kvazisinusodalno-naprugi.html" target="_blank" rel="follow" title="База патентів України">Інвертор квазісинусоїдальної напруги</a>

Попередній патент: Пероральна фармацевтична композиція на основі сполуки, що має антигрибкову активність, і спосіб її одержання

Наступний патент: Мотовило жниварки

Випадковий патент: Спосіб седативного впливу на пацієнта і трансдермальна терапевтична система