Пристрій для знаходження катастрофічних відмов в базових схемах пам’яті на елементах і-ні

Номер патенту: 88895

Опубліковано: 10.04.2014

Автори: Осадча Ганна Андрієвна, Москвін Максим Вікторович, Мараховський Леонід Федорович, Москвін Вадим Вікторович

Формула / Реферат

Пристрій для знаходження катастрофічних відмов в базових схемах пам'яті, що містить ![]() елементів І-НІ, один із входів елементів з'єднаний з вхідною шиною установки схеми пам'яті в один із станів, коли схеми пам'яті розбити на

елементів І-НІ, один із входів елементів з'єднаний з вхідною шиною установки схеми пам'яті в один із станів, коли схеми пам'яті розбити на ![]() груп, а коли схеми пам'яті розбити на

груп, а коли схеми пам'яті розбити на ![]() груп, то другий із входів елементи І-НІ елементів з'єднаний з вхідною шиною збереження станів схеми пам'яті, групи містять довільну кількість

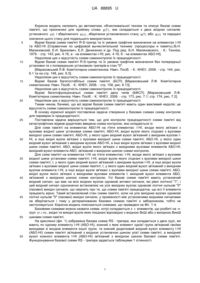

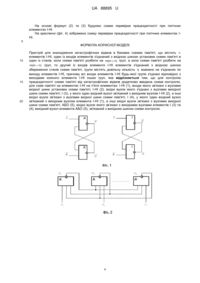

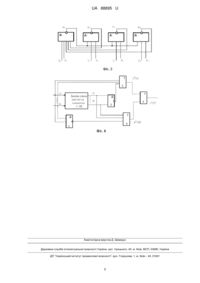

груп, то другий із входів елементи І-НІ елементів з'єднаний з вхідною шиною збереження станів схеми пам'яті, групи містять довільну кількість ![]() взаємно не з'єднаних по виходу елементів І-НІ, причому всі входи елементів І-НІ будь-якої групи з'єднані відповідно з виходами кожного елемента І-НІ інших груп, яка відрізняється тим, що для контролю працездатності схеми пам'яті від катастрофічних відмов додатково введена схема контролю, для схем пам'яті на елементах І-НІ на п'яти елементах: І-НІ (1), входи якого зв'язані з вузлами вхідної шини установки схеми пам'яті; І-НІ (2), вхідні вузли якого з'єднані з вузлами вихідної шини схеми пам'яті; І (3), у якого один вхідний вузол зв'язаний з вихідним вузлом І-НІ (2), а інші вхідні вузли зв'язані з вузлами вхідної шини схеми пам'яті; І (4), у якого один вхідний вузол зв'язаний з вихідним вузлом елемента І-НІ (1), а інші вхідні вузли зв'язані з вузлами вихідної шини схеми пам'яті; АБО (5), вхідні вузли якого зв'язані з вихідними вузлами елементів І (3) та (4); вихідний вузол елемента АБО (5), зв'язаний з вихідною шиною схеми контролю.

взаємно не з'єднаних по виходу елементів І-НІ, причому всі входи елементів І-НІ будь-якої групи з'єднані відповідно з виходами кожного елемента І-НІ інших груп, яка відрізняється тим, що для контролю працездатності схеми пам'яті від катастрофічних відмов додатково введена схема контролю, для схем пам'яті на елементах І-НІ на п'яти елементах: І-НІ (1), входи якого зв'язані з вузлами вхідної шини установки схеми пам'яті; І-НІ (2), вхідні вузли якого з'єднані з вузлами вихідної шини схеми пам'яті; І (3), у якого один вхідний вузол зв'язаний з вихідним вузлом І-НІ (2), а інші вхідні вузли зв'язані з вузлами вхідної шини схеми пам'яті; І (4), у якого один вхідний вузол зв'язаний з вихідним вузлом елемента І-НІ (1), а інші вхідні вузли зв'язані з вузлами вихідної шини схеми пам'яті; АБО (5), вхідні вузли якого зв'язані з вихідними вузлами елементів І (3) та (4); вихідний вузол елемента АБО (5), зв'язаний з вихідною шиною схеми контролю.

Текст

Реферат: Пристрій для знаходження катастрофічних відмов в базових схемах пам'яті містить n елементів І-НІ, один із входів елементів з'єднаний з вхідною шиною установки схеми пам'яті в один із станів, коли схеми пам'яті розбити на m(m n) груп, а коли схеми пам'яті розбити на m(m n) груп, то другий із входів елементи І-НІ елементів з'єднаний з вхідною шиною збереження станів схеми пам'яті, групи містять довільну кількість q взаємно не з'єднаних по виходу елементів І-НІ, причому всі входи елементів І-НІ будь-якої групи з'єднані відповідно з виходами кожного елемента І-НІ інших груп. Для контролю працездатності схеми пам'яті від катастрофічних відмов додатково введена схема контролю, для схем пам'яті на елементах І-НІ на п'яти елементах: І-НІ (1), входи якого зв'язані з вузлами вхідної шини установки схеми пам'яті; І-НІ (2), вхідні вузли якого з'єднані з вузлами вихідної шини схеми пам'яті; І (3), у якого один вхідний вузол зв'язаний з вихідним вузлом І-НІ (2), а інші вхідні вузли зв'язані з вузлами вхідної шини схеми пам'яті; І (4), у якого один вхідний вузол зв'язаний з вихідним вузлом елемента І-НІ (1), а інші вхідні вузли зв'язані з вузлами вихідної шини схеми пам'яті; АБО (5), вхідні вузли якого зв'язані з вихідними вузлами елементів І (3) та (4); вихідний вузол елемента АБО (5), зв'язаний з вихідною шиною схеми контролю. UA 88895 U (12) UA 88895 U UA 88895 U 5 10 15 20 25 30 35 40 45 50 55 Корисна модель належить до автоматики, обчислювальної техніки та описує базові схеми пам'яті, що призначені для прийому слова p(T) , яке складається з двох вхідних сигналів: установчого x(t) і зберігаючого e() , зберігання установленого стану a(T) або a() та передачі значення цього стану для подальшого використання. Відомі базові схеми пам'яті R-S-тригер та їх умовне графічне визначення на елементах І-НІ та АБО-НІ [Справочник по цифровой вычислительной технике: (процессоры и память),/Б.Н. Малиновский, Е.И. Брюхович, Е.Л. Денисенко и др. Под ред. Б.Н. Малиновского. - К.: Техніка, 1979. - стр. 143; рис. 4.18, а - на елементах І-НІ; рис. 4.18, б - на елементах АБО-НІ]. Недоліком цих є відсутність схеми самоконтролю їх працездатності. Відомі базові схеми пам'яті R-S-тригер та їх умовне графічне визначення без попередньої установки та з попередньою установкою тригерів в стан "0". [Мараховський Л.Ф. Комп'ютерна схемотехніка: Навч. Посіб. - К.: КНЕУ, 2008. - стр. 144, рис. 6.1 та на стр. 148, рис. 6.5]. Недоліком цих є відсутність схеми самоконтролю їх працездатності. Відомі базові багатостабільні схеми пам'яті (БСП) [Мараховський Л.Ф. Комп'ютерна схемотехніка: Навч. Посіб. - К.: КНЕУ, 2008. - стр. 158, рис. 6.13]. Недоліком цих є відсутність схеми самоконтролю їх працездатності. Відомі багатофункціональні схеми пам'яті двох типів (БФСП) [Мараховський Л.Ф. Комп'ютерна схемотехніка: Навч. Посіб. - К.: КНЕУ, 2008. - стр. 173, рис. 7.1; стр. 174, рис. 7.2]. Недоліком цих є відсутність схеми самоконтролю їх працездатності. Таким чином, бачимо, що всі відомі базові схеми пам'яті мають один важливий недолік: це відсутність схеми самоконтролю їх працездатності. В основу корисної моделі поставлена задача створення у базових схемах схему контролю для перевірки їх працездатності. Поставлена задача вирішується тим, що для контролю працездатності схеми пам'яті від катастрофічних відмов додатково введена схема контролю, яка складається із: Для схем пам'яті на елементах АБО-НІ на п'яти елементах: І-НІ, входи якого зв'язані з вузлами вхідної шини установки схеми пам'яті; АБО-НІ, вхідні вузли якого з'єднані з вузлами вихідної шини схеми пам'яті; АБО-НІ, у якого один вхідний вузол зв'язаний з вихідним вузлом ІНІ, а інші вхідні вузли зв'язані з вузлами вихідної шини схеми пам'яті; АБО-НІ, у якого один вхідний вузол зв'язаний з вихідним вузлом АБО-НІ, а інші вхідні вузли зв'язані з вузлами вхідної шини схеми пам'яті; АБО, вхідні вузли якого зв'язані з вихідними вузлами елементів АБО-НІ; вихідний вузол елемента АБО, зв'язаний з вихідною шиною схеми контролю. Для схем пам'яті на елементах І-НІ на п'яти елементах: І-НІ, входи якого зв'язані з вузлами вхідної шини установки схеми пам'яті; І-НІ, вхідні вузли якого з'єднані з вузлами вихідної шини схеми пам'яті; І, у якого один вхідний вузол зв'язаний з вихідним вузлом І-НІ, а інші вхідні вузли зв'язані з вузлами вхідної шини схеми пам'яті; І, у якого один вхідний вузол зв'язаний з вихідним вузлом елемента І-НІ, а інші вхідні вузли зв'язані з вузлами вихідної шини схеми пам'яті; АБО, вхідні вузли якого зв'язані з вихідними вузлами елементів І; вихідний вузол елемента АБО, зв'язаний з вихідною шиною схеми контролю. Усі базові схеми пам'яті мають установчий вхідний сигнал, що має на всіх вхідних вузлах однакові активні сигнали, які рівні логічної "1", і цей вхідний сигнал однозначно встановлює на усіх вихідних вузлах однакові логічні нульові "0" (пасивні) вихідні сигнали, що свідчить про те, що схема пам'яті працездатна, що всі її елементи працюють вірно. Такий встановлений стан схеми пам'яті, коли на усіх вихідних вузлах однакові логічні нульові "0" (пасивні) вихідні сигнали, у проміжності між установчими вхідними сигналами не зберігається і тому у детермінованих базових схемах пам'яті є забороненим, тобто не застосовується. Корисна модель пояснюється схемами, що приведені на Фіг. 1-4. Базовими схемами можна назвати схеми, котрі складаються з n елементів, що розбиті на m груп (n m) , вхідні та вихідні вузли яких поєднані відповідно з вхідною ВхШ або з вихідною ВихШ шинами схеми пам'яті. На кресленні (фіг. 1) зображена базова схема RS - тригера, яка складається з двох груп, які мають по одному елементу І-НІ (АБО-НІ), кожний з яких елемент однієї групи зв'язаний своїми виходами зі входом елемента іншої групи, та кожний додатковий вхідний вузол елементу І-НІ (АБО-НІ) схеми пам'яті зв'язаний з вхідною установчою шиною усієї схеми пам'яті, а вихідний вузол кожного елемента І-НІ (АБО-НІ) зв'язаний з вихідною шиною базової схеми пам'яті. Функціонування базової схеми RS - тригера задається таблицями 1 істинності. 1 UA 88895 U Таблиця 1 Робота RS - тригера На елементах І-НІ R 0 1 0 0 0 1 1 5 S Q 1 1 1 0 1 0 R 1 1 0 Q 1 0 1 0 1 0 На елементах АБО-НІ Q S 1 0 0 0 1 1 1 0 0 Q 0 1 0 0 1 Із табл. 1 бачимо, що стани у першому рядку, що встановлені установчим вхідним сигналом (R=S=0 на елементах І-НІ або R=S=1 на елементах АБО-НІ) не зберігаються при останньому рядку таблиці (R=S=0 на елементах І-НІ або R=S=1 на елементах АБО-НІ) і тому вони в детермінованому режимі заборонені. Визначення працездатності RS - тригера на логічних елементах АБО-НІ (І-НІ), при подачі на вхідні вузли установчого сигналу xp ( t ) (R 1; S 1) у час t на вихідних вузлах логічних елементів АБО-НІ(І-НІ) з'являється значення стану a(t ) (Q 0 i Q 0) , які разом визначають вихідній сигнал 10 y 4 ( t ) ( x p ( t ), a( t )) , який визначає працездатність усіх елементів схеми пам'яті у час t. (перевірки працездатності логічних елементів базової схеми у час t . Цей xp ( t ) вхідний сигнал у детермінованих пристроях заборонений. Тому, його можна використовувати тільки для перевірки працездатності схеми пам'яті у час подачі вхідного установчого сигналу xp ( t ) . Після закінчення xp ( t ) вхідного сигналу здійснюється ймовірний перехід схеми пам'яті в будь-який 15 запам'ятовуючий стан ai ( t ) , що запам'ятовуються при відповідному зберігаючому e() вхідному сигналі (R=S=0 на елементах І-НІ або R=S=1 на елементах АБО-НІ). При цьому, коли схема пам'яті працездатна, обов'язково на одному з вихідних вузлів логічних елементів АБО-НІ (ІНІ)схеми пам'яті вихідний сигнал повинний мати значення логічної 1. У цьому випадку, для перевірки працездатності базової схеми пам'яті у час , вихідний сигнал y 4 ( ) ( xp ( t ), 1( )) є 20 вихідним сигналом схеми контролю працездатності. За машинний час T (T t ) , коли RSтригер на логічних елементах АБО-НІ (I-НІ) працездатний, то при перевірки працездатності схеми пам'яті у час T вихідний сигнал y 4 (T) ( y 4 (T) y 4 (t )Uy 4 ()) повинний бути рівний логічному 1 (0). Схему перевірки працездатності базової схеми пам'яті можна задати у вигляді таблиці істинні, як для тригера на логічних елементах АБО-НІ, так й на логічних елементах І-НІ. 25 Таблиця 2 Перевірка працездатності RS - тригера На елементах І-НІ R S Q 0 0 1 1 1 1 0 На елементах АБО-НІ Q y 4 (t) y 4 ( ) R S Q Q y 4 (t) y 4 ( ) 1 0 1 0 1 1 1 0 0 1 1 0 0 0 1 0 0 0 1 1 0 0 0 1 1 2 UA 88895 U Таблиця 3 Перевірка працездатності багатостабільного тригера z1 z2 a1 0 ... 0 zn 0 0 1 1 1 1 0 1 1 1 1 z1 1 0 5 z2 zn 1 ... 1 0 0 0 1 На елементах І-НІ a2 ... 1 1 1 1 0 1 1 0 1 1 На елементах АБО-НІ a1 a2 ... 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 an y 4 (t) y 4 ( ) 1 1 1 1 0 0 1 1 1 1 1 0 0 0 0 an y 4 (t) y 4 ( ) 0 0 0 0 1 1 0 0 0 0 0 1 1 1 1 Для загальності розгляду зробимо заміну символів у RS - тригері, де R, S, Q відповідно позначимо z1 z2 , а вихідні сигнали позначимо a1 та a 2 . Тоді рівняння схеми перевірки працездатності тригерів на елементах АБО-НІ має такий вигляд: y 4 ( t ) z1z 2 ...zn a1 a 2 ... an , y 4 ( ) z1 z 2 ... zn a1 a 2 ... an . (1) 10 Рівняння схеми перевірки працездатності тригерів на елементах І-НІ має такий вигляд: y 4 ( t ) a1a2 ...an z1 z2 ... zn , y 4 ( ) z1z 2 ...zn a1 a2 ... an . (2) Загальний вихідний сигнал у машинному часу T має такий вигляд: y 4 (T) y 4 ( t ) y 4 ( ) (3) На кресленні (фіг. 3) зображена базова багатофункціональна схема, котра має дві множини вхідних сигналів Z(zi Z) та U(ui U) . Таблиця 4 Матриця станів багатофункціональної схеми пам'яті 1 0 2 a10 a20 ..... ... n an1 an0 1 a11 a21 ... 2 a12 a22 ... an2 ... ... anm ... ... ... m a1m a2m ... 15 Тригери та багатостабільні схеми пам'яті можна представити як рядок 0 (табл. 4) у зв'язку з тим, що усі її ai стани зберігаються при одному e() вхідному сигналі в одній множині всіх її станів. Ці схеми мають повноту функцій переходів, коли із кожного ak стану можна під впливом визначеного вхідного x(t) сигналу перейти в будь-яке, наперед заданий ai стан схеми пам'яті; а 20 також повнота системи виходів, коли кожний ai стан ототожнюється з вихіднім yi , сигналом, який відрізняється від усіх інших. При розгляданні рівняння схеми перевірки працездатності тригерів на елементах І-НІ, видно, що рівняння (2) та (3) підходять до створення схеми перевірки працездатності й багатофункціональних схем пам'яті. 3 UA 88895 U На основі формул (2) та (3) будуємо схеми перевірки працездатності при логічних елементах І-НІ На кресленні (фіг. 4) зображено схему перевірки працездатності при логічних елементах ІНІ. 5 ФОРМУЛА КОРИСНОЇ МОДЕЛІ 10 15 20 Пристрій для знаходження катастрофічних відмов в базових схемах пам'яті, що містить n елементів І-НІ, один із входів елементів з'єднаний з вхідною шиною установки схеми пам'яті в один із станів, коли схеми пам'яті розбити на m(m n) груп, а коли схеми пам'яті розбити на m(m n) груп, то другий із входів елементи І-НІ елементів з'єднаний з вхідною шиною збереження станів схеми пам'яті, групи містять довільну кількість q взаємно не з'єднаних по виходу елементів І-НІ, причому всі входи елементів І-НІ будь-якої групи з'єднані відповідно з виходами кожного елемента І-НІ інших груп, яка відрізняється тим, що для контролю працездатності схеми пам'яті від катастрофічних відмов додатково введена схема контролю, для схем пам'яті на елементах І-НІ на п'яти елементах: І-НІ (1), входи якого зв'язані з вузлами вхідної шини установки схеми пам'яті; І-НІ (2), вхідні вузли якого з'єднані з вузлами вихідної шини схеми пам'яті; І (3), у якого один вхідний вузол зв'язаний з вихідним вузлом І-НІ (2), а інші вхідні вузли зв'язані з вузлами вхідної шини схеми пам'яті; І (4), у якого один вхідний вузол зв'язаний з вихідним вузлом елемента І-НІ (1), а інші вхідні вузли зв'язані з вузлами вихідної шини схеми пам'яті; АБО (5), вхідні вузли якого зв'язані з вихідними вузлами елементів І (3) та (4); вихідний вузол елемента АБО (5), зв'язаний з вихідною шиною схеми контролю. 4 UA 88895 U Комп’ютерна верстка Д. Шеверун Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 5

ДивитисяДодаткова інформація

Автори англійськоюMarakhovskyi Leonid Fedorovych

Автори російськоюМараховский Леонид Федорович

МПК / Мітки

МПК: F15C 1/10

Мітки: пристрій, пам'яті, катастрофічних, базових, елементах, схемах, відмов, і-ні, знаходження

Код посилання

<a href="https://ua.patents.su/7-88895-pristrijj-dlya-znakhodzhennya-katastrofichnikh-vidmov-v-bazovikh-skhemakh-pamyati-na-elementakh-i-ni.html" target="_blank" rel="follow" title="База патентів України">Пристрій для знаходження катастрофічних відмов в базових схемах пам’яті на елементах і-ні</a>

Попередній патент: Спосіб біотестування контамінантів в харчових продуктах

Наступний патент: Спосіб внесення біопрепаратів мікроорганізмів в ґрунт та на поверхню рослин під час технологічних операцій при вирощуванні сільськогосподарських культур

Випадковий патент: Композиція для попередження інфекції mycoplasma spp.