Пристрій для захищеної передачі даних до радіомаяків для залізної дороги

Формула / Реферат

1. Пристрій (1) для захищеної передачі даних до радіомаяків для залізної дороги, який відрізняється тим, що він має першу та другу частини (1а, 1b) схеми, незалежні одна від іншої і гальванічно відокремлені одна від іншої, кожна з яких має:

- каскад вибору (2а, 2b) мікропроцесора (6а, 6b), сконфігурований для приймання інформаційних сигналів, що стосуються стану ділянки залізничної лінії, та для генерування принаймні однієї телеграми для передачі до радіомаяка; і

- контрольний каскад (3а, 3b), сконфігурований для порівняння телеграм, згенерованих першою та другою частинами (1а, 1b) схеми для дозволу/блокування передачі даних до згаданого радіомаяка;

причому згадана перша частина (1а) схеми також має передавальний каскад (4, 5, 17), сконфігурований для надання можливості передачі даних до згаданого радіомаяка телеграми, згенерованої згаданою першою частиною (1а) схеми, у випадку, коли порівняння, здійснене згаданим контрольним каскадом (3а, 3b), є успішним.

2. Пристрій за п. 1, який відрізняється тим, що згаданий передавальний каскад (4, 5, 17) має схему (4) швидкого вимикання, розташовану між виходом згаданого мікропроцесора (6а) та згаданим контрольним каскадом (3а) згаданої першої частини (1а) схеми, при цьому згадана схема (4) швидкого вимикання виконана з можливістю перешкоджання проходженню згаданої телеграми у випадку, коли згадане порівняння згаданим контрольним каскадом (3а, 3b) неуспішне.

3. Пристрій за п. 2, який відрізняється тим, що згадана схема (4) швидкого вимикання має перший та другий логічні елементи І (30, 31), кожен з яких має перший вхід (10а), до якого надсилається згадана телеграма, при цьому кожен логічний елемент І має другий вхід, до якого надсилається сигнал дозволу (EN1, EN2) від згаданого мікропроцесора (6b) другої частини (3b) згаданої схеми; при цьому згадана схема (4) швидкого вимикання також має логічний елемент АБО (32), який виконаний з можливістю приймання вихідних даних згаданих логічних елементів І (30, 31); і обидва згаданих сигнали дозволу (EN1, EN2) мають мале значення у випадку, коли згадане порівняння згаданим контрольним каскадом (3а, 3b) неуспішне.

4. Пристрій за п. 3, який відрізняється тим, що згадана схема (4) швидкого вимикання також має перший та другий порогові компаратори (33, 34), які виконані з можливістю приймання вихідних даних згаданого першого та відповідно другого логічних елементів І (30, 31) і приймання величини порогової напруги (VTH, -VTH), яка міняється у відповідь на контрольний сигнал (TSOG), згенерований мікропроцесором (6b) згаданої другої частини (3b) схеми, причому згаданий перший та згаданий другий порогові компаратори (33, 34) виконані з можливістю генерування відповідного контрольного сигналу (С1, С2), який надсилають до мікропроцесора (6а) згаданої першої частини (1а) схеми для перевірки роботи згаданої схеми (4) швидкого вимикання.

5. Пристрій за будь-яким одним з попередніх пп., який відрізняється тим, що згаданий передавальний каскад (4, 5, 17) має оптопару (17), розташовану між контрольним каскадом (3а) згаданої першої частини (1а) схеми, і згаданий радіомаяк, причому згадана оптопара (17) виконана з можливістю взаємодії зі схемою безпеки (18), яка виконана з можливістю приймання сигналів від мікропроцесорів (6а, 6b) згаданих першої та другої частин (1а, 1b) схеми для блокування згаданої оптопари (17) у випадку, коли згадане порівняння згаданим контрольним каскадом (3а, 3b) неуспішне.

6. Пристрій за будь-яким одним з попередніх пп., який відрізняється тим, що згаданий мікропроцесор (6а) згаданої першої частини (1а) схеми виконаний з можливістю переривання процесу генерування згаданої телеграми у випадку, коли згадане порівняння згаданим контрольним каскадом (3а, 3b) неуспішне.

7. Пристрій за будь-яким одним з попередніх пп., який відрізняється тим, що згаданий контрольний каскад (3а, 3b) має:

- принаймні один логічний елемент виключне АБО (20a-20d), який виконаний з можливістю приймання телеграм, згенерованих мікропроцесором (6а, 6b) першої та відповідно другої частин (1а, 1b) схеми;

- лічильник помилок (21a-21d), який має вхід, з'єднаний з виходом згаданого логічного елемента виключне АБО (20a-20d); та

- детектор помилок (22a-22d), який має вхід, з'єднаний з виходом згаданого лічильника помилок (21a-21d), та виконаний з можливістю генерування контрольного сигналу, який надсилається до відповідного мікропроцесора (6а, 6b).

8. Пристрій за п. 7, який відрізняється тим, що згаданий лічильник помилок (21a-21d) та згаданий детектор помилок (22a-22d) виконані з можливістю приймання тестувальної послідовності помилок, використовуваної для перевірки роботи згаданого контрольного каскаду (3а, 3b).

9. Пристрій за п. 8, який відрізняється тим, що згадана тестувальна послідовність помилок згенерована в телеграмі, згенерованій мікропроцесором (6b) згаданої другої частини (1b) схеми.

10. Пристрій за будь-яким із попередніх пп., який відрізняється тим, що кожен згаданий каскад вибору (2а, 2b) виконаний з можливістю генерування ряду телеграм для передачі до відповідних радіомаяків, причому згаданий каскад вибору (2а, 2b) виконаний з можливістю формування загальної телеграми, яка містить ряд груп послідовних бітів, кожна з яких містить біти, які мають відповідні позиції у різних телеграмах, а згаданий контрольний каскад (3а, 3b) має демультиплексорну схему (12а, 12b), яка виконана з можливістю приймання згаданої загальної телеграми і передавання різних бітів у кожній групі до відповідних виходів (OUT1a/b, OUT2a/b, OUT3a/b, OUT4a/b) так, що відповідна телеграма відновлюється на кожному виході (OUT1a/b, OUT2a/b, OUT3a/b, OUT4a/b).

11. Пристрій за п. 10, який відрізняється тим, що схема (4) швидкого вимикання розташована між виходом згаданого мікропроцесора (6а) та згаданим демультиплексором (12а) згаданої першої частини (1а) схеми, причому згадана схема (4) швидкого вимикання виконана з можливістю перешкоджання проходженню згаданої загальної телеграми у випадку, коли згадане порівняння згаданим контрольним каскадом (3а, 3b) неуспішне.

Текст

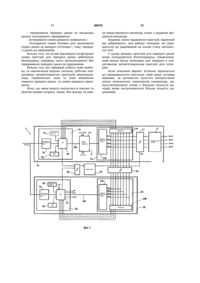

1. Пристрій (1) для захищеної передачі даних до радіомаяків для залізної дороги, який відрізняється тим, що він має першу та другу частини (1а, 1b) схеми, незалежні одна від іншої і гальванічно відокремлені одна від іншої, кожна з яких має: - каскад вибору (2а, 2b) мікропроцесора (6а, 6b), сконфігурований для приймання інформаційних сигналів, що стосуються стану ділянки залізничної лінії, та для генерування принаймні однієї телеграми для передачі до радіомаяка; і - контрольний каскад (3а, 3b), сконфігурований для порівняння телеграм, згенерованих першою та другою частинами (1а, 1b) схеми для дозволу/блокування передачі даних до згаданого радіомаяка; причому згадана перша частина (1а) схеми також має передавальний каскад (4, 5, 17), сконфігурований для надання можливості передачі даних до згаданого радіомаяка телеграми, згенерованої згаданою першою частиною (1а) схеми, у випадку, коли порівняння, здійснене згаданим контрольним каскадом (3а, 3b), є успішним. 2. Пристрій за п. 1, який відрізняється тим, що згаданий передавальний каскад (4, 5, 17) має схему (4) швидкого вимикання, розташовану між виходом згаданого мікропроцесора (6а) та згаданим контрольним каскадом (3а) згаданої першої частини (1а) схеми, при цьому згадана схема (4) швидкого вимикання виконана з можливістю перешкоджання проходженню згаданої телеграми у випадку, коли згадане порівняння згаданим контрольним каскадом (3а, 3b) неуспішне. 2 (19) 1 3 90676 4 вання згаданої телеграми у випадку, коли згадане порівняння згаданим контрольним каскадом (3а, 3b) неуспішне. 7. Пристрій за будь-яким одним з попередніх пп., який відрізняється тим, що згаданий контрольний каскад (3а, 3b) має: - принаймні один логічний елемент виключне АБО (20a-20d), який виконаний з можливістю приймання телеграм, згенерованих мікропроцесором (6а, 6b) першої та відповідно другої частин (1а, 1b) схеми; - лічильник помилок (21a-21d), який має вхід, з'єднаний з виходом згаданого логічного елемента виключне АБО (20a-20d); та - детектор помилок (22a-22d), який має вхід, з'єднаний з виходом згаданого лічильника помилок (21a-21d), та виконаний з можливістю генерування контрольного сигналу, який надсилається до відповідного мікропроцесора (6а, 6b). 8. Пристрій за п. 7, який відрізняється тим, що згаданий лічильник помилок (21a-21d) та згаданий детектор помилок (22a-22d) виконані з можливістю приймання тестувальної послідовності помилок, використовуваної для перевірки роботи згаданого контрольного каскаду (3а, 3b). 9. Пристрій за п. 8, який відрізняється тим, що згадана тестувальна послідовність помилок згенерована в телеграмі, згенерованій мікропроцесором (6b) згаданої другої частини (1b) схеми. 10. Пристрій за будь-яким із попередніх пп., який відрізняється тим, що кожен згаданий каскад вибору (2а, 2b) виконаний з можливістю генерування ряду телеграм для передачі до відповідних радіомаяків, причому згаданий каскад вибору (2а, 2b) виконаний з можливістю формування загальної телеграми, яка містить ряд груп послідовних бітів, кожна з яких містить біти, які мають відповідні позиції у різних телеграмах, а згаданий контрольний каскад (3а, 3b) має демультиплексорну схему (12а, 12b), яка виконана з можливістю приймання згаданої загальної телеграми і передавання різних бітів у кожній групі до відповідних виходів (OUT1a/b, OUT2a/b, OUT3a/b, OUT4a/b) так, що відповідна телеграма відновлюється на кожному виході (OUT1a/b, OUT2a/b, OUT3a/b, OUT4a/b). 11. Пристрій за п. 10, який відрізняється тим, що схема (4) швидкого вимикання розташована між виходом згаданого мікропроцесора (6а) та згаданим демультиплексором (12а) згаданої першої частини (1а) схеми, причому згадана схема (4) швидкого вимикання виконана з можливістю перешкоджання проходженню згаданої загальної телеграми у випадку, коли згадане порівняння згаданим контрольним каскадом (3а, 3b) неуспішне. Представлений винахід відноситься до пристрою для захищеної передачі даних, зокрема захищеної передачі телеграм, до радіомаяків для залізної дороги. Як відомо, радіомаяки для залізної дороги (також відомі під французьким терміном "орієнтир") встановлюються вздовж залізничних ліній, приймають електромагнітний сигнал дозволу від транспортного засобу, який рухається по залізничній лінії, і генерують закодований сигнал у відповідь (телеграму) 20 на надісланий до транспортного засобу сигнал, який містить інформацію, що стосується ділянки шляху та швидкості руху і транспортного засобу. Наприклад, інформація може відображати наявність перешкоди на ділянці залізничної лінії в напрямку руху від розташування радіомаяка. Радіомаяки мають приймальну антену та передавальну антену і зазвичай встановлюються між рейками залізничної лінії і кріпляться до шпал. Пристрої для кодування та передачі даних (відомі як «кодери») також встановлюються вздовж залізничних ліній для одержання інформації в місці експлуатації, що стосується стану залізничної лінії, і для передавання відповідної телеграми, вибраної і на основі вхідних сигналів, до радіомаяків. Вхідні сигнали для кодера зазвичай надходять від релейних контактів, встановлених вздовж залізничної лінії, і які перемикаються при наперед визначених подіях, таких як перемикання світла світ лофора з червоного на зелене, переведення стрілок, і т.д.. Іншими словами, радіомаяки просто надсилають релейні телеграми, вибрані і передані кодерами до транспортних засобів, які рухаються по залізничній лінії. Тому, суттєво, щоб телеграми, передані до транспортних засобів, які рухаються по даній ділянці залізничної лінії і від яких залежить їх безпека, були цілком достовірними. Тому, кодер повинен забезпечувати нехтуваний ступінь помилки як у виборі телеграми на основі стану залізничної лінії так й у передачі вибраної телеграми до радіомаяків. Задачею представленого винаходу є забезпечення покращеного, більш захищеного, більш надійного вибору та передачі телеграм до радіомаяків. Згідно з представленим винаходом надається пристрій для захищеної передачі даних до радіомаяків для залізної дороги, який відрізняється тим, що він містить першу та другу частини схеми, які незалежні та гальванічно відокремлені одна від іншої, і кожна з яких має: каскад вибору мікропроцесора для приймання інформаційних сигналів про стан ділянки залізничної лінії і для генерування принаймні однієї телеграми для передачі її до радіомаяка; і контрольний каскад для порівняння телеграм, згенерованих першою та другою частинами схеми, і для дозволу/блокування передачі даних до згаданого радіомаяка; причому згадана 5 перша частина схеми також має передавальний каскад, який дозволяє передачу до згаданого радіомаяка телеграми, згенерованої згаданою першою частиною схеми у випадку, коли порівняння, виконане згаданим контрольним каскадом, є успішним. Переважний, необмежувальний варіант виконання винаходу буде описуватися за допомогою прикладу з посиланням на супровідні креслення, на яких: Фіг.1 зображає блок-схему пристрою для передачі даних у відповідності з винаходом; Фіг.2 та 3 зображають детальні схеми частин пристрою з Фіг.1. Посилаючись на Фіг.1, пристрій 1 для передачі даних у відповідністю з винаходом має першу та другу частини 1а та 1b схеми, які гальванічно відокремлені одна від іншої і працюють паралельно незалежно одна від іншої. Перша частина схеми 1а передає телеграми до радіомаяків, у той час як друга частина 1b схеми перевіряє роботу пристрою 1 для передачі даних. Більш точно, в зображеному прикладі пристрій 1 для передачі даних контролює чотири радіомаяки (BCN1, BCN2, BCN3, BCN4), хоча кількість контрольованих радіомаяків очевидно може бути іншою ніж чотири. Перша та друга частини 1а, 1b схеми кожна має каскад вибору 2а, 2b для приймання вхідних сигналів (INPUTS), згенерованих відомим способом, і які стосуються стану ділянки залізничної лінії (наприклад, не зображена сортувальна станція), і для належного генерування відповідної телеграми для передачі до кожного радіомаяка. Кожна перша та друга частини 1а, 1b схеми також має контрольний каскад 3а, 3d для безперервного регулювання роботи пристрою 1 для передачі даних одночасно з передачею даних до радіомаяків. Перша частина 1а схеми також має схему 4 швидкого вимикання, яка розташована між каскадом вибору 2а та контрольним каскадом 3а для припинення передачі даних до радіомаяків у випадку аварій, та передавальний каскад 5 для передачі підтверджених згенерованих телеграм до радіомаяків. Більш точно, кожний каскад вибору 2а, 2b має мікропроцесор 6а, 6b, схему 7а, 7b прийому та накопичення даних для прийому вхідних сигналів, які відображають стан залізничної лінії, запам'ятовуючий пристрій 8а, 8b для телеграм, який містить ряд попередньо встановлених телеграм (визначені послідовністю бітів) та оперативний запам'ятовуючий пристрій 9а, 9b. Схеми 7а, 7b прийому та накопичення даних приймають, повністю незалежно одна від іншої, ряд паралельних сигналів по струму або напрузі. Кожен мікропроцесор 6а, 6b приймає сигнали від відповідної схеми 7а, 7b прийому та накопичення даних і з'єднаний з відповідним запам'ятовуючим пристроєм 8а, 8b для телеграм та з відповідним оперативним запам'ятовуючим пристроєм 9а, 9b. Більш точно, оперативний запам'ятовуючий пристрій 9а, 9b поділений на два блоки: робочий 90676 6 блок та тестувальний блок, які фізично відокремлені один від іншого. Вихід кожного мікропроцесора 6а, 6b під'єднаний до відповідного контрольного каскаду За, 3d за допомогою каналу 10а, 10b послідовної передачі даних. Контрольний каскад 3а, 3b має демультиплексорну схему 12а, 12b з одним входом та чотирма виходами, яка приймає сигнал, згенерований відповідним мікропроцесором 6а, 6b, і, у свою чергу, генерує чотири вихідні сигнали OUT1a/b, OUT2a/b, OUT3a/b, OUT4a/b, кожен з яких передбачений для контролю відповідного радіомаяка, та порівняльну схему 14а, 14b для прийому та порівняння біт за бітом відповідних сигналів, згенерованих першою та другою частинами 1а, 1b схеми. Більш точно, порівняльна схема 14а, 14b виконує побітове порівняння сигналів OUT1a та OUT1b, OUT2a та OUT2b, OUT3a та OUT3b, та OUT4a та OUT4b. Результат побітового порівняння передається порівняльною схемою 14а, 14b до відповідного мікропроцесора 6а, 6b. Перша оптопара 16 розташована між виходами демультиплексорної схеми 12а та входами порівняльної схеми 14b, і між виходами демультиплексорної схеми 12b та входами порівняльної схеми 14а, таким чином, що відсутнє пряме проходження електричних сигналів від першої частини 1а схеми до другої частини 1b схеми, які таким чином зберігаються гальванічно ізольованими. Фігура 2 зображає структуру порівняльної схеми 14а, 14b. Більш точно, порівняльна схема 14а, 14b має чотири логічних елемента «виключне АБО» 20a20d, які приймають сигнали OUT1a та OUT1b, сигнали OUT2a та OUT2b, сигнали OUT3a та OUT3b, і відповідно сигнали OUT4a та OUT4b. Порівняльна схема 14а, 14b також має чотири лічильники помилок 21a-21d та чотири детектори помилок 22a-22d. Кожен лічильник помилок 21a21d з'єднаний з виходом відповідного логічного елемента «виключне АБО» 20a-20d і має вихід, з'єднаний з входом відповідного детектора помилок 22a-22d, який генерує контрольний сигнал, який передається до відповідного мікропроцесора 6а, 6b. Фіг.3 зображає структуру схеми 4 швидкого вимикання, розташовану між виходом мікропроцесора 6а та демультиплексорною схемою 12а першої частини 1а схеми. Схема 4 швидкого вимикання має перший та другий логічний елементи «І» 30, 31, логічний елемент «АБО» 32, та перший і другий пороговий компаратор 33, 34. Більш точно, перший логічний елемент «І» 30 приймає вихідний сигнал мікропроцесора 6а по каналам 10а послідовного передавання і перший сигнал дозволу EN1, згенерований мікропроцесором 6b, а другий логічний елемент «І» 31 приймає вихідний сигнал мікропроцесора 6а та другий сигнал дозволу EN2, також згенерований мікропроцесором 6b. Логічний елемент «АБО» 32 приймає вихідні сигнали першого та другого логічного еле 7 мента «І» 30, 31 і генерує сигнал, який передається до входу демультиплексорної схеми 12а. Перший та другий порогові компаратори 33, 34 з'єднані з виходами першого та відповідно другого логічних елементів «І» 30, 31 і генерують перший та другий сигнали порівняння С1, С2, які зчитуються мікропроцесором 6b. Більш точно, перший та другий сигнали порівняння С1, С2 є результатами порівняння вихідних даних першого та відповідно другого логічних елементів «І» 30, 31 із змінною пороговою напругою. Більш точно, в залежності від стану перемикача 35, керованого контрольним сигналом TSOG, який надсилається мікропроцесором 6b, порогова напруга може приймати перше додатне значення (VTH) або друге від'ємне значення (-VTH), протилежне до першого значення. Передавальний каскад 5 на виході першої частини 1а схеми приймає вихідні сигнали OUT1a, OUT2a, ОUТ3а, OUT4a демультиплексорної схеми 12а за допомогою передбачення другої оптопари 17 і контролює чотири відповідні радіомаяки. Пристрій 1 для передачі даних також має схему безпеки 18, яка приймає сигнал дозволу від кожного мікропроцесора 6а, 6b за допомогою передбачення третьої оптопари 19 для утримування мікропроцесорів 6а, 6b гальванічно ізольованими. Більш точно, схема безпеки 18 живить другу оптопару 17 живлячою напругою Vdc. Пристрій 1 для передачі даних працює наступним чином. Перша та друга частини 1а та 1b схеми (Фіг.1) приймають вхідні сигнали, що незалежно стосуються стану залізничної лінії. Більш точно, схема 7а, 7b прийому та накопичення даних приймає та передає значення напруги та струму вхідних сигналів до відповідного мікропроцесора 6а, 6b, і може також приймати напругу відомої величини для перевірки роботи каналів прийому. Кожен мікропроцесор 6а, 6b надає доступ до двох фізично відокремлених (робочого та тестувального) блоків відповідного оперативного запам'ятовуючого пристрою 9а, 9b. Більш точно, перші робочі операції виконуються на першому блоці робочому блоці - у той час як другий блок - тестувальний блок - одночасно тестується. Після завершення тестування область робочого запам'ятовуючого пристрою копіюється в протестований другий блок, робочі операції виконуються на другому блоці і тестується перший блок. Іншими словами, два робочі блоки перемикаються і безперервно тестуються в робочому режимі без переривання в робочих операціях. На основі даних, прийнятих відповідною схемою 7а, 7b прийому та накопичення даних, мікропроцесор 6а, 6b незалежно вибирає відповідну телеграму із запам'ятовуючого пристрою 8а, 8b для телеграм на основі наперед встановлених (відомих) внутрішніх правил. Більш точно, на основі вхідних даних відомим способом генерується відповідна телеграма TG1, TG2, TG3, TG4 для кожного з чотирьох радіомаяків і з чотирьох телеграм TG1, TG2, TG3, TG4 формується загальна телеграма, яка містить ряд груп 90676 8 послідовних бітів, кожна з яких містить біти, які мають відповідні позиції у різних телеграмах. Тобто, перша група бітів має перші біти в телеграмах TG1, TG2, TG3, TG4, друга група бітів має другі біти в телеграмах TG1, TG2, TG3, TG4, і так далі до кінця телеграм. Таким чином сформована загальна телеграма передається по каналам 10а, 10b послідовного передавання зі швидкістю передачі, в чотири рази більшою за частоту, використовувану для передачі даних до радіомаяків. Ряд радіомаяків (чотири в зображеному прикладі) можуть, таким чином, керуватися по одному TDM (Мультиплексному з Часовим Розділенням) каналу послідовного передавання для безперервної передачі даних до радіомаяків. Синхронізуюча логічна схема в першому та другому мікропроцесорах 6а, 6b синхронізує передачу телеграм по каналам 10а, 10b послідовного передавання, які використовують загальний сигнал синхронізації. Загальна телеграма, згенерована мікропроцесором 6а, 6b, приймається відповідною демультиплексорною схемою 12а, 12b, яка передає різні біти в кожній групі до відповідних виходів ODT1a/b, OUT2a/b, OUT3a/b, OUT4a/b так, що відповідна телеграма TG1, TG2, TG3, TG4, яка передається до відповідного радіомаяка, відновлюється на кожному виході OUT1a/b, OUT2a/b, OUT3a/b, OUT4a/b. Демультиплексорна схема 12а, 12b виконує цю операцію за допомогою послідовних логічних синхронних операцій з сигналом синхронізації, дані якого передаються по каналу 10а, 10b послідовного передавання. Чотири відновлені телеграми на виходах OUT1a/b, OUT2a/b, OUT3a/b, OUT4a/b потім надсилаються до порівняльних схем 14а, 14b. Порівняльні схеми 14а, 14b виконують побітове порівняння телеграм TG1, TG2, TG3, TG4, переданих першою частиною 1а схеми, та телеграм TG1, TG2, TG3, TG4, переданих другою частиною 1b схеми, для встановлення відповідності переданих даних. Фактично, за відсутності дефектів в пристрої 1 для передачі даних, телеграми, незалежно згенеровані мікропроцесорами 6а, 6b з тих же вхідних сигналів, повинні співпадати. Більш точно (Фігура 2), біти в однакових позиціях в кожній телеграмі TG1, TG2, TG3, TG4, згенерованій двома частинами 1а та 1b схеми, порівнюються в логічних елементах «виключне АБО» 20a-20d, які генерують тільки малу логічну величину, якщо співставлені біти мають однакове значення. Вихідний сигнал з логічного елемента «виключне АБО» 20a-20d приймається лічильником помилок 21a-21d і детектором помилок 22a-22d, які відповідно запам'ятовують кількість виявлених помилок і їх місця в переданій телеграмі Більш точно, лічильник помилок 21а, 21d збільшує кількість виявлених помилок кожен раз, коли він приймає старший логічний сигнал від відповідного логічного елемента «виключне АБО» 20a-20d. 9 Дані, збережені в лічильниках помилок 21a21d та в детекторах помилок 22a-22d, потім передаються до відповідного мікропроцесора 6а, 6b у вигляді контрольних сигналів для відображення наявності, якщо це має місце, помилок передачі даних. Більш точно, кожен мікропроцесор 6а, 6b приймає контрольні сигнали, згенеровані незалежно відповідною порівняльною схемою 14а, 14b. Якщо не виявлено жодної помилки, то телеграми TG1, TG2, TG3, TG4 на чотирьох виходах OUT1a, OUT2a, OUT3a, OUT4a демультиплексорної схеми 12а передаються через оптопару 17 до передавального каскаду 5 для керування відповідними радіомаяками. Оптопара 17, яка дозволяє проходження вихідних даних, живиться напругою Vdc зі схеми безпеки 18, яка активується сигналами увімкнення від мікропроцесорів 6а, 6b. І навпаки, якщо виявлено якісь помилки передачі даних, то виконуються наступні дії для запобігання передачі хибних телеграм до радіомаяків і для запобігання прийманню та кодуванню будьякими рухомими транспортними засобами потенційно небезпечних повідомлень: - перший мікропроцесор 6а перериває передачу даних по каналу 10а послідовного передавання; - обидва мікропроцесори 6а, 6b переривають передачу сигналів дозволу до схеми безпеки 18, таким чином припиняючи подачу напруги Vdc до оптопари 17 і, таким чином, блокуючи проходження телеграм до передавального каскаду 5; і - другий мікропроцесор 6b активує схему 4 швидкого вимикання, яка припиняє передачу даних від виходу мікропроцесора 6а до входу демультиплексорної схеми 12а. Більш точно (Фіг.3), схема 4 швидкого вимикання працює наступним чином. Другий мікропроцесор 6b безперервно подає до схеми 4 швидкого вимикання сигнали дозволу EN1 та EN2, які, у випадку нормальної роботи пристрою 1 для передачі даних, дозволяють передачу даних за допомогою логічного елемента «І» 30 (високий логічний рівень сигналу дозволу EN1 та низький логічний рівень сигналу дозволу EN2) або за допомогою логічного елемента «І» 31 (високий логічний рівень сигналу дозволу EN2 та низький логічний рівень сигналу дозволу EN1). Виходи логічних елементів «І» 30, 31 з'єднані з входами логічного елементу «АБО» 32 так, що дані безперервно надходять до виходу схеми швидкого вимикання. При виявленні помилок, які вимагають переривання передачі даних, другий мікропроцесор 6b блокує обидва логічні елементи «І» 30, 31 шляхом переведення обох сигналів дозволу EN1, EN2 на низький логічний рівень. Наявність двох вхідних логічних елементів «І» 30, 31 дозволяє роботу схеми 4 швидкого вимикання, яка тестується одночасно з передачею даних. Тобто, другий мікропроцесор 6b поперемінно дозволяє передачу даних за допомогою логічного елемента «І» 30 і визначає, чи дійсно заблоковано 90676 10 вихід логічного елемента «І» 31, а потім дозволяє передачу даних за допомогою логічного елемента «І» 31 і визначає, чи дійсно заблокований вихід логічного елемента «І» 30. Ці перевірки виконуються другим мікропроцесором 6b шляхом прийому першого та другого сигналів порівняння С1, С2 від компараторів 33, 34. З цією метою, мікропроцесор 6b виконаний для вимикання перемикача 35 (за допомогою контрольного сигналу TSOG), таким чином міняючи порогову величину компараторів 33, 34, і для перевірки, чи заблоковано вихідний рівень логічних елементів «І» 30, 31. Більш точно, коли логічний елемент «І» 30 заблоковано, то перевірка виконується шляхом зчитування вихідних даних С1 відповідного компаратора 33 паралельно зі зміною в його вхідній пороговій напрузі. Тому, вихід логічного елемента «І» 30 (заблокований) приймає еталонне значення (наприклад нуль), яке надсилається до входу компаратора 33, при цьому його другий вхід приймає додатню або від'ємну порогову напругу (VTH, -VTH) так, що реальне блокування виходу логічного елемента «І» 30 може визначатися простим регулюванням перемикання виходу компаратора 33 паралельно із зміною порогової напруги. Теж саме також застосовується для визначення реального блокування логічного елемента «І» 31. Пристрій 1 для передачі даних також забезпечує перевірку роботи порівняльних схем 14а, 14b, зокрема схем виявлення та зберігання помилок, одночасно з передачею телеграм до радіомаяків. Більш точно, мікропроцесор 6b вводить в телеграму, передану по каналу 10b послідовної передачі, послідовність відомої кількості помилок у наперед визначені місця в телеграмі. Це можливо за рахунок того, що телеграми, реально надіслані до радіомаяків, є телеграмами, згенерованими мікропроцесором 6а і переданими по каналу 10а послідовного передавання, і які не містять помилок. Після передачі заданої кількості бітів в телеграмах, кожен мікропроцесор 6а, 6b незалежно перевіряє кількість і місце запрограмованих помилок (у послідовності перевірки помилок), які відповідають кількості та місцю реально виявлених помилок. Таким чином, може перевірятися робота порівняльних схем 14а, 14b і перериватися передача телеграм у випадку неспівпадіння виявлених помилок. Переваги представленого винаходу будуть очевидними з наступного опису. Зокрема, використовуючи дві незалежні, гальванічно ізольовані частини схеми для прийому вхідних сигналів і незалежно генерування відповідних телеграм, і дві незалежні порівняльні схеми для порівняння та забезпечення узгодження двох згенерованих телеграм, значно покращується захищена передача даних до радіомаяків. Якщо виявляються якісь помилки, то пристрій для передачі даних згідно з представленим винаходом надає три взаємно об'єднувані способи якомога скорішого переривання передачі даних: 11 - переривання передачі даних по вихідному каналу послідовного передавання; - активування схеми швидкого вимикання; і - блокування схеми безпеки для припинення подачі даних до вихідної оптопари і, тому, передачі даних до радіомаяків. Більше того, на основі відповідної конфігурації схеми пристрій для передачі даних забезпечує безперервну перевірку свого функціонування без переривання передачі даних до радіомаяків. Більше того, він перевіряє роботу схем прийому та накопичення вхідних сигналів, робочих оперативних запам'ятовуючих пристроїв мікропроцесора, порівняльних схем та схем виявлення помилок передачі даних, та схеми швидкого вимикання. Ясно, що зміни можуть вноситися в описані та проілюстровані розділи, однак, без виходу за рам 90676 12 ки представленого винаходу згідно з доданою формулою винаходу. Зокрема, може надаватися пристрій, відмінний від зображеного, для вибору телеграм, які передаються до радіомаяків на основі стану залізничної лінії. У цьому випадку пристрій для передачі даних може оснащуватися безпосередньо покажчиком, який вказує місце телеграми для передачі в оперативному запам'ятовуючому пристрої для телеграм. Хоча описаний варіант втілення відноситься до передавального пристрою, який керує чотирма маяками, за допомогою простого використання різних електронних компонентів (наприклад, демультиплексорної схеми з більшою кількістю виходів) може контролюватися більша кількість радіомаяків. 13 Комп’ютерна верстка М. Ломалова 90676 Підписне 14 Тираж 26 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for safe data transmission to railway beacons

Автори англійськоюFiz Maurizio, Curotto Mauro

Назва патенту російськоюУстройство для защищенной передачи данных на радиомаяки для железной дороги

Автори російськоюФиц Маурицио, Куротто Мауро

МПК / Мітки

МПК: B61L 1/00

Мітки: захищеної, залізної, передачі, даних, радіомаяків, пристрій, дороги

Код посилання

<a href="https://ua.patents.su/7-90676-pristrijj-dlya-zakhishheno-peredachi-danikh-do-radiomayakiv-dlya-zalizno-dorogi.html" target="_blank" rel="follow" title="База патентів України">Пристрій для захищеної передачі даних до радіомаяків для залізної дороги</a>

Попередній патент: Процес і пристрій для ремонту пошкодженого піддона

Наступний патент: Стійкий концентрат рідини, що включає барвник

Випадковий патент: Спосіб визначення рефлексу м'яза, який піднімає верхнє віко