Логічний елемент

Формула / Реферат

Логічний елемент, який містить джерело постійної напруги, перший, другий входи, перший, другий виходи пристрою, перший, другий вхідні транзистори, перший, другий проміжні транзистори, перший, другий, третій, четвертий, п'ятий вихідні транзистори, транзистор зворотної провідності, перший, другий, третій діоди, перший, другий, третій, четвертий, п'ятий, шостий, сьомий, восьмий резистори, причому емітери першого і другого вхідних транзисторів з'єднані відповідно з першим і другим входами пристрою, бази через перший і другий резистори підключені до додатного полюса джерела постійної напруги, а їх колектори з'єднані з базами відповідно першого і другого проміжних транзисторів, колектори яких через третій резистор підключені до додатного полюса джерела постійної напруги і з'єднані з базами першого і третього вихідних транзисторів, колектор третього вихідного транзистора підключений до додатного полюса джерела постійної напруги, емітер з'єднаний з анодом другого діода, катод якого з'єднаний з першим виводом шостого резистора, а колектор першого вихідного транзистора через четвертий резистор підключений до додатного полюса джерела постійної напруги, емітер з'єднаний з анодом першого діода, катод якого підключений до першого виходу пристрою і з'єднаний з колектором другого вихідного транзистора, емітер якого підключений до загальної шини джерела постійної напруги, а база через п'ятий резистор підключена до загальної шини джерела постійної напруги та з'єднана з емітерами першого, другого проміжних транзисторів і базою п'ятого вихідного транзистора, емітер якого підключений до загальної шини джерела постійної напруги, колектор з'єднаний з першим виводом сьомого резистора, а, також, перший вивід восьмого резистора підключений до додатного полюса джерела постійної напруги і катод третього діода підключений до другого виходу пристрою, який відрізняється тим, що додатково введено дев'ятий резистор, причому емітер транзистора зворотної провідності підключений до додатного полюса джерела постійної напруги, колектор з'єднаний з анодом третього діода, база з'єднана з другими виводами сьомого і восьмого резисторів, а емітер четвертого вихідного транзистора підключений до загальної шини джерела постійної напруги, колектор підключений до другого виходу пристрою, а база з'єднана з другим виводом шостого резистора і через дев'ятий резистор підключена до загальної шини джерела постійної напруги.

Текст

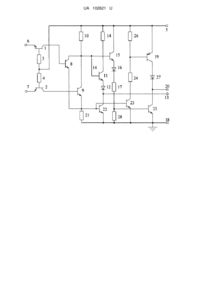

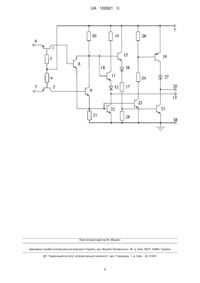

Реферат: UA 102621 U UA 102621 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до області мікроелектроніки і обчислювальної техніки та призначена для синхронізації (узгодження) цифрових пристроїв різної швидкості. Відомий логічний елемент І-НІ, який містить схему І на багатоемітерному транзисторі і резисторі, підсилювальний каскад і складний інвертор на доповнюючих транзисторах типу n-p-n і p-n-p, крім того, в ньому додатково встановлений транзистор типу p-n-p, емітер якого з'єднаний з шиною живлення, колектор - з базою доповнюючого транзистора типу р-n-р складного інвертора і через резистор - з базою багатоемітерного транзистора, а база доповнюючого транзистора типу p-n-p з'єднана з середньою точкою подільника напруги на резисторах, який підключено між шиною живлення і колектором транзистора підсилювального каскаду [див. А.С. СРСР № 466620, м.кл Н03К 19/36, бюл. № 13, 1975]. Недоліком такого пристрою, що реалізує тільки одну логічну функцію І-НІ, є обмежені функціональні можливості. За прототип вибрано логічний елемент [див. а.с. СРСР № 1568234, м.кл. Н03К 19/088, бюл. № 20, 1990], який містить перший і другий вхідні транзистори, бази яких через перший і другий резистори підключені до шини живлення, в подальшому додатного полюса джерела постійної напруги, емітери підключені до першого і другого входів логічного елемента, а колектори з'єднані з базами відповідно першого і другого проміжних транзисторів, колектори яких підключені через третій резистор до додатного полюса джерела постійної напруги і з'єднані з базою першого вихідного транзистора, емітер якого через перший діод підключений до першого виходу пристрою, а колектор через четвертий резистор підключений до додатного полюса джерела постійної напруги і колектору третього вихідного транзистора, база якого з'єднана з базою першого вихідного транзистора, емітер з'єднаний з анодом другого діода, катод якого через шостий резистор підключений до загальної шини, в подальшому загальної шини джерела постійної напруги і з'єднаний з базою транзистора зворотної провідності, колектор якого підключений до загальної шини джерела постійної напруги, а емітер підключений до другого виходу пристрою, емітери першого і другого проміжних транзисторів підключені через п'ятий резистор до загальної шини джерела постійної напруги і з'єднані з базами другого і п'ятого вихідних транзисторів, емітери яких підключені до загальної шини джерела постійної напруги, колектор другого вихідного транзистора підключений до першого виходу пристрою, а колектор п'ятого вихідного транзистора через сьомий резистор підключений до додатного полюса постійної напруги і з'єднаний з базою четвертого вихідного транзистора, колектор якого через восьмий резистор підключений до додатного полюса джерела постійної напруги, а емітер з'єднаний з анодом третього діода, катод якого підключений до другого виходу пристрою. Недоліком пристрою, що реалізує логічну функцію АБО-HI на першому виході та на другому виході - логічну функцію АБО-НІ із затримкою часу відносно появи сигналу на першому виході, є обмежені функціональні можливості, тому що він не дозволяє реалізувати на другому виході пристрою логічну функцію АБО із затримкою часу відносно інверсної функції АБО-НІ, що реалізована на першому виході пристрою. В основу корисної моделі поставлена задача створення логічного елемента з розширеними функціональними можливостями, в якому крім логічної функції АБО-НІ, що реалізована на першому виході пристрою, за рахунок введення нового елемента та нових зв'язків між елементами на другому виході пристрою реалізовано пряму логічну функцію АБО з затримкою часу відносно появи сигналу на першому вході пристрою, де реалізовано інверсну логічну функцію АБО-НІ. Це дозволяє використовувати запропонований логічний елемент для синхронізації (узгодження) цифрових пристроїв різної швидкодії. Поставлена задача вирішується тим, що в логічний елемент, який містить джерело постійної напруги, перший, другий входи, перший, другий виходи пристрою, перший, другий вхідні транзистори, перший, другий проміжні транзистори, перший, другий, третій, четвертий, п'ятий вихідні транзистори, транзистор зворотної провідності, перший, другий, третій діоди, перший, другий, третій, четвертий, п'ятий, шостий, сьомий, восьмий резистори, причому емітери першого і другого вхідних транзисторів з'єднані відповідно з першим і другим входами пристрою, бази через перший і другий резистори підключені до додатного полюса джерела постійної напруги, колектори з'єднані з базами відповідно першого і другого проміжних транзисторів, колектори яких через третій резистор підключені до додатного полюса джерела постійної напруги і з'єднані з базами першого і третього вихідних транзисторів, колектор третього вихідного транзистора підключений до додатного полюса джерела постійної напруги, емітер з'єднаний з анодом другого діода, катод якого з'єднаний з першим виводом шостого резистора, а колектор першого вихідного транзистора через четвертий резистор підключений до додатного полюса джерела постійної напруги, емітер з'єднаний з анодом першого діода, катод якого підключений до першого виходу пристрою і з'єднаний з колектором другого вихідного транзистора, емітер якого 1 UA 102621 U 5 10 15 20 25 30 35 40 45 50 55 60 підключений до загальної шини джерела постійної напруги, а база через п'ятий резистор підключена до загальної шини джерела постійної напруги та з'єднана з емітерами першого, другого проміжних транзисторів і базою п'ятого вихідного транзистора, емітер якого підключений до загальної шини джерела постійної напруги, колектор з'єднаний з першим виводом сьомого резистора, а, також, перший вивід восьмого резистора підключений до додатного полюса джерела постійної напруги і катод третього діода підключений до другого виходу пристрою, введено дев'ятий резистор, причому емітер транзистора зворотної провідності підключений до додатного полюса джерела постійної напруги, колектор з'єднаний з анодом третього діода, база з'єднана з другими виводами сьомого і восьмого резисторів, а емітер четвертого вихідного транзистора підключений до загальної шини джерела постійної напруги, колектор підключений до другого виходу пристрою, а база з'єднана з другим виводом шостого резистора і через дев'ятий резистор підключена до загальної шини джерела постійної напруги. На кресленні представлено схему логічного елемента. Пристрій містить додатний полюс 5 і загальну шину 18 джерела постійної напруги, перший 6, другий 7 входи і перший 13, другий 20 виходи пристрою, перший 1, другий 2 вхідні транзистори, перший 8, другий 9 проміжні транзистори, перший 11, другий 22, третій 15, четвертий 25, п'ятий 23 вихідні транзистори, транзистор зворотної провідності 19, перший 12, другий 16, третій 27 діоди, перший 3, другий 4, третій 10, четвертий 14, п'ятий 21, шостий 17, сьомий 24, восьмий 26 резистори, дев'ятий резистор 28, причому емітери першого 1 і другого 2 вхідних транзисторів з'єднані відповідно з першим 6 другим 7 входами пристрою, бази через перший 3 і другий 4 резистори підключені до додатного полюса 5 джерела постійної напруги, колектори з'єднані з базами відповідно першого 8 і другого 9 проміжних транзисторів, колектори яких через третій резистор 10 підключені до додатного полюса 5 джерела постійної напруги і з'єднані з базами першого 11 і третього 15 вихідних транзисторів, колектор третього вихідного транзистора 15 підключений до додатного полюса 5 джерела постійної напруги, емітер з'єднаний з анодом другого діода 16, катод якого з'єднаний з першим виводом шостого резистора 17, другий вивід якого через дев'ятий резистор 28 підключений до загальної шини джерела постійної напруги 18 і з'єднаний з базою четвертого вихідного транзистора 25, емітер якого підключений до загальної шини 18 джерела постійної напруги, колектор підключений до другого виходу пристрою 20 і з'єднаний з катодом третього діода 27, анод якого з'єднаний з колектором транзистора зворотної провідності 19, емітер якого підключений до додатного полюса 5 джерела постійної напруги, база з'єднана з другими виводами восьмого 26 і сьомого 24 резисторів, перший вивід восьмого резистора 26 підключений до додатного полюса 5 джерела постійної напруги, а перший вивід сьомого резистора 24 з'єднаний з колектором п'ятого вихідного транзистора 23, емітер якого підключений до загальної шини 18 джерела постійної напруги, база через п'ятий резистор 21 підключена до загальної шини 18 джерела постійної напруги і з'єднана з емітерами першого 8, другого 9 проміжних транзисторів і базою другого вихідного транзистора 22, емітер якого підключений до загальної шини 18 джерела постійної напруги, колектор підключений до першого виходу пристрою 13 і з'єднаний з катодом першого діода 12, анод якого з'єднаний з емітером першого вихідного транзистора 11, колектор якого через четвертий резистор 14 підключений до додатного полюса 5 джерела постійної напруги. Пристрій працює наступним чином. Нехай в початковому стані на першому 6 і другому 7 входах пристрою присутній низький потенціал, що відповідає рівням логічних нулів на першому 6, другому 7 входах. В цьому випадку перший 1, другий 2 вхідні транзистори відкриваються за рахунок струму від додатного полюса 5 джерела постійної напруги через перший 3 і другий 4 резистори і відкриті емітерні переходи першого 1, другого вхідних транзисторів, на які подано рівень логічного нуля. На базах відкритих першому 1, другому 2 вхідних транзисторів низький потенціал UБ11,0 В, якого недостатньо, щоб відкрити перший 8, другий 9 проміжні транзистори, де треба потенціал на базах вхідних транзисторів 1, 2 UБ22,1 В для відкривання першого 8, другого 9 проміжних транзисторів. Це призводить до закритого стану першого 8, другого 9 проміжних транзисторів, на колекторах яких присутній високий потенціал, тому що вони підключені через третій резистор 10 до додатного полюса 5 джерела постійної напруги, що приводе до відкритого стану першого 11, третього 15 вихідних транзисторів за рахунок протікання струму від додатного полюса 5 джерела постійної напруги через третій резистор 10 в бази першого 11, третього 15 вихідних транзисторів. Струм емітера відкритого третього вихідного транзистора 15 через прямо включений другий діод 16 потрапляє в подільник напруги на шостому 17 і дев'ятому 28 резисторах, де створює падіння напруги UБЕ0,7 В на дев'ятому резисторі 28, який підключено паралельно емітерному переходу четвертого вихідного транзистора 25, що призводить до 2 UA 102621 U 5 10 15 20 25 відкритого стану четвертого вихідного транзистора 25. Через невеликий опір відкритого четвертого вихідного транзистора 25 другий вихід пристрою 20 підключено до загальної шини 18 джерела постійної напруги. Через невеликий опір відкритого першого вихідного транзистора 11, емітерний струм якого відкриває прямо включений перший діод 12, перший вихід пристрою 13 підключено до додатного полюса 5 джерела постійної напруги. На емітерах закритих першого 8, другого 9 проміжних транзисторів і базах другого 23 вихідних транзисторів присутній низький потенціал, тому що вони підключені через п'ятий резистор 21 до загальної шини 18 джерела постійної напруги, що призводе до закритого стану другого 22, п'ятого 23 вихідних транзисторів. Перший вихід пристрою 13 відключено від загальної шини 18 джерела постійної напруги великим опором закритого другого вихідного транзистора 22. Великий опір закритого п'ятого вихідного транзистора послідовно підключено до подільника напруги на восьмому 26, сьомому 27 резисторах і струм від додатного полюса 5 джерела постійної напруги на восьмому 26, сьомому 27 резисторах не тече, що призводе до закритого стану третього діода 27 і транзистора зворотної провідності 19, емітерний перехід якого паралельно підключений до восьмого резистора 26. Другий вихід пристрою 20 відключено від додатного полюса 5 джерела постійної напруги великим опором закритого транзистора зворотної провідності і закритого третього діода 27. Таким чином, перший вихід пристрою 13 через невеликий опір відкритого першого вихідного транзистора 11 і відкритого першого діода 12 підключено до додатного полюса 5 джерела постійної напруги і відключено від загальної шини 18 джерела постійної напруги великим опором закритого другого вихідного транзистора 22, що відповідає високому потенціалу на першому виході пристрою 13, тобто логічній одиниці. Другий вихід пристрою 20 через невеликий опір відкритого четвертого вихідного транзистора 25 підключено до загальної шини 18 джерела постійної напруги і відключено від додатного полюса 5 джерела постійної напруги великим опором закритого транзистора зворотної провідності 19 і закритого третього діода 27, що відповідає низькому потенціалу на другому виході пристрою 20, тобто логічному нулю. Але логічна одиниця на першому виході пристрою 13 формується через час 1 , що 13 дорівнює В 1 1 З З , 13 8 22 30 (1) В де 1 - час відкривання першого вхідного транзистора 1; З , З - час закривання першого проміжного транзистора 8 і другого вихідного транзистора 8 22 22. Логічний нуль на другому виході пристрою 20 формується через час 0 , що дорівнює 20 В З 0 1 З З 19 , 20 8 23 35 40 З де З ,19 - час закривання п'ятого 23 вихідного транзистора і транзистора зворотної 23 провідності 19. Вважаємо час закривання другого 22, п'ятого 23 вихідних транзисторів однаковим, тому що їх бази з'єднані, емітери підключені до загальної шини 18 джерела постійної напруги і час розсмоктування неосновних носіїв заряду в базах цих транзисторів 22, 23 можна вважати однаковим, та можна, також, нехтувати часом закривання третього діода 27 в порівнянні з часом закривання будь-якого з транзисторів, з урахуванням виразів (1), (2) маємо наступний вираз З 0 1 19 , 20 13 45 50 (2) (3) тобто нульовий сигнал на другому виході пристрою 20 з'являється пізніше, ніж логічна одиниця на першому виході пристрою 13, на час закривання транзистора зворотної провідності 19. Якщо на одному з входів пристрою, першому 6 або другому 7, присутня логічна одиниця, то один з вхідних транзисторів перший 1 або другий 2 (або обидва вхідних транзистори 1, 2) знаходиться в інверсному активному режимі і його струм колекторного переходу, що визначається величиною опорів першого 3 або другого 4 резисторів, тече в базу першого 8 або другого 9 проміжних транзисторів (або обох проміжних транзисторів 8, 9), що приводе до відкритого стану першого 8 або другого 9 проміжних транзисторів (або обох проміжних 3 UA 102621 U 5 10 15 20 25 транзисторів 8, 9). Емітерний струм відкритого першого 8 або другого 9 проміжного транзистора створює на п'ятому резисторі 21 падіння напруги 0,7 В, якого достатньо, щоб відкрити емітерні переходи другого 22 і п'ятого 23 вихідних транзисторів, що призводить до відкритого стану другого 22, п'ятого 23 вихідних транзисторів. Перший вихід пристрою 13 підключений до загальної шини 18 джерела постійної напруги через невеликий опір відкритого другого вихідного транзистора 22. На колекторі відкритого п'ятого вихідного транзистора 23 низький потенціал, приблизно 0,3 В і через подільник напруги на восьмому 26, сьомому 24 резисторах тече струм, який створює падіння напруги 0,7 В на восьмому резисторі, який підключений паралельно емітерному переходу транзистора зворотної провідності 19, що приводе до відкритого стану транзистора зворотної провідності 19 і прямо включеного третього діода 27. Другий вихід пристрою 20 підключений до додатного полюса 5 джерела постійної напруги через невеликий опір відкритого транзистора зворотної провідності 19 і відкритого третього діода 27. Низький потенціал колектора відкритого першого 8 або другого 9 проміжного транзистора приводе до закритого стану першого 11, третього 15, четвертого 25 вихідних транзисторів, першого 12, другого 16 діодів, тому що в бази першого 11, третього 15 вихідних транзисторів не надходить струм додатного полюса 5 джерела постійної напруги через третій резистор 10. Перший вихід пристрою 13 відключено від додатного полюса 5 джерела постійної напруги великим опором закритого першого вихідного транзистора 11 і закритого першого діода 12. Другий вихід пристрою 20 відключено від загальної шини 18 джерела постійної напруги великим опором закритого четвертого вихідного транзистора 25. Таким чином, на першому виході пристрою 13 логічний нуль, а на другому виході пристрою 20 логічна одиниця, якщо на одному з входів пристрою 6, 7 присутня логічна одиниця. Вважаємо час закривання першого 11, третього 15 вихідних транзисторів приблизно однаковим, тому що їх бази з'єднані і час розсмоктування неосновних носіїв заряду в базі можна вважати однаковим та можна нехтувати часом закривання першого 12, другого 16 діодів, в порівнянні з часом відкриття будь-якого з транзисторів, то аналогічно до виразів (1-3) можна записати таке рівняння: 0 1 13 З , 20 25 30 35 (4) 0 де 1 ,13 - час формування одиночного сигналу на другому виході пристрою 20 і нульового 20 сигналу на першому виході пристрою 13, а З - час закривання четвертого вихідного 25 транзистора 25. Одиничний сигнал на другому виході пристрою 20 з'являється пізніше, ніж нульовий сигнал на першому виході пристрою 13 на величину часу закривання четвертого вихідного транзистора 25. Підбором відповідних номіналів третього 10, п'ятого 21, шостого 17, дев'ятого 28, восьмого 26, сьомого 24 резисторів можна забезпечити такі рівняння З 19 З , 25 0( 1(0 ) 131) , 20 40 45 (5) (6) тобто одиничний (нульовий) сигнал на другому виході пристрою 20 з'являється з затримкою відносно нульового (одиничного) сигналу на першому виході пристрою 13. Перший діод 12 використовується для того, щоб забезпечити закритий стан першого вихідного транзистора 11, якщо відкритий перший 8 або другий 9 проміжні транзистори. Третій діод 27 використовується для того, щоб забезпечити рівні значення рівнів логічної одиниці на першому 13 і другому 20 виходах пристрою. Четвертий резистор 14 використовується для обмеження величини вихідного струму при перемиканні логічного елемента на першому виході пристрою 11. Стан входів 6, 7 і виходів 13, 20 логічного елемента зведено в таблицю. 4 UA 102621 U Таблиця № п/п Входи Виходи Час формування сигналів на виходах 13 20 13 20 0 0 1 0 1 13 0 1 20 13 2 0 1 0 1 0 13 0 1 13 20 3 1 0 0 1 0 13 0 1 13 20 4 10 7 1 5 6 1 1 0 1 0 13 0 1 13 20 З таблиці бачимо, що логічний елемент реалізує на першому виході пристрою 13 логічну функцію АБО-НІ, а на другому виході пристрою 20 логічну функцію АБО, але сигнал на другому виході пристрою 20 з'являється із затримкою відносно появи сигналу на першому виході пристрою 13. Таким чином, запропонований логічний елемент має більш широкі функціональні можливості, тому що він дозволяє реалізувати на другому виході пристрою 20 пряму логічну функцію АБО із затримкою часу відносно інверсної логічної функції АБО-НІ, що реалізована на першому виході пристрою 19, що дозволяє використовувати цей логічний елемент для синхронізації (узгодження) цифрових пристроїв різної швидкодії. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 15 20 25 30 35 40 Логічний елемент, який містить джерело постійної напруги, перший, другий входи, перший, другий виходи пристрою, перший, другий вхідні транзистори, перший, другий проміжні транзистори, перший, другий, третій, четвертий, п'ятий вихідні транзистори, транзистор зворотної провідності, перший, другий, третій діоди, перший, другий, третій, четвертий, п'ятий, шостий, сьомий, восьмий резистори, причому емітери першого і другого вхідних транзисторів з'єднані відповідно з першим і другим входами пристрою, бази через перший і другий резистори підключені до додатного полюса джерела постійної напруги, а їх колектори з'єднані з базами відповідно першого і другого проміжних транзисторів, колектори яких через третій резистор підключені до додатного полюса джерела постійної напруги і з'єднані з базами першого і третього вихідних транзисторів, колектор третього вихідного транзистора підключений до додатного полюса джерела постійної напруги, емітер з'єднаний з анодом другого діода, катод якого з'єднаний з першим виводом шостого резистора, а колектор першого вихідного транзистора через четвертий резистор підключений до додатного полюса джерела постійної напруги, емітер з'єднаний з анодом першого діода, катод якого підключений до першого виходу пристрою і з'єднаний з колектором другого вихідного транзистора, емітер якого підключений до загальної шини джерела постійної напруги, а база через п'ятий резистор підключена до загальної шини джерела постійної напруги та з'єднана з емітерами першого, другого проміжних транзисторів і базою п'ятого вихідного транзистора, емітер якого підключений до загальної шини джерела постійної напруги, колектор з'єднаний з першим виводом сьомого резистора, а, також, перший вивід восьмого резистора підключений до додатного полюса джерела постійної напруги і катод третього діода підключений до другого виходу пристрою, який відрізняється тим, що додатково введено дев'ятий резистор, причому емітер транзистора зворотної провідності підключений до додатного полюса джерела постійної напруги, колектор з'єднаний з анодом третього діода, база з'єднана з другими виводами сьомого і восьмого резисторів, а емітер четвертого вихідного транзистора підключений до загальної шини джерела постійної напруги, колектор підключений до другого виходу пристрою, а база з'єднана з другим виводом шостого резистора і через дев'ятий резистор підключена до загальної шини джерела постійної напруги. 5 UA 102621 U Комп’ютерна верстка М. Мацело Державна служба інтелектуальної власності України, вул. Василя Липківського, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 6

ДивитисяДодаткова інформація

Назва патенту англійськоюLogical component

Автори англійськоюStronskyi Viktor Volodymyrovych

Назва патенту російськоюЛогический элемент

Автори російськоюСтронский Виктор Владимирович

МПК / Мітки

МПК: H03K 19/088

Код посилання

<a href="https://ua.patents.su/8-102621-logichnijj-element.html" target="_blank" rel="follow" title="База патентів України">Логічний елемент</a>

Попередній патент: Логічний елемент

Наступний патент: Датчик тиску з віброкомпенсацією

Випадковий патент: Пристрій регулювання вологості паперового полотна