Логічний елемент

Номер патенту: 83366

Опубліковано: 10.09.2013

Автори: Тромсюк Володимир Дмитрович, Стронський Віктор Володимирович, Кичак Василь Мартинович

Формула / Реферат

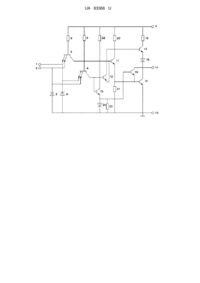

Логічний елемент, який містить джерело постійної напруги, перший, другий входи і вихід пристрою, перший, другий вхідні двоемітерні транзистори, перший, другий вхідні діоди, перший, другий, третій проміжні транзистори, перший і другий вихідні транзистори, перший, другий вхідні резистори, перший і другий проміжні резистори, вихідний резистор, вихідний діод, причому перший і другий емітери першого вхідного двоемітерного транзистора підключені до першого і другого входів пристрою та з'єднані з катодами першого та другого вхідних діодів, аноди яких підключені до загальної шини джерела постійної напруги, база першого вхідного двоемітерного транзистора через перший вхідний резистор підключена до додатного полюса джерела постійної напруги, а колектор з'єднаний з базою першого проміжного транзистора, емітер якого через другий проміжний резистор підключений до загальної шини джерела постійної напруги та з'єднаний з базою першого вихідного транзистора, емітер якого підключений до загальної шини джерела постійної напруги, а колектор підключений до виходу пристрою та з'єднаний з катодом вихідного діода, анод якого з'єднаний з емітером другого вихідного транзистора, колектор якого через вихідний резистор підключений до додатного полюса джерела постійної напруги, а база через перший проміжний резистор підключена до додатного полюса джерела постійної напруги і з'єднана з колекторами першого і другого проміжних транзисторів, база другого проміжного транзистора з'єднана з колектором другого вхідного двоемітерного транзистора, база якого через другий вхідний резистор підключена до додатного полюса джерела постійної напруги, який відрізняється тим, що додатково введено проміжний діод, третій і четвертий проміжні резистори, третій вихідний транзистор, причому перший і другий емітери другого вхідного двоемітерного транзистора підключені до першого і другого входів пристрою, а колектор з'єднаний з базою третього проміжного транзистора, колектор якого через третій проміжний резистор підключений до додатного полюса джерела постійної напруги, а емітер через четвертий проміжний резистор підключений до загальної шини джерела постійної напруги і з'єднаний з анодом проміжного діода, катод якого підключений до загальної шини джерела постійної напруги та з'єднаний з базою третього вихідного транзистора, емітер якого з'єднаний з базою першого вихідного транзистора, а колектор підключений до колектора першого вихідного транзистора і виходу пристрою, а емітер другого проміжного транзистора з'єднаний з базою першого проміжного транзистора.

Текст

Реферат: UA 83366 U UA 83366 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до мікроелектроніки і обчислювальної техніки та призначена для побудови відмовостійких цифрових пристроїв. Відомий інвертор, в якому використовується послідовно-паралельне з'єднання чотирьох однотипних транзисторів для усунення відмов, внаслідок короткого замикання емітерних переходів будь-якого з чотирьох транзисторів містить джерело постійної напруги, має вхід, вихід та складається з чотирьох вхідних резисторів, чотирьох прямо включених захисних діодів, чотирьох резисторів зміщення, чотирьох транзисторів підсилювального каскаду, трьох паралельно включених резисторів колекторного навантаження. Схему умовно поділимо на ліву частину на першому, другому транзисторах підсилювального каскаду та праву частину на третьому, четвертому транзисторах підсилювального каскаду. Тоді в стані логічної одиниці на вході в разі короткого замикання одного з емітерних переходів першого або другого транзисторів підсилювальних каскадів, перший або другий транзистор підсилювального каскаду переходить з відкритого у закритий стан та працює права половина схеми на відкритих третьому, четвертому транзисторах підсилювального каскаду та на виході пристрою стан логічного нуля не змінюється [див. Белецкий В.В. Теория и практические методы резервирования радиоэлектронной аппаратуры. - М: Энергия, 1997, рис. 3.2в, C. 135]. Недоліком такого пристрою є те, що навантаження на праву половину схеми збільшується майже в два рази, що знижує відмовостійкість схеми після першої відмови внаслідок короткого замикання одного з емітерних переходів транзисторів. Крім цього, основний та резервний елементи схеми постійно включені, що знижує відмовостійкість схеми, тому що за час до першої відмови внаслідок короткого замикання одного з емітерних переходів транзисторів відмовостійкість резервних транзисторів знижується. За прототип вибрано логічний елемент [див. Соломатин Н. М. Логические элементы ЭВМ. М.: Высшая школа, 1980, рис. 3.6ж, C. 92], який містить три вхідних двоемітерних транзистора, шість вхідних діодів, вихідний діод, три вхідних резистори, два проміжних резистори, вихідний резистор, три проміжних транзистора, два вихідних транзистора, причому джерело постійної напруги, перший, другий, третій, четвертий, п'ятий, шостий входи пристрою та його вихід утворені першим, другим, третім вхідними двоемітерними транзисторами, першим, другим, третім, четвертим, п'ятим, шостим вхідними діодами, вихідним діодом, першим, другим, третім проміжними транзисторами, першим, другим вихідними транзисторами, першим, другим, третім вхідними резисторами, першим, другим проміжними резисторами, вихідним резистором, причому перший, другий емітери першого, другого, третього вхідних двоемітерних транзисторів підключені до першого, другого, третього, четвертого, п'ятого, шостого входів пристрою та катодів першого, другого, третього, четвертого, п'ятого, шостого вхідних діодів, відповідно, аноди яких підключені до загальної шини джерела постійної напруги, бази першого, другого, третього вхідних двоемітерних транзисторів через перший, другий, третій вхідні резистори підключені до додатного полюса джерела постійної напруги, колектори з'єднані з базами, відповідно, першого, третього, другого, проміжних транзисторів, які через другий проміжний резистор підключені до від'ємного полюса джерела постійної напруги та з'єднані з базою першого вихідного транзистора, емітер якого підключений до загальної шини джерела постійної напруги, колектор підключений до виходу пристрою і з'єднаний з катодом вихідного діода, анод якого з'єднаний з емітером другого вихідного транзистора, колектор якого через перший проміжний резистор підключений до додатного полюса джерела постійної напруги, база через четвертий резистор підключена до додатного полюса джерела постійної напруги і з'єднана з колекторами першого, другого, третього проміжних транзисторів. Недоліком пристрою є відсутність захисту від короткого замикання емітерних переходів проміжного транзистора і першого вихідного транзистора, що знижує відновостійкість логічного елемента. В основу корисної моделі поставлена задача створення такого логічного елемента, в якому за рахунок введення нових елементів і зв'язків між ними знижується відновостійкість пристрою, що призводить до підвищення надійності роботи цифрових пристроїв. Поставлена задача вирішується тим, що в логічний елемент, який містить джерело постійної напруги, перший, другий входи і вихід пристрою, перший, другий вхідні двоемітерні транзистори, перший, другий вхідні діоди, перший, другий, третій проміжні транзистори, перший і другий вихідні транзистори, перший, другий вхідні резистори, перший і другий проміжні резистори, вихідний резистор, вихідний діод, причому перший і другий емітери першого вхідного двоемітерного транзистора підключені до першого і другого входів пристрою та з'єднані з катодами першого та другого вхідних діодів, аноди яких підключені до загальної шини джерела постійної напруги, база першого вхідного двоемітерного транзистора через перший вхідний резистор підключена до додатного полюса джерела постійної напруги, а колектор з'єднаний з 1 UA 83366 U 5 10 15 20 25 30 35 40 45 50 55 60 базою першого проміжного транзистора, емітер якого через другий проміжний резистор підключений до загальної шини джерела постійної напруги та з'єднаний з базою першого вихідного транзистора, емітер якого підключений до загальної шини джерела постійної напруги, а колектор підключений до виходу пристрою та з'єднаний з катодом вихідного діода, анод якого з'єднаний з емітером другого вихідного транзистора, колектор якого через вихідний резистор підключений до додатного полюса джерела постійної напруги, а база через перший проміжний резистор підключена до додатного полюса джерела постійної напруги і з'єднана з колекторами першого і другого проміжних транзисторів, база другого проміжного транзистора з'єднана з колектором другого вхідного двоемітерного транзистора, база якого через другий вхідний резистор підключена до додатного полюса джерела постійної напруги, введено проміжний діод, третій і четвертий проміжні резистори, третій вихідний транзистор, причому перший і другий емітери другого вхідного двоемітерного транзистора підключені до першого і другого входів пристрою, а колектор з'єднаний з базою третього проміжного транзистора, колектор якого через третій проміжний резистор підключений до додатного полюса джерела постійної напруги, а емітер через четвертий проміжний резистор підключений до загальної шини джерела постійної напруги і з'єднаний з анодом проміжного діода, катод якого підключений до загальної шини джерела постійної напруги та з'єднаний з базою третього вихідного транзистора, емітер якого з'єднаний з базою першого вихідного транзистора, а колектор підключений до колектора першого вихідного транзистора і виходу пристрою, а емітер другого проміжного транзистора з'єднаний з базою першого проміжного транзистора. На кресленні представлено схему логічного елемента. Пристрій містить додатний полюс 7 і загальну шину 10 джерела постійної напруги, перший 1, другий 2 входи і вихід 14 пристрою, перший 3, другий 4 вхідні двоемітерні транзистори, перший 5, другий 6 вхідні діоди, перший 11, другий 12, третій 13 проміжні транзистори, перший 17, другий 18, третій 19 вихідні транзистори, перший 8, другий 9 вхідні резистори, перший 20, другий 21, третій 22, четвертий 23 проміжні резистори, вихідний діод 15, вихідний резистор 16, проміжний діод 24, причому перший і другий емітери першого 3 і другого 4 вхідних двоемітерних транзисторів підключені до першого 1 і другого 2 входів пристрою та з'єднані з катодами першого 5 та другого 6 вхідних діодів, аноди яких підключені до загальної шини джерела постійної напруги 10, бази першого 3 і другого 4 вхідних двоемітерних транзисторів, відповідно, через перший 8 і другий 9 вхідні резистори підключені до додатного полюса джерела постійної напруги 7, колектор першого вхідного двоемітерного транзистора 3 з'єднаний з базою першого проміжного транзистора 11, емітер якого через другий проміжний резистор 21 підключений до загальної шини джерела постійної напруги 10 та з'єднаний з базою першого вихідного транзистора 17, емітер якого підключений до загальної шини джерела постійної напруги 10, а колектор підключений до виходу пристрою 14 та з'єднаний з колектором третього вихідного транзистора 19 і катодом вихідного діода 15, анод якого з'єднаний з емітером другого вихідного транзистора 18, колектор якого через вихідний резистор 16 підключений до додатного полюса джерела постійної напруги 7, а база через перший проміжний резистор 20 підключена до додатного полюса джерела постійної напруги 7 і з'єднана з колекторами першого 11 і другого 12 проміжних транзисторів, база другого проміжного транзистора 12 з'єднана з колектором другого вхідного двоемітерного транзистора 4 і базою третього проміжного транзистора 13, колектор якого через третій проміжний резистор 22 підключений до додатного полюса джерела постійної напруги 7, а емітер через четвертий проміжний резистор 23 підключений до загальної шини джерела постійної напруги 10 і з'єднаний з анодом проміжного діода 24, катод якого підключений до загальної шини джерела постійної напруги 10 та з'єднаний з базою третього вихідного транзистора 19, емітер якого з'єднаний з базою першого вихідного транзистора 17, а колектор підключений до колектора першого вихідного транзистора 17 і виходу пристрою 14, емітер другого проміжного транзистора 12 з'єднаний з базою першого проміжного транзистора 11. Пристрій працює наступним чином. При низькій напрузі на одному з емітерів першого 3 і другого 4 вхідних двоемітерних транзисторів, перший 5 і другий 6 вхідні діоди будуть обмежувати амплітуду від'ємних сигналів, що відповідає рівню логічного нуля на одному з входів, струм від додатного полюса джерела постійної напруги 7 тече через перший 8 і п'ятий 9 вхідні резистори і відкриті емітерні переходи першого 3, другого 4 вхідних двоемітерних транзисторів на які подано рівень логічного нуля. В результаті перший 3 і другий 4 двоемітерні транзистори відкриваються і напруга на їх базах не достатня, щоб відкрити перший 11 і третій 13 проміжні транзистори, перший вихідний транзистор 17 та прямо включений проміжний діод 24, причому в базу і колектор другого вихідного транзистора 18 тече струм, від додатного полюса джерела постійної напруги 7, 2 UA 83366 U 5 10 15 20 25 30 35 40 45 відповідно, через перший проміжний резистор 20 і вихідний резистор 16, що призводить до відкритого стану другого вихідного транзистора 18 і вихідного діода 15. На виході 14 пристрою логічна одиниця. В цьому стані перший 11, другий 12, проміжні транзистори, перший 17 і третій 19 вихідні транзистори закриті та вихід 14 пристрою через великий опір закритого першого вихідного транзистора 17 відключений від загальної шини джерела постійної напруги 10. Якщо на перший 1, другий 2 входи подано високу напругу, що відповідає рівню логічної одиниці на входах, то перший 5 і другий 6 вхідні діоди будуть обмежувати амплітуду від'ємних сигналів, при цьому перший 3 і другий 4 вхідні двоемітерні транзистори працюють в інверсному активному режимі і напрузі на їх базах U Б = 2,1 В достатньої для відкривання колекторних переходів першого 3 і другого 4 вхідних двоемітерних транзисторів, емітерних переходів першого 11 і третього 13 проміжних транзисторів, першого вихідного транзистора 17, та прямо включеного проміжного діода 24 і паралельно ввімкненого четвертого проміжного резистора 23. Це призводить до відкривання першого 11 і третього 13 проміжних транзисторів і першого вихідного транзистора 17. На колекторах відкритих першого 11 і третього 13 проміжних транзисторів низький потенціал UК = UБЕ + UКЕ, де UБЕ - напруга переходу база емітер і UКЕ напруга переходу колектор емітер, UК = 1,0 В, якого не достатньо для відкривання емітерного переходу другого вихідного транзистора 18 і прямо включеного вихідного діода 15. Вихід 14 пристрою через малий опір переходу колектор-емітер відкритого першого вихідного транзистора 17 підключений до загальної шини джерела постійної напруги 10, що відповідає стану логічного нуля на виході 14 пристрою. На базі та емітері третього вихідного транзистора 19 рівні потенціали UБ2 = UД = 0,7 В, UД - напруга відкривання проміжного діода 24, UЕ2 = UБЕ = 0,7 В, де UБЕ - напруга переходу база емітер, що обумовлює закритий стан третього вихідного транзистора 19. На базі та емітері другого проміжного транзистора 12 рівні потенціали U Б3 = 2UД = 1,4 В, UЕ3 = 2UБЕ = 1,4 В, що обумовлює закритий стан другого проміжного транзистора 12. Таким чином пристрій реалізує логічну функцію І-НI. Якщо в стані логічного нуля на виході 14 пристрою відбувається коротке замикання емітерного переходу першого проміжного транзистора 11, то в цьому випадку потенціал бази другого проміжного транзистора 12 залишається на рівні 1,4 В, а потенціал емітера зменшується до UБЕ = 0,7 В, що призводить до відкривання другого проміжного транзистора 12, який заміняє перший проміжний транзистор 11, що відмовив і замикається через другий проміжний резистор 21 на загальну шину джерела постійної напруги 10, тому відмова пристрою не спостерігається. Якщо в стані логічного нуля на виході 14 пристрою відбувається коротке замикання емітерного переходу першого вихідного транзистора 17, то перший вихідний транзистор 17 закривається і в цьому випадку потенціал третього вихідного транзистора 19 залишиться на рівні 0,7 В, а потенціал емітера зменшується до нульового значення, що призводить до відкривання третього вихідного транзистора 19, який заміняє перший вихідний транзистор 17, що відмовив, тому відмова пристрою не спостерігається. Потенціал баз другого 12 і третього 13 проміжних транзисторів залишається на рівні 1,4 В, а потенціал емітерів зменшується до UБЕ = 0,7 В, що призводить до відкривання другого 12 і третього 13 проміжних транзисторів, відповідно в базу третього проміжного транзистора тече струм через третій проміжний резистор 22 від додатного полюса джерела постійної напруги 7. Таким чином, в разі короткого замикання емітерного переходу першого проміжного транзистора 11 або емітерного переходу першого вихідного транзистора 17 відкриваються попередньо закриті другий проміжний 12 і третій вихідний 19 транзистори або другий проміжний транзистор 12 та відмова не спостерігається. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 50 55 60 Логічний елемент, який містить джерело постійної напруги, перший, другий входи і вихід пристрою, перший, другий вхідні двоемітерні транзистори, перший, другий вхідні діоди, перший, другий, третій проміжні транзистори, перший і другий вихідні транзистори, перший, другий вхідні резистори, перший і другий проміжні резистори, вихідний резистор, вихідний діод, причому перший і другий емітери першого вхідного двоемітерного транзистора підключені до першого і другого входів пристрою та з'єднані з катодами першого та другого вхідних діодів, аноди яких підключені до загальної шини джерела постійної напруги, база першого вхідного двоемітерного транзистора через перший вхідний резистор підключена до додатного полюса джерела постійної напруги, а колектор з'єднаний з базою першого проміжного транзистора, емітер якого через другий проміжний резистор підключений до загальної шини джерела постійної напруги та з'єднаний з базою першого вихідного транзистора, емітер якого підключений до загальної шини джерела постійної напруги, а колектор підключений до виходу пристрою та з'єднаний з катодом 3 UA 83366 U 5 10 15 вихідного діода, анод якого з'єднаний з емітером другого вихідного транзистора, колектор якого через вихідний резистор підключений до додатного полюса джерела постійної напруги, а база через перший проміжний резистор підключена до додатного полюса джерела постійної напруги і з'єднана з колекторами першого і другого проміжних транзисторів, база другого проміжного транзистора з'єднана з колектором другого вхідного двоемітерного транзистора, база якого через другий вхідний резистор підключена до додатного полюса джерела постійної напруги, який відрізняється тим, що додатково введено проміжний діод, третій і четвертий проміжні резистори, третій вихідний транзистор, причому перший і другий емітери другого вхідного двоемітерного транзистора підключені до першого і другого входів пристрою, а колектор з'єднаний з базою третього проміжного транзистора, колектор якого через третій проміжний резистор підключений до додатного полюса джерела постійної напруги, а емітер через четвертий проміжний резистор підключений до загальної шини джерела постійної напруги і з'єднаний з анодом проміжного діода, катод якого підключений до загальної шини джерела постійної напруги та з'єднаний з базою третього вихідного транзистора, емітер якого з'єднаний з базою першого вихідного транзистора, а колектор підключений до колектора першого вихідного транзистора і виходу пристрою, а емітер другого проміжного транзистора з'єднаний з базою першого проміжного транзистора. Комп’ютерна верстка Л. Ціхановська Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 4

ДивитисяДодаткова інформація

Автори англійськоюKychak Vasyl Martynovych

Автори російськоюКичак Василий Мартынович

МПК / Мітки

МПК: H03K 19/08

Код посилання

<a href="https://ua.patents.su/6-83366-logichnijj-element.html" target="_blank" rel="follow" title="База патентів України">Логічний елемент</a>

Попередній патент: Спосіб ремонту земляного полотна

Наступний патент: Спосіб корегування нерівномірності просідань під будівлями та спорудами на плитному фундаменті

Випадковий патент: Вібропоглинаючий полімерний матеріал та спосіб його одержання