Циклічний лічильник у фібоначчієвій системі числення

Номер патенту: 115994

Опубліковано: 10.05.2017

Формула / Реферат

Циклічний лічильник у фібоначчієвій системі числення, що має вхід встановлення у початковий стан, вхід тактових імпульсів, вхід одиничного потенціалу, N розрядів, N інформаційних виходів, та у кожному і-му розряді містить лічильний тригер, вхід С синхронізації якого з'єднаний зі входом тактових імпульсів лічильника, вхід R встановлення у початковий стан з'єднаний зі входом встановлення у початковий стан лічильника, а вихід з'єднаний з і-м інформаційним виходом лічильника, крім того, перший і другий розряди лічильника містять по одному логічному елементу І-НІ, а кожний розряд лічильника, починаючи з третього, містить перший і другий логічні елементи І-НІ, причому, перший вхід логічного елемента І-НІ першого розряду з'єднаний з прямим виходом лічильного тригера першого розряду, другий його вхід з'єднаний з прямим виходом лічильного тригера другого розряду, а вихід з'єднаний з Т-входом лічильного тригера першого розряду; перший вхід логічного елемента І-НІ другого розряду з'єднаний з інверсним виходом лічильного тригера першого розряду, другий його вхід з'єднаний з виходом першого логічного елемента І-НІ четвертого розряду, а вихід з'єднаний з Т-входом лічильного тригера другого розряду; у кожному і-му розряді лічильника, починаючи з третього, перший вхід першого логічного елемента І-НІ з'єднаний з інверсним виходом лічильного тригера і-го розряду, другий його вхід з'єднаний з прямим виходом лічильного тригера (і-і)-го розряду, третій вхід з'єднаний з прямим виходом лічильного тригера (і-2)-го розряду, а вихід з'єднаний з першим входом другого логічного елемента І-НІ і-го розряду, другий вхід другого логічного елемента І-НІ і-го розряду, крім N-го, з'єднаний з виходом першого логічного елемента І-НІ (і+1)-го розряду, третій вхід другого логічного елемента І-НІ і-го розряду, крім N-го та (N-1)-го, з'єднаний з виходом першого логічного елемента І-НІ (і+2)-го розряду, а вихід другого логічного елемента І-НІ і-го розряду з'єднаний з Т-входом лічильного тригера і-го розряду; другий і третій входи другого логічного елемента І-НІ N-го розряду та третій вхід другого логічного елемента І-НІ (N-1)-го розряду з'єднані з входом одиничного потенціалу лічильника, який відрізняється тим, що в нього введено логічний елемент І-НІ лічильника, причому прямий вихід лічильного тригера першого розряду з'єднаний з першим входом логічного елемента І-НІ лічильника, другий вхід якого з'єднаний з прямим виходом лічильного тригера другого розряду, третій вхід з'єднаний з прямим виходом лічильного тригера третього розряду, а вихід з'єднаний з третім входом логічного елемента І-НІ першого розряду, третім входом логічного елемента І-НІ другого розряду та четвертим входом другого логічного елемента І-НІ кожного розряду, починаючи з третього.

Текст

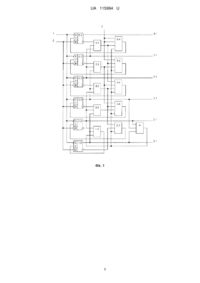

Реферат: UA 115994 U UA 115994 U 5 10 15 20 25 30 35 40 45 50 55 Корисна модель належить до обчислювальної техніки і автоматики та може бути використана у цифрових пристроях. Відомим аналогом є перешкодостійкий лічильник імпульсів Борисенко-Стахова [Патент на винахід UA 104939 С2 23/00 (2014/01) опублікований 25.03.2014 Бюл. № 6], що складається з регістра, що містить n тригерів і n схем І, перші входи яких сполучені з шиною тактових імпульсів, а виходи з входами установки в одиницю відповідних тригерів, а також має блок аналізу, що містить n-1 двовходові схеми І, блок диспозицій, що містить n-1 двовходові схеми І з інверторами на вході, блок контролю, що містить n-1 двовходові схеми І, які об'єднані схемою АБО, блок установки нуля, що містить n-1 двовходові схеми АБО і одну допоміжну схему І, до першого входу якої приєднана шина тактових імпульсів, при цьому входи установки в одиницю тригерів регістра сполучені з першими входами двовходових схем АБО сусідніх молодших розрядів блока установки нуля, виходи яких сполучені з входами установки в нуль відповідних тригерів і з другими входами схем АБО сусідніх молодших розрядів цього блока, до другого входу схеми АБО n-1 розряду і входу установки в нуль тригера n розряду підключений вихід допоміжної схеми І блока установки нуля, інверсні виходи кожного з тригерів регістра заведені на перший і другий входи відповідних йому двох двовходових схем 1 блока аналізу, прямий вихід кожного з перших n-1 тригерів заведений на другий вхід схеми І сусіднього старшого розряду регістра, прямий вихід тригера n розряду сполучений з другим входом допоміжної схеми І, виходи схеми І блока аналізу зв'язані через інвертори з першими і другими входами відповідних їм двох двовходових схем І блока диспозицій і з третім входом схеми І цього ж розряду регістра, вихід кожної з n-2 схем 1 блока диспозицій, починаючи з першого розряду, заведений на третій вхід сусідньої схеми І старшого розряду цього ж блока і четвертий вхід схеми І старшого розряду регістра, що стоїть через два розряди, вихід старшої n-1 схеми І блока диспозицій заведений на третій вхід допоміжної схеми І блока установки нуля, прямі виходи двох розміщених поруч тригерів заведені на перший і другий входи відповідних їм двох двовходових схем І блока контролю, виходи яких об'єднані схемою АБО. Недоліком аналога є великі апаратні витрати та низька швидкодія, яка визначається наявністю у схемі довгих шляхів розповсюдження сигналу через всі розряди на кожному такті. Найближчим аналогом до корисної моделі є цифро-аналоговий перетворювач, UA 94085 U H03M 1/46, опублікований 27.10.2014 Бюл. №20, в якому описано швидкодіючий лічильник у фібоначчієвій системі числення, що містить вхід встановлення у початковий стан, вхід тактових імпульсів, вхід одиничного потенціалу, N інформаційних виходів, та у кожному і-му розряді містить лічильний тригер, вхід С синхронізації якого з'єднаний зі входом тактових імпульсів лічильника, вхід R встановлення у початковий стан з'єднаний зі входом встановлення у початковий стан лічильника, а вихід з'єднаний з і-м інформаційним виходом лічильника, крім того, перший і другий розряди лічильника містять по одному логічному елементу 2І-НІ, а кожний розряд лічильника, починаючи з третього, містить перший і другий логічні елементи 3І-НІ, причому, перший вхід логічного елемента 2І-НІ першого розряду з'єднаний з прямим виходом лічильного тригера першого розряду, другий його вхід з'єднаний з прямим виходом лічильного тригера другого розряду, а вихід з'єднаний з Т-входом лічильного тригера першого розряду; перший вхід логічного елемента 2І-НІ другого розряду з'єднаний з інверсним виходом лічильного тригера першого розряду, другий його вхід з'єднаний з виходом першого логічного елемента 3І-НІ четвертого розряду, а вихід з'єднаний з Т-входом лічильного тригера другого розряду; у кожному і-му розряді лічильника, починаючи з третього, перший вхід першого логічного елемента 3І-НІ з'єднаний з інверсним виходом лічильного тригера і-го розряду, другий його вхід з'єднаний з прямим виходом лічильного тригера (і-і)-го розряду, третій вхід з'єднаний з прямим виходом лічильного тригера (і-2)-го розряду, а вихід з'єднаний з першим входом другого логічного елемента 3І-НІ і-го розряду; другий вхід другого логічного елемента 3І-НІ і-го розряду, крім N-го, з'єднаний з виходом першого логічного елемента 3І-НІ (і+1)-го розряду, третій вхід другого логічного елемента 3І-НІ і-го розряду, крім N-го та (N-l)-ro, з'єднаний з виходом першого логічного елемента 3І-НІ (і+2)-го розряду, а вихід другогологічного елемента 3І-НІ і-го розряду з'єднаний з Т-входом лічильного тригера і-го розряду; другий і третій входи другого логічного елемента 3І-НІ N-го розряду та третій вхід другого логічного елемента 3І-НІ (N-1)-го розряду з'єднані з входом одиничного потенціалу лічильника. Недоліком найближчого аналога є те, що при досягненні максимального коду "всі одиниці" подальша лічба зупиняється. В основу корисної моделі поставлена задача створення циклічного лічильника у фібоначчієвій системі числення, в якому за рахунок введення нових елементів та зв'язків організується режим циклічної лічби, що приводить до розширення функціональних 1 UA 115994 U 5 10 15 20 25 30 35 40 45 50 55 60 можливостей. В режимі циклічної лічби при досягненні лічильником максимального коду "всі одиниці" лічба продовжується далі з коду "всі нулі". Поставлена задача вирішується тим, що в циклічний лічильник у фібоначчієвій системі числення, який має вхід встановлення у початковий стан, вхід тактових імпульсів, вхід одиничного потенціалу, N розрядів, N інформаційних виходів, та у кожному і-му розряді містить лічильний тригер, вхід С синхронізації якого з'єднаний зі входом тактових імпульсів лічильника, вхід R встановлення у початковий стан з'єднаний зі входом встановлення у початковий стан лічильника, а вихід з'єднаний з і-м інформаційним виходом лічильника, крім того, перший і другий розряди лічильника містять по одному логічному елементу І-НІ, а кожний розряд лічильника, починаючи з третього, містить перший і другий логічні елементи І-НІ, причому, перший вхід логічного елемента І-НІ першого розряду з'єднаний з прямим виходом лічильного тригера першого розряду, другий його вхід з'єднаний з прямим виходом лічильного тригера другого розряду, а вихід з'єднаний з Т-входом лічильного тригера першого розряду; перший вхід логічного елемента І-НІ другого розряду з'єднаний з інверсним виходом лічильного тригера першого розряду, другий його вхід з'єднаний з виходом першого логічного елемента І-НІ четвертого розряду, а вихід з'єднаний з Т-входом лічильного тригера другого розряду; у кожному і-му розряді лічильника, починаючи з третього, перший вхід першого логічного елемента І-НІ з'єднаний з інверсним виходом лічильного тригера і-го розряду, другий його вхід з'єднаний з прямим виходом лічильного тригера (і-і)-го розряду, третій вхід з'єднаний з прямим виходом лічильного тригера (і-2)-го розряду, а вихід з'єднаний з першим входом другого логічного елемента І-НІ і-го розряду; другий вхід другого логічного елемента І-НІ і-го розряду, крім Afro, з'єднаний з виходом першого логічного елемента І-НІ (і+1)-го розряду, третій вхід другого логічного елемента І-НІ і-го розряду, крім N-го та (N-1)-го, з'єднаний з виходом першого логічного елемента 1-НІ (і+2)-го розряду, а вихід другого логічного елемента І-НІ і-го розряду з'єднаний з Т-входом лічильного тригера і-го розряду, другий і третій входи другого логічного елемента І-НІ N-го розряду та третій вхід другого логічного елемента І-НІ (N-1)-го розряду з'єднані з входом одиничного потенціалу лічильника, згідно з корисною моделлю, введено логічний елемент І-НІ лічильника, причому прямий вихід лічильного тригера першого розряду з'єднаний з першим входом логічного елемента І-НІ лічильника, другий вхід якого з'єднаний з прямим виходом лічильного тригера другого розряду, третій вхід з'єднаний з прямим виходом лічильного тригера третього розряду, а вихід з'єднаний з третім входом логічного елемента І-НІ першого розряду, третім входом логічного елемента І-НІ другого розряду та четвертим входом другого логічного елемента І-НІ кожного розряду, починаючи з третього. Корисна модель пояснюється кресленнями, де на фіг. 1 зображено схему шестирозрядного циклічного лічильника у фібоначчієвій системі числення. На фіг. 2 зображено часові діаграми роботи шестирозрядного циклічного лічильника у фібоначчієвій системі числення. На діаграмах не враховані затримки часу на перемикання логічних елементів і тригерів. Циклічний лічильник у фібоначчієвій системі числення має шість розрядів, шість інформаційних виходів 1.1÷6.1, вхід 1 тактових імпульсів, вхід 2 встановлення у початковий стан, вхід 3 одиничного потенціалу, містить логічний елемент 4 І-НІ лічильника, лічильні тригери 1.2÷6.2, логічний елемент 1.3 І-НІ першого розряду, логічний елемент 2.3 І-НІ другого розряду, перші логічні елементи 3.3÷6.3 І-НІ розрядів з третього по шостий та другі логічні елементи 3.4÷6.4 І-НІ розрядів з третього по шостий. Вхід 1 тактових імпульсів з'єднаний з С-входами всіх лічильних тригерів 1.2÷6.2, вхід 2 встановлення у початковий стан з'єднаний з R-входами всіх лічильних тригерів 1.2÷6.2. Прямі виходи лічильних тригерів 1.2÷6.2 розрядів з першого по шостий з'єднані з інформаційними виходами 1.1÷6.1 відповідно. Прямий вихід лічильного тригера 1.2 першого розряду з'єднаний з першим входом логічного елемента 1.3 І-НІ першого розряду. Інверсний вихід лічильного тригера 1.2 першого розряду з'єднаний з першим входом логічного елемента 2.3 І-НІ другого розряду. Прямий вихід лічильного тригера 2.2 другого розряду з'єднаний з другим входом логічного елемента 1.3 І-НІ першого розряду. Інверсні виходи лічильних тригерів 3.2÷6.2 розрядів з третього по шостий з'єднані з першими входами перших логічних елементів 3.3÷6.3 І-НІ розрядів з третього по шостий відповідно. Прямі виходи лічильних тригерів 2.2÷5.2 розрядів з другого по п'ятий з'єднані з другими входами перших логічних елементів 3.3÷6.3 І-НІ розрядів з третього по шостий відповідно. Прямі виходи лічильних тригерів 1.2÷4.2 розрядів з першого по четвертий з'єднані з третіми входами перших логічних елементів 3.3÷6.3 І-НІ розрядів з третього по шостий відповідно. Прямі виходи лічильних тригерів 1.2÷3.2 першого, другого і третього розрядів з'єднані відповідно з першим, другим і третім входами логічного елемента 4 І-НІ лічильника. Виходи перших логічних елементів 3.3÷6.3 І-НІ розрядів з третього по шостий з'єднані з першими входами других логічних елементів 3.4÷6.4 І-НІ розрядів з третього по шостий відповідно. Виходи перших 2 UA 115994 U 5 10 15 20 25 30 35 40 45 50 55 логічних елементів 4.3÷6.3 І-НІ розрядів з четвертого по шостий з'єднані з другими входами других логічних елементів 3,4÷5.4 І-НІ розрядів з третього по п'ятий відповідно. Виходи перших логічних елементів 5.3 та 6.3 І-НІ п'ятого і шостого розрядів з'єднані з третіми входами других логічних елементів 3.4 та 4.4 І-НІ третього і четвертого розрядів відповідно. Вихід першого логічного елемента 4.3 І-НІ четвертого розряду з'єднаний з другим входом логічного елемента 2.3 І-НІ другого розряду. Вхід 3 одиничного потенціалу з'єднаний з другим і третім входами другого елемента 6.4 І-НІ шостого розряду та третім входом другого елемента 5.4 І-НІ п'ятого розряду. Вихід логічного елемента 4 І-НЕ лічильника з'єднаний з третім входом логічного елемента 1.3 І-НІ першого розряду, третім входом логічного елемента 2.3 І-НІ другого розряду та четвертими входами логічних елементів 3.4÷6.4 І-НЕ розрядів з третього по шостий. Виходи логічних елементів 1.3 та 2.3 І-НІ першого і другого розрядів з'єднані з Т-входами лічильних тригерів 1.2 та 2.2 першого і другого розрядів відповідно. Виходи других логічних елементів 3.4÷6.4 І-НІ розрядів з третього по шостий з'єднані з Т-входами лічильних тригерів 3.2÷6.2 розрядів з третього по шостий відповідно. Лічильник працює таким чином. Перед початком роботи одиничний потенціал зі входу 3 одиничного потенціалу надходить на третій вхід другого логічного елемента 5.4 І-НІ п'ятого розряду, другий і третій входи другого логічного елемента 6.4 І-НІ шостого розряду. Робота починається з подання на вхід 2 початкового встановлення нульового сигналу, який надходить на R-входи лічильних тригерів 1.2÷2 розрядів з першого по шостий. Лічильні тригери 1.2÷6.2 розрядів з першого по шостий встановлюються у нульовий стан. У кожному і-му розряді нульовий сигнал з прямого виходу лічильного тригера 1.2 надходить на інформаційний вихід і.1 цього розряду. Нульові сигнали з прямих виходів лічильних тригерів 1.2÷6.2 розрядів з першого по шостий надходять на відповідні інформаційні виходи 1.1÷6.1 цих розрядів, на перший і другий входи логічного елемента 1.3 І-НІ першого розряду та другий і третій входи перших логічних елементів 3.3÷6.3 І-НІ розрядів з третього по шостий. На інформаційних виходах 6.1÷1.1 лічильника встановлюється код 000000. Одиничний сигнал з інверсного виходу лічильного тригера 1.2 першого розряду надходить на перший вхід логічного елемента 2.3 І-НІ другого розряду, на другий вхід якого надходить одиничний сигнал з виходу першого логічного елемента 4.3 І-НІ четвертого розряду. Одиничні сигнали з виходів перших логічних елементів 3.3÷6.3 І-НІ розрядів з третього по шостий надходять на перші входи других логічних елементів 3.4÷6.4 І-НІ розрядів з третього по шостий. Одиничні сигнали з виходів перших логічних елементів 4.3÷6.3 І-НІ розрядів з четвертого по шостий надходять на другі входи других логічних елементів 3.4÷5.4 І-НІ розрядів з третього по п'ятий. Одиничні сигнали з виходів перших логічних елементів 5.3 і 6.3 І-НІ п'ятого і шостого розрядів надходять на треті входи других логічних елементів 3.4÷4.4 І-НІ третього і четвертого розрядів. Нульові сигнали з прямих виходів лічильних тригерів 1.2÷3.2 розрядів з першого по третій надходять відповідно на перший, другий і третій входи логічного елемента 4 І-НІ, одиничний сигнал з виходу якого надходить на треті входи логічних елементів 1.3 і 2.3 І-НІ першого і другого розрядів та на четверті входи других логічних елементів 3.4÷6.4 І-НІ розрядів з третього по шостий. Одиничний сигнал з виходу логічного елемента 1.3 І-НІ першого розряду надходить на Т-вхід лічильного тригера 1.2 першого розряду. Нульові сигнали з виходів логічного елемента 2.3 І-НІ другого розряду та других логічних елементів 3.4÷6.4 І-НІ розрядів з третього по шостий надходять відповідно на Твходи лічильних тригерів 2.2÷6.2 розрядів з другого по шостий. При поданні на вхід 1 тактових імпульсів переднього фронту одиничного сигналу він надходить на С-входи лічильних тригерів 1.2÷6.2 розрядів з першого по шостий. Лічильні тригери розрядів 2.2÷6.2 розрядів з другого по шостий залишаються у нульовому стані, а лічильний тригер 1.2 першого розряду встановлюється в одиничний стан. На інформаційних виходах 6.1÷1.1 лічильника встановлюється код 000001. Подальша робота лічильника пояснюється за допомогою діаграм, наведених на фіг. 2. При встановленні у лічильнику коду 111111 на всі входи логічного елемента 4 І-НІ лічильника надходять одиничні сигнали. Нульовий сигнал з виходу цього елемента надходить на треті входи логічних елементів 1.3 і 2.3 І-НІ першого і другого розрядів та на четверті входи других логічних елементів 3.4÷6.4 І-НІ розрядів з третього по шостий. Одиничні сигнали з виходів цих елементів надходять на Т-входи лічильних тригерів 1.2÷6.2 розрядів з першого по шостий відповідно. При надходженні переднього фронту одиничного сигналу на С-входи лічильних тригерів 1.24-6.2 розрядів з першого по шостий вони встановлюються в нульовий стан. На інформаційних виходах 1.14-6.1 лічильника встановлюється код 000000, з якого далі циклічно починається лічба, що підтверджує вирішення поставленої задачі. 3 UA 115994 U ФОРМУЛА КОРИСНОЇ МОДЕЛІ 5 10 15 20 25 30 Циклічний лічильник у фібоначчієвій системі числення, що має вхід встановлення у початковий стан, вхід тактових імпульсів, вхід одиничного потенціалу, N розрядів, N інформаційних виходів, та у кожному і-му розряді містить лічильний тригер, вхід С синхронізації якого з'єднаний зі входом тактових імпульсів лічильника, вхід R встановлення у початковий стан з'єднаний зі входом встановлення у початковий стан лічильника, а вихід з'єднаний з і-м інформаційним виходом лічильника, крім того, перший і другий розряди лічильника містять по одному логічному елементу І-НІ, а кожний розряд лічильника, починаючи з третього, містить перший і другий логічні елементи І-НІ, причому, перший вхід логічного елемента І-НІ першого розряду з'єднаний з прямим виходом лічильного тригера першого розряду, другий його вхід з'єднаний з прямим виходом лічильного тригера другого розряду, а вихід з'єднаний з Т-входом лічильного тригера першого розряду; перший вхід логічного елемента І-НІ другого розряду з'єднаний з інверсним виходом лічильного тригера першого розряду, другий його вхід з'єднаний з виходом першого логічного елемента І-НІ четвертого розряду, а вихід з'єднаний з Т-входом лічильного тригера другого розряду; у кожному і-му розряді лічильника, починаючи з третього, перший вхід першого логічного елемента І-НІ з'єднаний з інверсним виходом лічильного тригера і-го розряду, другий його вхід з'єднаний з прямим виходом лічильного тригера (і-і)-го розряду, третій вхід з'єднаний з прямим виходом лічильного тригера (і-2)-го розряду, а вихід з'єднаний з першим входом другого логічного елемента І-НІ і-го розряду, другий вхід другого логічного елемента І-НІ і-го розряду, крім N-го, з'єднаний з виходом першого логічного елемента І-НІ (і+1)-го розряду, третій вхід другого логічного елемента І-НІ і-го розряду, крім N-го та (N-1)-го, з'єднаний з виходом першого логічного елемента І-НІ (і+2)-го розряду, а вихід другого логічного елемента І-НІ і-го розряду з'єднаний з Т-входом лічильного тригера і-го розряду; другий і третій входи другого логічного елемента І-НІ N-го розряду та третій вхід другого логічного елемента І-НІ (N-1)-го розряду з'єднані з входом одиничного потенціалу лічильника, який відрізняється тим, що в нього введено логічний елемент І-НІ лічильника, причому прямий вихід лічильного тригера першого розряду з'єднаний з першим входом логічного елемента І-НІ лічильника, другий вхід якого з'єднаний з прямим виходом лічильного тригера другого розряду, третій вхід з'єднаний з прямим виходом лічильного тригера третього розряду, а вихід з'єднаний з третім входом логічного елемента І-НІ першого розряду, третім входом логічного елемента І-НІ другого розряду та четвертим входом другого логічного елемента І-НІ кожного розряду, починаючи з третього. 4 UA 115994 U 5 UA 115994 U Комп’ютерна верстка О. Рябко Державна служба інтелектуальної власності України, вул. Василя Липківського, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 6

ДивитисяДодаткова інформація

МПК / Мітки

МПК: H03M 1/46

Мітки: системі, циклічний, лічильник, фібоначчієвій, числення

Код посилання

<a href="https://ua.patents.su/8-115994-ciklichnijj-lichilnik-u-fibonachchiehvijj-sistemi-chislennya.html" target="_blank" rel="follow" title="База патентів України">Циклічний лічильник у фібоначчієвій системі числення</a>

Попередній патент: Циклічний лічильник, що віднімає, у фібоначчієвій системі числення

Наступний патент: Спосіб визначення густини газу

Випадковий патент: Ущільнювальний пристрій