Лічильник, що віднімає, у фібоначчієвій системі числення

Номер патенту: 97829

Опубліковано: 10.04.2015

Автори: Азаров Олексій Дмитрович, Муращенко Олександр Геннадійович, Черняк Олександр Іванович

Формула / Реферат

Лічильник, що віднімає, у фібоначчієвій системі числення, який містить вхід тактових імпульсів, N інформаційних виходів та у кожному і-му розряді містить лічильний тригер, вхід С синхронізації якого з'єднаний зі входом тактових імпульсів лічильника, а прямий вихід лічильного тригера і-го розряду з'єднаний з інформаційним виходом лічильника, який відрізняється тим, що додатково містить вхід логічної одиниці, 2N входів встановлення у початковий стан, а кожний і-й розряд, крім першого розряду, додатково містить перший і другий логічні елементи I-НІ, причому перший вхід першого логічного елемента І-НІ і-го розряду, з'єднаний з прямим виходом лічильного тригера даного розряду, другий вихід з'єднаний з інверсним виходом лічильного тригера (і-1)-го розряду, третій вхід першого логічного елемента І-НІ і-го розряду, крім другого розряду, з'єднаний з інверсним виходом лічильного тригера (і-2)-го розряду, а вихід з'єднаний з першим входом другого логічного елемента І-НІ і-го розряду, другий вхід другого логічного елемента І-НІ і-го розряду, крім N-гo і (N-1)-гo розрядів, з'єднаний з виходом першого логічного елемента І-НІ (і+1)-го розряду, третій вхід з'єднаний з виходом першого логічного елемента І-НІ (і+2)-го розряду, а вихід з'єднаний з Т-входом лічильного тригера і-го розряду, крім того, у першому розряді лічильник додатково містить логічний елемент І-НІ, перший вхід якого з'єднаний з інверсним виходом лічильного тригера першого розряду, другий вхід з'єднаний з інверсним виходом лічильного тригера другого розряду, а вихід з'єднаний з Т-входом лічильного тригера першого розряду, а також, третій вхід першого елемента І-НІ другого розряду, другий і третій входи другого логічного елемента І-НІ N-гo розряду та третій вхід другого логічного елемента І-НІ (N-1)-гo розряду з'єднані зі входом логічної одиниці лічильника.

Текст

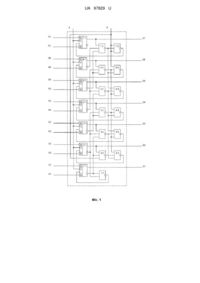

Реферат: Лічильник, що віднімає, у фібоначчієвій системі числення містить вхід тактових імпульсів, N інформаційних виходів та у кожному і-му розряді містить лічильний тригер, вхід С синхронізації якого з'єднаний зі входом тактових імпульсів лічильника, а прямий вихід лічильного тригера і-го розряду з'єднаний з інформаційним виходом лічильника. Крім цього, він додатково містить вхід логічної одиниці, 2N входів встановлення у початковий стан, а кожний і-й розряд, крім першого розряду, додатково містить перший і другий логічні елементи I-НІ, причому перший вхід першого логічного елемента І-НІ і-го розряду, з'єднаний з прямим виходом лічильного тригера даного розряду, другий вихід з'єднаний з інверсним виходом лічильного тригера (і-1)-го розряду, третій вхід першого логічного елемента І-НІ і-го розряду, крім другого розряду, з'єднаний з інверсним виходом лічильного тригера (і-2)-го розряду, а вихід з'єднаний з першим входом другого логічного елемента І-НІ і-го розряду. UA 97829 U (54) ЛІЧИЛЬНИК, ЩО ВІДНІМАЄ, У ФІБОНАЧЧІЄВІЙ СИСТЕМІ ЧИСЛЕННЯ UA 97829 U UA 97829 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до галузі цифрової вимірювальної і обчислювальної техніки і може бути використана для лічби імпульсів з представленням результату у фібоначчієвій системі числення. Відомий лічильник імпульсів в р-кодах фібоначчі [А.с. СРСР №1480121, м. кл. Н03К23/40, бюл. №18, 15.05.89], що містить елементи АБО, що з'єднані з лічильними входами лічильних тригерів, елементи І, D-тригер, елемент НІ і елемент затримки. Недоліком цього пристрою є неможливість лічби в режимі віднімання. За прототип обрано лічильник імпульсів в р-кодах фібоначчі [А.с. СРСР №1172006, м. кл. Н03К23/48, бюл. №29, 07.08.851, який містить лічильний вхід лічильника (в подальшому вхід тактових імпульсів), N інформаційних виходів, та у кожному і-му розряді містить лічильний тригер, вхід С синхронізації якого з'єднаний зі входом тактових імпульсів лічильника, а прямий вихід лічильного тригера і-го розряду з'єднаний з інформаційним виходом лічильника, елемент АБО, елемент І, вихід якого з'єднаний з першим входом елемента АБО, вихід якого з'єднано з лічильним входом тригера, інверсний вхід якого з'єднаний з першим входом елемента І. Недоліком прототипу є неможливість лічби в режимі віднімання. В основу корисної моделі поставлено задачу створення лічильника, що віднімає, у фібоначчієвій системі числення, в якому за рахунок введення нових елементів та зв'язків досягається можливість лічби імпульсів в режимі віднімання з представленням результату у фібоначчієвій системі числення, що у свою чергу розширює галузь використання корисної моделі у різноманітних пристроях імпульсної та обчислювальної техніки, автоматики тощо. Поставлена задача вирішується тим, що у лічильник імпульсів, який містить вхід тактових імпульсів, N інформаційних виходів, та у кожному і-му розряді містить лічильний тригер, вхід С синхронізації якого з'єднаний зі входом тактових імпульсів лічильника, а прямий вихід лічильного тригера і-го розряду з'єднаний з інформаційним виходом лічильника, введено вхід логічної одиниці, 2N входів встановлення у початковий етан, а кожний і-й розряд, крім першого розряду, додатково містить перший і другий логічні елементи І-НІ, причому перший вхід першого логічного елемента І-НІ і-го розряду, з'єднаний з прямим виходом лічильного тригера даного розряду, другий вихід з'єднаний з інверсним виходом лічильного тригера (і-1)-го розряду, третій вхід першого логічного елемента І-НІ і-го розряду, крім другого розряду, з'єднаний з інверсним виходом лічильного тригера (і-2)-го розряду, а вихід з'єднаний з першим входом другого логічного елемента І-НІ і-го розряду, другий вхід другого логічного елемента I-НІ і-го розряду, крім N-гo і (N-1)-гo розрядів, з'єднаний з виходом першого логічного елемента І-НІ(і+1)-го розряду, третій вхід з'єднаний з виходом першого логічного елемента І-НІ (і+2)-го розряду, а вихід з'єднаний з Т-входом лічильного тригера і-го розряду, крім того, у першому розряді лічильник додатково містить логічний елемент І-НІ, перший вхід якого з'єднаний з інверсним виходом лічильного тригера першого розряду, другий вхід з'єднаний з інверсним виходом лічильного тригера другого розряду, а вихід з'єднаний з Т-входом лічильного тригера першого розряду, а також, третій вхід першого елемента 1-НІ другого розряду, другий і третій входи другого логічного елемента І-НІ N-гo розряду та третій вхід другого логічного елемента 1-НІ (N1)-гo розряду з'єднані зі входом логічної одиниці лічильника. На фіг. 1 наведено структурну схему структурну семирозрядного лічильника що віднімає, у фібоначчієвій системі числення. На фіг. 2 наведено часову діаграму перших двадцяти тактів роботи семирозрядного лічильника що віднімає, у фібоначчієвій системі числення. Пристрій містить вхід тактових імпульсів 8, вхід логічної одиниці 9 призначений для подачі одиничного потенціалу, входи S1-S7 встановлення у початковий стан, призначені для подачі нульових сигналів для встановлення в одиничний стан лічильних тригерів з 1-го по 7-й розряд відповідно, входи R1-R7 встановлення у початковий етап, призначені для подачі нульових сигналів для встановлення в нульовий стан лічильних тригерів з 1-го по 7-й розряд відповідно, а також інформаційні виходи Q1-Q7. Крім того, лічильник містить лічильні тригери 1.1-7.1, призначені для зміни і зберігання етапів з 1-го по 7-й розряд відповідно; перші логічні елементи 2.2-7.2 1-І-НІ, призначені для формування сигналів розгортки з 2-го по 7-й розряд відповідно; другі логічні елементи 2.3-7.3 I-НІ, призначені для формування сигналів на Т-входи лічильних тригерів 2.1-7.1 відповідно, а також логічний елемент 1.2 І-НІ, призначений для формування сигналу на Т-вхід лічильного тригера 1.1. Вхід тактових імпульсів 8 лічильника з'єднаний з Свходами лічильних тригерів 1.1-7.1, входи S1-S7 встановлення у початковий стан лічильника з'єднані з S-входами лічильних тригерів 1.1-7.1 відповідно, входи R1-R7 встановлення у початковий стан лічильника з'єднані з R-входами лічильних тригерів 1.1-7.1 відповідно, прямі виходи лічильних тригерів 1.1-7.1 з'єднані з інформаційними виходами Q1-Q7 лічильника відповідно, прямі виходи тригерів 2.1-7.1 з'єднані з першими входами перших логічних елементів 2.2-7.2 відповідно, інверсні виходи лічильних тригерів 1.1-6.1 з'єднані з другими 1 UA 97829 U 5 10 15 20 25 30 35 40 45 50 55 60 входами перших логічних елементів 2.2-7.2 І-НІ відповідно, інверсні виходи лічильних тригерів 1.1-5.1 з'єднані з третіми входами перших логічних елементів І-НІ 3.2-7.2 відповідно, інверсний вихід лічильного тригера 1.1 з'єднаний з першим входом логічного елемента 1.2 1-1 НE, інверсний вихід лічильного тригера 2.1 з'єднаний з другим входом логічного елемента 1.2 І-НІ. Виходи перших логічних елементів 2.2-7.2 І-НІ з'єднані з першими входами других логічних елементів 2.3-7.3 І-НІ відповідно, виходи перших логічних елементів 3.2-7.2 І-НІ з'єднані з другими входами других логічних елементів 2.3-7.3 І-НІ відповідно, виходи перших логічних елементів 4.2-7.2 І-НІ з'єднані з третіми входами других логічних елементів 2.3-6.3 І-НІ відповідно. Виходи других логічних елементів 2.3-7.3 І-НІ з'єднані з Т-входами лічильних тригерів 2.1-7.1 відповідно, вихід логічного елемента 1.2 І-НІ з'єднаний з Т-входом лічильного тригера 1.1, вхід логічної одиниці 9 лічильника з'єднаний з третім входом першого логічного елемента 2.2 1-НІ, третім входом другого логічного елемента 6.3 І-НІ та другим і третім входами другого логічного елемента 7.3 І-НІ. З опису структури слідує, що при нарощуванні розрядності апаратні витрати даного лічильника зростають лінійно і становлять не більше одного лічильного тригера і двох логічних елементів 3 І-НІ на один розряд. Пристрій працює наступним чином. Робота починається із задання початкового стану лічильника шляхом встановлення нульових сигналів на входах початкового встановлення S1-S7 відповідно до того, які розряди коду початкового стану мають одиничні значення і на входах початкового встановлення R1-R7 відповідно до того, які розряди коду початкового стану мають нульові значення. На інших входах S1-S7 і R1-R7 встановлюються одиничні сигнали. На вході 8 лічильника задається нульовий сигнал, який надходить на С-входи всіх лічильних тригерів. Лічильні тригери всіх розрядів встановлюються відповідно до заданого коду. Нехай, наприклад це буде код 1100100. Одиничний потенціал зі входу логічної одиниці 9 надходить на третій вхід логічного елемента 2.1 І-НІ, третій вхід другого логічного елемента 6.3 І-НІ та другий і третій входи другого логічного елемента 7.3 І-НІ. Після встановлення заданого коду у лічильних тригерах на всіх входах початкового встановлення S1-S7 і R1-R7 встановлюється одиничний сигнал, який зберігається протягом подальшої роботи. Одиничні сигнали з прямих виходів лічильних тригерів 7.1, 6.1, 3.1 надходять на інформаційні виходи Q7, Q6. Q3 лічильника відповідно і на перші входи перших логічних елементів 3.2, 6.2, 7.2 І-НІ відповідно. Нульові сигнали з прямих виходів лічильних тригерів 2.1, 4.1, 5.1 поступають на інформаційні виходи Q2, Q4, Q5 відповідно лічильника і на перші входи перших логічних елементів 2.2, 4.2, 5.2 І-НІ відповідно. Нульовий сигнал з прямото виходу лічильного тригера 1.1 надходить на інформаційний вихід Q1 лічильника. Одиничні сигнали з інверсних виходів лічильних тригерів 2.1, 4.1. 5.1 надходять на другі входи перших логічних елементів 3.2, 5.2, 6.2 І-НІ відповідно. Нульові сигнали з інверсних виходів лічильних тригерів 3.1, 6.1 надходять на другі входи перших логічних елементів 4.2, 7.2 І-НІ відповідно. Одиничні сигнали з інверсних виходів лічильних тригерів 2.1, 4.1, 5.1 надходять на треті входи перших логічних елементів 4.2, 6.2, 7.2 І-НІ відповідно. Нульовий сигнал з інверсного виходу лічильного тригера 3.1 надходить на третій вхід першого елемента 5.2 І-НІ. Одиничний сигнал з інверсного виходу лічильного тригера 1.1 надходить на перший вхід елемента 1.2, на другий вхід якого поступає одиничний сигнал з інверсного виходу лічильного тригера 2.1. Нульовий сигнал з виходу логічного елемента 1.2 І-НІ надходить на Т-вхід лічильного тригера 1.1. Одиничний сигнал з виходу першого логічного елемента 2.2 І-НІ надходить на перший вхід другого логічного елемента 2.3 І-НІ. Нульовий сигнал з виходу першого логічного елемента 3.2 1-НІ надходить на другий вхід другого елемента 2.3 І-НІ і на перший вхід другого елемента 3.3 І-НІ. Одиничний сигнал з виходу першого логічного елемента 4.2 І-НІ надходить на третій вхід другого логічного елемента 2.3 ІНІ, на другий вхід другого логічного елемента 3.3 І-НІ і на перший вхід другого логічного елемента 4.3 І-НІ. Одиничний сигнал з виходу першого логічного елемента 5.2 І-НІ надходить на третій вхід другого логічного елемента 3.3 І-НІ, на другий вхід другого логічного елемента 4.3 ІНІ і на перший вхід другого логічного елемента 5.3 І-НІ. Нульовий сигнал з виходу першого логічного елемента 6.2 І-НІ надходить на третій вхід другого логічного елемента 4.3 І-НІ, на другий вхід другого логічного елемента 5.3 І-НІ і на перший вхід другого логічного елемента 5.3 І-НІ. Одиничний сигнал з виходу першого логічного елемента 7.2 І-НІ надходить на третій вхід другого логічного елемента 5.2 І-НІ, другий вхід другого логічного елемента 6.3 1-НІ і на перший вхід другого логічного елемента 7.3 І-НІ. Одиничний сигнал з виходу другого логічного елемента 2.3 І-НІ надходить на Т-вхід лічильного тригера 2.1. Одиничний сигнал з виходу другого логічного елемента 3.3 І-НІ надходить на Т-вхід лічильного тригера 3.1. Одиничний сигнал з виходу другого логічного елемента 4.3 І-НІ надходить на Т-вхід лічильного тригера 4.1. Одиничний сигнал з виходу другого логічного елемента 5.3 І-НІ поступає на Т-вхід лічильного тригера 5.1. Одиничний сигнал з виходу другого логічного елемента 6.3 І-НІ надходить на Т-вхід 2 UA 97829 U 5 лічильного тригера 6.1. Нульовий сигнал з виходу другого логічного елемента 7.3 І-НІ надходить на Т-вхід лічильного тригера 7.1. На всі входи початкового встановлення лічильника подаються одиничні сигнали, які надходять на S- і R-входи відповідних лічильних тригерів. При надходженні наступного імпульсу на вхід тактових імпульсів 8 лічильника сигнал надходить на С-входи всіх лічильних тригерів. У лічильнику встановлюється код 1011010. Коди і числові значення станів лічильника наведено в Таблиці 1. Таблиця 1 Коди і числові значення станів семирозрядного лічильника, що віднімає, у фібопаччієвій системі числення № стану 1 2 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 10 Q7 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 Q6 1 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 Розряди лічильника Q5 Q4 Q3 0 0 1 1 1 0 1 1 0 1 0 1 1 0 1 1 0 1 1 0 0 0 1 1 1 1 1 1 1 0 1 1 0 1 0 1 1 0 1 1 0 1 1 0 0 0 1 1 0 1 1 0 1 0 0 1 0 0 0 1 1 1 1 1 1 1 1 1 0 1 1 0 1 0 1 1 0 1 1 0 1 1 0 0 0 1 1 0 1 1 0 1 0 0 1 0 0 0 1 0 0 1 0 0 1 0 0 0 0 0 0 0 0 0 Q2 0 1 0 1 0 0 1 0 0 1 0 1 0 0 1 0 0 1 0 1 0 0 1 0 1 0 0 1 0 0 1 0 1 0 0 1 0 0 Q1 0 0 1 0 1 0 0 1 0 0 1 0 1 0 0 1 0 0 1 0 1 0 0 1 0 1 0 0 1 0 0 1 ρ 1 0 0 1 0 Значення КОДУ 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 Подальшу роботу лічильника пояснює часова діаграма, що представлена на фіг. 2. З опису роботи слідує, що максимальна затримка переключення станів лічильника на кожному такті не залежить від його розрядності і визначається затримкою переключения лічильного тригера та двох логічних елементів І-НІ. 3 UA 97829 U ФОРМУЛА КОРИСНОЇ МОДЕЛІ 5 10 15 20 Лічильник, що віднімає, у фібоначчієвій системі числення, який містить вхід тактових імпульсів, N інформаційних виходів та у кожному і-му розряді містить лічильний тригер, вхід С синхронізації якого з'єднаний зі входом тактових імпульсів лічильника, а прямий вихід лічильного тригера і-го розряду з'єднаний з інформаційним виходом лічильника, який відрізняється тим, що додатково містить вхід логічної одиниці, 2N входів встановлення у початковий стан, а кожний і-й розряд, крім першого розряду, додатково містить перший і другий логічні елементи I-НІ, причому перший вхід першого логічного елемента І-НІ і-го розряду, з'єднаний з прямим виходом лічильного тригера даного розряду, другий вихід з'єднаний з інверсним виходом лічильного тригера (і-1)-го розряду, третій вхід першого логічного елемента І-НІ і-го розряду, крім другого розряду, з'єднаний з інверсним виходом лічильного тригера (і-2)-го розряду, а вихід з'єднаний з першим входом другого логічного елемента І-НІ і-го розряду, другий вхід другого логічного елемента І-НІ і-го розряду, крім N-гo і (N-1)-гo розрядів, з'єднаний з виходом першого логічного елемента І-НІ (і+1)-го розряду, третій вхід з'єднаний з виходом першого логічного елемента І-НІ (і+2)-го розряду, а вихід з'єднаний з Т-входом лічильного тригера і-го розряду, крім того, у першому розряді лічильник додатково містить логічний елемент І-НІ, перший вхід якого з'єднаний з інверсним виходом лічильного тригера першого розряду, другий вхід з'єднаний з інверсним виходом лічильного тригера другого розряду, а вихід з'єднаний з Т-входом лічильного тригера першого розряду, а також, третій вхід першого елемента І-НІ другого розряду, другий і третій входи другого логічного елемента І-НІ N-гo розряду та третій вхід другого логічного елемента І-НІ (N-1)-гo розряду з'єднані зі входом логічної одиниці лічильника. 4 UA 97829 U Комп’ютерна верстка В. Мацело Державна служба інтелектуальної власності України, вул. Василя Липківського, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 5

ДивитисяДодаткова інформація

Автори англійськоюAzarov Oleksii Dmytrovych

Автори російськоюАзаров Алексей Дмитриевич

МПК / Мітки

МПК: H03K 23/00

Мітки: фібоначчієвій, числення, лічильник, системі, віднімає

Код посилання

<a href="https://ua.patents.su/7-97829-lichilnik-shho-vidnimaeh-u-fibonachchiehvijj-sistemi-chislennya.html" target="_blank" rel="follow" title="База патентів України">Лічильник, що віднімає, у фібоначчієвій системі числення</a>

Попередній патент: Спосіб визначення щільності ґрунту

Наступний патент: Машина електрична

Випадковий патент: Спосіб проходки виймальних камер