Пристрій для визначення резонансної частоти елемента конструкції

Номер патенту: 11737

Опубліковано: 16.01.2006

Формула / Реферат

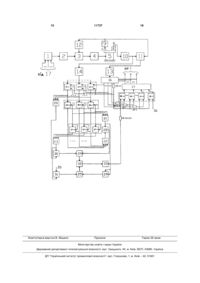

Пристрій для визначення резонансної частоти елемента конструкції, що містить послідовно з'єднані блок керування розгорткою частоти, задавальний генератор, регулятор амплітуди, підсилювач потужності і вібростенд, два віброперетворювачі, перший із яких разом з випробуваним об'єктом установлений на рухомій частині вібростенда, а другий віброперетворювач - на випробуваному об'єкті, два узгоджувальних підсилювачі, входи яких з'єднані з виходами відповідних віброперетворювачів, фазовий детектор, входи якого з'єднані з виходами відповідних узгоджувальних підсилювачів, блок зворотного зв'язку, вхід якого з'єднаний з виходом першого узгоджувального підсилювача, а вихід - з керувальним входом регулятора амплітуди, перетворювач «частота-напруга», вхід якого з'єднаний з виходом другого узгоджувального підсилювача, послідовно з'єднані нуль - орган, вхід якого з'єднаний з виходом фазового детектора, і комутатор, дешифратор, виходи якого з'єднані з відповідними керувальними входами блока керування розгорткою частоти і комутатора, чотири елементи затримки, регістратор, три блоки пам'яті з першого по третій, входи «Запис» яких з'єднані з відповідними виходами комутатора з першого по третій, два блоки множення, шість суматорів з першого по шостий, блок ділення, вихід якого з'єднаний з інформаційним входом регістратора, S-входи тригерів з першого по четвертий з'єднані відповідно з входом «Пуск» пристрою і через три елементи затримки з першого по третій - з виходами комутатора з першого по третій відповідно, прямі виходи тригерів з першого по четвертий з'єднані з входами комутатора з першого по четвертий відповідно, який відрізняється тим, що пристрій додатково містить групу блоків пам'яті із (n-3) блоків пам'яті (n - числа натурального ряду чисел, n![]() 4), першу і другу групи із «n» блоків множення з першого по «n»-й кожна, третій і четвертий блоки множення, (n-2) елементів затримки групи (n+1) елементів затримки, виходи комутатора з четвертого по (n-1)-й через відповідні елементи затримки з четвертого по (n-1)-й з'єднані з S-входами відповідних тригерів з п’ятого по «n»-й, R-входи яких об'єднані, з'єднані з R-входами тригерів з першого по четвертий і з'єднані з об'єднаними входами «Читання» «n» блоків пам'яті з першого по «n»-й, які через «n»-й елемент затримки з'єднані з «n»-м виходом комутатора, об'єднані R-входи тригерів через (n+1)-й елемент затримки з'єднані з входом «Запис» регістратора, прямі виходи тригерів з п'ятого по «n»-й з'єднані з відповідними входами дешифратора з п'ятого по «n»-й, виходи дешифратора з п'ятого по «n»-й з’єднані з відповідними керувальними входами з п'ятого по «n»-й комутатора і блока керування розгорткою частоти, виходи блоків пам'яті з першого по «n»-й групи блоків пам'яті з'єднані з відповідними першими входами відповідних блоків множення і з'єднані з відповідними першими входами відповідних блоків множення з першого по «n»-й першої групи блоків множення, виходи блоків пам'яті з першого по «n»-й групи блоків пам'яті з'єднані також з входами першого суматора, другі входи блоків множення з першого по «n»-й першої групи блоків множення з'єднані з виходами джерел напруги з першої по «n»-у відповідно групи джерел напругу, причому величини джерел напруги з першої по «n»-у відповідають величинам швидкостей

4), першу і другу групи із «n» блоків множення з першого по «n»-й кожна, третій і четвертий блоки множення, (n-2) елементів затримки групи (n+1) елементів затримки, виходи комутатора з четвертого по (n-1)-й через відповідні елементи затримки з четвертого по (n-1)-й з'єднані з S-входами відповідних тригерів з п’ятого по «n»-й, R-входи яких об'єднані, з'єднані з R-входами тригерів з першого по четвертий і з'єднані з об'єднаними входами «Читання» «n» блоків пам'яті з першого по «n»-й, які через «n»-й елемент затримки з'єднані з «n»-м виходом комутатора, об'єднані R-входи тригерів через (n+1)-й елемент затримки з'єднані з входом «Запис» регістратора, прямі виходи тригерів з п'ятого по «n»-й з'єднані з відповідними входами дешифратора з п'ятого по «n»-й, виходи дешифратора з п'ятого по «n»-й з’єднані з відповідними керувальними входами з п'ятого по «n»-й комутатора і блока керування розгорткою частоти, виходи блоків пам'яті з першого по «n»-й групи блоків пам'яті з'єднані з відповідними першими входами відповідних блоків множення і з'єднані з відповідними першими входами відповідних блоків множення з першого по «n»-й першої групи блоків множення, виходи блоків пам'яті з першого по «n»-й групи блоків пам'яті з'єднані також з входами першого суматора, другі входи блоків множення з першого по «n»-й першої групи блоків множення з'єднані з виходами джерел напруги з першої по «n»-у відповідно групи джерел напругу, причому величини джерел напруги з першої по «n»-у відповідають величинам швидкостей ![]() розгортки частоти з першої по «n» при умові V1<...<Vi.....<Vn, виходи джерел напруги з першої до «n»-ої групи «n» джерел напруги з'єднані з входами другого суматора і з входами відповідних блоків множення з першого по «n»-й другої групи блоків множення, входи кожного блоку множення з першого по «n»-й другої групи блоків множення об'єднані, виходи блоків множення першої групи блоків множення з'єднані з входами третього суматора, а виходи блоків множення другої групи блоків множення з'єднані з входами четвертого суматора, виходи другого і третього суматорів з'єднані з входами першого блока множення, вихід четвертого суматора з'єднаний з об'єднаними другими входами третього і четвертого блоків множення, перший вхід третього блока множення з'єднаний з виходом першого суматора, перший вхід четвертого блока множення з'єднаний з виходом джерела напруги величиною «n», виходи першого і третього блоків множення з'єднані з віднімальним і підсумовувальним входами п'ятого суматора відповідно, вихід другого суматора з'єднаний з об'єднаними входами другого блока множення, вихід якого з'єднаний з віднімальним входом шостого суматора, підсумовувальний вхід якого з'єднаний з виходом четвертого блока множення, вихід п'ятого суматора з'єднаний з входом «Ділене» блока ділення, вхід «Подільник» якого з'єднаний з виходом шостого суматора, входи групи «n»-х блоків пам'яті об'єднані і з'єднані з виходом перетворювача «частота - напруга».

розгортки частоти з першої по «n» при умові V1<...<Vi.....<Vn, виходи джерел напруги з першої до «n»-ої групи «n» джерел напруги з'єднані з входами другого суматора і з входами відповідних блоків множення з першого по «n»-й другої групи блоків множення, входи кожного блоку множення з першого по «n»-й другої групи блоків множення об'єднані, виходи блоків множення першої групи блоків множення з'єднані з входами третього суматора, а виходи блоків множення другої групи блоків множення з'єднані з входами четвертого суматора, виходи другого і третього суматорів з'єднані з входами першого блока множення, вихід четвертого суматора з'єднаний з об'єднаними другими входами третього і четвертого блоків множення, перший вхід третього блока множення з'єднаний з виходом першого суматора, перший вхід четвертого блока множення з'єднаний з виходом джерела напруги величиною «n», виходи першого і третього блоків множення з'єднані з віднімальним і підсумовувальним входами п'ятого суматора відповідно, вихід другого суматора з'єднаний з об'єднаними входами другого блока множення, вихід якого з'єднаний з віднімальним входом шостого суматора, підсумовувальний вхід якого з'єднаний з виходом четвертого блока множення, вихід п'ятого суматора з'єднаний з входом «Ділене» блока ділення, вхід «Подільник» якого з'єднаний з виходом шостого суматора, входи групи «n»-х блоків пам'яті об'єднані і з'єднані з виходом перетворювача «частота - напруга».

Текст

Пристрій для визначення резонансної частоти елемента конструкції, що містить послідовно з'єднані блок керування розгорткою частоти, задавальний генератор, регулятор амплітуди, підсилювач потужності і вібростенд, два віброперетворювачі, перший із яких разом з випробуваним об'єктом установлений на рухомій частині вібростенда, а другий віброперетворювач - на випробуваному об'єкті, два узгоджувальних підсилювачі, входи яких з'єднані з виходами відповідних віброперетворювачів, фазовий детектор, входи якого з'єднані з виходами відповідних узгоджувальних підсилювачів, блок зворотного зв'язку, вхід якого з'єднаний з виходом першого узгоджувального підсилювача, а вихід - з керувальним входом регулятора амплітуди, перетворювач «частота-напруга», вхід якого з'єднаний з виходом другого узгоджувального підсилювача, послідовно з'єднані нуль - орган, вхід якого з'єднаний з виходом фазового детектора, і комутатор, дешифратор, виходи якого з'єднані з відповідними керувальними входами блока керування розгорткою частоти і комутатора, чотири елементи затримки, регістратор, три блоки пам'яті з першого по третій, входи «Запис» яких з'єднані з відповідними виходами комутатора з першого по третій, два блоки множення, шість суматорів з першого по шостий, блок ділення, вихід якого з'єднаний з інформаційним входом регістратора, Sвходи тригерів з першого по четвертий з'єднані відповідно з входом «Пуск» пристрою і через три елементи затримки з першого по третій - з виходами комутатора з першого по третій відповідно, прямі виходи тригерів з першого по четвертий з'єднані з входами комутатора з першого по четвертий відповідно, який відрізняється тим, що пристрій додатково містить групу блоків пам'яті із (n-3) блоків пам'яті (n - числа натурального ряду чисел, n 4), першу і другу групи із «n» блоків множення з першого по «n»-й кожна, третій і четвертий блоки множення, (n-2) елементів затримки групи (n+1) елементів затримки, виходи комутато 2 (19) 1 3 11737 4 першого і третього блоків множення з'єднані з відякого з'єднаний з виходом четвертого блока мнонімальним і підсумовувальним входами п'ятого ження, вихід п'ятого суматора з'єднаний з входом суматора відповідно, вихід другого суматора з'єд«Ділене» блока ділення, вхід «Подільник» якого наний з об'єднаними входами другого блока мноз'єднаний з виходом шостого суматора, входи груження, вихід якого з'єднаний з віднімальним вхопи «n»-х блоків пам'яті об'єднані і з'єднані з виходом шостого суматора, підсумовувальний вхід дом перетворювача «частота - напруга». Корисна модель відноситься до області техніки дослідження динамічних і статичних характеристик резонуючих елементів випробуваних конструкцій при проведенні вібровипробувань і може бути застосована в галузі машинобудування, авіаційної, космічної техніки дня визначення параметрів елементів конструкцій, режим функціонування яких моделюється гармонійним процесом або процесом, що моделює сейсмічне навантаження. Відомий пристрій для визначення резонансної частоти елементів конструкції, що містить послідовно з'єднані блок керування розгорткою частоти, задавальний генератор, регулятор амплітуди, підсилювач потужності і вібростенд, з установленими на ньому випробуваним об'єктом, два віброперетворювача, один з яких установлений на вібростенді, а другий - на випробуваному об'єкті, два узгоджувальних підсилювача, входи яких сполучені з виходами першого і другого віброперетворювачів відповідно, фазовий детектор, входи якого сполучені з виходами першого і другого узгоджувальних підсилювачів, блок зворотного зв'язку, вхід якого сполучений з виходом першого узгоджувального підсилювача, а вихід - з керувальним входом регулятора амплітуди, перетворювач «частотанапруга», вхід якого сполучений з виходом другого узгоджувального підсилювача, нуль - орган , вхід якого сполучений з виходом фазового детектора, комутатор, інформаційний вхід якого сполучений з виходом нуль - органа, дешифратор, перший і другий виходи якого сполучені з відповідними входами блока керування розгорткою частоти і відповідними входами комутатора, два тригери, прямі виходи яких сполучені з відповідними входами дешифратора, два ключі, два підсилювачі з регульованими коефіцієнтами підсилення, блок пам'яті, суматор, регістратор, два елементи затримки, входи першого і другого ключів об'єднані і сполучені з виходом перетворювача «частота-напруга», а виходи цих ключів сполучені з входами першого і другого підсилювачів з регульованими коефіцієнтами підсилення відповідно, вихід першого підсилювача з регульованим коефіцієнтом підсилення сполучений з інформаційним входом блока пам'яті, вихід якого і вхід другого підсилювача з регульованим коефіцієнтом підсилення сполучені з підсумовувальним і віднімальним входами суматора, вихід якого сполучений з інформаційним входом регістратора, керувальний вхід першого ключа сполучений з входом «Запис» блока пам'яті і під'єднаний до першого виходу комутатора безпосередньо, а через перший елемент затримки до S-входу першого тригера, другий вихід комутатора сполучений з об'єднаними керувальним входом другого ключа і входом «Читання» блока па м'яті безпосередньо, а через другий елемент затримки - з об'єднаними R - входами першого і другого тригерів, S - вхід другого тригера сполучений з входом «Пуск» пристрою [Див. ав.св. СРСР №1633294,М.кл. G01H13/00, 1991]. Недоліком відомого пристрою є недостатня точність визначення значення резонансної частоти резонуючого елемента конструкції, що пояснюється похибками виміру, фіксації та запам’ятовування значень частот максимумів обвідних напіврозмахів коливань динамічних резонансних піків, що призводить для звуження функціональних можливостей самого пристрою, а тому і до звуження області його використання. Відомий також пристрій для визначення резонансної частоти резонуючого елемента випробуваної конструкції, що містить послідовно з'єднані блок керування розгорткою частоти, задавальний генератор, регулятор амплітуди, підсилювач потужності і вібростенд, два віброперетворювачі, перший із яких разом з випробуваним об'єктом установлений на рухомій частині вібростенда, а другий віброперетворювач - на випробуваному об'єкті, два узгоджувальних підсилювачі, входи яких з'єднані з виходами відповідних віброперетворювачів, фазовий детектор, входи якого з'єднані з виходами відповідних узгоджувальних підсилювачів, блок зворотного зв'язку, вхід якого з'єднаний з виходом першого узгоджувального підсилювача, а вихід - з керувальним входом регулятора амплітуди, перетворювач «частота-напруга», вхід якого з'єднаний з виходом другого узгоджувального підсилювача, послідовно з'єднані нуль-орган, вхід якого з'єднаний з виходом фазового детектора, і комутатор, дешифратор, виходи якого з'єднані з відповідними керувальними входами блока керування розгорткою частоти і комутатора, чотири тригери, прямі виходи яких з'єднані з відповідними входами дешифратора, S - входи тригерів з другого по четвертий через три елементи затримки відповідно з'єднані з першим, другим і третім виходами відповідно комутатора, a R - входи тригерів з першого по четвертий об'єднані і через четвертий елемент затримки з'єднані з четвертим виходом комутатора, S - вхід першого тригера з'єднаний з зовнішнім входом «Пуск», чотири ключі, інформаційні входи яких об'єднані і з'єднані з виходом перетворювача «частота-напруга», а керувальні вході з'єднані з відповідними виходами комутатора, три блоки пам'яті, інформаційні входи яких з'єднані з виходами відповідних ключів, входи «Запис» - з відповідними виходами з першого по третій комутатора, а входи «Читання» блоків пам'яті об'єднані і з'єднані з четвертим виходом комутатора, два блоки множення, шість суматорів, блок ділення, блок порівняння, 5 11737 6 другий нуль - орган і регістратор, входи першого з’єднані з виходами відповідних узгоджувальних блоку множення з'єднані з виходами першого блопідсилювачів, блок зворотного зв'язку, вхід якого ка пам'яті і четвертого ключа, входи другого блока з'єднаний з виходом першого узгоджувального множення з'єднані з виходами другого і третього підсилювача, а вихід - з керувальним входом регублоків пам'яті, віднімальний і підсумовувальний лятора амплітуди, перетворювач «частотавходи першого суматора з'єднані з виходами пернапруга», вхід якого з'єднаний з виходом другого шого і другого блоків множення відповідно, підсуузгоджувального підсилювача, послідовно з'єднані мовувальні входи другого суматора з'єднані з винуль-орган, вхід якого з'єднаний з виходом фазоходами другого і третього блоків пам'яті, вого детектора, і комутатор, дешифратор, виходи підсумовувальні входи третього суматора з'єднані якого з'єднані з відповідними керувальними вхоз виходами першого блока пам'яті і четвертого дами блока керування розгорткою частоти і комуключа відповідно, віднімальний і підсумовувальтатора, чотири елементи затримки, регістратор, ний входи четвертого суматора з'єднані з виходатри блоки пам'яті з першого по третій, входи «Зами другого і третього суматорів відповідно, підсупис» яких з'єднані з відповідними виходами комумовувальний і віднімальний входи п'ятого татора з першого по третій, два блоки множення, суматора з'єднані з виходами першого і третього шість суматорів з першого по шостий, блок діленблоків пам'яті відповідно, віднімальний і підсумоня, вихід якого з'єднаний з інформаційним входом вувальний входи шостого суматора з'єднані з вирегістратора, S-входи тригерів з першого по четходами другого блока пам'яті і четвертого ключа вертий з'єднані відповідно з входом «Пуск» привідповідно, вхід «Ділене» блока ділення з'єднаний строю і через три елементи затримки з першого по з виходом першого суматора, вхід «Подільник» - з третій - з виходами комутатора з першого по тревиходом четвертого суматора, а вихід - з першим тій відповідно, прямі виходи тригерів з першого по входом регістратора, входи блока порівняння з'єдчетвертий з'єднані з входами комутатора з першонані з виходами п'ятого і шостого суматорів, а виго по четвертий відповідно, згідно з корисною мохід - з другим входом регістратора, входи другого деллю, пристрій додатково містить групу блоків нуль - органу з'єднані з входами блока порівняння, пам'яті із (n-3) блоків пам'яті (n-числа натуральноа вихід другого нуль - органу з'єднаний з третім го ряду чисел, n 4 ), першу і другу групи із «n» входом регістратора [Див. ав.св. СРСР №1832183, блоків множення з першого по «n»-й кожна, третій і М. кл, G01М7/00, 1993]. четвертий блоки множення, (n-2) елементів затриДаний пристрій є найбільш близьким до замки групи (n+1) елементів затримки., виходи комупропонованої корисної моделі по технічній суті і татора з четвертого по (n-1)-й через відповідні отриманому результату, в якості чого і прийнятий елементи затримки з четвертого по (n-1)-й з'єднані за прототип. з S-входами відповідних тригерів з п'ятого по «n»Але недоліком відомого пристрою залишаєтьй, R- входи яких об'єднаю, з'єднані з R-входами ся недостатня точність визначення резонансної тригерів з першого по четвертий і з'єднані з об'єдчастоти, що пояснюється похибками виміру, фікнаними входами «Читання» «n» блоків пам'яті з сації та запам'ятовування значень частот максипершого по «n»-й, які через «n»-й елемент затриммумів обвідних напіврозмахів коливань динамічних ки з'єднані з «n» - м виходом комутатора, об'єднані резонансних піків, які відповідають постійнім, але R-входи тригерів через (n+1)-й елемент затримки різним швидкостям розгортки частоти сигналу збуз'єднані з входом «Запис» регістратора, прямі виджувальної вібростенд разом з випробуваним ходи тригерів з п'ятого по «n»-й з'єднані з відповіоб'єктом дії. Це, в свою чергу, призводить як до дними входами дешифратора з п'ятого по «n»-й, звуження функціональних можливостей пристрою, виходи дешифратора з п'ятого по «n»-й з'єднані з так і області його застосування. відповідними керувальними входами з п'ятого по В основу запропонованої корисної моделі пос«n»-й комутатора і блока керування розгорткою тавлене завдання удосконалення пристрою за частоти, виходи блоків пам'яті з першого по «n»-й рахунок введення до його складу додаткових блогрупи блоків пам'яті з'єднані з відповідними перків, включення яких за рахунок формування нового шими входами відповідних блоків множення з алгоритму, який заснований на нових аналітичних першого по «n»-й першої групи блоків множення, співвідношеннях, що ураховують похибки при провиходи блоків пам'яті з першого по «n»-й групи веденні вимірювань, призводить до збільшення блоків пам'яті з'єднані також з входами першого точності визначення резонансної частоти, розшисуматора, другі входи блоків множення з першого рення функціональних можливостей пристрою і по «n»-й першої групи блоків множення з'єднані з галузі його застосування. виходами джерел напруги з першої по «n»-у відпоПоставлене завдання вирішується тим, що у відно групи джерел напруги, причому величини відомому пристрої для визначення резонансної джерел напруги з першої по «n»-у відповідають частоти елемента конструкції, що містить послідовеличинам швидкостей Vi (i=1 n ) розгортки частоти вно з'єднані блок керування розгорткою частоти, з першої по «n» при умові V1

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for determining the resonance frequency of a structural component

Автори англійськоюPuz'ko Ihor Danylovych

Назва патенту російськоюУстройство для определения резонансной частоты элемента конструкции

Автори російськоюПузько Игорь Данилович

МПК / Мітки

МПК: G01M 7/02, G01H 13/00

Мітки: пристрій, резонансної, визначення, частоти, конструкції, елемента

Код посилання

<a href="https://ua.patents.su/8-11737-pristrijj-dlya-viznachennya-rezonansno-chastoti-elementa-konstrukci.html" target="_blank" rel="follow" title="База патентів України">Пристрій для визначення резонансної частоти елемента конструкції</a>

Попередній патент: Нетканий волокнистий матеріал

Наступний патент: Спосіб обробки сферичних поверхонь