Пристрій для визначення нормованих векторів нормалей

Номер патенту: 18419

Опубліковано: 15.11.2006

Автори: Неживенко Максим Валерійович, Чорний Анатолій Вікторович, Романюк Олександр Никифорович, Мельников Олександр Никитович

Формула / Реферат

1. Пристрій для визначення нормованих векторів нормалей, який містить перший, другий, третій блоки множення, виходи яких відповідно з'єднано з другими входами першого, другого і третього суматорів, який відрізняється тим, що в нього введено сім регістрів, блок керування, лічильник, інформаційний вхід якого з'єднаний з восьмим інформаційним входом пристрою, вхід запису в лічильник підключено до четвертого керуючого входу пристрою, перший керуючий вхід якого підключено відповідно до перших керуючих входів першого, третього і п'ятого регістрів, другий керуючий вхід пристрою підключено відповідно до перших керуючих входів другого, четвертого і шостого регістрів, третій керуючий вхід пристрою підключений до керуючого входу сьомого регістра, а до других керуючих входів відповідно першого, другого, третього, четвертого, п'ятого і шостого регістрів підключено перший вихід блока керування, який також з'єднано з входом лічби лічильника, вихід переносу якого підключено до першого входу блока керування, другий, третій і четвертий входи якого відповідно з'єднані з п'ятим, шостим і сьомим керуючими входами пристрою, перший-сьомий інформаційні входи якого з'єднано відповідно з першими інформаційними входами першого-сьомого регістрів, інформаційні виходи відповідно першого, третього і п'ятого регістрів підключено до перших інформаційних входів першого, другого і третього суматорів, інформаційні виходи яких з'єднано відповідно з першим-третім інформаційними виходами пристрою і другими інформаційними входами другого, четвертого і шостого регістрів, інформаційні виходи яких підключено відповідно до других інформаційних входів першого, третього і п'ятого регістрів, а також кожний і-й розряд відповідно другого, четвертого і шостого регістрів з'єднано з (і+1)-ми розрядами других інформаційних входів першого, другого і третього блоків множення, а молодший розряд других інформаційних входів відповідно першого, другого і третього блоків множення заземляють, перші інформаційні входи відповідно першого, другого і третього блоків множення з'єднано з інформаційним виходом сьомого регістра, інформаційні виходи відповідно першого, другого і третього блоків множення підключено до другихінформаційних входів першого, другого і третього суматорів, входи переносу яких заземлено, другий і третій керуючі виходи блока керування з'єднані відповідно з другим і першим керуючими виходами пристрою.

2. Пристрій за п. 1, який відрізняється тим, що блок керування складається з першого, другого елемента І, першого і другого інвертора, першого і другого D-тригера, перший вхід першого елемента І з'єднано з сьомим керуючим входом пристрою, який також з'єднаний з R-входом другого D-тригера, D-вхід якого підключено до виходу першого D-тригера, R-вхід якого з'єднано з виходом першого елемента І, другий вхід якого підключено до виходу переносу лічильника, на D-вхід першого D-тригера подається логічна одиниця, С-вхід першого D-тригера з'єднано з п'ятим керуючим входом пристрою, S-входи відповідно першого і другого D-тригерів заземлено, а С-вхід другого D-тригера з'єднано з виходом першого інвертора, вхід якого підключено до шостого керуючого входу пристрою, який також підключено до другого входу другого елемента І, перший вхід якого з'єднано з виходом другого D-тригера, вихід якого також з'єднано з другим керуючим виходом пристрою, а перший керуючий вихід пристрою з'єднано з виходом другого елемента І, вихід якого також підключено до входу другого інвертора, вихід якого з'єднано з першим виходом блока керування.

3. Пристрій за п. 1, який відрізняється тим, що перший, третій і п'ятий регістри включають мультиплексор, регістр і елемент І, перший і другий входи якого з'єднано відповідно з першим і другим керуючими входами першого, третього і п'ятого регістрів, вихід елемента І підключено до керуючого входу регістра, інформаційний вхід якого підключено до інформаційного входу мультиплексора, перший інформаційний вхід якого з'єднано з першим інформаційним входом першого, третього і п'ятого регістрів, а другий інформаційний вхід підключено до інформаційного виходу другого, четвертого і шостого регістрів, інверсний інформаційний вихід регістра з'єднано з інверсним інформаційним виходом першого, третього і п'ятого регістрів, третій керуючий вхід першого, другого і третього регістрів підключено до керуючого входу мультиплексора.

4. Пристрій за п. 1, який відрізняється тим, що другий, четвертий і шостий регістри включають мультиплексор, регістр і елемент І, перший і другий входи якого з'єднано відповідно з першим і другим керуючими входами другого, четвертого і шостого регістрів, вихід елемента І підключено до керуючого входу регістрів, інформаційній вхід якого підключено до інформаційного входу мультиплексора, перший інформаційний вхід якого з'єднано з першим інформаційним входом другого, четвертого і шостого регістрів, а другий інформаційний вхід підключено до інформаційного виходу першого, другого і третього суматорів, інформаційний вихід регістра з'єднано з інформаційним виходом другого, четвертого і шостого регістрів, третій керуючий вхід другого, четвертого і шостого регістрів підключено до керуючого входу мультиплексора.

Текст

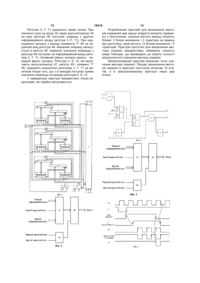

1. Пристрій для визначення нормованих векторів нормалей, який містить перший, другий, третій блоки множення, виходи яких відповідно з'єднано з другими входами першого, другого і третього суматорів, який відрізняється тим, що в нього введено сім регістрів, блок керування, лічильник, інформаційний вхід якого з'єднаний з восьмим інформаційним входом пристрою, вхід запису в лічильник підключено до четвертого керуючого входу пристрою, перший керуючий вхід якого підключено відповідно до перших керуючих входів першого, третього і п'ятого регістрів, другий керуючий вхід пристрою підключено відповідно до перших керуючих входів другого, четвертого і шостого регістрів, третій керуючий вхід пристрою підключений до керуючого входу сьомого регістра, а до других керуючих входів відповідно першого, другого, третього, четвертого, п'ятого і шостого регістрів підключено перший вихід блока керування, який також з'єднано з входом лічби лічильника, вихід переносу якого підключено до першого входу блока керування, другий, третій і четвертий входи якого відповідно з'єднані з п'ятим, шостим і сьомим керуючими входами пристрою, перший-сьомий інформаційні входи якого з'єднано відповідно з першими інформаційними входами першогосьомого регістрів, інформаційні виходи відповідно першого, третього і п'ятого регістрів підключено до перших інформаційних входів першого, другого і третього суматорів, інформаційні виходи яких з'єднано відповідно з першим-третім інформаційними виходами пристрою і другими інформаційними входами другого, четвертого і шостого регістрів, інформаційні виходи яких підключено відповідно до других інформаційних входів першого, третього і п'ятого регістрів, а також кожний і-й розряд відповідно другого, четвертого і шостого регістрів з'єднано з (і+1)-ми розрядами других інформаційних входів першого, другого і третього 2 (19) 1 3 18419 4 вертого і шостого регістрів, інверсний інформаційкеруючого входу регістрів, інформаційній вхід яконий вихід регістра з'єднано з інверсним інформаго підключено до інформаційного входу мультипційним виходом першого, третього і п'ятого регістлексора, перший інформаційний вхід якого з'єднарів, третій керуючий вхід першого, другого і но з першим інформаційним входом другого, третього регістрів підключено до керуючого входу четвертого і шостого регістрів, а другий інформамультиплексора. ційний вхід підключено до інформаційного виходу 4. Пристрій за п. 1, який відрізняється тим, що першого, другого і третього суматорів, інформадругий, четвертий і шостий регістри включають ційний вихід регістра з'єднано з інформаційним мультиплексор, регістр і елемент І, перший і друвиходом другого, четвертого і шостого регістрів, гий входи якого з'єднано відповідно з першим і третій керуючий вхід другого, четвертого і шостого другим керуючими входами другого, четвертого і регістрів підключено до керуючого входу мультипшостого регістрів, вихід елемента І підключено до лексора. Корисна модель відноситься до автоматики та обчислювальної техніки і призначена для визначення нормованих векторів нормалей у системах формування реалістичних зображень. Відомий пристрій для обчислення вектора нормалі, який включає дільник 1 на A і пам'ять для зберігання цих значень, [стаття: The Triangle Processor and Normal Vector Shader: A VLSI System for High Performance Graphics, Computer Graphics, Volume 22, Number 4, August 1988]. Недолік пристрою полягає у великих витратах пам'яті для збереження таблиць значень векторів нормалей, а також низької точності визначення векторів нормалей. Найбільш близьким є пристрій для обчислення вектора нормалі, який включає тринадцять блоків множення, п'ять суматорів, блок декрементування та блок інкрементування, регістр зсуву, виходи першого і четвертого блоків множення з'єднано відповідно з першим та другим входами першого суматора, виходи другого і п'ятого блоків множення з'єднано відповідно з першим та другим входами другого суматора, виходи третього і шостого блоків множення з'єднано відповідно з першим та другим входами третього суматора, вихід першого суматора відповідно з'єднаний з першим входом одинадцятого блока множення і першим та другим входами сьомого блока множення, вихід другого суматора відповідно з'єднаний з першим входом дванадцятого блока множення і першим та другим входами шостого блока множення, вихід третього суматора відповідно з'єднаний з першим входом тринадцятого блока множення і першим та другим входами дев'ятого блока множення, виходи сьомого дев'ятого боків множення підключено відповідно до першого, другого і третього входів четвертого суматора, а вихід цього ж суматора з'єднано з блоком декрементування, вихід якого підключено до першого та другого інформаційних входів десятого блока множення і першого входу п'ятого суматора, а другий вхід якого з'єднано з виходом десятого блока множення, вихід п'ятого суматора з'єднано з регістром зсуву, вихід якого підключено до блока інкрементування, вихід якого з'єднано відповідно з другими інформаційними входами одинадцятого тринадцятого блоків множення, [стаття: Phong Shading Reformulation for Hardware Renderer Simplification, Apple Technical Report #43, Richard F. Lyon, Apple Computer, Inc, August 2, 1993]. Недоліки пристрою полягають у великих апаратних витратах за рахунок використання 13 блоків множення, 5 суматорів та низької точності визначення векторів нормалей за рахунок використання при апроксимації обмеженої кількості рядів Тейлора і багатоетапності перетворень. В основу корисної моделі поставлена задача створення пристрою, у якому реалізовано розрахунок векторів нормалей по рекурентному співвідношенні, що забезпечує підвищення швидкодії і точності визначення нормованих векторів нормалей. Поставлена задача вирішується тим, що в пристрій для нормалізації вектора нормалі, який включає перший, другий, третій блоки множення, виходи яких з'єднано з другими входами першого, другого і третього суматорів відповідно, додатково введено перший сьомий регістри, блок керування, лічильник, інформаційний вхід якого з'єднаний з восьмим інформаційним входом пристрою, вхід запису в лічильник підключено до четвертого керуючого входу пристрою, перший керуючий вхід якого підключено відповідно до перших керуючих входів першого, третього і п'ятого регістрів, другий керуючий вхід пристрою підключено відповідно до перших керуючих входів другого, четвертого і шостого регістрів, третій керуючий вхід пристрою підключений до керуючого входу сьомого регістра, а до других керуючих входів відповідно першого, другого, третього, четвертого, п'ятого і шостого регістрів підключено перший вихід блока керування, який також з'єднано з входом лічби лічильника, вихід переносу якого підключено до першого входу блока керування, другий, третій і четвертий входи якого відповідно з'єднані з п'ятим, шостим і сьомим керуючими входами пристрою, перший сьомий інформаційні входи якого з'єднано відповідно з першими інформаційними входами першого сьомого регістрів, інформаційні виходи відповідно першого, третього і п'ятого регістрів підключено до перших інформаційних входів першого, другого і третього суматорів, інформаційні виходи яких з'єднано відповідно з першим третім інформаційними виходами пристрою і другими інформаційними входами другого, четвертого і шостого регістрів, інформаційні виходи яких підключено відповідно до других інформаційних входів першо 5 18419 6 го, третього і п'ятого регістрів, а також кожний і-й першого, другого і третього суматорів, інформарозряд відповідно другого, четвертого і шостого ційний вихід регістру з'єднано з інформаційним регістрів з'єднано з (і+1)-ми розрядами других інвиходом другого, четвертого і шостого регістрів, формаційних входів першого, другого і третього третій керуючий вхід другого, четвертого і шостого блоків множення, а молодший розряд других інрегістрів підключено до керуючого входу мультипформаційних входів відповідно першого, другого і лексора. третього блоків множення заземляють, перші інНа Фіг.1 зображено структурну схему приформаційні входи відповідно першого, другого і строю; третього блоків множення з'єднано з інформаційна Фіг.2 - принципову схему реалізації блоку ним виходом сьомого регістра, інформаційні вихо15 керування; ди відповідно першого, другого і третього блоків на Фіг.3 - структурну схему регістра з двома множення підключено до других інформаційних інформаційними входами і інверсним інформаційвходів першого, другого і третього суматорів, вхоним виходом; ди переносу яких заземлено, другий і третій керуна Фіг.4 - структурну схему регістра з двома ючі виходи блока керування з'єднані відповідно з інформаційними входами; другим і першим керуючими виходами пристрою. на Фіг.5 приведено часову діаграму роботи Блок керування складається з першого, другого блоку 15 керування; елементу "І", першого і другого інвертора, першого на Фіг.6 зображено принцип сферично-кутової і другого D-тригера, перший вхід першого елеменінтерполяції векторів нормалей; та "І" з'єднано з сьомим керуючим входом прина Фіг.7 - розрахунок вектора Nk ; строю, який також з'єднаний з R-входом другого Dна Фіг.8 зображено рядок растеризації у трикутригера, D-вхід якого підключено до виходу пертнику. шого D-тригера, R-вхід якого з'єднано з виходом Пристрій для визначення векторів нормалей першого елементу "І", другий вхід якого підключе(Фіг.1) включає перший суматор 1, перший блок но до виходу переносу лічильника, на D-вхід пермноження 2, перший регістр 3, другий регістр 4, шого D-тригера подається логічна одиниця, С-вхід другий суматор 5, другий блок множення 6, третій першого D-тригера з'єднано з п'ятим керуючим регістр 7, четвертий регістр 8, третій суматор 9, входом пристрою, S-входи відповідно першого і третій блок множення 10, п'ятий регістр 11, шостий другого D-тригерів заземлено, а С-вхід другого Dрегістр 12, сьомий регістр 13, лічильник 14, блок тригера з'єднано з виходом першого інвертора, 15 керування. Блок 15 керування складається з вхід якого підключено до шостого керуючого входу першого елементу "І" 38, першого D-тригера 39, пристрою, який також підключено до другого входу першого інвертора 40, другого D-тригера 41, друдругого елементу "І", перший вхід якого з'єднано з гого елементу "І" 42 та другого інвертора 43. Регісвиходом другого D-тригера, вихід якого також з'єдтри 3, 7, 11 ідентичні і включають мультиплексор нано з другим керуючим виходом пристрою, а пе44, регістр 46 і елемент "І" 45. Регістри 4, 8, 12 рший керуючий вихід пристрою з'єднано з виходом ідентичні і включають мультиплексор 47, регістр другого елементу "І", вихід якого також підключено 49 і елемент "I'" 48. до входу другого інвертора, вихід якого з'єднано з Пристрій включає відповідно перший восьмий першим виходом блока керування. Перший, третій інформаційні входи 16 23, відповідно пері п'ятий регістри включають мультиплексор, регістр ший третій інформаційні виходи 24 26, відповідно і елемент "І", перший і другий входи якого з'єднано перший сьомий керуючі входи 27 33, перший 34, відповідно з першим і другим керуючими входами другий 35 керуючі виходи. першого, третього і п'ятого регістрів, вихід елеменВихід першого суматора 1 з'єднано з першим та "І" підключено до керуючого входу регістра, інінформаційним виходом пристрою 24 і другим інформаційний вхід якого підключено до інформаформаційним входом другого регістра 4. Перший ційного входу мультиплексора, перший та другий інформаційні входи першого суматора 1 інформаційний вхід якого з'єднано з першим інфоз'єднані відповідно з виходом першого регістра 3 рмаційним входом першого, третього і п'ятого регіта виходом першого блоку множення 2. Кожний і-й стрів, а другий інформаційний вхід підключено до розряд другого регістра 4 з'єднано з (і+1)-м розряінформаційного виходу другого, четвертого і шосдом другого інформаційного входу першого блоку того регістрів, інверсний інформаційний вихід регімноження 2, а молодший розряд другого інформастру з'єднано з інверсним інформаційним виходом ційного входу першого блоку множення 2 заземпершого, третього і п'ятого регістрів, третій керуюляють. Вихід другого регістра 4 з'єднано з другим чий вхід першого, другого і третього регістрів підкінформаційним входом першого регістра 3. Перлючено до керуючого входу мультиплексора. Друший інформаційний вхід першого блоку множення гий, четвертий і шостий регістри включають 2 з'єднано з виходом сьомого регістра 13. Перші мультиплексор, регістр і елемент "І", перший і друінформаційні входи першого 3 та другого 4 регістгий входи якого з'єднано відповідно з першим і рів підключено відповідно до першого 16 та другодругим керуючими входами другого, четвертого і го 17 інформаційних входів пристрою. Вихід другошостого регістрів, вихід елемента "І" підключено го суматора 5 з'єднано з другим інформаційним до керуючого входу регістра, інформаційний вхід виходом пристрою 25 і другим інформаційним якого підключено до інформаційного входу мульвходом четвертого регістра 8. Перший та другий типлексора, перший інформаційний вхід якого інформаційні входи другого суматора 5 з'єднані з'єднано з першим інформаційним входом другого, відповідно з виходом третього регістра 7 та вихочетвертого і шостого регістрів, а другий інформадом другого блоку множення 6. Кожний і-й розряд ційний вхід підключено до інформаційного виходу 7 18419 8 четвертого регістра 8 з'єднано з (і+1)-м розрядом льника 14 з'єднано з першим входом 37 блоку 15 другого інформаційного входу другого блоку мнокерування. Керуючі входи другий, третій, четверження 6, а молодший розряд другого інформаційтий блока 15 керування підключені відповідно до ного входу другого блоку множення 6 заземляють. п'ятого 31, шостого 32, сьомого 33 керуючих входів Вихід четвертого регістра 8 з'єднано з другим інпристрою. Третій вихід блоку 15 керування з'єднаформаційним входом третього регістра 7. Перший но з першим 34 керуючим виходом пристрою. Друінформаційний вхід другого блоку множення 6 гий вихід блоку 15 керування з'єднано з другим 35 з'єднано з виходом сьомого регістра 13. Перші керуючим виходом пристрою. інформаційні входи третього 7 та четвертого 8 Перший і другий керуючі входи регістрів 3, 7, регістрів підключено відповідно до третього 18 та 11 з'єднано відповідно з першим і другим входами четвертого 19 інформаційних входів пристрою. елемента "І" 45, вихід якого підключено до керуюВихід третього суматора 9 з'єднано з третім інфочого входу регістра 46. Третій керуючий вхід регісрмаційним виходом пристрою 26 і другим інфортрів 3, 7, 11 з'єднано з керуючим входом мультипмаційним входом шостого регістра 12. Перший та лексора 44. Перший і другий керуючі входи другий інформаційні входи третього суматора 3 регістрів 4, 8, 12 з'єднано відповідно з першим і з'єднані відповідно з виходом п'ятого регістра 11 другим входами елемента "І" 48, вихід якого підкта виходом третього блоку множення 10. Кожний ілючено до керуючого входу регістра 49. Третій й розряд шостого регістра 12 з'єднано з (і+1)-м керуючий вхід регістрів 4, 8, 12 з'єднано з керуюрозрядом другого інформаційного входу третього чим входом мультиплексора 47. блоку множення 10, а молодший розряд другого Вихід 34 - сигнал на виході підтверджує, що інформаційного входу третього блоку множення 10 дані, які сформовані на виходах 24, 25, 26 - достозаземляють. Вихід шостого регістра 12 з'єднано з вірні. Активний рівень сигналу - передній фронт. другим інформаційним входом п'ятого регістра 11. Вихід 35 - вихід "Кінець". Нульовий рівень сигналу Перший інформаційний вхід третього блоку мнона виході 35 сигналізує, що пристрій закінчив роження 10 з'єднано з виходом сьомого регістра 13. боту і готовий до прийому вхідних даних. ФункціоПерші інформаційні входи п'ятого 11 та шостого 12 нальне призначення входів 31-33 таке: вхід 31 регістрів підключено відповідно до п'ятого 20 та вхід "Пуск". Під дією сигналу, який поступає на вхід шостого 21 інформаційних входів пристрою. Інфо31 пристрій приступає до визначення векторів нормаційний вхід сьомого регістра 13 з'єднано з сьормалей; вхід 32 - вхід опорної імпульсної послідомим 22 інформаційним входом пристрою. вності, під дією якої здійснюється синхронізація Інформаційний вхід лічильника 14 з'єднано з роботи пристрою; вхід 33 - вхід "Початкова уставосьмим 23 інформаційним входом пристрою. новка". Під дією сигналу, що поступає на вхід 33, Перший інформаційний вхід регістрів 3, 7, 11 пристрій установлюється в початковий стан. з'єднано з інформаційним входом мультиплексора Перший та другий входи елементу "І" 38 з'єд44, другий інформаційний вхід якого з'єднано з нані відповідно з входами 33 і 37. Вихід елементу другим інформаційним входом регістрів 3, 7, 11. "І" 38 з'єднано з R-входом D-тригера 39. С-вхід DІнформаційний вихід мультиплексора 44 підклютригера 39 з'єднано з входом 31. S-вхід D-тригера чено до інформаційного входу регістра 46, інверс39 заземлено. R-вхід D-тригера 41 з'єднано з вхоний інформаційний вихід якого з'єднано з інверсдом 33. Вихід D-тригера 39 з'єднано з D-входом Dним виходом регістрів 3, 7, 11. Перший тригера 41. Інверсний вихід першого інвертора 40 інформаційний вхід регістрів 4, 8, 12 з'єднано з з'єднано з С-входом D-тригера 41. S-вхід Dінформаційним входом мультиплексора 47, другий тригера 41 заземлено. Вхід 32 з'єднано з першим інформаційний вхід якого з'єднано з другим інфоінвертором 40 і другим входом елемента "І" 42. рмаційним входом регістрів 4, 8, 12. ІнформаційПерший вхід елемента "І" 42 з'єднано з виходом Dний вихід мультиплексора 47 підключено до інфотригера 41. Вихід D-тригера 41 також з'єднано з рмаційного входу регістра 49, інформаційний вихід другим 35 керуючим виходом пристрою. Вихід якого з'єднано з виходом регістрів 4, 8, 12. елемента "І" 42 з'єднано з першим 34 керуючим Відповідно перший 1, другий 5 і третій 9 сумавиходом пристрою і входом другого інвертора 43. тори використовують для віднімання двох операнІнверсний вихід другого інвертора 43 з'єднано з дів у доповняльних кодах. Для цього вхід переносу першим виходом блока 15 керування. суматорів 1, 5, 9 заземляють, а на перші входи Регістри 3, 4, 7, 8, 11, 12, 13 використано для відповідно 1, 5, 9 суматорів подається інверсне збереження початкових і проміжних даних у прозначення 3, 7, 11 регістрів. цесі виконання операції визначення векторів норТреті керуючі входи регістрів 3, 4, 7, 8, 11, 12 малей. Блоки множення 2, 6, 10 призначені для підключено до другого керуючого виходу 35 блока виконання операції множення значення 2N(t) на 15 керування. Другі керуючі входи регістрів 3, 4, 7, cos . Суматори 1, 5, 9 призначені для віднімання 8, 11, 12 підключено до першого виходу 36 блока двох операндів у доповняльних кодах. Для цього 15 керування. Перший 36 вихід блока 15 керуванвхід переносу суматорів 1, 5, 9 заземляють, а на ня підключено до входу лічби лічильника 14. Перперші входи суматорів 1, 5, 9 подаються інверсні ші керуючі входи регістрів 3, 7, 11 підключено до значення перших операндів з регістрів 3, 7, 11. На першого керуючого входу 27. Перші керуючі входи другі інформаційні входи 1, 5, 9 суматорів подарегістрів 4, 8, 12 підключено до другого керуючого ються значення операндів від блоків 2, 6, 10 мновходу 28. Керуючий вхід сьомого 13 регістра підкження відповідно. Результатом виконання операції лючено до третього керуючого входу 29. Четвервіднімання буде отримання відповідно на 24, 25, тий керуючий вхід 30 підключено до керуючого 26 інформаційних виходах значень X, Y, Z коордивходу запису лічильника 14. Вихід переносу лічинат вектора нормалі. Блок 15 керування формує 9 18419 10 керуючі сигнали для роботи пристрою. зом Nb Na (Nb ·Na ) , то формула для визначення Лічильник 14 визначає закінчення процесу ройого модуля має такий вигляд: зрахунку векторів нормалей у рядку растеризації. 2 2 2 Лічильник виконує мікрооперацію віднімання одиNk Nb Na (Nb·Na ) Nb (Nb·Na )(Nb·Na ) (Nb·Na )2 Na ниці. . Розглянемо основні теоретичні положення, які Враховуючи, що Na і Nb - одиничні вектори, використані в запропонованому пристрої. то попереднє рівняння перепишемо таким чином: 1. Кутова інтерполяція (Фіг.5) одиничних векторів нормалей між початковим Na і кінцевим Nb векторами виконується згідно з виразом [Shoemake К. Animating rotation with quaternion curves //ACM SIGGRAPH. -Vol.19. -July 1985. pp.245-254]: sin((1 w ) ) sin( w ) N( w ) Na Nb (1) sin sin , де w [0,1], а - кут між векторами нормалей Na і Nb . Використовуючи тригонометричні співвідношення, перепишемо рівняння (1) у вигляді: sin cos( w ) cos sin( w ) sin( w ) N( w ) Na Nb sin sin . Na cos( w ) Na cos sin( w ) sin( w ) Nb sin sin . Запишемо останнє рівняння у вигляді: Nb Na cos sin( w ) sin Замінимо в формулі (2) функцію sin N( w ) Na cos( w ) 2 cos 2 , та представимо cos (2) на як скалярний добуток векторів векторами Na і Nb , Отримаємо: N( w ) Nb Nb Na (Nb·Na ) ( sin( w ) 3) 2 1 (Nb·Na ) що в виразі (3) множник Na cos( w ) Доведемо, Na (Nb ·Na ) sin( w ) - це нормалізований век 1 (Nb ·Na ) 2 тор Nb 1 2(Nb·Na )(Nb·Na ) (Nb·Na )2 Na (Nb ·Na ) , який є ортогональним до 1 (Nb·Na )2 . Тобто, знаменник у другому доданку формули (3) є модулем вектора Nk . Вектор Nk є ортогональним до Na . Дійсно, якщо Na Nk , то з прямокутного трикутника (Фіг.6) знаходимо: Nk Nb sin Враховуючи, що Nb Nk Після спрощення отримуємо: N( w ) Nk sin 1 (Nb ·Na ) 2 , оскільки (Nb ·Na ) Оскільки Nk 1, то cos Nb Na (Nb ·Na ) ,то 1 (Nb ·Na ) 2 (4) N( w ) Na cos( w ) Nk sin( w ) , Якщо рядок растеризації l - довжина рядка растеризації, то кут між двома сусідніми векторами нормалей буде дорівнювати: /l , (5) де arccos(Na ·Nb ) Із урахуванням останнього виразу, рівняння (4) перепишемо таким чином: (6) N( t ) Na cos(t ) Nk sin( t ) , де t - номер піксела вздовж рядка растеризації, t [0, l]. Запишемо вираз (6) в ітераційній формі. Знайдемо N( t 1) і N( t 1) . вектора Na . Позначимо його через Nk (Фіг.6). Якщо вектор Nk розраховується згідно з вираN( t 1) Na cos(( t 1) ) Nk sin(( t 1) ) Na cos(t ) cos Na sin( t ) sin Nk sin( t ) cos Nk cos(t ) sin N( t 1) Na cos((t 1) ) Nk sin(( t 1) ) Na cos(t ) cos Na sin( t ) sin Nk sin( t ) cos Nk cos(t ) sin Додавши N( t 1) і N( t 1) , отримуємо: N( t 1) N( t 1) 2 cos (Na cos(t ) Nk sin( t )) . З урахуванням формули (6), останній вираз перепишемо у вигляді: N( t 1) N( t 1) Звідси: 2N( t ) cos (7) N( t 1) . Із останньої формули можна зробити висно N( t 1) 2N( t ) cos вок, що одиничний вектор нормалі при сферичнокутовій інтерполяції можна знайти через два попередніх значення. Формулу (7) використано у корисній моделі для розрахунку нормалізованих векторів нормалей. Пристрій працює наступним чином. Структурну схему пристрою для розрахунку нормованих значень координат векторів нормалей наведено на Фіг.1. При включені напруги на вхід 33 подається імпульс нульового рівня, під дією якого блок 15 ке 11 18419 12 рування встановлюється в початковий стан. Нуякий поступає з блоку 15 керування на вихід 36. льовий рівень сигналу на виході 34 блока 15 керуАналогічно працює блок по визначенню Y ковання сигналізує, що пристрій готовий прийняти ординати, який включає суматор 5, блок множення вхідні дані. 6, регістр 7, перший інформаційний вхід якого Пристрій включає три аналогічні сукупності з'єднано з інформаційним входом пристрою 18 і блоків по формуванню X, Y, Z координат вектора регістр 8, перший інформаційний вхід якого з'єднормалі: блоки по формуванню Х координат; блонано з інформаційним входом пристрою 19, а таки по формуванню Y координат; блоки по формукож блок по визначенню Z координати, який вклюванню Z координат. Приведені блоки працюють чає суматор 9, блок множення 10, регістр 11, синхронно, їх робота абсолютно аналогічна. Принперший інформаційний вхід якого з'єднано з інфоцип роботи сукупності блоків по формуванню Х рмаційним входом пристрою 20 і регістр 12, перкоординати вектора нормалі приведено нижче. ший інформаційний вхід якого з'єднано з інформаУ циклі підготовки до визначення векторів ноційним входом пристрою 21. На виходах 24, 25 і 26 рмалей виконуються такі дії: у регістри 3, 4 від пристрою відповідно отримують одночасно X, Y, Z зовнішнього пристрою відповідно на входи 16, 17 координати вектора нормалі третьої точки в рядку подаються Х координати векторів у першій і другій растеризації. точках рядка растеризації, які записуються у вкаПісля отримання вектору нормалі, вміст лічизані регістри переднім фронтом сигналів, які посльника 14 зменшується на одиницю. Для цього на тупають на вхід 27, 28 пристрою відповідно. На виході 36 блока 15 керування формується імпульс інформаційний вхід регістра 13, який з'єднаний з від'ємної полярності. Активний фронт сигналу лічінформаційним входом 22 пристрою, подається би - передній фронт сигналу на виході 36 блока 15 керування. При досягненні лічильником нульового значення cos , яке записується у вказаний регістр стану на його виході переносу формується імпульс сигналом, який поступає на вхід 29. На інформавід'ємної полярності, який поступає на вхід 37 блоційний вхід лічильника 14, який з'єднаний з інфорка 15 керування і сигналізує, що пристрій закінчив маційним входом 23 пристрою, подається значенформування векторів нормалі у рядку растеризаня (n-2), яке записується у лічильник 14 нульовим ції. На виході 35 блока 15 керування формується рівнем сигналу, де n - кількість точок у рядку расрівень логічного нуля, який сигналізує про завертеризації. шення роботи пристрою. При подачі на п'ятий вхід 31 пристрою сигналу Часову діаграму блоку 15 керування наведено "Пуск" починається робота по формуванню норна Фіг.5, принципову схему реалізації блоку керумалізованих векторів нормалей. Активний рівень вання - на Фіг.2. сигналу на п'ятому 31 вході пристрою - нульовий Блок 15 керування працює наступним чином: рівень сигналу. У початковий момент часу на вхід 37 пристрою Із виходу регістра 4 на другий вхід блока 2 поступає імпульс від'ємної полярності, під дією множення подається подвоєне значення операнду якого D-тригера 39 і 41 відповідно обнулюються. 2Nx(t). Це досягається за рахунок монтажного зсуПочатковий стан сигналу на вході 33 початкової ву, для чого молодший розряд другого інформаустановки - одиниця. Після запису вхідних даних у ційного входу блока 2 множення заземляють, а регістри 3, 4, 7, 8, 11, 12, 13 і лічильник 14, на друкожний (і-й) розряд регістра 4 підключають до (і+1) гий вхід 31 "Пуск" поступає імпульс від'ємної полярозряду блока 2 множення. На перший вхід блока рності, під дією переднього фронту якого тригер 39 2 множення подається значення cos . У блоці 2 установлюється в одиничний стан. D-вхід тригера множення виконується множення cos з подвоє39 підключено до логічної одиниці, a S-входи триним значенням Х координати другої точки в рядку герів 39 і 41 заземляють. растеризації. З виходу блока 2 множення отримаПід дією заднього фронту імпульсної послідоний добуток 2Nx(t) cos надходить на вхід суматовності, яка поступає на вхід 32, тригер 41 установра 1, де від нього віднімається значення Х коордилюється в одиничний стан, оскільки на інверсному нати першої точки рядка растеризації, яке виході тригера 39 присутній рівень логічної одинизберігається в регістрі 3. Суматор 1 працює у реці. При формуванні лічильником 14 сигналу пережимі віднімання двох операндів у доповняльних носу на R-вхід тригера 39 подається рівень логічкодах. Для цього вхід переносу суматора заземного нуля і тригер 39 обнулюється. Заднім ляють, а на перший вхід суматора подається інвефронтом імпульсної послідовності на вході 32 обрсне значення першого операнду з виходу першонулюється тригер 41. Нульове значення на виході го регістру. На виході суматора 1 отримують тригера 41 поступає на другий вихід пристрою 35 значення Х координати вектора нормалі третьої "Кінець" і сигналізує, що пристрій закінчив формуточки рядка растеризації. вання векторів нормалі у рядку растеризації. НуДостовірність отримання Х координати вектольове значення на виході тригера 41 поступає на ра нормалі на інформаційному виході 24 пристрою перший вхід елемента "І" 42, на другий вхід якого підтверджується переднім фронтом сигналу, який поступає значення з входу 32. Рівень логічної одиформується на першому керуючому виході 34 приниці на виході елемента "І" 42 поступає на керуюстрою. чий вихід 34 пристрою, який підтверджує, що дані, Для формування вектора нормалі у наступній які сформовані на виходах 24, 25, 26 - достовірні. точці рядка растеризації значення Х координати Також рівень логічної одиниці на виході елемента другої точки рядка растеризації, яке зберігається в "І" 42 поступає на вхід інверсного елемента 43, регістрі 4, записується в регістр 3. Отримане знанульове значення якого поступає на перший вихід чення Х координати третьої точки в рядку расте36 блока 15 керування. ризації записується в регістр 4 під дією сигналу, 13 18419 14 Регістри 3, 7, 11 працюють таким чином. При Розроблений пристрій для визначення вектозначенні нуля на вході 35 через мультиплексор 44 рів нормалей має менші апаратні витрати порівняна вхід регістра 46 поступає операнд з другого но з прототипом, оскільки містить меншу кількість інформаційного входу регістра 3 (7, 11). При надблоків: 3 блоки множення і 3 суматора на відміну ходженні сигналу з виходу елемента "І" 45 на кевід прототипу, який містить 13 блоків множення і 5 руючий вхід регістра 46, вказаний операнд записусуматорів. Пристрій прототип для визначення векється в регістр 46. Інверсне значення операнду з тора нормалі використовує обмежену кількість регістра 46 поступає на інформаційний вихід регісрядів Тейлора, що призводить до втрати точності трів 3, 7, 11. Активний рівень сигналу запису - перезультуючого значення вектору нормалі. редній фронт сигналу. Регістри 4, 8, 12, які вклюЗапропонований пристрій визначає точні значають мультиплексор 47, регістр 49 і елемент "І" чення вектора нормалі. Процес визначення векто48, працюють аналогічно регістрам 3, 7, 11 за вира нормалі в пристрої прототипу включає 10 етанятком тільки того, що з їх виходів поступає пряме пів, а в запропонованому пристрої лише два значення операнду на виходи регістрів 4, 8, 12. етапи. У наведеному пристрої використано тільки мікросхеми, які серійно випускаються. 15 Комп’ютерна верстка Л.Литвиненко 18419 Підписне 16 Тираж 26 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for determining normalized vectors

Автори англійськоюRomaniuk Oleksandr Nykyforovych

Назва патенту російськоюУстройство для определения нормированных нормальных векторов

Автори російськоюРоманюк Александр Никифорович

МПК / Мітки

МПК: G06T 15/50

Мітки: нормалей, векторів, нормованих, пристрій, визначення

Код посилання

<a href="https://ua.patents.su/8-18419-pristrijj-dlya-viznachennya-normovanikh-vektoriv-normalejj.html" target="_blank" rel="follow" title="База патентів України">Пристрій для визначення нормованих векторів нормалей</a>

Попередній патент: Пристрій для сушіння сільськогосподарських кормів

Наступний патент: Спосіб відновлення шкірного покриву при опікових ураженнях

Випадковий патент: Спосіб гідророзриву пласта