Інтерфейсна схема і спосіб передачі даних між послідовним інтерфейсом і процесором

Формула / Реферат

1. Інтерфейсна схема для передачі даних через послідовний інтерфейс від процесора і до процесора, яка відрізняється тим, що між послідовним інтерфейсом і процесором встановлений лише один запам'ятовуючий пристрій об'ємом на кілька слів шини чи процесора, причому запам'ятовуючий пристрій виконаний з можливістю здійснення запису і зчитування послівно або побітно.

2. Схема за п.1, яка відрізняється тим, що запам'ятовуючий пристрій зворотного магазинного типу містить вказівник запису і вказівник зчитування, здатні окремо адресувати кожен біт або кожне слово (наприклад байт).

3. Схема за п.1 або 2, яка відрізняється тим, що процесор виконаний з можливістю переведення в режим економії струму (режим "очікування").

4. Схема за одним із пп. 1-3, яка відрізняється тим, що в запам'ятовуючий пристрій зворотного магазинного типу вбудовано компаратор.

5. Схема за п. 4, яка відрізняється тим, що компаратор містить просту логічну схему (50), виконану з можливістю автоматичного порівняння кожного прийнятого біта (2) з вмістом комірки (1) запам'ятовуючого пристрою зворотного магазинного типу, в яку має бути записаний прийнятий біт (2).

6. Схема за одним із пунктів 1-5, яка відрізняється тим, що запам'ятовуючий пристрій зворотного магазинного типу інтегрований в процесорний модуль (34).

7. Схема за одним із пунктів 1-5, яка відрізняється тим, що запам'ятовуючий пристрій зворотного магазинного типу інтегрований в приймальний модуль (40).

8. Схема за одним із пунктів 1-5, яка відрізняється тим, що запам'ятовуючий пристрій зворотного магазинного типу реалізований з використанням комірок стандартної пам'яті з довільною вибіркою в адресному полі процесора.

9. Схема за одним із пунктів 1-8, яка відрізняється тим, що додатково до запам'ятовуючого пристрою зворотного магазинного типу вона містить модуль формування контрольної суми.

10. Схема за п. 9, яка відрізняється тим, що додатково до модуля формування контрольної суми вона містить компаратор, виконаний з можливістю порівняння контрольної суми прийнятих даних з очікуваною попередньо вирахованою контрольною сумою.

11. Схема за одним із пунктів 1-10, яка відрізняється тим, що запам'ятовуючий пристрій зворотного магазинного типу виконаний у формі кільцевої структури.

12. Схема за одним із пунктів 1-11, яка відрізняється тим, що запам'ятовуючий пристрій зворотного магазинного типу містить пристрій контролю переповнення, виконаний з можливістю активізації процесора при загрозі переповнення запам'ятовуючого пристрою зворотного магазинного типу.

13. Спосіб передачі даних між послідовним інтерфейсом і процесором, який відрізняється тим, що дані послідовно побітно приймають і записують у запам'ятовуючий пристрій зворотного магазинного типу і з нього за допомогою процесора знову побайтно зчитують, або за допомогою процесора побайтно записують у запам'ятовуючий пристрій зворотного магазинного типу і звідти побітно передають.

14. Спосіб за п. 13, який відрізняється тим, що запис даних до запам'ятовуючого пристрою зворотного магазинного типу і зчитування даних з нього здійснюють процесором лише послідовно шляхом автоматичного встановлення вказівників запису і зчитування запам'ятовуючого пристрою зворотного магазинного типу без навантаження процесора.

15. Спосіб за п. 13, який відрізняється тим, що процесором вивільняють вказівники запису і зчитування запам'ятовуючого пристрою зворотного магазинного типу.

16. Спосіб за п. 13 або 15, який відрізняється тим, що як окремі комірки запам'ятовуючого пристрою зворотного магазинного типу використовують елементи пам'яті з довільною вибіркою із власного адресного поля процесора, операції запису і зчитування стосовно яких здійснюють за допомогою процесора.

17. Спосіб за одним із пунктів 13 - 16, який відрізняється тим, що здійснюють автоматичне порівняння даних, причому очікувані дані записують до певних комірок запам'ятовуючого пристрою зворотного магазинного типу і за допомогою простої логічної схеми (50) кожен прийнятий біт (2) порівнюють із вмістом комірки (51) пам'яті запам'ятовуючого пристрою зворотного магазинного типу, до якої він має бути записаний.

18. Спосіб за п. 17, який відрізняється тим, що за допомогою вказівника (53) запису запам'ятовуючого пристрою здійснюють як адресування очікуваного біта, з яким має бути порівняний прийнятий біт, так і адресування прийнятого біта (2), що має бути записаний до запам'ятовуючого пристрою.

19. Спосіб за п. 17 або 18, який відрізняється тим, що після порівняння всіх бітів одного байта поставлений у відповідність даному байту біт (4) встановлюють у стан логічного нуля, якщо всі біти однакові, і у стан логічної одиниці в іншому разі.

20. Спосіб за п. 19, який відрізняється тим, що до бітів, поставлених у відповідність байтам, здійснюють побайтний доступ процесором.

21. Спосіб за одним із пунктів 13-20, який відрізняється тим, що процесор під час передачі даних перемикають у режим економії струму.

22. Спосіб за п. 21, який відрізняється тим, що процесор активізують при загрозі переповнення запам'ятовуючого пристрою зворотного магазинного типу.

23. Спосіб за одним із пунктів 13-16, який відрізняється тим, що здійснюють порівняння даних, при якому автоматично порівнюють контрольну суму прийнятих даних з попередньо вирахованою контрольною сумою очікуваних даних.

24. Спосіб за одним із пунктів 21-23, який відрізняється тим, що передачу даних із запам'ятовуючого пристрою зворотного магазинного типу здійснюють в час, коли процесор перебуває в режимі економії споживаного струму без активізації процесора.

25. Спосіб за одним із пунктів 21-24, який відрізняється тим, що після передачі даних здійснюють автоматичне перемикання в режим прийому даних без активізації процесора.

Текст

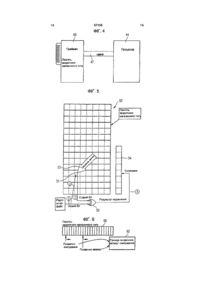

1 Інтерфейсна схема для передачі даних через послідовний інтерфейс від процесора і до процесора, яка відрізняється тим, що між послідовним інтерфейсом і процесором встановлений лише один запам'ятовуючий пристрій об'ємом на кілька слів шини чи процесора, причому запам'ятовуючий пристрій виконаний з можливістю здійснення запису і зчитування послівно або побітно 2 Схема за п 1, яка відрізняється тим, що запам'ятовуючий пристрій зворотного магазинного типу містить вказівник запису і вказівник зчитування, здатні окремо адресувати кожен біт або кожне слово (наприклад байт) 3 Схема за п 1 або 2, яка відрізняється тим, що процесор виконаний з можливістю переведення в режим економії струму (режим "очікування") 4 Схема за одним із пп 1-3, яка відрізняється тим, що в запам'ятовуючий пристрій зворотного магазинного типу вбудовано компаратор 5 Схема за п 4, яка відрізняється тим, що компаратор містить просту логічну схему (50), виконану з можливістю автоматичного порівняння кожного прийнятого біта (2) з вмістом комірки (1) запам'ятовуючого пристрою зворотного магазинного типу, в яку має бути записаний прийнятий біт (2) 6 Схема за одним із пунктів 1-5, яка відрізняється тим, що запам'ятовуючий пристрій зворотного магазинного типу інтегрований в процесорний модуль (34) 7 Схема за одним із пунктів 1-5, яка відрізняється тим, що запам'ятовуючий пристрій зворотного магазинного типу інтегрований в приймальний модуль (40) 8 Схема за одним із пунктів 1-5, яка відрізняєть ся тим, що запам'ятовуючий пристрій зворотного магазинного типу реалізований з використанням комірок стандартної пам'яті з довільною вибіркою в адресному полі процесора 9 Схема за одним із пунктів 1-8, яка відрізняється тим, що додатково до запам'ятовуючого пристрою зворотного магазинного типу вона містить модуль формування контрольної суми 10 Схема за п 9, яка відрізняється тим, що додатково до модуля формування контрольної суми вона містить компаратор, виконаний з можливістю порівняння контрольної суми прийнятих даних з очікуваною попередньо вирахованою контрольною сумою 11 Схема за одним із пунктів 1-10, яка відрізняється тим, що запам'ятовуючий пристрій зворотного магазинного типу виконаний у формі кільцевої структури 12 Схема за одним із пунктів 1-11, яка відрізняється тим, що запам'ятовуючий пристрій зворотного магазинного типу містить пристрій контролю переповнення, виконаний з можливістю активізації процесора при загрозі переповнення запам'ятовуючого пристрою зворотного магазинного типу 13 Спосіб передачі даних між послідовним інтерфейсом і процесором, який відрізняється тим, що дані послідовно побітно приймають і записують у запам'ятовуючий пристрій зворотного магазинного типу і з нього за допомогою процесора знову побайтно зчитують, або за допомогою процесора побайтно записують у запам'ятовуючий пристрій зворотного магазинного типу і звідти побітно передають 14 Спосіб за п 13, який відрізняється тим, що запис даних до запам'ятовуючого пристрою зворотного магазинного типу і зчитування даних з нього здійснюють процесором лише послідовно шляхом автоматичного встановлення вказівників запису і зчитування запам'ятовуючого пристрою зворотного магазинного типу без навантаження процесора 15 Спосіб за п 13, який відрізняється тим, що процесором вивільняють вказівники запису і зчитування запам'ятовуючого пристрою зворотного магазинного типу 16 Спосіб за п 13 або 15, який відрізняється О Ю Ю 1 ю 57155 20 Спосіб за п 19, який відрізняється тим, що до тим, що як окремі комірки запамятовуючого прибітів, поставлених у ВІДПОВІДНІСТЬ байтам, строю зворотного магазинного типу використовуздійснюють побайтний доступ процесором ють елементи пам'яті з довільною вибіркою із вла21 Спосіб за одним із пунктів 13-20, який сного адресного поля процесора, операції запису і відрізняється тим, що процесор під час передачі зчитування стосовно яких здійснюють за допомоданих перемикають у режим економії струму гою процесора 17 Спосіб за одним із пунктів 13 - 16, який відріз22 Спосіб за п 21, який відрізняється тим, що няється тим, що здійснюють автоматичне порівпроцесор активізують при загрозі переповнення няння даних, причому очікувані дані записують до запам'ятовуючого пристрою зворотного магазинпевних комірок запам'ятовуючого пристрою звороного типу тного магазинного типу і за допомогою простої 23 Спосіб за одним із пунктів 13-16, який відрізлогічної схеми (50) кожен прийнятий біт (2) порівняється тим, що здійснюють порівняння даних, нюють із вмістом комірки (51) пам'яті запам'ятовупри якому автоматично порівнюють контрольну ючого пристрою зворотного магазинного типу, до суму прийнятих даних з попередньо вирахованою якої він має бути записаний контрольною сумою очікуваних даних 18 Спосіб за п 17, який відрізняється тим, що за 24 Спосіб за одним із пунктів 21-23, який допомогою вказівника (53) запису запам'ятовуючовідрізняється тим, що передачу даних із заго пристрою здійснюють як адресування очікуванопам'ятовуючого пристрою зворотного магазинного го біта, з яким має бути порівняний прийнятий біт, типу здійснюють в час, коли процесор перебуває в так і адресування прийнятого біта (2), що має бути режимі економії споживаного струму без акзаписаний до запам'ятовуючого пристрою тивізації процесора 19 Спосіб за п 17 або 18, який відрізняється 25 Спосіб за одним із пунктів 21-24, який тим, що після порівняння всіх бітів одного байта відрізняється тим, що після передачі даних поставлений у ВІДПОВІДНІСТЬ даному байту біт (4) здійснюють автоматичне перемикання в режим встановлюють у стан логічного нуля, якщо всі біти прийому даних без активізації процесора однакові, і у стан логічної одиниці в іншому разі Винахід стосується штерфейсної схеми для передачі даних через послідовний інтерфейс від і до процесора, а також способу передачі даних між послідовним інтерфейсом і процесором Даний винахід має служити для послідовної, зокрема безпровідної передачі даних до процесора, розміщеного, наприклад, на чіп-картці Особливо придатний цей винахід для безпровідної передачі даних між пристроєм для зчитування карток і безконтактною карткою з процесором В цих випадках застосування процесор має бути розвантажений, щоб при обміні даними міг бути використаний процесор, керований тактовими імпульсами з меншою частотою Завдяки цьому споживання струму має знизитися (споживання струму пропорційне тактовій частоті) Крім того, процесор має якомога частіше і на якомога більш тривалий час перемикатися у режим очікування, або так званий режим Stand-by, в якому процесор не працює ("спить") і тому споживає значно менший струм Згідно З ВІДОМИМ рівнем техніки передачу даних між послідовним інтерфейсом І процесором здійснюють за допомогою паралельнопослідовного або послідовно-паралельного перетворення у так званому універсальному асинхронному приймачі/передавачі (УАПП) (UART = Universal Asynchronus Receiver Transmitter) Цей приймач/передавач зазвичай реалізовують у вигляді зсувного регістра на стороні, до якої приєднаний, наприклад, приймач/передавач безпровідної передачі В цьому зсувному регістрі побітно може бути здійснений запис (при прийомі) і зчитування (при передачі) Процесор мусить на ІНШІЙ стороні УАПП ВІДПОВІДНО до використовуваного протоколу передачі даних паралельно і синхронно приймати дані від УАПП або передавати їх (див фіг 1 і 2) Це висуває високі вимоги до процесора стосовно роботи в реальному часі Такі високі вимоги стосовно роботи в реальному часі вступають у протиріччя з вимогою низького струму споживання і низької ціни Саме в безконтактних чіп-картках мають бути застосовані процесори, управління якими здійснюється якомога простіше і з якомога нижчою тактовою частотою, тому вони споживають дуже малий струм і дуже дешеві Але такі процесори не можуть задовольняти вказаній вище вимозі стосовно роботи в реальному масштабі часу Тому в безконтактних картках згідно з рівнем техніки використовують спосіб при якому послідовну інформацію побітно отримують від контакту послідовного інтерфейсу або посилають на контакт послідовного інтерфейсу Одначе ця задача вимагає надто багато робочого часу процесора, тому знову виникає потреба в застосуванні швидкодійного процесора Тому задача даного винаходу полягає в розробці штерфейсної схеми для передачі даних через послідовний інтерфейс від і до процесора, при якій передача даних може відбуватися без значного навантаження процесора Крім того, задачею винаходу є розробка придатного способу передачі даних між послідовним інтерфейсом і процесором Згідно З винаходом ця задача вирішена за допомогою штерфейсної схеми в якій між послідовним інтерфейсом і процесором під'єднано запам'ятовуючий пристрій (ЗП) об'ємом на кілька слів (наприклад, байт) Задача вирішена також за допомогою способу, згідно з яким дані послідовно побітно приймають і записують у запам'ятовуючий пристрій, а звідти процесором побітно знову зчитують їх, або процесором записують у запам'ятовуючий пристрій, а 57155 звідти побітно передають ким чином досягається подальше спрощення проПри цьому доцільним є виконання, при якому грамування і структури схеми запис і зчитування даних може бути здійснене поПри цьому після порівняння всіх бітів одного слівне або побітно Для цього запам'ятовуючий байта поставлений у ВІДПОВІДНІСТЬ цьому байту біт пристрій оснащують покажчиком запису і покажчивстановлюється у стан логічного нуля, якщо всі ком зчитування, які кожен біт і кожне слово (наприбіти були однакові, інакше він встановлюється в клад байт) можуть адресувати окремо стан логічної одиниці При цьому особливо доцільним є забезпечення процесору побайтного доступу З метою подальшого зменшення споживання до поставлених у ВІДПОВІДНІСТЬ бітів Шляхом розструму доцільним є виконання процесора з можмаскування порівняльної інформації можуть бути ливістю переведення його в режим економії спошвидко і просто оцінені прийняті біт-послідовності живаного струму (режим Standby) Крім того, доцільним є оснащення запам'ятоДоцільним Є переведення процесора під час вуючого пристрою компаратором Завдяки цьому передачі даних у режим економи струму (режим досягається подальше розвантаження процесора "спання" або готовності (Stand by)) При цьому має бути передбачено, щоб процесор активізувався При цьому компаратор доцільно оснастити ("прокидався") при виникненні загрози переповпростою логічною схемою, яка автоматично порівнення запам'ятовуючого пристрою нює кожен прийнятий біт із вмістом комірки запам'ятовуючого пристрою, до якої має бути записаЗамість порівняно витратного порівняння ний прийнятий біт окремих бітів може бути передбачене також автоматичне порівняння даних, яке здійснюється шляДля подальшого спрощення схеми запам'ятохом автоматичного порівняння контрольної суми вуючий пристрій може бути інтегрований у процеприйнятих даних із наперед вирахуваною контросорний модуль або у приймальний модуль Подальною сумою очікуваних даних льше спрощення схеми можливе також за рахунок того, що запам'ятовуючий пристрій реалізується Таким чином може бути досягнуте подальше на комірках з довільним доступом із стандартної розвантаження процесора завдяки тому, що порівоперативної пам'яті в адресному полі процесора няння, наприклад, серійного номера безконтактної чіп-картки здійснюється автоматично і без залуДля подальшого розвантаження процесора чення процесора під час прийому даних додатково до запам'ятовуючого пристрою може бути передбачений модуль формування контрольВинайденим способом можуть бути оброблені ної суми Додатково до модуля контрольної суми також протоколи, які допускають передачу фрагможе бути передбачений компаратор який порівментів байта (наприклад, лише 3 біти) нює контрольну суму прийнятих даних з очікуваЯк застосування багатобайтних запам'ятовуюною, попередньо вирахуваною контрольною сучих пристроїв у послідовних інтерфейсах чіпмою Таким чином може бути досягнуте подальше карток, так і застосування таких автоматичних розвантаження процесора схем і способів порівняння у комбінації з одним процесором досі ВІДОМІ не були Доцільною Є реалізація запам'ятовуючого пристрою у формі кільцевої структури оснащеної приНижче винахід детальніше пояснюється за достроєм запобігання переповненню який при загрозі помогою форм виконання з використанням фігур переповнення запам'ятовуючого пристрою активіНа них схематично зображено зує ("будить") процесор Завдяки цьому можуть фіг 1 Рівень техніки з послідовною передачею бути уникнуті втрати даних внаслідок переповненміж приймальним модулем і процесорним модуня запам'ятовуючого пристрою лем, Згідно З винайденим способом для розвантафіг 2 Рівень техніки з приєднанням приймальження процесора стан покажчика запису і покажного модуля до шини процесора, чика зчитування може бути змінений автоматично фіг 3 Відповідне винаходу рішення з послідобез залучення процесора вною передачею між приймальним модулем і процесорним модулем, Значної гнучкості надає програмуванню спосіб, згідно з яким процесор може вивільняти покажчики фіг 4 Відповідне винаходу рішення з приєдзапису і зчитування нанням приймального модуля до шини процесора, Ще більшої гнучкості надає програмуванню фіг 5 ВІДПОВІДНИЙ винаходу запам'ятовуючий спосіб, згідно з яким процесор оброблює окремі пристрій зворотного магазинного типу (з алгориткомірки пам'яті як складові власного адресного мом "першим увійшов - першим вийшов") з компаполя і, таким чином, вільно може здійснювати заратором для перевірки правильності очікуваних пис і зчитування даних, Подальше розвантаження процесора може буфіг 6 Принцип дії запам'ятовуючого пристрою ти досягнуто завдяки використанню автоматичного зворотного магазинного типу, порівняння даних, причому очікувані дані мають фіг 7 Відповідне винаходові порівняння даних бути записані у ВІДПОВІДНІ МІСЦЯ пам'яті і за допопро утворення контрольної суми, могою простої логічної схеми кожен прийнятий біт фіг 8 Утворення контрольної суми паралельно має бути порівняний зі вмістом комірки пам'яті, в до завантаження даних в запам'ятовуючий прияку він має бути записаний стрій зворотного магазинного типу При цьому покажчик запису запам'ятовуючого Фігури 1 і 2 ілюструють проблеми рівня техніпристрою має здійснювати як адресування очікуки В першому варіанті приймач 10 через послідованого біта, з яким має бути порівняний прийнятий вну ЛІНІЮ зв'язку 12 з'єднаний з процесорним мобіт, так і адресування прийнятого біта, що має будулем 14, в якому передбачений універсальний ти записаний до запам'ятовуючого пристрою Таасинхронний приймач/передавач (УАПП) (UART = 57155 Universal Asynchronus Receiver Transmitter) Інше рішення рівня техніки передбачає наявність приймального модуля 20, який сам містить схему УАПП, а потім через шину 22 даних процесора 24 приєднаний до нього На противагу цьому фігури 3 і 4 ілюструють винайдене рішення Згідно з фіг 3 знову використовують приймальний модуль ЗО з послідовним інтерфейсом Через послідовну ЛІНІЮ 32 зв'язку приймальний модуль ЗО з'єднаний з процесорним модулем 34 Одначе в процесорному модулі 34 замість схеми УАПП передбачений ЗП зворотного магазинного типу (запам'ятовуючий пристрій з алгоритмом "першим увійшов - першим вийшов", FiFo = First-m-First-out) ємністю, наприклад, 32 байти В такому разі при прийомі даних їх побітно записують у цей запам'ятовуючий пристрій зворотного магазинного типу По закінченні запису одного байта автоматично побітно записують наступний байт, поки не буде записаний увесь блок даних Передачу здійснюють аналогічно прийому, тобто дані байт за байтом зчитують із запам'ятовуючого пристрою зворотного магазинного типу Як процес приймання, так і процес передачі можуть відбуватися незалежно від процесора Під час цих процедур процесор може перебувати в режимі очікування (Stand-by) зі споживанням струму, яким можна знехтувати Процесор може побайтно послідовно зчитувати вміст запам'ятовуючого пристрою зворотного магазинного типу або побайтно послідовно записувати в нього дані Є можливість окремого адресування кожного біта в запам'ятовуючому пристрої зворотного магазинного типу за допомогою покажчика запису і покажчика зчитування Завдяки цьому можуть бути прийняті або передані також неповні байти, наприклад, лише 3 біти При цьому вимоги до процесора стосовно роботи в реальному масштабі часу значно нижчі, ніж у варіантах згідно з рівнем техніки зі схемою УАПП Альтернативно до запам'ятовуючого пристрою зворотного магазинного типу може бути застосований також ЗП магазинного типу (запам'ятовуючий пристрій з алгоритмом "останнім увійшовпершим вийшов", LiFo = Last-m-First-out) При цьому лише ПОСЛІДОВНІСТЬ прийнятих і переданих даних інвертують Це може бути враховано при програмуванні або може бути навіть бажаним Самозрозуміло, що у наступних формах виконання винаходу також може бути використаний запам'ятовуючий пристрій з алгоритмом "останнім увійшов-першим вийшов" Таким чином, у формі виконання згідно з фіг З запам'ятовуючий пристрій зворотного магазинного типу інтегрований у процесорний модуль При цьому запам'ятовуючий пристрій зворотного магазинного типу може бути реалізований навіть на комірках з довільною вибіркою із стандартної оперативної пам'яті в адресному полі процесора Завдяки цьому відпадає необхідність у додаткових запам'ятовуючих елементах На фіг 4 представлена наступна форма виконання винаходу При цьому запам'ятовуючий пристрій зворотного магазинного типу інтегрований у приймальний модуль 40 Останній через процесорну шину 42 з'єднаний з процесорним модулем 44 8 Як у формі виконання винаходу згідно з фіг З, так і у формі виконання згідно з фіг 4 може бути передбачено, що звертання процесора до запам'ятовуючого пристрою зворотного магазинного типу для запису і для зчитування може здійснюватися лише послідовно Таким чином виключається довільний доступ процесора до запам'ятовуючого пристрою зворотного магазинного типу Це робить суттєвий внесок у безпеку даних, коли необхідно запобігти спробам зміни даних однієї прикладної програми шляхом маніпуляції з іншою прикладною програмою Одначе, можливе значно гнучкіше програмування, коли процесорможе скидати у початковий стан покажчик запису і покажчик зчитування запам'ятовуючого пристрою зворотного магазинного типу Таким чином може бути задано, в якому МІСЦІ (з точністю до біта) здійснює запис чи зчитування процесор, а також в якому МІСЦІ (З ТОЧНІСТЮ ДО біта) здійснює запис чи зчитування безпровідний інтерфейс Подальше підвищення гнучкості доступу досягається завдяки тому, що процесор розглядає окремі розряди запам'ятовуючого пристрою зворотного магазинного типу як складові його логічної адресної зони і може здійснювати запис і зчитування довільно і незалежно від покажчиків запису чи зчитування Це рішення особливо придатне у поєднанні з реалізацією запам'ятовуючого пристрою зворотного магазинного типу з використанням запам'ятовуючих комірок стандартної оперативної пам'яті процесора В кожній з описаних форм виконання запам'ятовуючого пристрою зворотного магазинного типу додатково може бути передбачений компаратор або схема автоматичної перевірки контрольної суми Додатково до запам'ятовуючого пристрою зворотного магазинного типу може бути передбачена також схема УАПП згідно з рівнем техніки, наприклад, з метою надання можливості звичайним чином обробляти протоколи з довгим форматом даних (наприклад, 40-байтні протоколи в разі 32-байтного запам'ятовуючого пристрою зворотного магазинного типу) Особливу перевагу має організація запам'ятовуючого пристрою зворотного магазинного типу у формі кільцевої структури Тоді В разі загрози переповнення запам'ятовуючого пристрою зворотного магазинного типу процесор активізується ("прокидається") для обробки цих даних із запам'ятовуючого пристрою зворотного магазинного типу В разі необхідності запам'ятовуючий пристрій зворотного магазинного типу може працювати також як "класична" схема УАПП згідно з рівнем техніки Самозрозуміле, що запам'ятовуючий пристрій зворотного магазинного типу може бути реалізований також і з процесорами без режиму економії струму Для додаткового розвантаження процесора може бути реалізований автоматичний компаратор в штерфейсній схемі Завдяки цьому процесор звільняється від задачі порівняння прийнятих даних з очікуваними даними (наприклад для аутен 57155 10 запамятовуючии пристрій зворотного магазинного типу порожній Це виявляє відповідна диференційна схема 62 Після цього формують або логічний нуль, або повідомлення проте, що зчитування більше не може бути здійснене Оскільки диференційна схема 62 постійно видає інформацію про КІЛЬКІСТЬ бітів у запам'ятовуючому пристрої зворотного магазинного типу ця схема може бути використана також для активування процесора перед переповненням запам'ятовуючого пристрою зворотного магазинного типу і ініціювання обробки даних з тим щоб знову звільнити місце у запам'ятовуючому пристрої зворотного магазинного типу Наступна відповідна винаходові можливість порівняння даних полягає в автоматичному формуванні контрольної суми отриманих даних, наприклад за методом циклічного надлишкового коду (CRCметод), яку порівнюють з наперед (наприклад при Ініціалізації") вирахованою контрольною сумою очікуваних даних Одначе цей спосіб не такий ефективний, як описаний за фіг 5 компаратор у запам'ятовуючому пристрої зворотного магазинного типу, оскільки контрольні суми отриманих і очікуваних даних мають порівнюватися процесором А це знову навантажує процесор Крім того для надійного розпізнавання блок даних може містити Після порівняння і запису до запам'ятовуючого максимум одну помилку До того ж логічна схема пристрою 52 зворотного магазинного типу всіх мусить відрізняти дані від команд, оскільки інакше бітів байта в разі позитивного результату порівконтрольна сума прийнятих даних за певних умов няння здійснюють встановлення поставленого у може формуватися командою, ВІДМІННОЮ ВІД коВІДПОВІДНІСТЬ цьому байту спеціального біта порівманди формування контрольної суми очікуваних няльного регістра 54 у стан логічного нуля, в інданих Це показано окремо на фігурах 7 і 8 шому разі цей біт встановлюють у стан логічної одиниці Із очікуваних даних CRC-методом вираховують контрольну суму Вона складається із двох Схема порівняння працює таким чином перед байтів Потім також CRC-методом вираховують початком операції порівняння регістр 54 встановконтрольну суму із отриманих даних Після цього люють у стан логічного нуля, а логічна схема 50 в порівнянню підлягають лише контрольні суми доразі, коли старий біт і новий біт не співпадають, вжиною 2 байти а не увесь блок даних Порівняння записує у відповідну комірку регістра 54 логічну цих коротких контрольних сум довжиною 2 байти одиницю Після ЦЬОГО побітно здійснюють обробку здійснюється набагато швидше, ніж порівняння наступного байта, доки не буде оброблений увесь усього блоку даних Контрольна сума очікуваних блок даних Процесор має доступ до вмісту регістданих може бути вирахувана наперед Як показано ра 54, тобто до результатів порівняння Шляхом на фіг 8, є також можливість подавати прийняті розкривання порівняльної інформації може бути дані одночасно до запам'ятовуючого пристрою швидко і просто оцінена прийнята ПОСЛІДОВНІСТЬ зворотного магазинного типу і на логічну схему бітів формування контрольної суми Остання формує Звичайно ж, ця схема порівняння може бути контрольні суми в реальному масштабі часу, завикористана також і в поєднанні зі схемою УАПП вдяки чому процесор мусить працювати в режимі згідно з рівнем техніки Таким чином операція авреального часу лише незначний відрізок часу, нетоматичного порівняння може бути реалізована обхідний для порівняння контрольних сум також без запам'ятовуючого пристрою 52 зворотного магазинного типу Таким чином, шляхом використання запам'ятовуючого пристрою зворотного магазинного типу, Принцип роботи запам'ятовуючого пристрою а також при необхідності компаратора чи генеразворотного магазинного типу представлений на тора контрольних сум, який автоматично формує фіг 6 Запам'ятовуючий пристрій 60 зворотного контрольну суму прийнятих даних, можна значною магазинного типу складається із ряду запам'ятомірою розвантажити процесор порівняно з традивуючих комірок, які циклічно адресують покажчиційною концепцією УАПП Завдяки цьому тактова ком зчитування і покажчиком запису Значення, що частота і, тим самим, споживаний струм можуть підлягає запису, записують в розряд, вказаний бути суттєво зменшені А зменшення споживаного покажчиком запису, при цьому покажчик запису струму для безконтактної картки означає зокрема отримує приріст на одиницю При зчитуванні здійзбільшення дальності дії снюють перевірку, чи не дорівнює покажчик запису покажчику зчитування Після цього здійснюють При цьому особливо доцільним є використанзчитування вмісту запам'ятовуючої комірки, на яку ня процесора, який під час передачі і прийому або вказує покажчик зчитування, при цьому покажчик коли він не задіяний, може бути переведений у зчитування отримує приріст на одиницю Коли порежим економії споживаного струму Тоді процекажчик запису і покажчик зчитування однакові, сор по закінченні підготовки до передачі/прийому тифікації) ВІДПОВІДНО ДО винаходу ця задача вирішена за допомогою запам'ятовуючого пристрою зворотного магазинного типу з вбудованим компаратором, як показано на фіг 5 Завдяки цьому може бути досягнуте подальше зниження вимог до продуктивності процесора і, ВІДПОВІДНО, ДО споживаного ним струму Існує також можливість використання дешевшого процесора Представлена на фіг 5 схема порівняння потребує наявності очікуваних даних, наприклад, поточного номера чи паролю, у запам'ятовуючому пристрої зворотного магазинного типу Проста логічна схема 50 автоматично порівнює кожен прийнятий біт (новий біт, 2) з вмістом запам'ятовуючої комірки 51 запам'ятовуючого пристрою 52 зворотного магазинного типу, в яку має бути записаний цей біт Таким чином, покажчик 53 запису служить як для адресування очікуваного біта (1), з яким має здійснюватися порівняння, так і для адресування місця запису прийнятого біта (2), який має бути записаний до запам'ятовуючого пристрою 52 зворотного магазинного типу (-> 3) При цьому нові біти отримують приймальнопередавальним вузлом радюштерфейсу PI (RFI = Radio Frequency Interface) 12 11 57155 може бути переведений у режим економії спожидальності дії ваного струму до закінчення передачі/прийому До того ж, операція передачі даних може бути даних Енергія, використана в іншому разі процефункцією часу, тобто ініціюватися в час, коли просором, може бути або зекономлена, або надана в цесор перебуває в режимі економії споживаного розпорядження схем передачі/прийому даних струму Так само може бути реалізована функція Крім того, під час передачі/прийому даних на сигавтоматичного прийому даних При цьому в час, нал, що передається безпровідним каналом, не коли процесор перебуває в режимі економії сподіють піки струму від процесора Зменшений споживаного струму, після передачі даних здійснюють живаний струм і більш сприятливий розподіл енеравтоматичне перемикання в режим прийому даних гії в чіп-картці, а також більш сприятливі умови без активізації процесора розповсюдження сигналу зумовлюють збільшення ФІГ. 1 10 "Рівень техніки" Приймач послідовний 12 ФІГ. 2 "Рівень техніки" 24 Процесор ФІГ. З послідовний 32 Пам'ять зворотного магазинного типу Процесор 14 57155 13 ФІГ. 4 Приймач 44 Процесор шина Пам'ять зворотного магазинного типу ФІГ. 5 Пам'ять зворотного магазинного тип) 5 3 т Пам'ять " ' зворотного магазинного типу 60 / 62 РІЗНИЦЯ покажчиків Покажчик зчитування запису І зчитування Покажчик зали 15 57155 16 ФІГ 7 Утворення CRC Очікувані 2 байтиСЙС Дані Утворення CRC Прийняті 2 байтиСИС Дані ФІГ. 8 Радіоінтерфейс Пам'ять зворотного магазинного типу CRC Комп'ютерна верстка А Крулевський Підписано до друку 05 07 2003 Тираж39 прим Міністерство освіти і науки України Державний департамент інтелектуальної власності, Львівська площа, 8, м Київ, МСП, 04655, Україна ТОВ "Міжнародний науковий комітет", вул Артема, 77, м Київ, 04050, Україна

ДивитисяДодаткова інформація

Назва патенту англійськоюInterface circuit for transferring data from and to a processor via a serial interface

Назва патенту російськоюИнтерфейсная схема для передачи входных и выходных данных прцессора через последовательный интерфейс

МПК / Мітки

МПК: G06F 1/32, G06F 13/38, H04L 13/08, G06F 13/40, G06K 19/07

Мітки: схема, послідовним, інтерфейсом, процесором, даних, спосіб, інтерфейсна, передачі

Код посилання

<a href="https://ua.patents.su/8-57155-interfejjsna-skhema-i-sposib-peredachi-danikh-mizh-poslidovnim-interfejjsom-i-procesorom.html" target="_blank" rel="follow" title="База патентів України">Інтерфейсна схема і спосіб передачі даних між послідовним інтерфейсом і процесором</a>

Попередній патент: Керована тактовим сигналом напівпровідникова інтегральна схема і спосіб (варіанти) приведення в дію керованої тактовим сигналом напівпровідникової інтегральної схеми

Наступний патент: Спосіб зміни проміжного ковша і дільниця для його здійснення

Випадковий патент: Спосіб одержання сухого препарату для обробки насіння з екстракту насіння, що проростає