Двовходовий багатозначний логічний елемент

Номер патенту: 20462

Опубліковано: 15.07.1997

Автори: Конопляненко Зеновій Дмитрович, Четвериков Григорій Григорович, Бондаренко Михайло Федорович

Формула / Реферат

Двовходовий багатозначний логічний елемент, що містить перший одновходовий багатозначний потенційний елемент, до складу якого входять компаратори, об'єднані входи яких є першим інформаційним входом пристрою, та ключі, який відрізняється тим, що в нього додатково введені другий та третій одновходов багатозначні потенційні елементи, входи яких відповідно є другим інформаційним та входом керування двовходового багатозначного логічного елемента, три дешифратори, кожний з яких містить дев'ять двовходових елементів І, матричний селектор, що містить десять груп по десять двовходових елементів І, а також комутатор, що містить тисячу двовходових елементів І, які складають прямокутну матрицю з десяти блоків комутації по сто двовходових елементів І у кожному, виходи першого — третього одновходових багатозначних потенційних елементів підключені до відповідних інформаційних входів першого—третього дешифраторів, при цьому в кожному дешифраторі перший вхід, що є першим входом першого елемента І, підключений до першого прямого виходу одновходового багатозначного потенційного елемента, перший інверсний вихід якого підключений до першого виходу дешифратора, другий вхід першого елемента І підключений до другого інверсного виходу одновходового багатозначного потенційного элемента, вихід першого елемента І підключений до другого виходу дешифратора, другий вхід дешифратора, що є першим входом другого елемента І, підключений до другого прямого виходу одновходового багатозначного потенційного элемента, друлій вхід другого елемента І підключений до третього інверсного виходу одновходового багатозначного потенційного елемента, вихід другого елемента І підключений до третього виходу дешифратора, третій вхід дешифратора, що є першим входом третього елемента І, підключений до третього прямого виходу одновходового багатозначного потенційного елемента, другий вхід третього елемента І підключений до четвертого інверсного виходу одновходового багатозначного потенційного елемента, вихід третього елемента І підключений до четвертого виходу дешифратора, четвертий вхід дешифратора, що є першим входом четвертого елемента І, підключений до четвертого прямого виходу одновходового багатозначного потенційного элемента, другий вхід четвертого елемента І підключений до п'ятого інверсного виходу одновходового багатозначного потенційного елемента, вихід четвертого елемента І підключений до п'ятого виходу дешифратора, п'ятий вхід дешифратора, що є пертим входом п'ятого елемента І, підключений до п'ятого прямого виходу одновходового багатозначного потенційного елемента, другий вхід п'ятого елемента І підключений до шостого інверсного виходу одновходового багатозначного потенційного елемента, вихід п'ятого елемента І підключений до шостого виходу дешифратора, шостий вхід дешифратора, що є першим входом шостого елемента І, підключений до шостого прямого виходу одновходового багатозначного потенційного елемента, другий вхід шостого елемента І підключений до сьомого інверсного виходу одновходового багатозначного потенційного елемента, вихід шостого елемента І підключений до сьомого виходу дешифратора, сьомий вхід дешифратора, що є першим входом сьомого елемента І, підключений до сьомого прямого виходу одновходового багатозначного потенційного елемента, другий вхід сьомого елемента І підключений до восьмого інверсного виходу одновходового багатозначного потенційного елемента, вихід сьомого елемента І підключений до восьмого виходу дешифратора, восьмий вхід дешифратора, що є першим входом восьмого елемента І, підключений до восьмого прямого виходу одновходового багатозначного потенційного елемента, другий вхід восьмого елемента І підключений до дев'ятого інверсного виходу одновходового багатозначного потенційного елемента, вихід восьмого елемента І підключений до дев'ятого виходу дешифратора, дев'ятий прямий вихід одновходового багатозначного потенційного елемента підключений до десятого виходу дешифратора, у матричному селекторі в кожній групі двовходових елементів І перші входи останніх підключені до його другої групи відповідних входів, які з'єднані з відповідними виходами другого дешифратора, а об'єднані другі входи двовходових елементів І підключені до першої групи входів матричного селектора, що з'єднаю з виходами першого дешифратора, виходи першої - десятої груп двовходових елементів І утворюють десять груп по десять виходів матричного селектора, що підключені до відповідних ста входів першої групи входів комутатора, причому перші входи елементів І стовпця матриці в кожному блоці комутації сполучені разом й утворюють другу групу входів комутатора та підключені до відповідних десяти виходів третього дешифратора, другі входи двовходових елементів І комутатора у кожному рядку прямокутної матриці блоків комутації сполучені разом й утворюють першу групу входів комутатора та підключені до відповідних виходів матричного селектора, виходи кожного стовпця елементів І, кожного з десяти блоків комутації, об'єднані разом і утворюють десять виходів комутатора, що підключені до відповідних десяти входів ключів, об'єднаний вихід яких є виходом елемента в цілому.

Текст

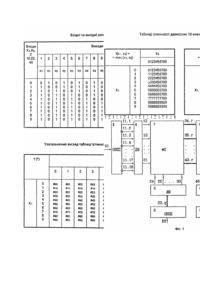

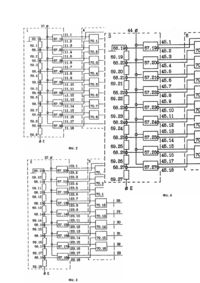

Винахід відноситься до автоматики, обчислювальної техніки та може використовуватись у системах керування, а також під час автоматичного оброблення мовної інформації, поданої у знаковому чи акустичному вигляді. З відомих пристроїв найближчим до цього винаходу є двовходовий багатозначний логічний елемент (А.с. СРСР №573879, кл. H03K19/02, 1977), що складається з одновходового багатозначного потенційного елемента, до складу якого входять компаратори, об'єднані входи яких є першим інформаційним входом пристрою та ключі. Виходи компараторів підключені до входів керування ключами, другі виходи яких підключені до джерела базисних сигналів багатозначного елемента, який складається з послідовно з'єднаних перетворювача напруги в фазу, вхід якого є другим інформаційним входом пристрою та перетворювача фази в напругу, виходи ключів з'єднані між собою і підключені до входу керування перетворювача фази в напругу. Двовходовий багатозначний логічний елемент характеризується деревоподібною архітектурою та складністю схемного вирішення, яка наростає через значне число зовнішніх входів і збільшення числа ключів до (де - значність структурного алфавіту, - число вхідних змінних елемента), неоднорідністю схемних рішень багатозначного потенційного елемента та перетворювачів напруги в фазу й фази в напругу як наслідок, низького технологічністю у процесі мікроелектронної реалізації, а також низькою швидкодією через послідовний характер роботи перетворювачів напруги в фазу й фази в напругу. В основу винаходу поставлено задачу створення такого двовходового багатозначного логічного елемента, у якому уведення нових блоків, нових зв'язків та виконання їх на однотипних елементах кон'юнкції дозволяє забезпечити однорідність виконання й веде до підвищення технологічності пристрою в процесі мікроелектронної реалізації, а також підвищує швидкодію через паралелізм структури і однотактний режим роботи всіх уведених блоків. Поставлена задача вирішується тим, що в двовходовий багатозначний логічний елемент, який містить перший одновходовий багатозначний потенційний елемент, до складу якого входять компаратори, об'єднані входи яких є першим інформаційним входом пристрою та ключі, згідно з винаходом, додатково уведені другий та третій одновходові багатозначні потенційні елементи, входи яких відповідно є другим інформаційним та входом керування двовходового багатозначного логічного елемента, три дешифратори, кожний з яких містить дев'ять двовходових елементів І, матричний селектор, що містить десять груп по десять двовходових елементів І, а також комутатор, що містить тисячу двовходових елементів І, які складають прямокутну матрицю з десяти блоків комутації по сто двовходових елементів І у кожному, виходи першого-третього одновходових багатозначних потенційних елементів підключені до відповідних інформаційних входів першого-третього дешифраторів, при цьому в кожному дешифраторі перший вхід, що є першим входом першого елемента І, підключений до першого прямого виходу одновходового багатозначного потенційного елемента, перший інверсний вихід якого транзитом підключений до першого виходу дешифратора, другий вхід першого елемента І підключений до другого інверсного виходу одновходового багатозначного потенційного елемента, вихід першого елемента І підключений до другого виходу дешифратора, другий вхід дешифратора, що є першим входом другого елемента І, підключений до другого прямого виходу одновходового багатозначного потенційного елемента, другий вхід другого елемента І підключений до третього інверсного виходу одновходового багатозначного потенційного елемента, вихід другого елемента І підключений до третього виходу дешифратора, третій вхід дешифратора, що є першим входом третього елемента І, підключений до третього прямого виходу одновходового багатозначного потенційного елемента, другий вхід третього елемента І підключений до четвертого Інверсного виходу одновходового багатозначного потенційного елемента, вихід третього елемента І підключений до четвертого виходу дешифратора, четвертий вхід дешифратора, що є першим входом четвертого елемента І, підключений до четвертого прямого виходу одновходового багатозначного потенційного елемента, другий вхід четвертого елемента І підключений до п'ятого інверсного виходу одновходового багатозначного потенційного елемента, вихід четвертого елемента І підключений до п'ятого виходу дешифратора, п'ятий вхід дешифратора, що є першим входом п'ятого елемента І, підключений до п'ятого прямого виходу одновходового багатозначного потенційного елемента, другий вхід п'ятого елемента І підключений до шостого інверсного виходу одновходового багатозначного потенційного елемента, вихід п'ятого елемента І підключений до шостого виходу дешифратора, шостий вхід дешифратора, що є першим входом шостого елемента І, підключений до шостого прямого виходу одновходового багатозначного потенційного елемента, другий вхід шостого елемента І підключений до сьомого інверсного виходу одновходового багатозначного потенційного елемента, вихід шостого елемента І підключений до сьомого виходу дешифратора, сьомий вхід дешифратора, що є першим входом сьомого елемента І, підключений до сьомого прямого виходу одновходового багатозначного потенційного елемента, другий вхід сьомого елемента І підключений до восьмого інверсного виходу одновходового багатозначного потенційного елемента, вихід сьомого елемента І підключений до восьмого виходу дешифратора, восьмий вхід дешифратора, що є першим входом восьмого елемента І, підключений до восьмого прямого виходу одновходового обагатозначного потенційного елемента, другий вхід восьмого елемента І підключений до дев'ятого інверсного виходу одновходового багатозначного потенційного елемента, вихід восьмого елемента І підключений до дев'ятого виходу дешифратора, дев'ятий прямий вихід одновходового багатозначного потенційного елемента транзитом підключений до десятого виходу дешифратора, у матричному селекторі в кожній групі двовходових елементів І перші входи останніх підключені до його другої групи відповідних входів, які з'єднані з відповідними виходами другого дешифратора, а об'єднані другі входи двовходових елементів І підключені до першої групи входів матричного селектора, що з'єднані з виходами першого дешифратора, виходи першої-десятої груп двовходових елементів І утворюють десять груп по десять виходів матричного селектора, що підключені до відповідних ста входів першої групи входів комутатора, причому перші входи елементів І стовпця матриці в кожному блоці комутації сполучені разом й утворюють другу групу входів комутатора та підключені до відповідних десяти виходів третього дешифратора, другі входи двовходових елементів І комутатора у кожному рядку, прямокутної матриці блоків комутації сполучені разом й утворюють першу групу входів комутатора та підключені до відповідних виходів матричного селектора, виходи кожного стовпця елементів і, кожного з десяти блоків комутації, об'єднані разом і утворюють десять виходів комутатора, що підключені до відповідних десяти входів ключів, об'єднаний вихід яких є виходом елемента в цілому. Уведення додатково в двовходовий багатозначний логічний елемент двох одновходових багатозначних потенційних елементів та трьох однотипних за принципом дії та побудовою дешифраторів, матричного селектора та комутатора, а також виконання дешифратора, селектора та комутатора на елементах кон'юнкції, що утворюють у просторі структуру паралельного типу з просторовим значним кодуванням, реалізованим у вигляді збуджених двійкових станів просторових полюсів, дозволило забезпечити однотипність й однорідність внутрішньої структури елемента, а також підвищити швидкодію за рахунок мінімальної затримки в усіх ланках елемента. У структурі та принципі дії двовходового багатозначного логічного елемента використовуються логічні, а не обчислювальні методи проміжних перетворень з застосуванням симбіозу дво- та значного кодування, що усуває необхідність врахування міжрозрядних зв'язків й набігання розрядної сітки і, як наслідок, веде до граничного паралелізму структури та зменшення затримок під час перетворень, спрощення структури проміжних субблоків. Відхід від деревоподібної організації структури багатозначних багатовходових елементів та усунення налагодження на виконання певного функціонального перетворення шляхом комутації базисних сигналів також веде до зменшення апаратурних затрат, оскільки число ключів на виході елемента при цьому не зростає до з збільшенням числа входів елемента, а залишається постійно та повністю усуває потребу в зовнішніх базисних входах. На фіг.1 зображена структурна схема двовходового багатозначного логічного елемента; на фіг.2 - 4 - функціональні схеми першого, другого та третього одновходового багатозначного потенційного елемента та дешифраторів відповідно; на фіг.5 - функціональна схема матричного селектора; на фіг.6 - функціональна схема комутатора; на фіг.7 - принципова електрична схема ключів. Двовходовий багатозначний логічний елемент (фіг.1), містить перший, другий та третій одновходові багатозначні потенційні елементи (ОБПЕ) 1, 2 та 3, а також перший, другий та третій дешифратори (ДШ) 4, 5 та 6, матричний селектор (МС) 7, комутатор (КМ) 8 і ключі (Кл) 9, причому вхід 10 першого ОБПЕ 1 є першим інформаційним входом пристрою, прямі та інверсні виходи першого ОБПЕ 1 підключені до відповідних інформаційних входів першого ДШ 4, десять виходів 12 ... 21 якого підключені до першої групи відповідних десяти входів МС 7, вхід 22 другого ОБПЕ 2 є другим інформаційним входом пристрою, прямі та інверсні виходи 23.q другого ОБПЕ 2 підключені до відповідних вісімнадцяти інформаційних входів другого ДНІ 5, десять виходів 24 ... 33 якого підключені до другої групи відповідних десяти входів МС 7, десять груп по десять виходів якого підключені до першої групи відповідних входів КМ 8, вхід третього ОБПЕ 3 є входом керування 44 пристрою, прямі та інверсні виходи третього ОБПЕ 3 підключені до відповідних інформаційних входів третього ДШ 6, десять виходів 46 ... 55 якого підключені до другої групи відповідних десяти входів КМ 8, десять виходів 56 ... 65 якого підключені до відповідних десяти входів Кл 9, об'єднані виходи яких є виходом 66 пристрою. Перший ОБПЕ 1 (див. фіг.2) містить вхід 10, що є одночасно першим інформаційним входом пристрою і об'єднаним інформаційним входом компараторів входи опорних сигналів компараторів 67.p, підключені до відповідних точок дільника напруги, що складається з дев'яти резисторів вісімнадцять прямих та інверсних а також виходів Перший дешифратор 4 (див. фіг.2) містить вісімнадцять інформаційних входів десять виходів 12 - 21 та включає до свого складу вісім двовходових елементів 70.1 - 70.8 І, причому перший вхід дешифратора 4, що є першим входом першого елемента 70.1 І, підключений до першого прямого виходу 11.1 першого одновходового багатозначного потенційного елемента 1, перший інверсний вихід 11.2 ОБПЕ 1 транзитом підключений до першого виходу 12 дешифратора 4, другий вхід першого елемента 70.1 І підключений до другого інверсного виходу 11.4 ОБПЕ 1, вихід першого елемента 70.1 І підключений до другого виходу 13 дешифратора 4; другий вхід дешифратора 4, що є першим входом другого елемента 70.2 І, підключений до другого прямого виходу 11.3 ОБПЕ 1, другий вхід другого елемента 70.2 І підключений до третього інверсного виходу 11.6 ОБПЕ 1, вихід другого елемента 70.2 І підключений до третього виходу 14 дешифратора 4; третій вхід 11.5 дешифратора 4, що є першим входом третього елемента 70.3 І, підключений до третього прямого виходу 11.5 ОБПЕ 1, другий вхід третього елемента 70.3 І підключений до четвертого інверсного виходу 11.8 ОБПЕ 1, вихід третього елемента 70.3 І підключений до четвертого виходу 15 дешифратора 4; четвертий вхід дешифратора 4, що є першим входом четвертого елемента 70.4 І, підключений до четвертого прямого виходу 11.7 ОБПЕ 1, другий вхід четвертого елемента 70.4 І підключений до п'ятого інверсного виходу 11.10 ОБПЕ 1, вихід четвертого елемента 70.4 І підключений до п'ятого виходу 16 дешифратора 4; п'ятий вхід дешифратора 4, що є першим входом п'ятого елемента 70.5 І, підключений до п'ятого прямого виходу 11.9 ОБПЕ 1, другий вхід п'ятого елемента 70.5 І підключений до шостого інверсного виходу 11.12 ОБПЕ 1. вихід п'ятого елемента 70.5 І підключений до шостого виходу 17 дешифратора 4; шостий вхід дешифратора 4, що є першим входом шостого елемента 70.6 І, підключений до шостого прямого виходу 11.11 ОБПЕ 1, другий вхід шостого елемента 70.6 І підключений до сьомого інверсного виходу 11.14 ОБПЕ 1, вихід шостого елемента 70.6 І підключений до сьомого виходу 18 дешифратора 4; сьомий вхід дешифратора 4, що є першим входом сьомого елемента 70.7 І, підключений до сьомого прямого виходу 11.13 ОБПЕ 1, другий вхід сьомого елемента 70.7 І підключений до восьмого інверсного виходу 11.16 ОБПЕ 1, вихід сьомого елемента 70.7 І підключений до восьмого виходу 19 дешифратора 4; восьмий вхід дешифратора 4, що є першим входом восьмого елемента 70.8 І, підключений до восьмого прямого виходу 11.15 ОБПЕ 1, другий вхід восьмого елемента 70.8 І підключений до дев'ятого інверсного виходу 11.18 ОБПЕ 1, вихід восьмого елемента 70.8 І підключений до дев'ятого виходу 20 дешифратора 4; дев'ятий прямий вихід 11.17 ОБПЕ 1 транзитом підключений до десятого виходу 21 дешифратора 4. Другий ОБПЕ 2 (див. фіг.3) містить вхід 22, що є одночасно другим інформаційним входом пристрою і об'єднаним інформаційним входом компараторів входи опорних сигналів компараторів підключені до відповідних точок дільника напруги, що складається з дев'яти резисторів а також вісімнадцять прямих та інверсних виходів Другий дешифратор 5 (див. фіг.3) містить вісімнадцять інформаційних входів десять виходів 24 - 33 та включає до свого складу вісім двовходових елементів 70.9 - 70.16 І, причому перший вхід дешифратора 5, що є першим входом першого елемента 70.9 І, підключений до першого прямого виходу 23.1 другого одновходового багатозначного потенційного елемента 2, перший інверсний вихід 23.2 ОБПЕ 2 транзитом підключений до першого виходу 24 дешифратора 5, другий вхід першого елемента 70.9 І підключений до другого інверсного виходу 23.4 ОБПЕ 2, вихід першого елемента 70.9 1 підключений до другого виходу 25 дешифратора 5; другий вхід дешифратора 5, що є першим входом другого елемента 70.10 І, підключений до другого прямого виходу 23.3 ОБПЕ 2, другий вхід елемента 70.10 І підключений до третього інверсного виходу 23.6 ОБПЕ 2, вихід другого елемента 70.10 І підключений до третього виходу 26 дешифратора 5; третій вхід 23.5 дешифратора 5, що є першим входом третього елемента 70.11 І, підключений до третього прямого виходу 23.5 ОБПЕ 2, другий вхід третього елемента 70.11 І підключений до четвертого інверсного виходу 23.8 ОБПЕ 2, вихід третього елемента 70.11 І підключений до четвертого виходу 27 дешифратора 5; четвертий вхід дешифратора 5, що є першим входом четвертого елемента 70.12 І, підключений до четвертого прямого виходу 23.7 ОБПЕ 2, другий вхід, четвертого елемента 70.12 І підключений до п'ятого інверсного виходу 23.10 ОБПЕ 2, вихід четвертого елемента 70.12 1 підключений до п'ятого виходу 28 дешифратора 5; п'ятий вхід дешифратора 5, що є першим входом п'ятого елемента 70.13 І, підключений до п'ятого прямого виходу 23.9 ОБПЕ 2, другий вхід п'ятого елемента 70.13 І підключений до шостого інверсного виходу 23.12 ОБПЕ 2, вихід п'ятого елемента 70.13 І підключений до шостого виходу 29 дешифратора 5; шостий вхід дешифратора 5, що є першим входом шостого елемента 70.14 І, підключений до шостого прямого виходу 23.11 ОБПЕ 2, другий вхід шостого елемента 70.14 І підключений до сьомого інверсного виходу 23.14 ОБПЕ 2, вихід шостого елемента 70.14 і підключений до сьомого виходу 30 дешифратора 5; сьомий вхід дешифратора 5, що є першим входом сьомого елемента 70.15 І, підключений до сьомого прямого виходу 23.13 ОБПЕ 2, другий вхід сьомого елемента 70.15 І підключений до восьмого інверсного виходу 23.16 ОБПЕ 2, вихід сьомого елемента 70.15 І підключений до восьмого виходу 31 дешифратора 5; восьмий вхід дешифратора 5, що є першим входом восьмого елемента 70.16 І, підключений до восьмого прямого виходу 23.15 ОБПЕ 2, другий вхід восьмого елемента 70.16 І підключений до дев'ятого інверсного виходу 23.18 ОБПЕ 2, вихід восьмого елемента 70.16 І підключений до дев'ятого виходу 32 дешифратора 5; дев'ятий прямий вихід 23.17 ОБПЕ 2 транзитом підключений до десятого виходу 33 дешифратора 5. Третій ОБПЕ 3 (див. фіг.4) містить вхід 44, що є одночасно входом керування пристрою і об'єднаним інформаційним входом компараторів входи 68.n опорних сигналів компараторів підключені до відповідних точок дільника напруги, що складається з дев'яти резисторів 69.n, а також вісімнадцять прямих та інверсних виходів Третій дешифратор 6 (див. фіг.4) містить вісімнадцять інформаційних входів десять виходів 46 - 55 та включає до свого складу вісім двовходових елементів 70.17 - 70.24 І, причому перший вхід дешифратора 6, що є першим входом першого елемента 70.17 І, підключений до першого прямого виходу 45.1 третього одновходового багатозначного потенційного елемента 3, перший інверсний вихід 45.2 ОБПЕ 3 транзитом підключений до першого виходу 16 дешифратора 6, другий вхід першого елемента 70.17 І підключений до другого інверсного виходу 45.4 ОБПЕ 3, вихід першого елемента 70.17 І підключений до другого виходу 47 дешифратора 6; другий вхід дешифратора 6, що є першим входом другого елемента 70.18 І, підключений до другого прямого виходу 45.3 ОБПЕ 3, другий вхід другого елемента 70.18 І підключений до третього інверсного виходу 45.6 ОБПЕ 3, вихід другого елемента 70.18 І підключений до третього виходу 48 дешифратора 6; третій вхід дешифратора 6, що є першим входом третього елемента 70.19 І, підключений до третього прямого виходу 45.5 ОБПЕ 3, другий вхід третього елемента 70.19 І підключений до четвертого інверсного виходу 45.8 ОБПЕ 3, вихід третього, елемента 70.19 і підключений до четвертого виходу 27 дешифратора 6; четвертий вхід дешифратора 6, що є першим входом четвертого елемента 70.20 І, підключений до четвертого прямого виходу 45.7 ОБПЕ 3, другий вхід четвертого елемента 70.20 І підключений до п'ятого інверсного виходу 45.10 ОБПЕ 3, вихід четвертого елемента 70.20 І підключений до п'ятого виходу 50 дешифратора 6; п'ятий вхід дешифратора 6, що є першим входом п'ятого елемента 70.21 І, підключений до п'ятого прямого виходу 45.9 ОБПЕ 3, другий вхід п'ятого елемента 70.21 І підключений до шостого інверсного виходу 45.12 ОБПЕ 3, вихід п'ятого елемента 70.21 І підключений до шостого виходу 51 дешифратора 6; шостий вхід дешифратора 6, що є першим входом шостого елемента 70.22 І, підключений до шостого прямого виходу 45.11 ОБПЕ 3, другий вхід шостого елемента 70.22 І підключений до сьомого інверсного виходу 45.14 ОБПЕ 3, вихід шостого елемента 70.22 І підключений до сьомого виходу 52 дешифратора 6; сьомий вхід дешифратора 6, що є першим входом сьомого елемента 70.23 І, підключений до сьомого прямого виходу 45.13 ОБПЕ 3, другий вхід сьомого елемента 70.23 І підключений до восьмого інверсного виходу 45.16 ОБПЕ З, вихід сьомого елемента 70.23 І підключений до восьмого виходу 53 дешифратора 6; восьмий вхід дешифратора 6, що є першим входом восьмого елемента 70.24 І, підключений до восьмого прямого виходу 45.15 ОБПЕ 3, другий вхід восьмого елемента 70.24 І підключений до дев'ятого інверсного виходу 45.18 ОБПЕ 3, вихід восьмого елемента 70.24 І підключений до дев'ятого виходу 54 дешифратора 6; дев'ятий прямий вихід 45.17 ОБПЕ 3 транзитом підключений до десятого виходу 55 дешифратора 6. Матричний селектор 7 (фіг.5) містить десять груп 7.1 - 7.10 по десять двовходових елементів 70.25 - 70.124 І, першу та другу групу входів 12 ... 21, 24 ... 33 відповідно, а також десять груп десять виходів, причому в кожній групі 7.1 - 7.10 перші входи двовходових елементів 70.25 - 70.34, ..., 70.115 - 70.124 І підключені до відповідних десяти входів 24 ... 33 другої групи входів МС 7, а другі входи кожного з десяти елементів 70.25 ... 70.34, 70.35 ... 70.44 - 70.115 ... 70.124 І першої, другої, ..., десятої груп об'єднані разом та підключені до відповідних десяти входів 12 ... 21 першої групи входів МС 7, виходи першої, другої, ..., десятої груп двовходових елементів 70.25 - 70.124 І утворюють десять груп по десять виходів що підключені до відповідних ста входів КМ 8. Комутатор 8 (фіг.6) містить тисячу двовходових елементів 70.125 - 70.1124 І, що утворюють прямокутну матрицю з десяти блоків 8.1 - 8.10 комутації по сто двовходових елементів І у кожному, причому перші входи елементів стовпця матриці в кожному блоці комутації сполучені разом й підключені до відповідних виходів 46 - 55 третього дешифратора 6, другі входи двовходових елементів 70.125 - 70.1124 І комутатора 8 у кожному рядку, з першого по сотий, прямокутної матриці блоків 8.1 - 8.10 комутації сполучені разом та підключені до відповідних виходів матричного селектора 7, виходи кожного стовпця елементів у кожному з блоків 8.1 - 8,10 комутації об'єднані разом і утворюють відповідно десять виходів 56 - 65 комутатора 8. Ключі 9 (Кл) (див. фіг.7) містять десять схем керування 71.1 - 71.10, лінійку 72 транзисторних біполярних ключів, десятиланковий транзисторний дільник 73 напруги, причому входи схем 71.1 71.10 керування підключені до виходів 56 - 65 комутатора 8, а об'єднаний вихід ключів 9 є виходом 66 пристрою. У початковому стані на входи 10, 22, 44 всіх ОБПЕ 1 - 3, що входять до складу пристрою (див. фіг.1) надходять нульові початкові сигнали значного коду, тобто логічні сигнали на входах 10, 22 та сигнал на вході 44 керування є значні (10-значні) сигнали При цьому, під впливом логічного "0" на дев'яти прямих виходах компараторів 67.p, m, n (див. фіг.2 - 4 та табл.1) сформовані двозначні логічні сигнали виду а на дев'яти інверсних Теорія та практика штучного інтелекту (Шабанов-Кушнаренко Ю.П. Теория интеллекта. Математические средства. - Xарьков: Выща шк. (Изд-во при Харьк. ун-те), 1984. - 144с.) використовує поняття елемента розпізнавання, який під час подачі на його вхід букви виробляє на виході сигнал "1". Підчас подачі будь-якої іншої букви елемент розпізнавання виробляє сигнал "0", що свідчить про незбіжність букви, яка надійшла з потрібною буквою Таким чином здійснюється присвоювання кожному провіднику (кожному виходу), через який надходить двозначний сигнал ("0" чи "1"), певне розпізнавання де - деяке значення значного алфавіту, - буквенна змінна. Двозначні сигнали, що проходять таким провідником (виходом), інтерпретуються тепер як значення розпізнавання значних змінних. Отже необхідно реалізувати елемент розпізнавання з одним входом 10, 22 чи 44 і виходами 12 - 21, 24 - 33 чи 46 - 55 для розпізнавання значних (багаторівневих) сигналів одновходовим багатозначним потенційним елементом 1 - 3 паралельного типу (лінійка компараторів з єдиним опорним дільником напруги). Для цього необхідно розв'язати задачу однозначного розпізнавання вхідного значного сигналу, коли його амплітуда перетинає опорні рівні напруги з меншими значеннями амплітуд. Це досягається шляхом уведення в структуру пристрою, на кожному прямому виході компаратора останнього, додатково елементів входу елемента прямий вихід компаратора сигнал з інверсного восьми крім двовходових причому до одного підключено виходу а на інший наступного компаратора (див. фіг.2 - 4). Елементи разом з зв'язками утворюють перший-третій дешифратори 4 - 6. Логіку роботи дешифраторів 4 - 6 описує наступна система рівнянь змінних, причому кожне з значень Отже, де - сигнали прямих виходів 11.q, 23.q, 45.q ОБПЕ 1 - 3; - сигнали інверсних виходів ОБПЕ 1 - 3; кон'юнкції, значних змінних, - операція - сигнали розпізнавання що приймають значення з функції а самі значення можуть повторюватися. для кожної пари сигналів (табл.2), що присутня на входах 10, 22 пристрою необхідно сформувати один єдиний керуючий сигнал на одному з просторових входів 56 - 65 ключів 9, що й здійснюється селектором 7 та комутатором 8 під впливом сигналу керування з входу 44. Таким чином, для просторового варіанту дії елемента при необхідно сформувати просторову матрицю сигналів логічної "1" для ста виходів матричного селектора 7. Логіку роботи матричного селектора 7 описує наступна система рівнянь: множини Використовуючи у кожному з одновходових багатозначних потенційних елементів 1 - 3 дев'ять компараторів 67.1 - 67.9 можна розпізнати десять рівнів 10-значного сигналу (з "0" до "9"). Кожний раз, під час спрацювання наступного компаратора, на його інверсному виході виникне сигнал логічного "0", який надійде на другий вхід елемента а оскільки на перший вхід елемента подано сигнал "1", у результаті відбудеться логічне відключення прямого виходу попереднього компаратора що призначений для розпізнавання меншого значення значного сигналу. Для розпізнавання нульового сигналу, при цьому, не потрібний окремий компаратор, оскільки інверсний сигнал з виходу 11.2 першого компаратора повністю відповідає сигналу, який повинен формувати елемент розпізнавання "0". Таким чином, елементи розпізнавання, утворені одновходовими багатозначними потенційними елементами 1 - 3 просторового типу та дешифраторами 4 - 6, перетворюють слова складені з букв значного алфавіту у двозначне їх відображення станів просторових полюсів виходів 12 - 21, 24 - 33, 46 - 55. З метою економії апаратних затрат, у двовходовому багатозначному логічному елементі (БЛЕ) для розпізнавання десяти рівнів значного сигналу в ОБПЕ 1 - 3 використано тільки дев'ять компараторів а у дешифраторах 4 - 6 (див. фіг.2 - 4), при нульових сигналах на входах 10, 22, 44 пристрою, використано транзитом інверсний вихід перших компараторів 67.1, 67.2, 67.19. Тому на відповідних паралельних десяти виходах 12 - 21, 24 - 33, 46 - 55 отримуємо логічні сигнали виду тобто на виходах 12, 24, 46 маємо логічну "1", а на решті - "0". Після розпізнавання значних сигналів на виходах дешифраторів 4, 5 отримано значень просторових (паралельних) одиничних кодів (див. табл.1). Для формування же вихідних сигналів пристрою в цілому, у кожному такті перетворення, необхідно й достатньо кожній парі просторових вихідних сигналів елементів розпізнавання співвіднести тепер один з сигналів вихідної значної функції двох де - вихідні сигнали матричного селектора 7, що приймають значення з множини У початковому стані в матричному селекторі 7 сигнали з виходів 12, 24 дешифраторів 4, 5 надійдуть на елемент 70.25 І (див. фіг.5) і на виході 34.1 МС 7 маємо логічну "1", а на решті 99 - и виходах - логічні "0". Переходячи до опису роботи комутатора 8 відзначимо, що тут розглянуто варіант реалізації двовходового БЛЕ (див. фіг.1) для значності Оскільки БЛЕ є універсальним, то потужність множини функцій, що реалізуються двовходовим 10-значним універсальним елементом, дорівнює Через універсальність двовходового багатозначного логічного елемента, сто варіантів пар можливих комбінацій сигналів елементів розпізнавання на виходах 12 - 21, 24 - 33 дешифраторів 4, 5, необхідно перетворити в один з k керуючих сигналів для ключів 9. Для здійснення вказаних перетворень та просторового розподілу до складу двовходового БЛЕ уведено комутатор 8 у вигляді прямокутної матриці, що містить десять блоків комутації сигналів логічної "1" з виходів матричного селектора 7 до входів 56 - 65 ключів 9. Матричний селектор 7 здійснює вертикальне переміщення логічної "1" у прямокутній матриці елементів 70.125 - 70.1124 І комутатора 8 і включає один із ста елементів у блоках комутації кожний з яких спрямовує логічну "1" в одному з можливих напрямів для включення єдиного з лінійки транзисторних біполярних ключів 72. Ключові транзистори постійно підключені до відповідних опорних сигналів дільника 73 напруги. Згідно з зміною значень 10-значних змінних на входах 10, 22 та з урахуванням таблиці істинності (див. табл.2), на вихід 66 логічного елемента, надходять значення функції, вибрані комутатором 8 під впливом сигналів матричного селектора 7 та ДШ 6. Формально робота комутатора 8 може бути описана наступною системою рівнянь де вихідні сигнали матричного селектора 7, а - дешифратора 6, операція диз'юнкції (АБО). Керування процесом вибору та формування значень двомісної функції здійснюється третім дешифратором 6 під впливом сигналів з входу 44 керування. Оскільки необхідно у кожному такті перетворень сформувати тільки один з керуючих просторових сигналів на одному з входів 56 - 65 ключів 9, на вхід 44 керування у кожному такті надходить одне з значень згідно з табл.2. Виходи кожних ста елементів у кожному з блоків комутації об'єднані разом 1 утворюють десять виходів 56 - 65 комутатора 8. Використання у цьому випадку провідного АБО правомірне, оскільки в кожний такт роботи двовходового багатозначного логічного елемента активним є тільки один із виходів елементів блоків комутації. Відповідно, у початковому стані коли сигнал логічної "1" з виходу 46 ДШ 6 надійде на двовходовий елемент 70.125 І (див. фіг.6) комутатора 8, куди надійшла логічна "1" з виходу 34.1 від МС 7, на виході 56 КМ 8 маємо логічну "1"', яка надходить на відповідний логічному "0" вхід 56 (див. фіг.7) і на вихід 66 двовходового БЛЕ надходить логічний "0" значного сигналу. Надходження у подальшому на входи 10, 22 сигналів логічної "1" на виходах 12 - 21, 24 - 33 дає а логічної "2" логічної "9" тобто на відповідні входи першого та другого дешифраторів 4, 5 надходять (див. табл.1) парафазні сигнали від компараторів 67.1 - 67.9, 67.10 - 67.18 (див. фіг.2, 3) одновходових багатозначних потенційних елементів 1, 2. Сигнал розпізнавання "1" від компаратора 67.1 ОБПЕ 1 чи 67.10 ОБПЕ 2 проходить через елемент 70.1 І ДШ 4 чи 70.9 І ДШ 5 лише у тому випадку, коли не включений компаратор 67.2 ОБПЕ 1 чи 67.11 ОБПЕ 2, що розпізнає логічну "2". Відбувається розпізнавання логічної "1", тобто на входи 10, 22 ОБПЕ 1, 2 надійшли 10-значні сигнали з рівнем, що дорівнює "1". Відповідно, коли на вхід 10 ОБПЕ 1 надходить логічна "2" здійснюється відключення прямого виходу 11.1 попереднього компаратора 67.1 і на окремий прямий вихід 11.3 другого компаратора 67.2 надходить логічна "1", що сигналізує про те, що відбулося розпізнавання логічної "2". Аналогічно виглядає робота всіх наступних компараторів 67.1 під час перевищення рівня вхідного сигналу над опорним рівнем відповідного компаратора, крім останнього, де на виході немає елемента І. Справа у тому, що наступного вищого рівня вхідного сигналу немає, а всі решта значень є меншими, отже відпадає необхідність відключення даного виходу дією наступного каскаду. Логічні функції (1) - (3) виконують дешифратори 4 - 6, матричний селектор 7 та комутатор 8, а логіка їх роботи визначається таблицями істинності (див. табл.3). Для наглядності наведемо ряд таблиць істинності функцій 10-значної логіки двох змінних. Уведення в двовходовий багатозначний логічний елемент матричного селектора 7, комутатора 8 та дешифраторів 4 - 6, які утворюють у просторі структуру паралельного типу з просторовим значним кодуванням, здійсненим за рахунок збуджених у вигляді двійкових станів просторових полюсів, а також використання методів теорії інтелекту для описання алгоритмів роботи і структури побудови, коли значні числа і перетворення над ними описуються з допомогою алгебри скінченних предикатів вперше дозволило отримати найпростіші аналітичні записи (1) - (3) описання необхідних співвідношень вхідних і вихідних змінних та дії його основних компонентів, що збігаються з формулами алгебри логіки, але зберігають властивості значного алфавіту, паралелізм та однорідність структури. Застосування логічних методів керування з симбіозом значного розпізнавання і формування сигналів та двозначних методів побудови проміжних просторових операційних засобів (ДШ, МС та КМ) дозволило реалізувати структуру двовходового багатозначного логічного елемента значно простіше, ніж при використанні традиційних розв'язків, які отримуються з використанням деревоподібної архітектури та керування комутацією джерел базисних сигналів, забезпечити однотипність і однорідність внутрішньої структури, суттєво зменшити апаратурні затрати на створення елемента, а також підвищити швидкодію за рахунок мінімальної затримки в усіх ланках.

ДивитисяДодаткова інформація

Автори англійськоюBondarenko Mykhailo Fedorovych, Konoplianenko Zenovii Dmytrovych, Chetverykov Hryhorii Hryhorovych

Автори російськоюБондаренко Михаил Федорович, Конопляненко Зеновий Дмитрович, Четвериков Григорий Григорович

МПК / Мітки

МПК: H03K 19/02

Мітки: багатозначний, двовходовий, елемент, логічний

Код посилання

<a href="https://ua.patents.su/9-20462-dvovkhodovijj-bagatoznachnijj-logichnijj-element.html" target="_blank" rel="follow" title="База патентів України">Двовходовий багатозначний логічний елемент</a>

Попередній патент: Спосіб реконструкції малоповерхової будівлі

Наступний патент: Генератор трифазних синусоїдальних сигналів

Випадковий патент: Насосна станція