Мікропроцесорна система

Номер патенту: 104340

Опубліковано: 27.01.2014

Автори: Макаренко Олександр Якович, Лозовий Олексій Григорович, Донцов Ігор Анатолійович

Формула / Реферат

1. Мікропроцесорна система, кожен канал якої містить мікропроцесор, два буферні регістри, буфер даних, блок постійної пам'яті, блок оперативної пам'яті, порт введення, порт виводу, при цьому перший вхід першого буферного регістра через резистор сполучений з клемою позитивного потенціалу джерела живлення, перша восьмирозрядна адресна шина мікропроцесора сполучена з відповідними входами першого буферного регістра, перший вхід другого буферного регістра сполучений з першим виходом мікропроцесора, друга восьмирозрядна адресна шина мікропроцесора сполучена з відповідними входами другого буферного регістра і буфера даних, другий вихід мікропроцесора сполучений з першим входом буфера даних, виходи першого і другого буферних регістрів утворюють адресну шину мікропроцесора і сполучені з відповідними адресними входами блока оперативної пам'яті, виходи другого буферного регістра сполучені з відповідними адресними входами порту введення і порту виводу, виходи буфера даних утворюють двонаправлену шину даних мікропроцесора і сполучені з відповідними входами блока оперативної пам'яті, порту введення і порту виводу, виходи шин керування мікропроцесора сполучені з відповідними входами блока оперативної пам'яті, порту введення і порту виводу, яка відрізняється тим, що в кожен канал додатково введені блок регенерації інформації, при цьому перші, другі і треті входи блока регенерації інформації сполучені з шиною керування, шиною даних і з адресною шиною мікропроцесора відповідно, четверті двонаправлені входи/виходи блока регенерації інформації сполучені з двонаправленою шиною даних блока постійної пам'яті, перші виходи адресної шини блока регенерації інформації сполучені з відповідними входами блока постійної пам'яті, другі виходи шини керування сполучені з відповідними входами блока постійної пам'яті в кожному каналі, треті інформаційні виходи блока регенерації інформації першого каналу сполучені з п'ятими інформаційними входами блоків регенерації інформації в другому і третьому каналах відповідно, треті інформаційні виходи блока регенерації інформації другого каналу сполучені з п'ятими і шостими інформаційними входами блоків регенерації інформації в першому і третьому каналах відповідно, треті інформаційні виходи блока регенерації інформації третього каналу сполучені з шостими і п'ятими інформаційними входами блоків регенерації інформації в другому і першому каналах відповідно.

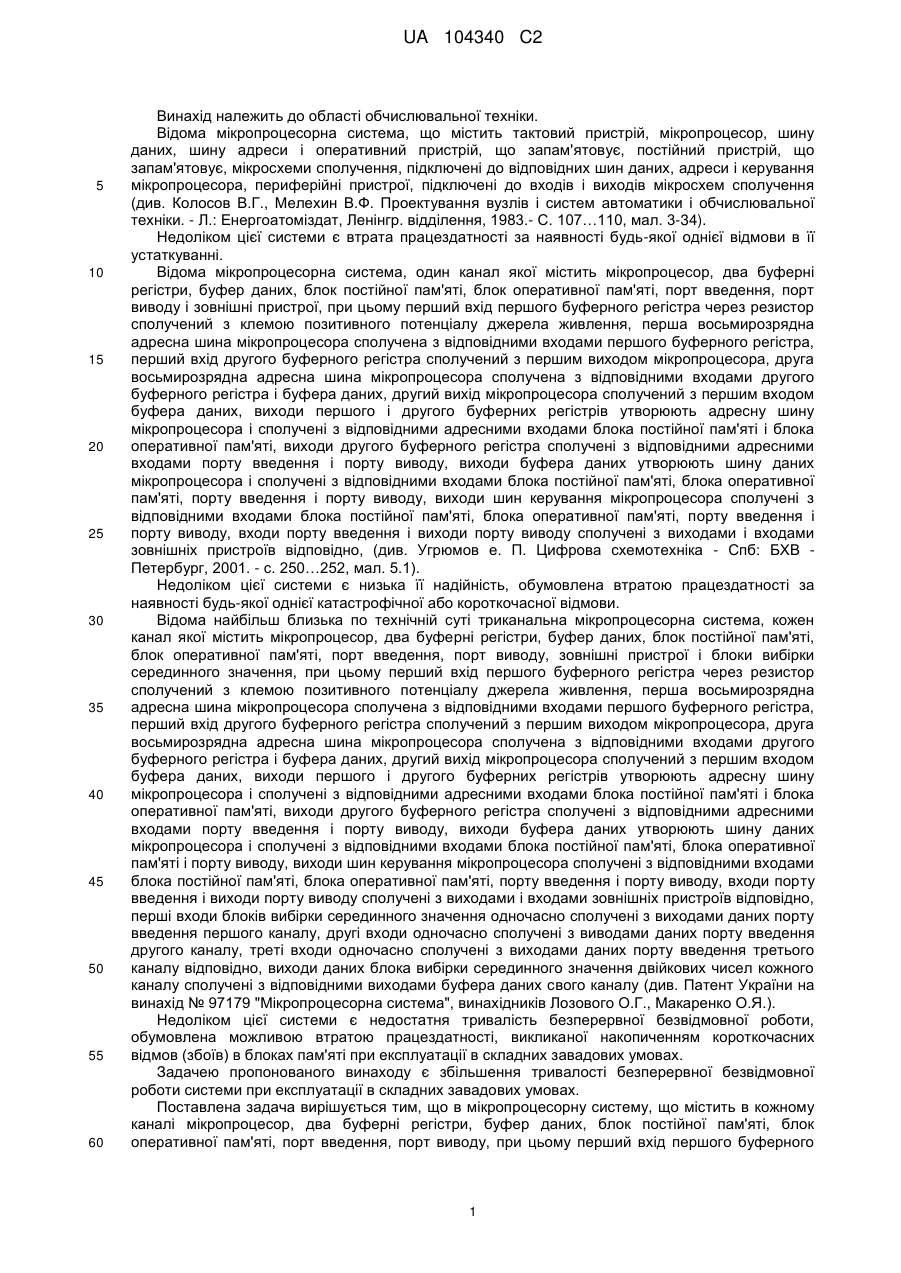

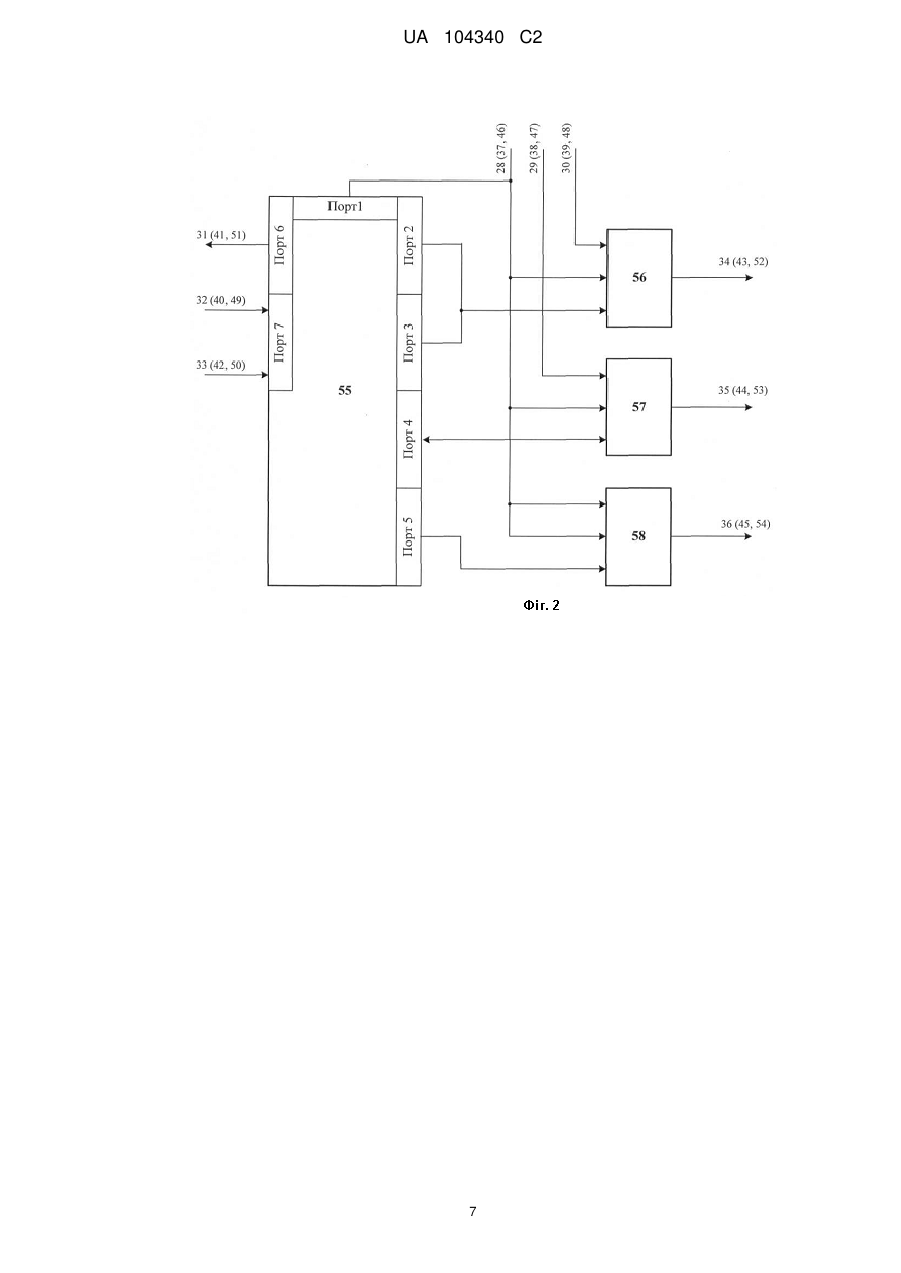

2. Система за п. 1, яка відрізняється тим, що кожен блок регенерації інформації містить перший мультиплексор шини адреси, другий мультиплексор шини даних, третій мультиплексор шини керування мікропроцесора і один мікроконтролер, при цьому перші входи мультиплексорів сполучені з шиною адреси, шиною даних і шиною керування мікропроцесора відповідно, другі входи мультиплексорів сполучені з шиною керування мікроконтролера і розрядами першого порту мікроконтролера, треті входи першого мультиплексора сполучені з розрядами другого і третього портів мікроконтролера, створюючими шину адреси блока постійної пам'яті, треті входи другого мультиплексора сполучені з розрядами четвертого порту мікроконтролера, створюючими шину даних блока постійної пам'яті, треті входи третього мультиплексора сполучені з розрядами п'ятого порту мікроконтролера, створюючими шину керування блока постійної пам'яті, виходи першого мультиплексора сполучені з адресними входами блока постійної пам'яті, виходи другого мультиплексора сполучені з двонаправленими входами/виходами блока постійної пам'яті, виходи третього мультиплексора сполучені з входами керування блока постійної пам'яті, інформаційні виходи даних шостого порту мікроконтролера свого каналу сполучені з відповідними портами входу даних лівого і правого каналів, інформаційні входи даних сьомого порту мікроконтролера сполучені з відповідними портами виходу даних лівого і правого каналів.

Текст

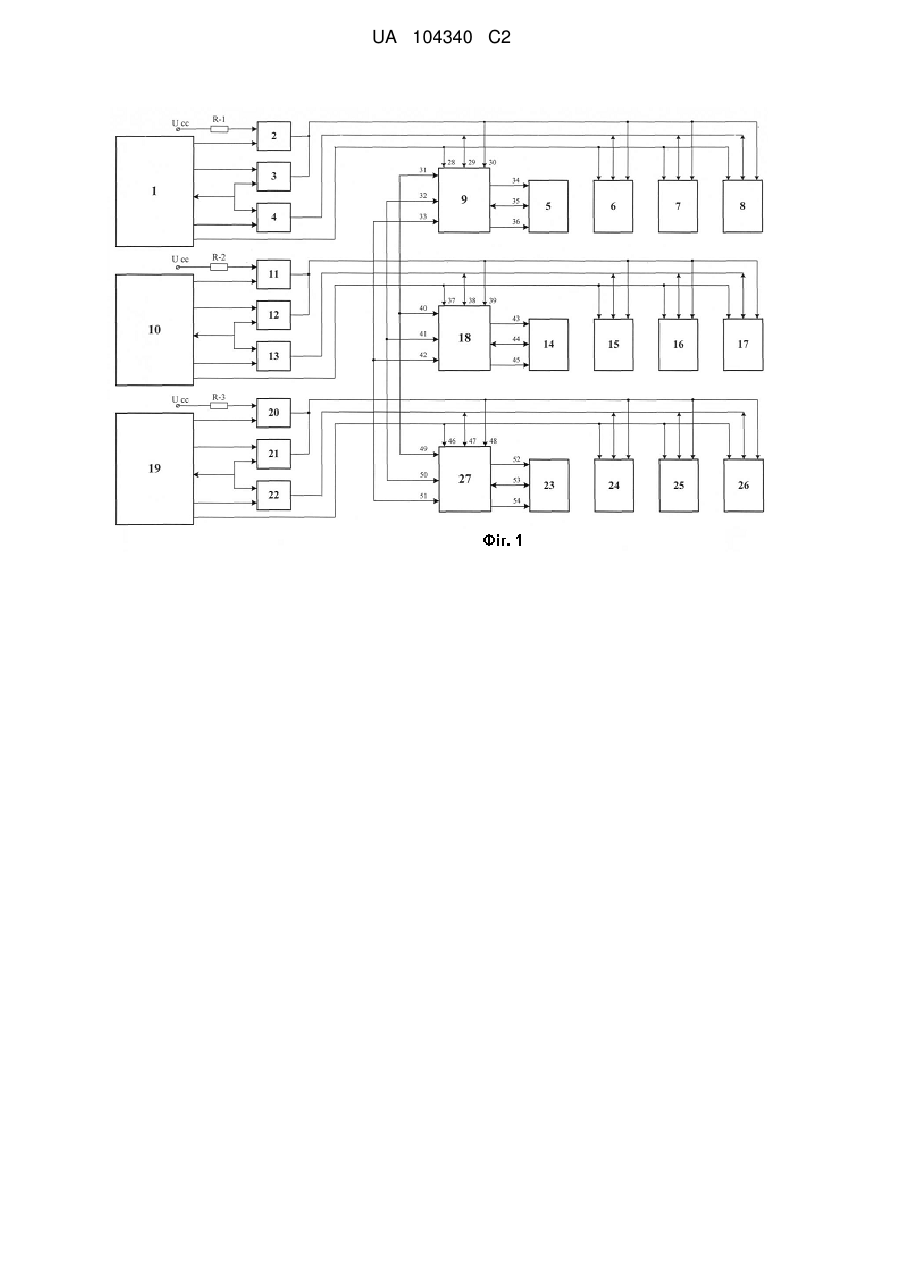

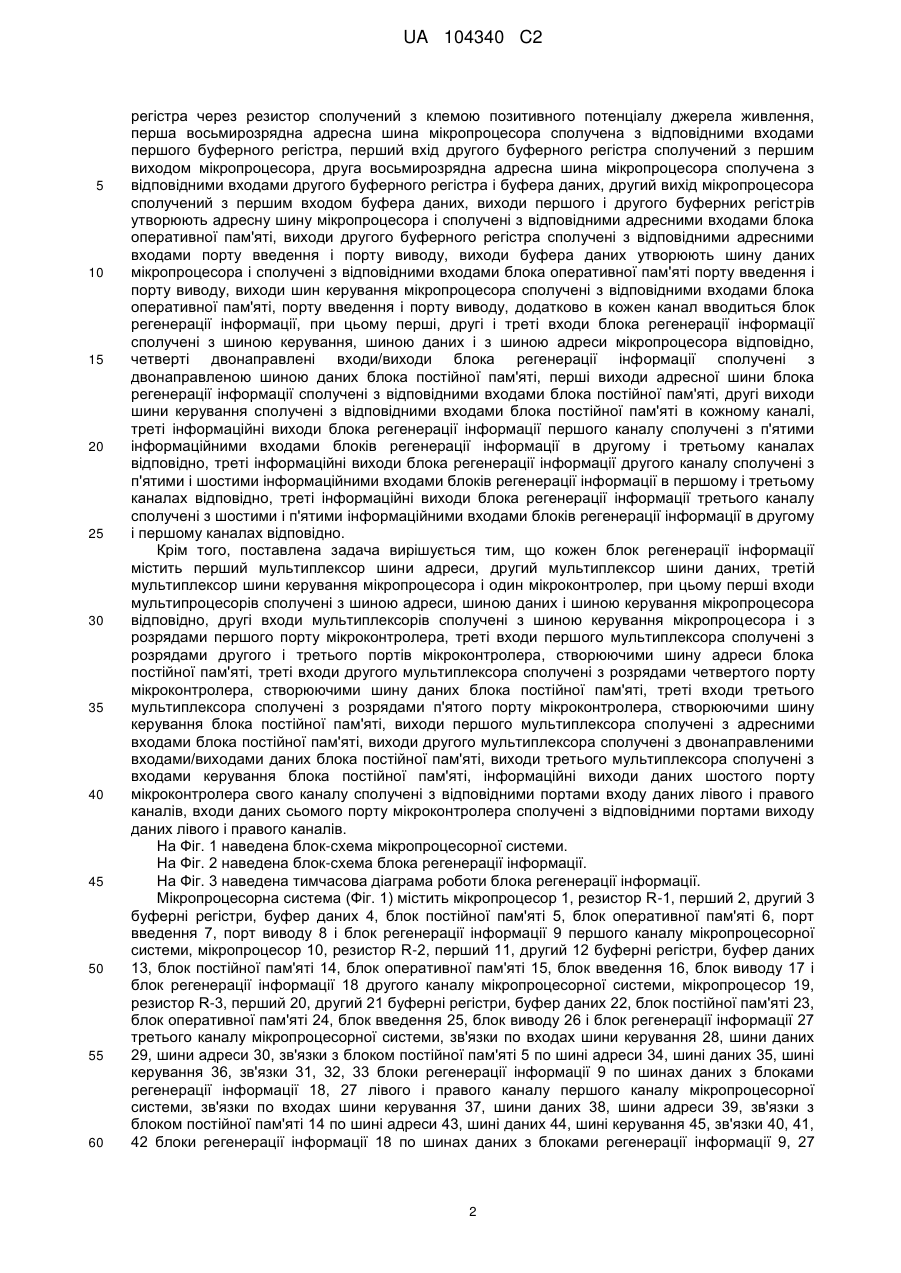

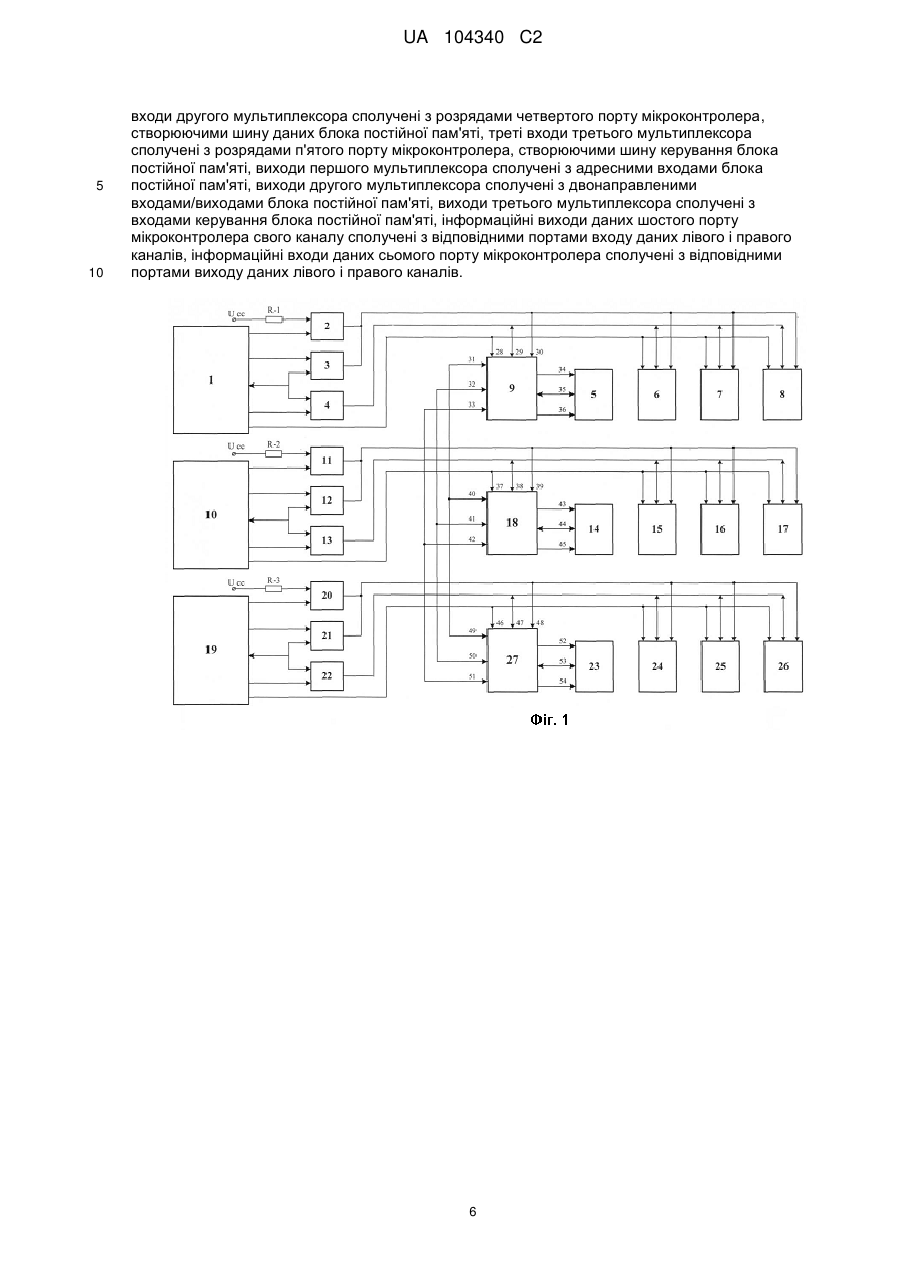

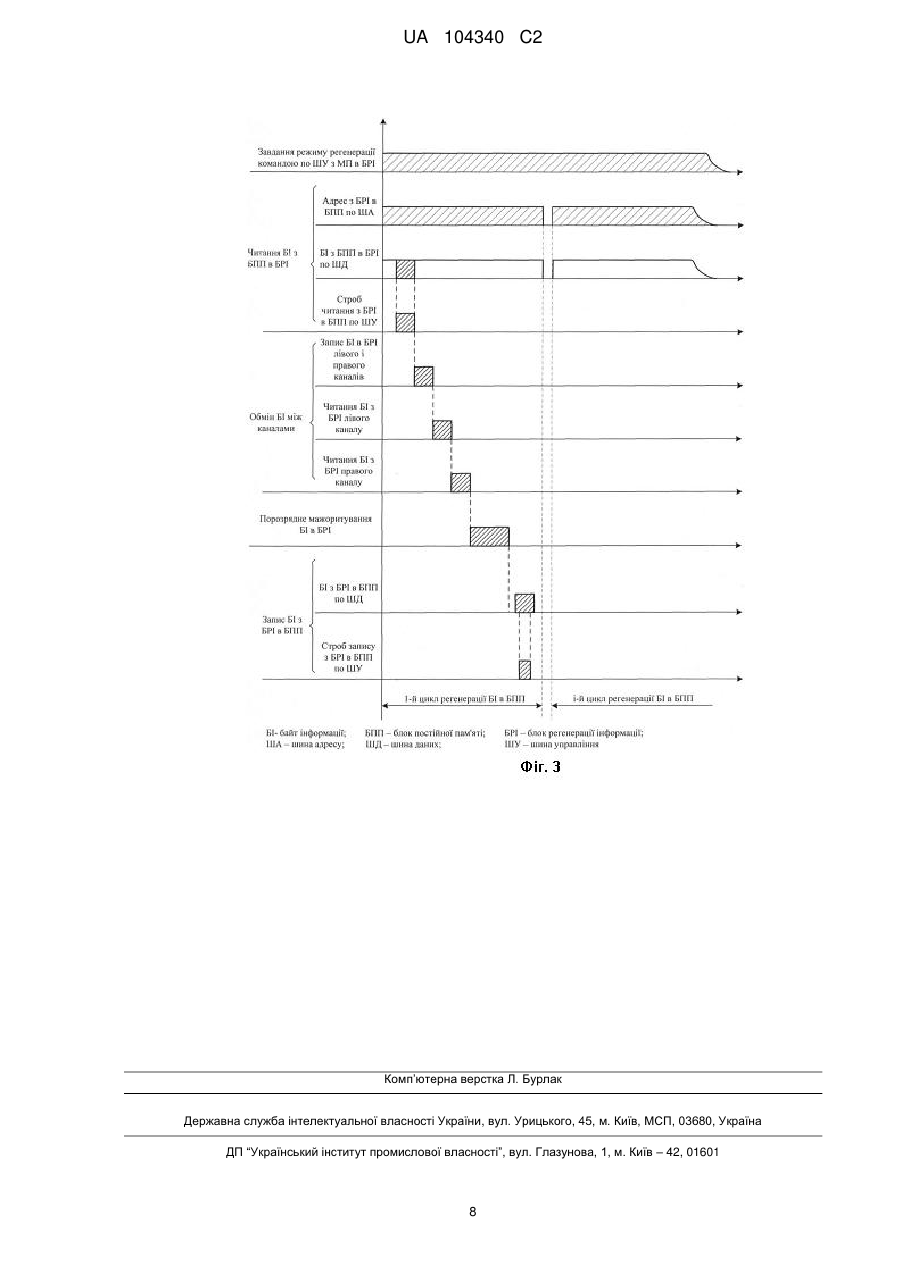

Реферат: Винахід належить до галузі обчислювальної техніки. Мікропроцесорна система за допомогою введення в кожний канал блока регенерації інформації, який містить перший мультиплексор адресної шини, другий мультиплексор шини даних, третій мультиплексор шини керування мікропроцесора і один мікроконтролер, а також зв'язків між ними забезпечує збільшення тривалості безперервної безвідмовної роботи системи при експлуатації в складних завадових умовах. UA 104340 C2 (12) UA 104340 C2 UA 104340 C2 5 10 15 20 25 30 35 40 45 50 55 60 Винахід належить до області обчислювальної техніки. Відома мікропроцесорна система, що містить тактовий пристрій, мікропроцесор, шину даних, шину адреси і оперативний пристрій, що запам'ятовує, постійний пристрій, що запам'ятовує, мікросхеми сполучення, підключені до відповідних шин даних, адреси і керування мікропроцесора, периферійні пристрої, підключені до входів і виходів мікросхем сполучення (див. Колосов В.Г., Мелехин В.Ф. Проектування вузлів і систем автоматики і обчислювальної техніки. - Л.: Енергоатоміздат, Ленінгр. відділення, 1983.- С. 107…110, мал. 3-34). Недоліком цієї системи є втрата працездатності за наявності будь-якої однієї відмови в її устаткуванні. Відома мікропроцесорна система, один канал якої містить мікропроцесор, два буферні регістри, буфер даних, блок постійної пам'яті, блок оперативної пам'яті, порт введення, порт виводу і зовнішні пристрої, при цьому перший вхід першого буферного регістра через резистор сполучений з клемою позитивного потенціалу джерела живлення, перша восьмирозрядна адресна шина мікропроцесора сполучена з відповідними входами першого буферного регістра, перший вхід другого буферного регістра сполучений з першим виходом мікропроцесора, друга восьмирозрядна адресна шина мікропроцесора сполучена з відповідними входами другого буферного регістра і буфера даних, другий вихід мікропроцесора сполучений з першим входом буфера даних, виходи першого і другого буферних регістрів утворюють адресну шину мікропроцесора і сполучені з відповідними адресними входами блока постійної пам'яті і блока оперативної пам'яті, виходи другого буферного регістра сполучені з відповідними адресними входами порту введення і порту виводу, виходи буфера даних утворюють шину даних мікропроцесора і сполучені з відповідними входами блока постійної пам'яті, блока оперативної пам'яті, порту введення і порту виводу, виходи шин керування мікропроцесора сполучені з відповідними входами блока постійної пам'яті, блока оперативної пам'яті, порту введення і порту виводу, входи порту введення і виходи порту виводу сполучені з виходами і входами зовнішніх пристроїв відповідно, (див. Угрюмов е. П. Цифрова схемотехніка - Спб: БХВ Петербург, 2001. - с. 250…252, мал. 5.1). Недоліком цієї системи є низька її надійність, обумовлена втратою працездатності за наявності будь-якої однієї катастрофічної або короткочасної відмови. Відома найбільш близька по технічній суті триканальна мікропроцесорна система, кожен канал якої містить мікропроцесор, два буферні регістри, буфер даних, блок постійної пам'яті, блок оперативної пам'яті, порт введення, порт виводу, зовнішні пристрої і блоки вибірки серединного значення, при цьому перший вхід першого буферного регістра через резистор сполучений з клемою позитивного потенціалу джерела живлення, перша восьмирозрядна адресна шина мікропроцесора сполучена з відповідними входами першого буферного регістра, перший вхід другого буферного регістра сполучений з першим виходом мікропроцесора, друга восьмирозрядна адресна шина мікропроцесора сполучена з відповідними входами другого буферного регістра і буфера даних, другий вихід мікропроцесора сполучений з першим входом буфера даних, виходи першого і другого буферних регістрів утворюють адресну шину мікропроцесора і сполучені з відповідними адресними входами блока постійної пам'яті і блока оперативної пам'яті, виходи другого буферного регістра сполучені з відповідними адресними входами порту введення і порту виводу, виходи буфера даних утворюють шину даних мікропроцесора і сполучені з відповідними входами блока постійної пам'яті, блока оперативної пам'яті і порту виводу, виходи шин керування мікропроцесора сполучені з відповідними входами блока постійної пам'яті, блока оперативної пам'яті, порту введення і порту виводу, входи порту введення і виходи порту виводу сполучені з виходами і входами зовнішніх пристроїв відповідно, перші входи блоків вибірки серединного значення одночасно сполучені з виходами даних порту введення першого каналу, другі входи одночасно сполучені з виводами даних порту введення другого каналу, треті входи одночасно сполучені з виходами даних порту введення третього каналу відповідно, виходи даних блока вибірки серединного значення двійкових чисел кожного каналу сполучені з відповідними виходами буфера даних свого каналу (див. Патент України на винахід № 97179 "Мікропроцесорна система", винахідників Лозового О.Г., Макаренко О.Я.). Недоліком цієї системи є недостатня тривалість безперервної безвідмовної роботи, обумовлена можливою втратою працездатності, викликаної накопиченням короткочасних відмов (збоїв) в блоках пам'яті при експлуатації в складних завадових умовах. Задачею пропонованого винаходу є збільшення тривалості безперервної безвідмовної роботи системи при експлуатації в складних завадових умовах. Поставлена задача вирішується тим, що в мікропроцесорну систему, що містить в кожному каналі мікропроцесор, два буферні регістри, буфер даних, блок постійної пам'яті, блок оперативної пам'яті, порт введення, порт виводу, при цьому перший вхід першого буферного 1 UA 104340 C2 5 10 15 20 25 30 35 40 45 50 55 60 регістра через резистор сполучений з клемою позитивного потенціалу джерела живлення, перша восьмирозрядна адресна шина мікропроцесора сполучена з відповідними входами першого буферного регістра, перший вхід другого буферного регістра сполучений з першим виходом мікропроцесора, друга восьмирозрядна адресна шина мікропроцесора сполучена з відповідними входами другого буферного регістра і буфера даних, другий вихід мікропроцесора сполучений з першим входом буфера даних, виходи першого і другого буферних регістрів утворюють адресну шину мікропроцесора і сполучені з відповідними адресними входами блока оперативної пам'яті, виходи другого буферного регістра сполучені з відповідними адресними входами порту введення і порту виводу, виходи буфера даних утворюють шину даних мікропроцесора і сполучені з відповідними входами блока оперативної пам'яті порту введення і порту виводу, виходи шин керування мікропроцесора сполучені з відповідними входами блока оперативної пам'яті, порту введення і порту виводу, додатково в кожен канал вводиться блок регенерації інформації, при цьому перші, другі і треті входи блока регенерації інформації сполучені з шиною керування, шиною даних і з шиною адреси мікропроцесора відповідно, четверті двонаправлені входи/виходи блока регенерації інформації сполучені з двонаправленою шиною даних блока постійної пам'яті, перші виходи адресної шини блока регенерації інформації сполучені з відповідними входами блока постійної пам'яті, другі виходи шини керування сполучені з відповідними входами блока постійної пам'яті в кожному каналі, треті інформаційні виходи блока регенерації інформації першого каналу сполучені з п'ятими інформаційними входами блоків регенерації інформації в другому і третьому каналах відповідно, треті інформаційні виходи блока регенерації інформації другого каналу сполучені з п'ятими і шостими інформаційними входами блоків регенерації інформації в першому і третьому каналах відповідно, треті інформаційні виходи блока регенерації інформації третього каналу сполучені з шостими і п'ятими інформаційними входами блоків регенерації інформації в другому і першому каналах відповідно. Крім того, поставлена задача вирішується тим, що кожен блок регенерації інформації містить перший мультиплексор шини адреси, другий мультиплексор шини даних, третій мультиплексор шини керування мікропроцесора і один мікроконтролер, при цьому перші входи мультипроцесорів сполучені з шиною адреси, шиною даних і шиною керування мікропроцесора відповідно, другі входи мультиплексорів сполучені з шиною керування мікропроцесора і з розрядами першого порту мікроконтролера, треті входи першого мультиплексора сполучені з розрядами другого і третього портів мікроконтролера, створюючими шину адреси блока постійної пам'яті, треті входи другого мультиплексора сполучені з розрядами четвертого порту мікроконтролера, створюючими шину даних блока постійної пам'яті, треті входи третього мультиплексора сполучені з розрядами п'ятого порту мікроконтролера, створюючими шину керування блока постійної пам'яті, виходи першого мультиплексора сполучені з адресними входами блока постійної пам'яті, виходи другого мультиплексора сполучені з двонаправленими входами/виходами даних блока постійної пам'яті, виходи третього мультиплексора сполучені з входами керування блока постійної пам'яті, інформаційні виходи даних шостого порту мікроконтролера свого каналу сполучені з відповідними портами входу даних лівого і правого каналів, входи даних сьомого порту мікроконтролера сполучені з відповідними портами виходу даних лівого і правого каналів. На Фіг. 1 наведена блок-схема мікропроцесорної системи. На Фіг. 2 наведена блок-схема блока регенерації інформації. На Фіг. 3 наведена тимчасова діаграма роботи блока регенерації інформації. Мікропроцесорна система (Фіг. 1) містить мікропроцесор 1, резистор R-1, перший 2, другий 3 буферні регістри, буфер даних 4, блок постійної пам'яті 5, блок оперативної пам'яті 6, порт введення 7, порт виводу 8 і блок регенерації інформації 9 першого каналу мікропроцесорної системи, мікропроцесор 10, резистор R-2, перший 11, другий 12 буферні регістри, буфер даних 13, блок постійної пам'яті 14, блок оперативної пам'яті 15, блок введення 16, блок виводу 17 і блок регенерації інформації 18 другого каналу мікропроцесорної системи, мікропроцесор 19, резистор R-3, перший 20, другий 21 буферні регістри, буфер даних 22, блок постійної пам'яті 23, блок оперативної пам'яті 24, блок введення 25, блок виводу 26 і блок регенерації інформації 27 третього каналу мікропроцесорної системи, зв'язки по входах шини керування 28, шини даних 29, шини адреси 30, зв'язки з блоком постійної пам'яті 5 по шині адреси 34, шині даних 35, шині керування 36, зв'язки 31, 32, 33 блоки регенерації інформації 9 по шинах даних з блоками регенерації інформації 18, 27 лівого і правого каналу першого каналу мікропроцесорної системи, зв'язки по входах шини керування 37, шини даних 38, шини адреси 39, зв'язки з блоком постійної пам'яті 14 по шині адреси 43, шині даних 44, шині керування 45, зв'язки 40, 41, 42 блоки регенерації інформації 18 по шинах даних з блоками регенерації інформації 9, 27 2 UA 104340 C2 5 10 15 20 25 30 35 40 45 50 55 60 лівого і правого каналу другого каналу мікропроцесорної системи, зв'язки по входах шини керування 46, шини даних 47, шини адреси 48, зв'язки з блоком постійної пам'яті 23 по шині адреси 52, шині даних 53, шині керування 54, зв'язки 49, 50, 51 блока регенерації інформації 27 по шинах даних з блоками регенерації інформації 19, 18 лівого і правого каналу третього каналу мікропроцесорної системи. Блок регенерації інформації (Фіг. 2) містить мікроконтролер 55, перший мультиплексор 56 шини адреси, другий мультиплексор 57 шини даних і третій мультиплексор 58 шини керування. Мікропроцесорна система функціонує таким чином. По включенню живлення мікропроцесори 1, 10, 19 сигналом "Скидання", що автоматично виробляється, приводяться в початковий стан. При постійно дозволяючих сигналах, що надходять на перші входи буферних регістрів 2, 11, 20 з першої восьмирозрядної адресної шини мікропроцесорів 1, 10, 19 в буферні регістри 2, 11, 20 записується старший байт 16-ти розрядної адреси відповідно. Молодший байт 16-ти розрядної адреси передається з другої восьмирозрядної шини мікропроцесорів 1, 10, 19 в буферні регістри 3, 12, 21 за наявності на їх перших входах сигналу дозволу з перших виходів мікропроцесорів 1, 10, 19 відповідно. Після завантаження буферних регістрів 3, 12, 21 сигнал дозволу з їх перших входів знімається і їх вміст зберігається до нового циклу завантаження, при цьому на виходах буферних регістрів 2, 3 першого каналу, буферних регістрів 11, 12 другого каналу, буферних регістрів 20, 21 третього каналу мікропроцесорної системи буде сформований 16-ти розрядний код адреси, який по адресних шинах надходить на перші входи блока регенерації інформації 9, блока оперативної пам'яті 6, порту введення 7 і порту виводу 8 першого каналу мікропроцесорної системи, блока регенерації інформації 18, блока оперативної пам'яті 15, порту введення 16, порту виводу 17 другого каналу мікропроцесорної системи, блока регенерації інформації 27, блока оперативної пам'яті 24, порту введення 25 і порту виводу 26 третього каналу мікропроцесорної системи. Після передачі молодшого байта адреси друга восьмирозрядна шина мікропроцесорів 1, 10, 19 віддається для передачі даних. Ці передачі двонаправлені, напрям задається буферами даних 4, 13, 22 залежно від стану сигналу, що надходить з другого виходу мікропроцесорів 1, 10, 19 на перший вхід буферів даних 4, 13, 22 в кожному каналі мікропроцесорної системи відповідно. При активному стані сигналу з другого виходу мікропроцесорів 1, 10, 19 дані передаються справа наліво, при пасивному - у зворотному напрямі в кожному каналі мікропроцесорної системи. Таким чином, на виходах буферів 4, 13, 22 буде сформована двонаправлена інформаційна шина даних, підключена до других входів блоків регенерації інформації 9, 18, 27, блоків оперативної пам'яті 6, 15, 24, портів введення 7, 16, 25 і портів виводу 8, 17, 26 в кожному каналі мікропроцесорної системи відповідно. Шини керування з виходів керування мікропроцесорів 1, 10, 19 підключаються до третіх входів блоків регенерації інформації 9, 18, 27, блоків оперативної пам'яті 6, 15, 24, портів введення 7, 16, 25 і портів виводу 8, 17, 26 в кожному каналі мікропроцесорної системи відповідно, перші виходи адресної шини блоків регенерації інформації 9, 18, 27 сполучені з адресними входами блоків постійної пам'яті 5, 14, 23, четверті двонаправлені входи/виходи блоків регенерації інформації 9, 18, 27 сполучені двонаправленою шиною даних блоків постійної пам'яті 5, 14, 23, другі виходи шини керування блоків регенерації інформації 9, 18, 27 сполучені з входами керування блоків постійної пам'яті 5, 14, 23 в кожному каналі мікропроцесорної системи відповідно, треті інформаційні виходи блока регенерації 9 першого каналу сполучені з п'ятими інформаційними входами блоків регенерації інформації 18, 27 в другому і третьому каналах, треті інформаційні виходи блока регенерації інформації 18 другого каналу сполучені з п'ятими і шостими інформаційними входами блоків регенерації інформації 9, 27 в першому і третьому каналах відповідно, треті інформаційні виходи блока регенерації інформації 27 третього каналу сполучені з шостими і п'ятими інформаційними входами блоків регенерації інформації 18, 19 в другому і третьому каналах відповідно. Робота мікропроцесорної системи починається з включення напруги живлення, приведення мікропроцесорної системи в початковий стан, при якому шини керування, шини даних і шини адреси мікропроцесора 1 першого каналу по шинах зв'язку 28, 29, 30 через блок регенерації інформації 9 надходять на шину керування 36, шину даних 35 і шину адреси 34 блоки постійної пам'яті 5, шини керування, шини даних і шини адреси мікропроцесора 10 другого каналу по шинах зв'язку 37, 38, 39 через блок регенерації інформації 18 надходять на шину керування 45, шину даних 44 і шину адреси 43 блоки постійної пам'яті 14, шини керування, шини даних і шини адреси мікропроцесора 19 третього каналу по шинах зв'язку 46, 47, 48 через блок регенерації інформації 27 надходять на шину керування 54, шину даних 53, шину адреси 52 блоки постійної пам'яті 23 і закачування програми роботи з блоків постійної пам'яті 5, 14, 23 в блоки оперативної пам'яті 6, 15, 24 з подальшою видачею команд, що управляють, через порти виводу 8, 17, 26 на 3 UA 104340 C2 5 10 15 20 25 30 35 40 45 50 55 виконавські елементи в кожному каналі мікропроцесорної системи. Реакцією на команди, що управляють, є донесення, що надходять на входи портів 7, 16, 25 в кожному каналі мікропроцесорної системи. Мікропроцесорна система в режимі регенерації інформації, що міститься в блоках пам'яті, працює за спеціальною програмою відповідно до тимчасової діаграми, приведеної на малюнку Фіг. 3. Режим регенерації інформації задається мікропроцесорами 1, 10, 19 спеціальною командою, що надходить по шинах керування на шини зв'язку 28, 37, 46 блоків регенерації інформації 9, 18, 27 відповідно. Блок регенерації інформації (Фіг. 2) функціонує таким чином. Спеціальна команда, сформована мікропроцесорами 1, 10, 19 надходить по шинах керування через шини зв'язків 28, 37, 46 блоків регенерації інформації 9, 18, 27 на перший порт мікроконтролерів 55 і на другий вхід мультиплексорів 56 адреси, мультиплексорів 57 шини даних і мультиплексорів 58 шини керування, задаючи мікроконтролерам 55 режим регенерації інформації, а також перемикаючи шини адреси, шини даних і шини керування мікропроцесорів 1, 10, 19, що надходять по зв'язках 30, 39, 48 на перший вхід мультиплексорів 56, по зв'язках 29, 38, 47 на перший вхід мультиплексорів 57 і по зв'язках 28, 37, 46 на перший вхід мультиплексорів 58 відповідно на шину адреси з виходу третього і четвертого портів мікроконтролерів 55 на третій вхід мультиплексорів 56, на шину даних з виходу четвертого порту мікроконтролерів 55 на третій вхід мультиплексорів 57, на шину керування з виходу порту п'ять мікроконтролерів 55 на третій вхід мультиплексорів 58 в кожному блоці регенерації інформації 9, 18, 27 відповідно. Таким чином, шини адреси по зв'язках 34, 43, 52, шини даних по зв'язках 35, 44, 53 і шини керування по зв'язках 36, 45, 54 блоків постійної пам'яті 5, 14, 23 підключені через мультиплексори 56, 57, 58 до відповідних портів шини адреси, шини даних і шини керування мікроконтролерів 55 в кожному блоці регенерації інформації відповідно. Перший цикл регенерації інформації (Фіг. 3) здійснюється мікроконтролерами 55 блоків регенерації інформації 9, 18, 27 шляхом задання адреси першого байта інформації, що надходить через мультиплексори 56 по зв'язках 34, 43, 52 на шини адреси блоків постійної пам'яті 5, 14, 23. Підготовлений блоками постійної пам'яті 5, 14, 23 байт інформації при видачі мікроконтролерами 55 строба читання, що надходить через мультиплексори 58 по зв'язках 36, 45, 54 на входи шин керування блоків постійної пам'яті 5, 14, 23, прочитується по шинах даних блоків постійної пам'яті 5, 14, 23 по зв'язках 35, 44, 53 через мультиплексори 57 в пам'ять мікроконтролерів 55 кожного блока регенерації інформації відповідно. Після считування першого байта інформації з блоків постійної пам'яті 5, 14, 23 мікроконтролери 55 блоків регенерації 9,18, 27 проводять обмін отриманими байтами інформації. При цьому інформація з виходу порту в мікроконтролери 55 блока регенерації інформації 9 по зв'язку 31 через зв'язок 40 надходить на інформаційний вхід порту сім мікроконтролера 55 блока регенерації інформації 18 і через зв'язок 49 на інформаційний вхід порту сім мікроконтролера 55 блока регенерації інформації 27, інформація з виходу порту 6 мікроконтролера 55 блока регенерації 18 по зв'язку 41 через зв'язок 32 надходить на інформаційний вхід порту сім мікроконтролера 55 блока регенерації інформації 9 і по зв'язку 50 на інформаційний вхід порту сім мікроконтролера 55 блока регенерації інформації 27, інформація з виходу порту 6 по зв'язку 51 через зв'язок 33 надходить на інформаційний вхід порту сім мікроконтролера 55 блока регенерації інформації 9 і через зв'язок 42 на інформаційний вхід порту 7 мікроконтролера 55 регенерацій 18. Таким чином, після обміну інформацією в пам'яті кожного контроллера 55 блоків регенерації інформації 9, 18, 27 знаходяться байти інформації, лічені з блоків постійної пам'яті 5, 14, 23. Подальшою операцією є порозрядне мажоритування байта інформації, таке, що здійснює вибірку достовірного значення біта інформації в розряді по будь-яких двох достовірних значеннях. Отриманий байт інформації не міститиме можливих непересічних короткочасних відмов (збоїв), накопичених в каналах блоків постійної пам'яті 5, 14, 23 мікропроцесорних системи. Після операції мажоритування мікроконтролери 55 виставляють результуючий байт інформації на шину даних порту чотири, який через треті інформаційні входи мультиплексорів 57 блоків регенерації інформації 9, 18, 27 по лініях зв'язку 35, 44, 53 надходить на вхідні шини даних блоків постійної пам'яті 5, 14, 23 відповідно. Запис результуючого байта інформації проводиться по стробу запису, сформованому на шині керування порту п'ять мікроконтролерів 55, які через треті входи мультиплексорів 58 блоків регенерації інформації 9, 18, 27 по лініях 4 UA 104340 C2 5 10 15 20 зв'язку 36, 45, 54 надходять на вхідні шини керування блоків постійної пам'яті 5, 14, 23 відповідно. Запис результуючого байта інформації в блоки постійної пам'яті 5, 14, 23 проводиться за тією ж адресою, з якої було проведено зчитування, що дозволяє у всіх трьох каналах блоків постійної пам'яті 5, 14, 23 виключити можливі короткочасні непереміжні відмови за даною адресою. Шляхом задання подальших циклів регенерації проводиться відновлення достовірної інформації від короткочасних непереміжних відмов як в окремих масивах, так і у всьому об'ємі блоків постійної пам'яті 5, 14, 23. Після регенерації інформації в блоках постійної пам'яті 5, 14, 23 можливе накопичення короткочасних відмов в блоках оперативної пам'яті 6, 15, 24 може бути усунено шляхом перепису робочих масивів інформації з блоків постійної пам'яті 5, 14, 23. Технічний аналіз переваг приводиться по відношенню до прототипу, як найбільш прогресивного технічного рішення, відомого авторам подачі заявки. Як показав аналіз схемно-технічних рішень і результатів експериментального відробітку пропонована мікропроцесорна система забезпечує збільшення тривалості безперервної безвідмовної роботи за рахунок періодичного усунення короткочасних відмов в блоках пам'яті при тривалій експлуатації у складі систем орієнтації і стабілізації штучних супутників землі і космічних апаратів, у складі систем керування технологічними процесами атомних електростанцій. Таким чином, як випливає з приведених вище матеріалів опису, пропонована мікропроцесорна система по відношенню до прототипу забезпечує істотний ефект підвищення тривалої безперервної безвідмовної роботи і відповідно ефект економічності в експлуатації. ФОРМУЛА ВИНАХОДУ 25 30 35 40 45 50 55 60 1. Мікропроцесорна система, кожен канал якої містить мікропроцесор, два буферні регістри, буфер даних, блок постійної пам'яті, блок оперативної пам'яті, порт введення, порт виводу, при цьому перший вхід першого буферного регістра через резистор сполучений з клемою позитивного потенціалу джерела живлення, перша восьмирозрядна адресна шина мікропроцесора сполучена з відповідними входами першого буферного регістра, перший вхід другого буферного регістра сполучений з першим виходом мікропроцесора, друга восьмирозрядна адресна шина мікропроцесора сполучена з відповідними входами другого буферного регістра і буфера даних, другий вихід мікропроцесора сполучений з першим входом буфера даних, виходи першого і другого буферних регістрів утворюють адресну шину мікропроцесора і сполучені з відповідними адресними входами блока оперативної пам'яті, виходи другого буферного регістра сполучені з відповідними адресними входами порту введення і порту виводу, виходи буфера даних утворюють двонаправлену шину даних мікропроцесора і сполучені з відповідними входами блока оперативної пам'яті, порту введення і порту виводу, виходи шин керування мікропроцесора сполучені з відповідними входами блока оперативної пам'яті, порту введення і порту виводу, яка відрізняється тим, що в кожен канал додатково введені блок регенерації інформації, при цьому перші, другі і треті входи блока регенерації інформації сполучені з шиною керування, шиною даних і з адресною шиною мікропроцесора відповідно, четверті двонаправлені входи/виходи блока регенерації інформації сполучені з двонаправленою шиною даних блока постійної пам'яті, перші виходи адресної шини блока регенерації інформації сполучені з відповідними входами блока постійної пам'яті, другі виходи шини керування сполучені з відповідними входами блока постійної пам'яті в кожному каналі, треті інформаційні виходи блока регенерації інформації першого каналу сполучені з п'ятими інформаційними входами блоків регенерації інформації в другому і третьому каналах відповідно, треті інформаційні виходи блока регенерації інформації другого каналу сполучені з п'ятими і шостими інформаційними входами блоків регенерації інформації в першому і третьому каналах відповідно, треті інформаційні виходи блока регенерації інформації третього каналу сполучені з шостими і п'ятими інформаційними входами блоків регенерації інформації в другому і першому каналах відповідно. 2. Система за п. 1, яка відрізняється тим, що кожен блок регенерації інформації містить перший мультиплексор шини адреси, другий мультиплексор шини даних, третій мультиплексор шини керування мікропроцесора і один мікроконтролер, при цьому перші входи мультиплексорів сполучені з шиною адреси, шиною даних і шиною керування мікропроцесора відповідно, другі входи мультиплексорів сполучені з шиною керування мікроконтролера і розрядами першого порту мікроконтролера, треті входи першого мультиплексора сполучені з розрядами другого і третього портів мікроконтролера, створюючими шину адреси блока постійної пам'яті, треті 5 UA 104340 C2 5 10 входи другого мультиплексора сполучені з розрядами четвертого порту мікроконтролера, створюючими шину даних блока постійної пам'яті, треті входи третього мультиплексора сполучені з розрядами п'ятого порту мікроконтролера, створюючими шину керування блока постійної пам'яті, виходи першого мультиплексора сполучені з адресними входами блока постійної пам'яті, виходи другого мультиплексора сполучені з двонаправленими входами/виходами блока постійної пам'яті, виходи третього мультиплексора сполучені з входами керування блока постійної пам'яті, інформаційні виходи даних шостого порту мікроконтролера свого каналу сполучені з відповідними портами входу даних лівого і правого каналів, інформаційні входи даних сьомого порту мікроконтролера сполучені з відповідними портами виходу даних лівого і правого каналів. 6 UA 104340 C2 7 UA 104340 C2 Комп’ютерна верстка Л. Бурлак Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 8

ДивитисяДодаткова інформація

МПК / Мітки

МПК: G06F 7/57, G05B 11/32

Мітки: мікропроцесорна, система

Код посилання

<a href="https://ua.patents.su/10-104340-mikroprocesorna-sistema.html" target="_blank" rel="follow" title="База патентів України">Мікропроцесорна система</a>

Попередній патент: Гальмівна колодка для дискових гальм транспортного засобу

Наступний патент: Нейромережний пристрій зі штучним інтелектом для рівномірного розподілення навантажень в мережах 0,38/0,22 кв

Випадковий патент: Спосіб автоматичного керування процесом зневоднення та гранулювання у псевдозрідженому шарі