Пристрій для визначення кількості одиниць (нулів) у двійковому числі

Формула / Реферат

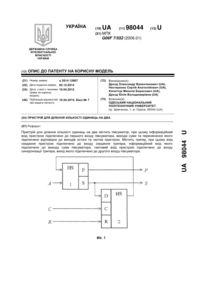

Пристрій для визначення кількості одиниць (нулів) у двійковому числі, що містить модулі, які складаються з елементів АБО, який відрізняється тим, що пристрій містить 2n-1 модулів, які послідовно розташовані один за одним, причому перший модуль складається з 2n комбінаційних схем визначення кількості одиниць у чотирирозрядному двійковому коді, третій модуль містить 2n-2 комбінаційних схем визначення одиниць у шістнадцятирозрядному двійковому коді, кожний наступний модуль містить у два рази менше комбінаційних схем визначення одиниць у двійковому коді, кількість розрядів якого у два рази більше, ніж у комбінаційних схем попереднього модуля, причому виходи кожної непарної комбінаційної схеми попереднього модуля підключені до перших входів відповідної комбінаційної схеми наступного модуля, а виходи кожної парної комбінаційної схеми попереднього модуля підключені до других входів відповідної комбінаційної схеми наступного модуля, виходи перших комбінаційних схем кожного модуля підключені до виходів пристрою, а входи комбінаційних схем першого модуля підключені до входів пристрою.

Текст

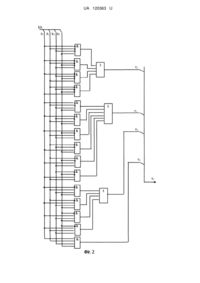

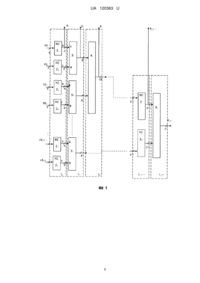

Реферат: UA 120363 U UA 120363 U 5 Корисна модель належить до обчислювальної техніки, а саме до обробки даних, і може бути використана для побудови засобів автоматики, функціональних вузлів систем управління та обробки зображень. Відомо пристрій для підрахунку кількості одиниць у двійковому коді (Патент Росії №1795455, МПК G06F 7/50, Бюл. № 6, 1993), що містить n-розрядний вхідний регістр, вихідний регістр, вузол керованої інверсії, який зв'язаний з керуючим входом, перетворювач двійкового коду в ущільнений код, модифіковану матрицю модулів, кожний з яких містить елемент І і елемент АБО, яка складається з m 1 10 15 20 25 30 35 40 45 50 55 2 строк модулів, перетворювач ущільненого коду у двійковий код кількості одиниць. Недоліком даного пристрою є те, що проводиться декілька перетворювань кодів вхідного двійкового коду в ущільнений код, формування вихідного ущільненого коду, який дорівнюється кількості одиниць у вхідному коді, перетворення ущільненого коду у двійковий код кількості одиниць. Така організація знижує швидкодію та надійність функціонування. Відомо пристрій для підрахунку кількості одиниць в n-розрядному двійковому коді, який містить яруси, що складаються з суматорів і блоків сумування, які складаються з тривходових суматорів, півсуматорів, логічних елементів І та ВИКЛЮЧНЕ АБО. Недоліками даного пристрою є низька надійність функціонування та швидкодія за рахунок реалізації великої кількості обчислень. Найбільш близьким за технічною суттю до заявлюваної корисної моделі є пристрій для визначення кількості одиниць (нулів) у двійковому числі (Патент РФ №2446442, Бюл. №9, 2012), що містить елемент ВИКЛЮЧНЕ АБО і елемент І, причому перші і другі входи елемента ВИКЛЮЧНЕ АБО з'єднані відповідно з першим і другим входами елемента І і є, відповідно, першим і другим входами модуля, вихід елемента ВИКЛЮЧНЕ АБО є першим виходом модуля, вихід елемента І є другим виходом модуля, пристрій містить також елементи АБО і блок керованої інверсії, що складається з n-елементів ВИКЛЮЧНЕ АБО, де n-кількість розрядів вхідного числа, причому перші входи n-елементів ВИКЛЮЧНЕ АБО з'єднані між собою і підключені до зовнішнього керуючого входу, другі входи гьелементів ВИКЛЮЧНЕ АБО з'єднані з відповідними n-зовнішніми входами вхідного числа, виходи n-елементів ВИКЛЮЧНЕ АБО є відповідно першим - n-м виходами блоку керованої інверсії, модулі об'єднані в яруси і групи, які об'єднані в k-каскадів (k=] Iog2n [більше ціле), при цьому і-й каскад містить g(i)=n/2i груп (і=1,…, k), кожна група і-го каскаду розділена на j ярусів (j=1,…, і, ), кожна група і-го каскаду має 2і входів групи, які є входами першого ярусу групи, і (і+1) виходів групи (і=1,…, k), перший ярус кожної групи відповідного і-го каскаду містить відповідно і модулів і має 2і входів і 2і виходів (і=1,…, k), другий - j-й яруси кожної групи відповідного і-го каскаду (і=3,…, k, j=2,…, (і-1)), містять (i-j) модулів і елемент АБО і мають (2 (i-j) +2) входів ярусу і (2 (i-j) +1) виходів ярусу, і-й ярус кожної групи відповідного і-го каскаду (і=2,…, k), містить елемент АБО і має два входи і один вихід, перший і другий входи першого ярусу першої - (n/2)-й груп першого каскаду з'єднані відповідно з першим і другим входами відповідних модулів першого ярусу першої - (n/2)-ї груп першого каскаду, непарні перший, третій - (n-1)-й виходи блока керованої інверсії з'єднані з першими входами першого ярусу відповідно першої - (n/2)-й груп першого каскаду, парні другий, четвертий - n-й виходи блока керованої інверсії з'єднані з другими входами першого ярусу відповідно першої - (n/2)-й груп першого каскаду, перший і другий виходи модулів першого ярусу першої -(n/2)-й груп першого каскаду є відповідно першим і другим виходами першого ярусу відповідних першої - (n/2)-й груп першого каскаду, перший і другий входи першого - і-го модуля першого ярусу кожної групи другого - і-го каскадів є відповідно першим, другим, третім - (2і)-м входами першого ярусу відповідної групи другого - і-го каскадів (і=2,…, k), перший і другий виходи першого - і-го модуля першого ярусу кожної групи другого - і-го каскадів є відповідно першим, другим, третім - (2і)-м виходами першого ярусу відповідної групи другого - і-го каскадів (і = 2,…, k), перший і другий входи першого - (i-j)-гo модулів відповідно другого - j-ro ярусу кожної групи третього - k-гo каскаду є відповідно першим, другим - 2 (i-j) -му входами відповідного другого - j-ro ярусу відповідної групи третього - k-го каскаду (і=3, 4,…, k, j=2, 3,…, (і-1)), перший і другий виходи першого - (i-j) -го модулів відповідно другого - j- го ярусу кожної групи третього -kго каскаду є відповідно першим, другим - 2 (i-j) -м виходами відповідного другого - j-ro ярусу відповідної групи третього - k-го каскаду (і=3, 4,…, k, j=2, 3,…, (і-1)), перший і другий входи елемента АБО відповідно другого - j-ro ярусу кожної групи відповідно другого - k-го каскаду є відповідно (2(i-j)+1)-M і (2(і-j)+2)-M входами відповідного другого - j-гo ярусу відповідної групи відповідного другого - k-го каскаду (і = 2, 3,…, k, j=2, 3,…, і), вихід елемента АБО відповідно другого - j- го ярусу кожної групи відповідно другого - k-го каскаду є відповідно ((i-j)+l)-M виходом відповідного другого - j-ro ярусу відповідної групи відповідного другого - k-го каскаду (і=2, 3,…, k, 1 UA 120363 U 5 10 15 20 25 30 35 40 45 50 55 60 j=2, 3,…, і), другий, третій - (2 (i-j)+1) -й виходи відповідно першого - j- го ярусу кожної групи відповідно другого - і-го каскаду з'єднані відповідно з першим, другим - (2(i-j))-м входами відповідного другого - (j+1) -го ярусу відповідної групи відповідно другого - і-го каскаду (і=2, 3,…, k), j=1, 2,…, (і-1)), перші виходи відповідно першого - j-ro ярусу кожної групи відповідного другого - і-го каскаду є відповідно першим, другим - j-м виходами відповідної групи відповідно другого - іго каскаду (і=2, 3,…, k, ) j=2,…, і), старший (2і) -й вихід 1-го ярусу кожної групи відповідно другого - і-го каскадів є відповідно старшим (і+1) -м виходом відповідної групи відповідно другого - і-го каскадів (і=2, 3,…, k), перший, другий - (z+1) -й виходи непарних першої, третьої (s-1) -й груп z-го каскаду з'єднані відповідно з непарними першим, третім - (2z-1)-m входами відповідно першої, другої - (s/2)-й груп (z+1)- го каскаду, (z=1,…, (k-1), s=2, 4, 6,…, n/2z), перший, другий - (z+1) -й виходи парних другою, четвертою - s-ї груп z- го каскаду з'єднані відповідно з парними другим, четвертим - (2z) -м входами відповідно першої, другої - (s/2) -ї групи (z+1) -го каскаду (z=1,…, (k-1), s=2, 4, 6,…, n/2z), перший, другий - (k+1) - й виходи групи k-го каскаду є відповідно першим, другим - (k+1) -м виходами пристрою. Недоліками даного пристрою є низька швидкодія та надійність функціонування, оскільки для реалізації пристрою використовується постійне подання результату у двійковій системі числення, а також для отримання результату використовується велика кількість каскадів. Наприклад, для шістнадцятирозрядного двійкового коду використовується одинадцять логічних ярусів та чотири каскади. Кожний логічний ярус здійснює затримку одним логічним елементом. При цьому елементи ВИКЛЮЧНЕ АБО, АБО та І мають різні затримки. Отже затримка одного ярусу визначається найбільшою затримкою одного логічного елемента. Як правило найбільшу має елемент ВИКЛЮЧНЕ АБО, оскільки він реалізується двома каскадами кон'юнкторів та диз'юнкторів. Задачею корисної моделі є підвищення швидкодії та надійності функціонування. Висока швидкодія та надійність досягаються за рахунок зменшення логічних ярусів і подання результату у одинично-позиційному коді. Поставлена задача вирішується тим, що пристрій для визначення кількості одиниць (нулів) у двійковому числі, що містить модулі, які складаються з елементів АБО, пристрій містить 2""' П модулів, які послідовно розташовані один за одним, причому перший модуль складається з 2 комбінаційних схем визначення кількості одиниць у чотирирозрядному двійковому коді, третій П 2 модуль містить 2 " комбінаційних схем визначення одиниць у шістнадцятирозрядному двійковому коді, кожний наступний модуль містить у два рази менше комбінаційних схем визначення одиниць у двійковому коді, кількість розрядів якого у два рази більше, ніж у комбінаційних схем попереднього модуля, причому виходи кожної непарної комбінаційної схеми попереднього модуля підключені до перших входів відповідної комбінаційної схеми наступного модуля, а виходи кожної парної комбінаційної схеми попереднього модуля підключені до других входів відповідної комбінаційної схеми наступного модуля, виходи перших комбінаційних схем кожного модуля підключені до виходів пристрою, а входи комбінаційних схем першого модуля підключені до входів пристрою. На фіг. 1 подано структурну схему пристрою для визначення кількості одиниць (нулів) у двійковому числі, на фіг. 2 представлена функціональна схема для визначення кількості одиниць (нулів) у чотирьох розрядному двійковому числі, на фіг. 3 - зображено графічне подання елементу для аналізу шістнадцятирозрядного двійкового коду та часові діаграми його роботи. Пристрій для визначення кількості одиниць (нулів) у двійковому числі (фіг. 1) містить модулі 11, 12,…, 1n, які послідовно розташовані один за одним, причому перший модуль 11 складається n з 2 комбінаційних схем 21,22,…,22n визначення кількості одиниць у чотирирозрядному n-1 n-1 двійковому коді, другий модуль 12 містить 2 комбінаційних схем 31,32,…,32 і визначення n-2 одиниць у восьмирозрядному двійковому коді, третій модуль 13 містить 2 комбінаційних схем 41,42,…,42„…2 визначення одиниць у шістнадцятирозрядному двійковому коді, кожний наступний модуль містить у два рази менше комбінаційних схем визначення одиниць у двійковому коді, кількість розрядів якого у два рази більше ніж у комбінаційних схем попереднього модуля, причому виходи 5, кожної непарної комбінаційної схеми попереднього модуля 1і підключені до перших входів 6 відповідної комбінаційної схеми попереднього модуля, а виходи 7, кожної непарної комбінаційної схеми попереднього модуля 1i підключені до других входів 8 відповідної комбінаційної схеми наступного модуля, виходи 5 перших комбінаційних схем кожного модуля підключені до виходів 91,92,…,92n-1 пристрою, а входи комбінаційних схем 21,22,…,22n підключені до входів 101,102,…,102n пристрою. Комбінаційна схема 2 визначення одиниць у двійковому коді (фіг. 2) містить п'ятнадцять чотиривходових кон'юнкторів, чотири з яких мають три інверсних входи і один прямий вхід, 2 UA 120363 U 5 шість містять два інверсних входи і два прямих входи, чотири кон'юнктори містять один інверсний вхід і три прямих входи, один чотиривходовий кон'юнктор без інверсних входів, а також два чотриривходових диз'юнктора і один шестивходовий диз'юнктор. Пристрій для визначення кількості одиниць (нулів) у двійковому числі працює в такий спосіб. Двійковий код у вигляді сигналів логічних "0" та "1" подається на відповідні входи 10 пристрою і на відповідні входи комбінаційних схем 2 першого модуля b (фіг. 1). Кожна комбінаційна схема реалізується згідно з таблицею істинності (таблиця 1). Таблиця 1 Таблиця істинності для четирирозрядної комбінаційної схеми підрахунку кількості одиниць в двійковому коді. X1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 10 X2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 Х3 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 У1 0 1 1 0 1 0 0 0 1 0 0 0 0 0 0 0 X4 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 У2 0 0 0 1 0 1 1 0 0 1 1 0 1 0 0 0 У3 0 0 0 0 0 0 0 1 0 0 0 1 0 1 1 0 У4 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 В таблиці 1 значення Х1, Х2, Х3, X4 позначають вхідні сигнали, а значення У1, У2, У3, У4 позначають логічні сигнали на виходах комбінаційної схеми. Виходи У i даної схеми описуються наступними логічними виразами. 1 1 2 3 4 1 2 3 4 1 2 3 4 1 2 3 4 2 1 2 3 4 1 2 3 4 1 2 3 4 1 2 3 4 1 2 3 4 1 2 3 4 3 1 2 3 4 1 2 3 4 1 2 3 4 1 2 3 4 4 1 2 3 4 . (1) 15 20 25 30 Функціональна схема, комбінаційної схеми 2 першого модуля 11 подана на фіг. 2. Дана схема реалізована згідно з таблицею 1 та логічними виразами (1). Час, який витрачається на отримання результату даною схемою, визначається сумарним часом спрацювання одного кон'юнктора і одного диз'юнктора. Сигнали результату виводяться на чотирирозрядний перший вихід 91 пристрою. Наприклад, якщо чотирирозрядний код на чотирирозрядному вході 10і містить дві одиниці, то на другому виході (У2=1) присутній одиничний сигнал, а на інших виходах (У1 = У3= У4=0) - нульовий сигнал. Опис поведінки даної комбінаційної схеми подано наступним VHDL-кодом. library IEEE; use IEEE.stdlogicl 164.all; entity CNOC4 is port( x1: in STD_LOGIC; x2: in STD_LOGIC; x3: in STD_LOGIC; x4: in STD_LOGIC; y1: out STD_LOGIC; y2: out STD_LOGIC; 3 UA 120363 U 5 10 15 20 25 30 35 40 45 y3: out STD_LOGIC; y4: out STD_LOGIC ); end CNOC4; architecture CNOC4 °F CNOC4 is signal NET332: STD_LOGIC; signal NET345: STD_LOGIC; signal NET362: STD_LOGIC; signal NET371: STD_LOGIC; signal NET4713: STD_LOGIC; signal NET4730: STD_LOGIC; signal NET4743: STD_LOGIC; signal NET4752: STD_LOGIC; signal NET842: STD_LOGIC; signal NET855: STD_LOGIC; signal NET864: STD_LOGIC; signal NET873: STD_LOGIC; signal NET882: STD_LOGIC; signal NET895: STD_LOGIC; signal NET904: STD_LOGIC; begin NET332

ДивитисяДодаткова інформація

МПК / Мітки

МПК: G06F 7/50

Мітки: нулів, двійковому, одиниць, числі, пристрій, кількості, визначення

Код посилання

<a href="https://ua.patents.su/10-120363-pristrijj-dlya-viznachennya-kilkosti-odinic-nuliv-u-dvijjkovomu-chisli.html" target="_blank" rel="follow" title="База патентів України">Пристрій для визначення кількості одиниць (нулів) у двійковому числі</a>

Попередній патент: Пральна машина

Наступний патент: Спосіб очищення газів від кислих домішок

Випадковий патент: Спосіб пресування кінців волокнистооптичних жгутів