Пристрій для визначення місць пошкодження напірного трубопроводу

Формула / Реферат

1. Устройство для определения мест повреждения напорного трубопровода, содержащее датчики двух каналов, соединенные с усилителями, выходы которых подключены ко входам формирователей импульсов, две пары буферных блоков оперативной памяти, информационные входы которых подключены к выходам первого и второго формирователей импульсов соответственно, первый-четвертый блоки управления памятью, выходы которых подключены к входам управления соответствующих буферных блоков оперативной памяти, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первые входы которых соединены с выходами буферных блоков оперативной памяти первой пары, а вторые - с выходами буферных блоков оперативной памяти второй пары, коммутатор, входы которого подключены к выходам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блок формирования приращения, входом подключенный к выходу коммутатора, реверсивный счетчик накопления, вход которого подключен к выходу блока формирования приращения, накопительный блок оперативной памяти, цифроаналоговый преобразователь, индикатор, первый вход которого подключен к выходу цифроаналогового преобразователя, генератор тактовых импульсов, первый блок управления устройством, второй блок управления, первый выход которого подключен к адресному входу накопительного блока оперативной памяти, блок вычисления расстояния, который содержит перестраиваемый генератор, элемент И, первый вход которого соединен с выходом перестраиваемого генератора, первый счетчик задержки, выход которого подключен к второму входу индикатора, счетчик установки задержки, кнопку маркера, выход которой подключен к входу счетчика установки задержки, индикатор расстояния до места утечки, счетчик расстояния, выход которого подключен к индикатору расстояния, блок переключателей установки расстояния между датчиками, группу сумматоров, входы которых подключены к блоку переключателей установки расстояния, а выходы подключены ко входу начальной установки счетчика расстояния, отличающееся тем, что в него введены управляемый делитель частоты, вход которого подключен к выходу генератора тактовых импульсов, а выход подключен к синхровходу блока управления устройством, переключатель режима, выход которого подключен к управляющему входу управляемого делителя частоты и первому блоку управления устройством, регистр результата, входом подключенный к выходу накопительного блока оперативной памяти и входу начальной установки реверсивного счетчика накопления, а выходом подключенный к входу аналого-цифрового преобразователя, второй счетчик задержки, вход начальной установки которого подключен к выходу счетчика установки задержки и входу начальной установки первого счетчика задержки, а выход подключен к второму входу элемента И, переключатель установки скорости, подключенный к управляющему входу перестраиваемого генератора, причем выход реверсивного счетчика накопления соединен с входом накопительного блока оперативной памяти, выход стробирующего сигнала второго блока управления подключен к синхровходу индикатора и входу разрешений начальной установки первого счетчика задержки, первый выход первого блока управления устройством подключен к первому управляющему входу блока формирования приращения, второй управляющий вход которого подключен к второму выходу первого блока управления устройством, третий выход которого подключен к синхровходу второго блока управления, вход начальной установки которого подключен к первым входам с первого по четвертый блоков управления памятью, входу управления индикатора расстояния и к четвертому выходу первого блока управления устройством, пятый и шестой выходы которого подключены соответственно к входам разрешения записи первых и вторых буферных блоков оперативной памяти, первой и второй пары, седьмой и восьмой выходу - ко вторым и - третьим входам первого и третьего блоков управления памятью, девятый и десятый выходы - ко вторым и третьим второго и четвертого блоков управления памятью, соответственно, вход разрешения записи накопительного блока оперативной памяти подключен ко входу переключателя адреса второго блока управления и к одиннадцатому выходу первого блока управления устройством, двенадцатый выход которого подключен к четвертым входам блоков управления памятью, пятые входы первых двух из которых и пятые входы вторых двух подключены к тринадцатому и четырнадцатому входам первого блока управления устройством, пятнадцатый выход которого подключен к старшему разряду входа начальной установки второго счетчика задержки, вход разрешения начальной установки которого подключен к входу кнопки маркера, к управляющему входу коммутатора и к десятому выходу первого блока управления устройством, шестнадцатый и семнадцатый выходы которого подключены соответственно к входам суммирования и вычитания первого счетчика задержки, восемнадцатый выход первого блока управления устройством подключен ко второму синхровходу второго блока управления и к входу управления начальной установки реверсивного счетчика накопления, вход сброса которого подключен к девятнадцатому выходу первого блока управления устройством, двадцатый выход которого подключен к вычитающему входу второго счетчика задержки, шестые входы первых и вторых блоков управления памятью первой и второй пары входных блоков оперативной памяти подключены к двадцать первому и двадцать второму выходам первого блока управления устройством соответственно.

2. Устройство по п.1, отличающееся тем, что блок формирования приращения содержит первый и второй триггеры, D-входы которых подключены к выходу коммутатора, а инверсный выход первого триггера и выход второго триггера соединены соответственно с входами сложения и вычитания реверсивного счетчика накопления, причем первый управляющий вход блока подключен к синхровходам первого и второго триггеров, S-вход первого и R-вход второго из которых подключены к второму управляющему входу этого блока.

3. Устройство по пп.1 и 2, отличающееся тем, что первый блок управления содержит кнопку пуска, кнопку продолжения, переключатель положения окна, четыре выхода которого соответствуют четырем положениям окна просмотра участка трубопровода, счетчик тактов, имеющий восемь ступеней деления частоты, синхровход которого является синхровходом и вторым выходом блока, первый элемент НЕ, вход которого подключен к синхровходу, а выход является первым выходом блока, первый триггер, выход которого является третьим выходом блока, а синхровход и R-вход подключены к инверсному выходу третьей ступени и выходу второй ступени счетчика тактов, с второго по четвертый триггеры, синхровходы которых подключены соответственно к инверсным выходам с четвертой по шестую ступеней счетчика тактов, пятый и шестой триггеры, D-входы которых подключены соответственно к выходам третьего и четвертого триггеров, седьмой триггер, R-вход которого подключен к кнопке пуска и S-входу четвертого триггера, а синхровход подключен к выходу восьмой ступени счетчика тактов, выход первой ступени которого подключен к R-входам со второго по четвертый триггеров и к синхровходам пятого и шестого триггеров, а инверсный и прямой выходы седьмой ступени которого являются соответственно восьмым и десятым выходами блока, второй и третий элемент И, выходы которых являются пятым и шестым выходами блока, первые входы которых -подключены к выходу второго триггера, а вторые входы подключены к восьмому и десятому выходам блока, четвертый-элемент И, входы которого подключены к выходам первого и пятого триггеров, а выход которого является восемнадцатым выходом блока, первый элемент ИЛИ, входами подключенный к выходу четвертого элемента И и выходу шестого триггера, пятый и шестой элементы И, первые входы которых подключены к выходу первого элемента ИЛИ, а вторые входы и выходы подключены соответственно к десятому и восьмому, седьмому и девятому выходам блока, седьмой элемент И, выход которого является девятнадцатым выходом блока, а первый и второй входы подключены к восемнадцатому выходу блока и инверсному выходу шестого триггера, второй элемент ИЛИ, выход которого подключен к R-входу восьмого триггера, а первый и второй входы подключены к инверсному выходу седьмого триггера и кнопке продолжения, восьмой элемент И, выход которого является одиннадцатым выходом блока, а первый и второй входы подключены к прямому и инверсному выходам третьего и восьмого триггеров, счетчик задания задержки, выход которого является двенадцатым выходом первого блока управления, вход управления начальной установки которого подключен к четвертому выходу блока, третий элемент ИЛИ, выход которого является пятнадцатым выходом блока, а входы подключены к второму и четвертому выходам переключателя положения окна, первый и четвертый выходы которого подключены к входам четвертого элемента ИЛИ, пятый элемент ИЛИ, входы которого подключены к третьему и четвертому входам переключателя положения окна, первый и четвертый выходы которого подключены к входам шестого элемента ИЛИ, выход которого является двадцатым выходом блока, первый и второй коммутаторы, первые и вторые входы которых подключены соответственно к инверсному и прямому выходам шестой ступени счетчика тактов, к выходам четвертого и пятого элементов ИЛИ, а выходы коммутаторов подключены к входам сложения и вычитания счетчика задания задержки, вход разрешения начальной установки которого подключен к четвертому выходу блока, третий и четвертый коммутаторы, выходы которых являются тринадцатым и четырнадцатым выходами блока, второй элемент НЕ, вход которого подключен к переключателю режима, девятый и десятый элементы И, первые входы которых подключены к входу второго элемента НЕ, а вторые входы подключены к первому входу переключателя положения окна и выходу шестого элемента ИЛИ, одиннадцатый и двенадцатый элементы И, выходы которых являются шестнадцатым и семнадцатым выходами блока, а первые входы подключены к третьему выходу блока, пятый и шестой коммутаторы, выходы которых являются двадцать первым и двадцать вторым выходами блока, управляющие входы которых подключены к десятому выходу блока, причем D-входы с первого по четвертый, седьмого и восьмого триггеров подключены к источнику логической единицы, разряды, начиная с младших, входа начальной установки счетчика задания задержки подключены соответственно к источнику логического нуля, выходу второго элемента НЕ и выходам девятого и десятого элементов И, одиннадцатый выход блока подключен ко входам разрешения выдачи первого и второго коммутаторов, выход первого элемента ИЛИ подключен ко входам разрешения выдачи третьего и четвертого коммутаторов, первые и вторые входы которых подключены соответственно к выходам шестой ступени счетчика тактов второго элемента НЕ, пятого и четвертого элементов ИЛИ, вход второго элемента НЕ подключен к управляющим входам с первого по четвертый коммутаторов, выход четвертого элемента ИЛИ подключен к вторым прямому и инверсному входам одиннадцатого и двенадцатого элементов И, первый и второй входы пятого коммутатора, второй и первый входы шестого коммутатора подключены к выходам второго триггера и первого элемента НЕ соответственно.

4. Устройство по п.1, 2, 3, отличающееся тем, что каждый блок управления памятью содержит коммутатор, первый, второй, и управляющий входы которого являются соответственно, первым, пятым и третьим входами блока, счетчик адреса, выход которого является выходом блока, вход установки в ноль которого подключен к выходу коммутатора, входы начальной установки и разрешения начальной установки являются четвертым и вторым входами блока, а вход сложения является шестым входом блока.

Текст

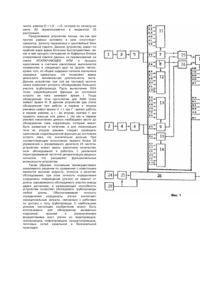

Изобретение относится к технике контроля трубопроводных систем и предназначено для определения мест повреждения в напорных трубопроводах. Наиболее близким по технической сущности к заявляемому является устройство для определения мест повреждения напорного трубопровода, содержащее датчики двух каналов, соединенные с усилителями, выходы которых подключены к входам формирователей импульсов, две пары буферных блоков оперативной памяти, информационные входы которых подключены к выходам первого и второго формирователей импульсов соответственно с первого по четвертый блоки управления памятью, выходы которых подключены к входам управления соответствующи х буферных блоков оперативной памяти два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первые входы которых соединены с выходами буферных блоков оперативной памяти первой пары, а вторые - с выходами буферных блоков оперативной памяти второй пары, коммутатор, входы которого подключены к выходам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блок формирования приращения, входом подключенный к выходу коммутатора, реверсивный счетчик накопления, вход которого подключен к выходу блока формирования приращения, накопительный блок оперативной памяти, цифроаналоговый преобразователь, индикатор, первый вход которого подключен к выходу цифроаналогового преобразователя, генератор тактовых импульсов, первый блок управления устройством, второй блок управления, первый выход которого подключен к адресному входу накопительного блока оперативной памяти, блок вычисления расстояния, который содержит перестраиваемый генератор, элемент И, первый вход которого соединен с выходом перестраиваемого генератора, первый счетчик задержки, выход которого подключен к второму входу индикатора, счетчик установки задержки, кнопку маркера, выход которой подключен к входу сче тчика установки задержки, индикатор расстояния до места утечки, счетчик расстояния, выход которого подключен к индикатору расстояния, блок переключателей установки расстояния между датчиками; группу сумматоров, входы которых подключены к блоку переключателей установки расстояния, а выходы подключены к входу начальной установки счетчика расстояния. Недостаток устройства заключается в его большой сложности и невысоком быстродействии, т.к. устройство содержит дополнительно два буферных регистра, блок оперативной памяти и блок управления этим устройством. Указанное устройство также имеет низкую точность локализации течи вследствие приближенного определения пика корреляционной функции и корреляционной задержки. В основу изобретения поставлена задача упростить устройство для определения мест повреждений напорного трубопровода, не снижая его технологических и функциональных возможностей, повысить быстродействие и точность путем обследования трубопровода в режимах с различным пространственновременным масштабом определения корреляционной функции между сигналами от датчиков. Указанная задача решается тем, что в устройство для определения мест повреждения трубопровода, содержащее датчики двух каналов, соединенные с усилителями, выходы которых подключены к входам формирователей импульсов, две пары буферных блоков оперативной памяти, информационные входы которых подключены к выходам первого и второго формирователей импульсов соответственно, с первого по четвертый блоки управления памятью, выходы которых подключены к входам управления соответствующи х буферных блоков оперативной памяти, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первые входы которых соединены с выходами буферных блоков оперативной памяти первой пары, а вторые соединены с выходами буферных блоков оперативной памяти второй пары, коммутатор, входы которого подключены к выходам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блок формирования приращения, входом подключенный к выходу коммутатора, реверсивный счетчик накопления, вход которого подключен к выходу блока формирования приращения, накопительный блок оперативной памяти, цифроаналоговый преобразователь, индикатор, первый вход которого подключен к выходу цифроаналогового преобразователя, генератор тактовых импульсов, первый блок управления устройством, второй блок управления, первый выход которого подключен к адресному входу накопительного блока оперативной памяти, блок вычисления расстояния, который содержит' перестраиваемый генератор, элемент И, первый вход которого соединен с выходом перестраиваемого генератора, первый счетчик задержки, выход которого подключен к второму входу индикатора, счетчик установки задержки, кнопку маркера, выход которой подключен к входу сче тчика установки задержки, индикатор расстояния до места утечки, счетчик расстояния, выход которого подключен к индикатору расстояния, блок переключателей установки, расстояния между датчиками, группу сумматоров, входы которых подключены к блоку переключателей установки расстояния, а выходы подключены к входу начальной установки счетчика расстояния, согласно изобретению введены управляемый делитель частоты, вход которого подключен к выходу генератора тактовых импульсов, а выход подключен к синхровходу блока управления устройством, переключатель режима, выход которого подключен к управляющему входу управляемого делителя частоты и первому бляху управления устройством, регистр результата, входом подключенный к выходу накопительного блока оперативной памяти и входу начальной установки реверсивного счетчика накопления, а выходом подключенный к входу аналого-цифрового преобразователя, второй счетчик задержки, вход начальной установки которого подключен к выходу счетчика установки задержки и входу начальной установки первого счетчика задержки, а выход подключен к второму входу элемента И, переключатель установки скорости, подключенный к управляющему входу перестраиваемого генератора, причем выход реверсивного счетчика накопления соединен с входом накопительного блока оперативной памяти, выход стробирующего сигнала второго блока управления подключен к синхровходу индикатора и входу разрешения начальной установки первого счетчика задержки, первый выход первого блока управления устройством подключен к первому управляющему входу блока формирования приращения, второй управляющий вход которого подключен к второму выходу первого блока управления устройством, третий выход которого подключен к синхровходу второго блока управления, вход начальной установки которого подключен к первым входам с первого по четвертый блоков управления памятью, входу управления индикатора расстояния и к четвертому выходу первого блока управления устройством, пятый и шестой выходы которого подключены соответственно к входам разрешения записи первых и вторых буферных блоков оперативной памяти первой и второй пары, седьмой и восьмой выходы первого блока управления устройством подключены к вторым и третьим входам первого и третьего блоков управления памятью, девятый и десятый выходы блока управления устройством подключены к вторым и третьим входам второго и четвертого блоков управления памятью соответственно, вход разрешения записи накопительного блока оперативной памяти подключен к входу переключения адреса второго блока управления и к одиннадцатому вы ходу первого блока управления устройством, двенадцатый выход которого подключен к четвертым входам блоков управления памятью, пятые входы первых двух из которых и пятые входы вторых двух подключены к тринадцатому и четырнадцатому входам первого блока управления устройством, пятнадцатый выход которого подключен к старшему разряду входа начальной установки второго счетчика задержки, вход разрешения начальной установки которого подключен к входу кнопки маркера, к управляющему входу коммутатора и к десятому выходу первого блока управления устройством, а шестнадцатый и семнадцатый выходы которого подключены соответственно к входам суммирования и вычитания первого счетчика задержки, восемнадцатый выход первого блока управления устройством подключен ко второму синхровходу второго блока управления и к входу управления начальной установкой реверсивного счетчика накопления, вход сброса которого подключен к девятнадцатому выходу первого блока управления устройством, двадцатый выход которого подключен к вычитающему входу второго счетчика задержки, шестые входы первых и вторых блоков управления памятью первой и второй пары входных блоков оперативной памяти подключены к двадцать первому й двадцать второму выходам первого блока управления устройством соответственно. Блок формирования приращения содержит первый и второй триггеры, D-входы которых подключены к выходу коммутатора, а инверсный выход первого триггера и вы ход второго триггера соединены соответственно с входами сложения и вычитания реверсивного счетчика накопления, причем первый управляющий вход блока подключен к синхровходам первого и второго триггеров, S-вход первого и R-вход второго из которых подключены к второму управляющему входу этого блока. Первый блок управления содержит кнопку пуска, кнопку продолжения, переключатель положения окна, четыре выхода которого соответствуют че тырем положениям окна просмотра участка трубопровода, счетчик тактов, имеющий восемь ступеней деления частоты, синхровход которого является синхровходом и вторым выходом блока, первый элемент НЕ, вход которого подключен к синхровходу, а вы ход является первым выходом блока, первый триггер, выход которого является третьим выходом блока, а синхровход и R-вход подключены к инверсному выходу третьей ступени и выходу второй ступени счетчика тактов, со второго по четвертый триггеры, синхровходы которых подключены соответственно к инверсным выходам с четвертой по шестую ступеней счетчика тактов, пятый и шестой триггеры, D-входы которых подключены соответственно к выходам третьего и четвертого триггеров, седьмой триггер, R-вход которого подключен к кнопке пуска и S-входу четвертого триггера, а синхровход подключен к выходу восьмой ступени счетчика тактов, выход первой ступени которого подключен к R-входам со второго по четвертый триггеров и к синхровходам пятого и шестого триггеров, а инверсный и прямой выходы седьмой ступени которого являются соответственно восьмым и десятым; выходами блока, второй и третий элементы И, выходы которых являются пятым и шестым выходами блока, первые входы которых подключены к выходу второго триггера, а вторые входы подключены к восьмому и десятому выходам блока, четвертый элемент И, входы которого является девятнадцатым выходом блока, а первый и второй входы подключены к восемнадцатому выходу блока и инверсному выходу шестого триггера, второй элемент ИЛИ, выход которого подключены к выходам первого и пятого триггеров, а выход которого является, восемнадцатым выходом блока, первый элемент ИЛИ, входами подключенный к выходу четвертого элемента И и выходу шестого триггера, пятый и шестой элементы И, первые входы которых подключены к выходу первого элемента ИЛИ, а вторые входы и выходы подключены соответственно к десятому и восьмому, седьмому и девятому выходам блока, седьмой элемент И, выход которого является девятнадцатым выходом блока, а первый и второй входы подключены к восемнадцатому выходу блока и инверсному выходу шестого триггера, второй элемент ИЛИ, выход которого подключен к R-входу восьмого триггера; а первый и второй входы подключены к инверсному выходу седьмого триггера и кнопке продолжения, восьмой элемент И, выход которого является одиннадцатым выходом блока, а первый и второй входы подключены к прямому и инверсному выходам третьего и восьмого триггеров, счетчик задания задержки, выход которого является двенадцатым выходом первого блока управления, вход управления начальной установки которого подключен к четвертому выходу блока, третий элемент ИЛИ, выход которого является пятнадцатым выходом блока, а входы подключены к второму и четвертому выходам переключателя положения окна, первый и четвертый выходы которого подключены к входам четвертого элемента ИЛИ, пятый элемент ИЛИ, входы которого подключены к третьему и четвертому входам переключателя положения окна, первый и четвертый выходы которого подключены к входам шестого элемента ИЛИ, выход которого является двадцатым выходом блока, второй и третий коммутаторы, первые и вторые входы которых подключены соответственно к инверсному и прямому выходам шестой ступени счетчика тактов, к выходам четвертого и пятого элементов ИЛИ, а выходы коммутаторов подключены к входам сложения и вычитания счетчика задания задержки, вход разрешения начальной установки которого подключен к четвертому выходу блока, третий и четвертый коммутаторы, выходы которых являются тринадцатым и четырнадцатым выходами блока, второй элемент НЕ, вход которого подключена переключателю режима, девятый и десятый элементы И, первые входы которых подключены к входу второго элемента НЕ, а вторые входы подключены к первому входу переключателя положения окна, и выходу шестого элемента ИЛИ, одиннадцатый и двенадцатый элементы И, выходы которых являются шестнадцатым и семнадцатым выходами блока, а первые входы подключены к третьему выходу блока, пятый и шестой коммутаторы, выходы которых являются двадцать первым и двадцать вторым выходами блока, управляющие входы которых подключены к десятому выходу блока, причем D-входы с первого по четвертый, седьмого и восьмого триггеров подключены к источнику логической единицы, разряды, начиная с младших, входа начальной установки счетчика задания задержки подключены соответственно к источнику логического нуля, выходу второго элемента НЕ, и выходам девятого и десятого элементов И, одиннадцатый выход блока подключен к входам разрешения выдачи первого и второго коммутаторов, вы ход первого элемента ИЛИ подключен к входам разрешения выдачи третьего и четвертого коммутаторов, первые и вторые входы которых подключены соответственно к выходам шестой ступени счетчика тактов, второго элемента НЕ, пятого и четвертого элементов ИЛИ, вход второго элемента НЕ подключен к управляющим входам с первого по четвертый коммутаторов вы ход четвертого элемента ИЛИ подключен к вторым прямому и инверсному входам одиннадцатого и двенадцатого элементов И, первый и второй входы пятого коммутатора, второй и первый входы шестого коммутатора подключены к выходам второго триггера и первого элемента НЕ соответственно. Каждый блок управления памятью содержит коммутатор, первый, второй и управляющий входы которого являются соответственно первым, пятым и третьим входами блока, счетчик адреса, выход которого является выходом блока, вход установки в ноль которого подключен к выходу коммутатора, входы начальной установки и разрешения начальной установки являются четвертым и вторым входами блока, а вход сложения является шестым входом блока. Совокупностью существенных признаков заявляемого устройства обеспечивается надежное и качественное выявление и определение местоположения утечки с высокой степенью достоверности. Предлагаемое устройство проще, т.к. в нем отсутствует сумматор, регистр перезаписи и дисплейный блок оперативной памяти. Это устройство имеет вдвое большее быстродействие, т.к. в нем процесс считывания из буферных блоков оперативной памяти данных, их перемножение на схеме ИСКЛЮЧАЮЩЕЕ ИЛИ и процесс накопления в счетчике накоплений выполняются независимо в следующи х друг за другом тактах. Это устройство при тактовой частоте позволяет ускорять, обследование большого участка трубопровода. Устройство имеет различное количество окон обследования и работает с различной перестраиваемой частотой дискретизации входных, сигналов, что расширяет функциональные возможности устройства. При этом при управляемом изменении коэффициента деления перестраиваемого делителя частоты изменяется частота дискретизации сигнала, а с ней и пространственно-временной масштаб определяемой корреляционной функции. На фиг.1, 2, 3 показаны структурные схемы устройства для определения мест повреждения напорного трубопровода, его блока формирования приращения и блока вычисления расстояния соответственно. Структурные схемы блоков управления устройством и управления памятью показаны на фиг.4, 5 и 6 соответственно, а на фиг.7 представлена временная диаграмма работы блока управления устройством. Устройство для определения мест повреждения напорного трубопровода содержит датчики двух каналов 1 и 2, соединенные с усилителями 3 и 4, выходы которых подключены к входам формирователей импульсов 5 и 6, две пары буферных блоков оперативной памяти 7 и 8, 9 и 10 информационные входы которых подключены к выходам первого и второго формирователей импульсов 5, 6 с первого по четвертый блока управления памятью 11 - 14, выходы которых подключены к входам управления соответствующи х буферных блоков оперативной памяти 7 - 10, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15 и 16, первые входы которых соединены с выходами буферных блоков оперативной памяти пары 7 и 8, а вторые соединены с выходами буферных блоков оперативной памяти второй пары 9 и 10, коммутатор 17, входы которого подключены к выходам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 15 и 16, блок формирования приращения 18, входом подключенный к выходу коммутатора 17, реверсивный счетчик накопления 19, вход которого подключен к выходу блока формирования приращения 18, накопительный блок оперативной памяти 20, регистр результата 21, цифроаналоговый преобразователь 22, индикатор 23, первый вход которого подключен к выходу цифроаналогового преобразователя 22, генератор тактовых импульсов 24, управляемый делитель частоты 25, первый блок управления 26 устройством, блок вычисления расстояния 27, переключатель режима 28, второй блок управления 29 выходом подключенный к адресному входу накопительного блока оперативной памяти 20. Вход управляемого делителя частоты 25, подключен к выходу генератора тактовых импульсов 24, а выход подключен к синхровходу первого блока управления 26 устройством, выход переключателя режима 28 подключен к управляющему входу управляемого делителя частоты 25 и первому блоку управления 26 устройством. Выход реверсивного счетчика накопления 19 соединен с входом накопительного блока оперативной памяти 20, а регистр результата 21 подключен к выходу накопительного блока оперативной памяти 20 и входу начальной установки реверсивного счетчика накопления 19, а выходом подключен к входу аналого-цифрового преобразователя 22. Блок формирования приращения 18 содержит первый и второй триггеры 30, 31, D-входы которых подключены к выходу коммутатора 17, а инверсный выход первого триггера и выход второго триггера соединены соответственно с входами сложения и вычитания реверсивного счетчика накопления 19, причем первый управляющий вход блока подключен к синхровходам первого и второго триггеров 30, 31, S-вход триггера 30 и R-вход триггера 31 подключены к второму управляющему входу блока 18. Блок вычисления расстояния 27 содержит блок переключателей установки расстояния между датчиками 32, группу сумматоров 33, входы которых подключены к блоку переключателей установки расстояния 32, счетчик расстояния 34, индикатор расстояния до места утечки 35, переключатель установки скорости 36, перестраиваемый генератор 37, элемент И 38, первый вход которого соединен с выходом перестраиваемого генератора 37, кнопку маркера 39, счетчик установки задержки 40, второй счетчик задержки 4 І, первый счетчик задержки 42, выход которого подключен к второму входу индикатора 23. Выходы группы сумматоров 33 подключены к входу начальной установки счетчика расстояния 34, выход счетчика расстояния 34 подключен к индикатору расстояния 35, выход кнопки маркера 39 подключен к входу счетчика установки задержки 40, вход начальной установки второго счетчика задержки 41 подключен к выходу счетчика установки задержки 40 и входу начальной установки первого счетчика задержки 41, а выход подключен к второму входу элемента И 38, выход переключателя установки скорости 36 подключен к управляющему входу перестраиваемого генератора 37. Первый блок управления 26 устройством содержит кнопку пуска 43, кнопку продолжения 44, переключатель положения окна 45, четыре выхода которого соответствуют четырем положениям окна просмотра участка трубопровода, счетчик тактов 46, первый триггер 47, с второго по четвертый триггеры 48-50, синхровходы которых подключены соответственно к инверсным выходам с четвертой по шестую ступеней счетчика тактов 46, пятый и шестой триггеры 51, 52, D-входы которых подключены соответственно к выходам третьего 49 и четвертого триггеров 50, седьмой триггер 53, R-вход которого подключен к кнопке пуска 43, и к S-вход че твертого триггера 50, а синхровход подключен к выходу восьмой ступени счетчика тактов 46, выход первой ступени которого подключен к R-входам с второго по четвертый триггеров 48, 49 и 50 и к синхровходам пятого 51 и шестого 52 триггеров восьмой триггер 54, второй 55 и третий 56 элементы И, первые входы которых подключены к выходу второго триггера 48, четвертый элемент И 57, входы которого подключены к выходам первого 47 и пятого 51 триггеров, с пятого по двенадцатый элементы И 58 - 65 первый элемент ИЛИ 66, входами подключенный к выходу четвертого элемента И 57 и выходу шестого триггера 52, второй элемент ИЛИ 67, выход которого подключен к R-входу восьмого триггера 54, а первый и второй входы подключены к инверсному выходу седьмого триггера 53 и кнопке продолжения 44, с третьего по шестой элементы ИЛИ 68 - 71, первый и второй коммутаторы 72, 73, первые и вторые входы которых подключены соответственно к инверсному и прямому выходам шестой ступени счетчика тактов 46, к выходам четвертого и питого элементов ИЛИ 69, 70 третий и четвертый коммутаторы 74, 75, первый и второй элементы НЕ 76, 77, счетчик задания задержки 78, с первого по двадцать второй выходы 79, ..., 100, которые являются одноименными шинами управления устройства, пятый 101 и шестой 102 коммутаторы, выходы которых являются двадцать первым 99 и двадцать вторым 100 выходами первого блока управления. Синхровход сче тчика тактов 46 является синхровходом и вторым выходом 80 первого блока управления 26, вход элемента НЕ 76 подключен к синхровходу блока 26, а выход является первым выходом 79 первого блока управления 26. Выход первого триггера 47 является третьим выходом 81 блока 26, а синхровход и R-вход подключены к инверсному выходу третьей ступени и выходу второй ступени счетчика тактов 46. Инверсный и прямой выходы седьмой ступени счетчика тактов 46 является соответственно восьмым 86 и десятым 88 выходами первого блока управления 26. Выходы второго 55 и третьего 56 элементов И являются пятым 83 и шестым 84 выходами блока 26, а вторые входы второго и третьего элементов И 55, 56 подключены к восьмому 86 и десятому 88 выходам блока управления 26. Выход четвертого элемента И 57 является восемнадцатым 96 выходом первого блока управления 26. Первые входы пятого 58 и шестого 59 элементов И подключены к выходу первого элемента ИЛИ 66, а вторые входы и вы ходы подключены соответственно к десятому 88 и восьмому 86, седьмому 85 и девятому 87 вы ходам блока управления 26. Выход седьмого элемента И 60 является девятнадцатым выходом 97 блока 26, а его первый и. второй выходы подключены к восемнадцатому вы ходу 96 блока 26 и к инверсному выходу шестого триггера 53. Выход восьмого элемента И 61 является одиннадцатым выходом 89 блока 26, а первый и второй входы подключены к прямому и инверсному выходам третьего 48 и восьмого 54 триггеров. Выход счетчика задания задержки 78 является двенадцатым выходом 90 первого блока 26, а его вход управления начальной установки подключен к четвертому вы ходу 82 первого блока управления 26. Выход третьего элемента ИЛИ 68 является пятнадцатым выходом 93 блока 26, а его входы. подключены к второму и четвертому вы ходам переключателя положения окна 45, первый и четвертый выходы которого подключены к входам четвертого элемента ИЛИ 69. Входы пятого элемента ИЛИ 70 подключены к третьему и четвертому входам переключателя положения окна 45, первый и четвертый выходы которого подключены к входам шестого элемента ИЛИ 71, выход которого является двадцатым выходом 98 первого блока управления 26. Выходы первого и второго коммутаторов 72, 73 подключены к входам сложения и вычитания счетчика задания задержки 78, вход разрешения начальной установки которого подключен к четвертому выходу 82 первого блока управления 26. Выходы третьего и четвертого коммутаторов 74, 75 являются тринадцатыми 91 и четырнадцатым 92 выходами первого блока управления 26. Вход второго элемента НЕ 77 подключен к переключателю режима 28. Первые входы девятого и десятого элементов И 62, 63 подключены к входу второго элемента НЕ 77, а вторые входы подключены к первому входу переключателя положения окна 45 и выходу шестого элемента ИЛИ 71. Выходы одиннадцатого и двенадцатого элементов И 64, 65 являются шестнадцатым 94 и семнадцатым 95 выходами блока 26, а их первые входы подключены к третьему выходу 81 блока управления 26. D-входы с первого по четвертый 47, ..., 50, седьмого 53 и восьмого 54 триггеров подключен к источнику логической единицы. Разряды, начиная с младших, входа начальной установки счетчика задания задержки 78 подключены соответственно к источнику логического нуля, выходу второго элемента НЕ 77 и выходам девятого и десятого элемента И 62, 63, Одиннадцатый выход 89 блока 26 подключен к входам разрешения выдачи первого и второго коммутатора 72, 73, вы ход первого элемента ИЛИ 66 подключен к входам разрешения выдачи третьего и четвертого коммутаторов 74, 75, первые и вторые входы которых подключены соответственно к выходам шестой ступени счетчика тактов 46, второго элемента НЕ 77, пятого 71 и третьего 68 элементов ИЛИ. Вход второго элемента НЕ подключен к управляющим входам с первого по четвертый коммутатор 72 - 75, выход третьего элемента ИЛИ 68 подключен к вторым прямому и инверсному входам одиннадцатого и двенадцатого элементов И 64, 65. Выход стробирующего сигнала второго блока управления 29 подключен к синхровходу индикатора 23 и входу разрешения начальной установки первого счетчика задержки 42, первый выход 79 первого блока управления 26 устройством подключен к первому управляющему входу блока формирования приращения 18, второй управляющий вход которого подключен к второму выходу 80 блока управления 26 устройством, третий выход 81 которого подключен к синхровходу второго блока управления 29, вход начальной установки которой подключен к первым входам с первого по четвертый блоков управления памятью 11 - 14, входу управления индикатора расстояния 35 и к четвертому выходу 82 первого блока управления устройством 26, пятый 83 и шестой 84 выходы которого подключены соответственно к входам разрешения записи первых 7, 9 и вторых 8, 10 буферных блоков оперативной памяти первой и второй пары, седьмой 85 и 86 восьмой выходы первого блока 26 управления устройством подключены к вторым и третьим входам первого 11 и третьего 13 блоков управления памятью, девятый 87 и десятый 88 выходы первого блока 26 управления устройством подключены к вторым и третьим входам второго 12 и четвертого 14 блоков управления памятью соответственно, вход разрешения записи накопительного блока оперативной памяти 30 подключен к одиннадцатому выходу 89 блока 26 управления устройством, двенадцатый 90 выход которого подключен к четвертым входам блоков управленияпамятью 11 - 14, пятые входы первых двух из которых 11, 12 и пятые входы вторых двух из которых 13, 14 подключены к тринадцатому 91 и четырнадцатому 92 входам блока управления устройством, пятнадцатый выход 93 которого подключен к старшему разряду входа начальной установки второго счетчика задержки 41, вход разрешения начальной установки которого подключен к входу кнопки маркера, к управляющему входу коммутатора и к десятому выходу 88 первого блока 26 управления устройством, шестнадцатый 94 и семнадцатый 95 выходы которого подключены соответственно к входам суммирования и вычитания первого счетчика задержки 42. Восемнадцатый выход 96 первого блока 26 управления устройством подключен к входу управления начальной установкой реверсивного счетчика накопления 19, вход сброса которого подключен к девятнадцатому выходу 97 первого блока 26 управления устройством, двадцатый выход 98 которого подключен к вычитающему входу второго счетчика задержки. Двадцать первый 101 и двадцать второй 102 выходы блока управления подключены к шестым входам блоков управления памятью 11, 13 и 12, 14 соответственно. Каждый блок управления памятью 11 - 14 содержит коммутатор 103, первый, второй и управляющие входы которого являются соответственно первым, пятым и третьим входами блока, счетчик адреса 104, выход которого является выходом блока. Вход установки в ноль счетчика адреса 104 подключен к выходу коммутатора 103, а входы начальной установки, разрешения начальной установки и сложения являются четвертым, вторым и шестым входами блока управления памятью. Второй блок управления 29 выполнен в виде счетчика адреса считывания, выход переполнения которого является выходом стробирующего сигнала второго блока управления 29 и счетчика адреса записи, адреса из которых выдаются через коммутатор на адресный вход накопительного блока оперативной памяти 20. При этом начальная установка счетчиков производится сигналом на шине 82, приращения счетчиков адреса считывания и записи выполняется по сигналам на шине 81 и на шине 96 соответственно, при единичном состоянии шины 89 второй блок управления выдает адрес записи, а иначе - адрес считывания. Устройство работает следующим образом. Ме ханические колебания трубопровода, вызванные утечкой продуктов из трубопровода в месте повреждения, с помощью датчиков 1, 2, установленных с двух сторон от места утечки, преобразуются в электрические сигналы. После усиления сигналов усилителями 3 и 4 и преобразования формирователями импульсов 5 и 6 в двоичную последовательность они поступают на входы буферных блоков оперативной памяти 7 10. Устройство при конкретной его реализации выполняет вычисление корреляционной функции между сигналами от датчиков в 1024 точках. При этом с выходов с первой по восьмую ступеней счетчика тактов 46 выдается сигнал с частотой сигнала f0, поступающего на его синхровход с управляемого делителя частоты 25, деленной соответственно на 2, 4, 16, 128, 512, 219, 220, 221. На младшие девять разрядов счетчика 78 задания задержки подается логический 0, а на десятый, одиннадцатый и двенадцатый разряды соответственно сигналы с выходов элементов НЕ 77, И 62 и 63. Все счетчики и триггеры устройства меняют свое состояние по фронту сигналов на своих синхровхода х. Вначале устройство устанавливается переключателем режима 28 в первый режим (на выходе переключателя 28 логический 0), в котором выполняется обзорное обследование участка трубопровода. При этом управляемый делитель 25 частоты выполняет деление частоты генератора 24 тактовых импульсов на 4. После нажатия кнопки 43 пуска счетчик 46 тактов и седьмой триггер 53 устанавливается в ноль, а четвертый триггер 50 устанавливается в единицу. Сигнал с триггера 50 по шине 82 устанавливает в ноль счетчик второго блока управления 29, а также пройдя через первые входы коммутаторов 103 устанавливает в ноль счетчики адреса 104 блоков управления памятью 11 и 13. Через такт, после установки в 0 счетчика 46 тактов, устанавливается в 0 триггер 50 и начинается цикл записи исходных данных в буферные блоки оперативной памяти 7 и 9. При этом на входы разрешения записи буферных блоков оперативной памяти 7 и 9 поступают импульсы записи с шины 83 с частотой f0/128 и длительностью 1'/f0 (фиг.7), которая является частотой дискретизации входных сигналов. Буферные блоки оперативной памяти 7 и 9 получают со счетчиков 104 адреса блоков 11 и 13 адреса записи и после записи в них очередной пары данных Xi и Yi (i = 1', ..., 4095) эти счетчики 104 увеличивают свое содержимое на 1' при поступлении сигнала по шине 99. После записи 4096 данных сигнал на шине 86 устанавливается в 0, а на шине 88 - в 1' и начинается цикл записи данных в др угую пару блоков оперативной памяти 8 и 10. При этом вначале устанавливаются в 0 счетчики 104 блоков управления памятью 12, 14 импульсом с триггера 50 и далее импульсы записи и увеличения на 1 счетчиков 104 блоков управления памятью 12, 14 поступают с шин 84 и 100 соответственно. В это же время выполняется цикл обработки данных, считываемых с буферных блоков оперативной памяти 7 и 9. При этом в нулевом такте цикла обработки по сигналу на шине 82 и счетчик 78 задания задержки записывается число 512, как начальный адрес считывания одного из каналов, а также устанавливается в ноль второй блок управления 29. В следующем такте содержимое счетчика 78 переписывается в счетчик 104 адреса блока 11 управления памятью по сигналу на шине 85, а счетчик 104 блока 13 устанавливается в 0 по сигналу на шине 92, который формируется коммутатором 75 по сигналу разрешения с выхода элемента ИЛИ 66. В этом же такте устанавливаются в 1 триггеры 47, 49. В следующем такте с буферных блоков оперативной памяти. 7 и 9 по адресам 512 и 0 считываются битовые операнды X512 и Y0, которые складываются по модулю 2 на схеме ИСКЛЮЧАЮЩЕЕ ИЛИ 15 и таким образом сформированное их арифметическое произведение Z0 = X512 Y0, пройдя через первый вход коммутатора 17, записывается в первый и второй триггеры 30, 31 и по сигналу на шине 79. Так как триггер 53 установлен в 1, и на выходе элемента И сформировался импульс, поскольку единица из триггера 49 переписывается в триггер 51, то схема И 60 выдает импульс в шин у 97, который устанавливает в 0 счетчик 19 накопления. В конце этого такта увеличивается на 1 содержимое счетчиков адреса 104 блоков 11, 13 по сигналу на шине 99. В следующем такте если операнд Z0 = 0 (то есть X512 = Y0), триггер 30 выдает импульс сложения с +1 (положительное приращение) на вход счетчика 19 накопления, а если Z0 = 1 (X512 ¹ Y0), то триггер 31 выдает импульс сложения с -1 (отрицательное приращение) на счетчик 19 накоплений, то есть операнд Z0, как приращение алгебраические складывается с содержимым счетчика 19. В этом же такте из буферных блоков оперативной памяти 7 и 9 считываются следующие операнды X513 и Y1, произведение которых Z1 = X513 Y1 фиксируется в триггерах 30, 31. Далее работа устройства продолжается аналогично. В i - м такте произведение Zi - 1 прибавляется к содержимому счетчика 19 накопления, операнды X512 + i и Y0, считываются из буферных блоков оперативной памяти 7 и 9 и произведение Zi = X512 + i Yi записывается в триггеры 30, 31, а содержимое счетчиков адреса 104 блоков 11,13 увеличивается на 1 и становится равным 512 + i + 1 и i + 1. Через 512 тактов после начала цикла обработки триггер 49 на 1 такт устанавливается в 1 и сформированный таким образом импульс через элемент И 61 поступает на шину 89, как сигнал разрешения записи в накопительный блок оперативной памяти 20 и оценка корреляционной функции в точке, соответствующей задержке - 512 тактов периода дискретизации, как сумма приращений, записывается в нулевую ячейку блока оперативной памяти 20. В это же время из содержимого счетчика 78 задания задержки вычитается 1 и оно становится 511. В следующем такте начальный адрес 511 переписывается из счетчика 78 в счетчик адреса 104 блока 11 управления памятью по сигналу на шине 85, а счетчик 104 блока 13 и счетчик 19 накопления устанавливаются в 0 и начинается новый цикл вычисления оценки корреляции в следующей точке R - 511. Аналогично вычисляются оценки корреляции R - j в точках j = 511, ..., 1. При этом начальный адрес, в счетчике 78 меняется от 511 до 1, из буферных блоков оперативной памяти 7 и 9 считываются операнды Xi+j и Yi и произведение Zi = Xi + j Yi записывается в триггеры 30, 31, а в конце цикла в 512 - j - ю ячейку накопительного блока оперативной памяти 20 записывается результат R j. После этого вычисляются оценки корреляции Rj в точках j = 0, ..., 511. При этом вначале каждого цикла начальный адрес в счетчике 78 меняется от 0 до 511, этот адрес переписывается из счетчика 78 в счетчик адреса 104 блока 13 управления памятью по сигналу на шине 87, а счетчик 104 блока 11 устанавливается в 0. Далее из буферных блоков оперативной памяти 7 и 9 в каждом такте считываются операнды Xi и Yi+j и произведение Z = Xi × Yi+j записывается в триггеры 30, 31, а в конце цикла в j + 512 - ю ячейку накопительного блока оперативной памяти 20 записывается результат Rj. В конце первого цикла обработки, под действием сигнала на выходе восьмой ступени счетчика 46 тактов, то есть через 220 тактов после начала цикла, триггеры 53 и 54 устанавливаются в 1, сигнал записи в накопительный блок оперативной памяти 20 в шине 89 запрещается и устройство считается остановленным. Одновременно с записью исходных данных в буферные блоки оперативной памяти 7 - 10 и их обработкой, или когда устройство остановлено, выполняется отображение вычисляемых результатов Rj на экране индикатора 23. При этом каждые 16 тактов из накопительного блока оперативной памяти 20 считывается по адресу 0, ..., 1023 из второго блока управления 29 результат Rj (j = -512, ..., 511), который записывается в регистр результата 21 по сигналу на шине 81 и после преобразования в аналого-цифровом преобразователе 22 поступает в индикатор 23 для отображения. Индикатор синхронизируется сигналом переполнения счетчика адреса считывания второго блока управления, адрес в котором увеличивается по сигналу на шине 81. Если после одного цикла обработки пик корреляционной функции, который соответствуе т местоположению течи не обнаружен, то после нажатия кнопки 44 продолжения начинается процесс уточнения оценок корреляционной функции Rj в точках j = -512, ..., 511. При этом триггер 53 устанавливается в 1, а триггер 54 - в 0 и процесс вычисления повторяется аналогично, как в первом цикле вычислений. Однако при этом запрещается установка в ноль-счетчика 19 накоплений сигналом на шине 97 и вместо нее в том же такте выполняется считывание результата Rj из накопительного блока оперативной памяти 20 и запись его в счетчик 19, как его начальное состояние. При этом в конце цикла вычисления оценки в ту же ячейку накопительного. блока оперативной памяти 20 записывается новое уточненное значение Очередной цикл вычислений выполняется одновременно с реализацией цикла записи исходных данных для нового цикла вычислений и в то же время, когда в буферные блоки оперативной памяти 7, 9 записываются исходные данные по адресу, выдаваемому блоками 11, 13 из буферных блоков оперативной памяти 8, 10 считываются данные на обработку по адресам из блоков 12, 14 и поступают на схему ИСКЛЮЧАЮЩЕЕ ИЛИ 16. В конце цикла буферные блоки оперативной памяти 7, 9 и 8, 10, блоки 11, 13 и 12, 14 и схемы 15 и 16 меняются ролями. Процесс вычислений продолжается при нажатой кнопке 44 продолжения, пока не будет обнаружен пик корреляции на экране индикатора 23. При этом фиксируют номер, четверти участка экрана индикатора (номер окна от 1 до 4) в котором обнаружен корреляционный пик и переключателем 28 переводят устройство во второй режим - режим лупы, в котором уточняют положение корреляционного пика, а на переключателе 45 положения окна устанавливают номер окна обследования. Работа устройства во втором режиме аналогична работе в первом режиме за исключением следующи х особенностей. Управляемый делитель частоты 25 пропускает сигнал с генератора тактовых импульсов 24 без изменений. Таким образом, тактовая частота f0 блока 26 управления, а с ней и частота дискретизации входных сигналов оказываются вчетверо выше, чем в первом режиме и тем самым временной масштаб вычисляемой корреляционной функции оказывается вчетверо более крупным. В зависимости от заданного переключателем 44 окно просмотра изменяется начальное значение счетчика 78 установки задержки и знак его приращения, а также номер блока управления памятью, в которой записывается начальное значение адреса из счетчика 78. При исследовании первого окна просмотра исходное состояние счетчика 78 равно 2048 и к нему прибавляется -1, ненулевой, начальный адрес пересылается в блок 11 или 12, а устройство вычисляет корреляционную функцию Rj для j = -2048, ..., 1025. При исследовании второго окна просмотра исходное состояние счетчика 78 равно 1024 и к нему прибавляется -1, ненулевой начальный адрес пересылается в блок 11 или 12, а устройство вычисляет корреляционную функцию Rj для j = 1024, ..., -1. При исследовании третьего окна просмотра исходное состояние счетчика 78 равно 0 и к нему прибавляется +1, ненулевой начальный адрес пересылается в блок 13 или 14, а устройство вычисляет корреляционную функцию Rj для j = 0, ..., 1023. И наконец, при исследовании четвертого окна просмотра исходное состояние счетчика 78 равно 1023 и к нему прибавляется +1, ненулевой начальный адрес пересылается в блок 13 или 14, а устройство вычисляет корреляционную функцию R для j = 1024, ..., 2047. После обнаружения корреляционного пика в одном из окон просмотра выполняется вычисление расстояния до места течи с помощью блока вычисления расстояния 27. Переключателем установки расстояния 32 устанавливается расстояние L между датчиками, переключателем установки скорости 36 устанавливается скорость звука n в трубопроводе. При нажатии на кнопку 39 маркера импульса с шины 86 поступают на вход счетчика 40 установки задержки, в котором устанавливается код t = 0, ..., 1023, соответствующий положению курсора. По стробирующему импульсу, пришедшему из второго блока управления 29, этот код переписывается в первый счетчик 42 задержки, а по импульсу на шине 88 - во второй счетчик 41 задержки. В последнем случае, если обследование ведется в первом или четвертом окне к коду t прибавляется смещение 1024 - как единица в старшем разряде счетчика 41, поступившая по шине 98. Если установлено первое или второе окно, то к содержимому счетчика 42 прибавляется +1, а иначе - -1 и при переполнении счетчика 42 он выдает на второй вход индикатора 23 импульс маркера. Таким образом, регулируя с помощью кнопки 39 состояние t счетчика 40, равное числу временных отсчетов от края окна, ближайшего к середине обследуемого участка трубы, устанавливается курсор на экране индикатора 23 в месте пика корреляционной функции, а в счетчике 41 оказывается код, равный искомой задержке t = 0, ..., 2047. По сигналу на шине 86 в счетчик расстояния записывается код 1/2, полученный делением пополам кода переключателя 32 с помощью группы сумматоров 33. Перестраиваемый генератор 37 выдает последовательность импульсов с частотой, равной скорости звука, деленной пополам n/2. Импульсами на шине 93 из содержимого t счетчика 41 вычитаются 1 и на его выходе присутствует логическая 1, пока он не установится в ноль. Таким образом, на выходе счетчика 41 вырабатывается импульс длительностью, пропорциональной t и схема И 38 выдает на счетный вход счетчика 34 количество импульсов, равное n t/2, которое вычитается из содержимого счетчика 34. В конце вычислений в счетчике 34 оказывается искомое число, равное D = L/2 - nt/2, которое по сигналу на шине 82 переписывается в индикатор 35 расстояния. Предлагаемое устройство проще, так как при прочих равных условиях в нем отсутствуе т сумматор, регистр перезаписи и дисплейный блок оперативной памяти. Данное устройство имеет по крайней мере вдвое большее быстродействие, гак как в нем процесс считывания из буферных блоков оперативной памяти данных, их перемножения на схеме ИСКЛЮЧАЮЩЕЕ ИЛИ и процесс накопления в счетчике накоплений выполняется независимо в следующи х друг за другом тактах, кроме того, из общей задержки сигнала исключена задержка сумматора, что позволяет вдвое уменьшить минимальную длительность такта. Данное устройство при той же тактовой частоте также позволяет ускорить обследование большого участка тр убопровода. Пусть вычисление 1024 точек корреляционной функции до состояния острого ее пика занимает время t. Тогда обнаружение течи прототипом для 4096 точек займет время 4t. В данном устройстве два этапа обнаружения при работе в первом и втором режимах займут время t1 + t, где t' - время работы в первом режиме, a t - во втором, причем t', как правило, меньше или равно t, так как в первом режиме накопление данных необходимо вести до обнаружения пика корреляции, который может быть размытым и нечетким, а для локализации течи во втором режиме следует проводить накопление корреляционной функции до состояния острого пика, что значительно дольше. При соответствующем исполнении первого блока 26 управления и управляемого делителя 25 частоты устройство может иметь различное количество окон обследования и работать с различной перестраиваемой частотой дискретизации входных сигналов, что расширяет функциональные возможности устройства. Таким образом, основными преимуществами заявляемого решения по сравнению с известными являются высокая скорость, точность и качество обследования, при этом точность определения координаты повреждения (утечки) не зависит от длины одновременно обследуемого участка между двумя датчиками, а разрешающая способность устройства позволяет обследовать трубопроводы любой длины. Обеспечиваемая точность определения координаты утечки исключает нерациональные затраты, связанные с работами по доступу к телу трубопровода. С наибольшим успехом настоящее изобретение может быть использовано для обнаружения вызванных коррозией, эрозией и механическими воздействиями мест утечки из водопроводов, газопроводов, нефтепроводов, продуктопроводов, тепловых сетей канальной и бесканальной прокладки.

ДивитисяДодаткова інформація

Автори англійськоюAstafiev Volodymyr Oleksandrovych

Автори російськоюАстафьев Владимир Александрович

МПК / Мітки

МПК: G06F 15/00, F17D 5/06

Мітки: пошкодження, пристрій, трубопроводу, місць, напірного, визначення

Код посилання

<a href="https://ua.patents.su/10-26228-pristrijj-dlya-viznachennya-misc-poshkodzhennya-napirnogo-truboprovodu.html" target="_blank" rel="follow" title="База патентів України">Пристрій для визначення місць пошкодження напірного трубопроводу</a>

Попередній патент: Інгалятор для спільного використання з лікувальним блоком і лікувальний блок

Наступний патент: Пружний елемент тензодинамометра

Випадковий патент: Молольне тіло