Система обробки сигналів приймальної цифрової антенної решітки

Номер патенту: 47675

Опубліковано: 25.02.2010

Автори: Слюсар Вадим Іванович, Нікітін Микола Михайлович, Шацман Леонід Георгієвич, Бондаренко Максим Васильович, Малащук Володимир Петрович, Гриценко Віктор Миколайович, Волощук Ігор Вікторович

Формула / Реферат

1. Система обробки сигналів приймальної цифрової антенної решітки, до складу якої входять багатоканальні цифрові приймальні модулі (БЦПМ), об'єднавчий модуль, синхронізатор, процесорний модуль, перша об'єднавча (крос) плата, причому вихідна шина об'єднавчого модуля через рознім першої об'єднавчої (крос) плати підключені до шини даних процесорного модуля, тактові виходи синхронізатора підключені до тактових входів модулів БЦПМ та об'єднавчого модуля, виходи БЦПМ підключені до сигнальних входів об'єднавчого модуля, вихідна шина об'єднавчого модуля через рознім першої об'єднавчої (крос) плати підключені до шини даних процесорного модуля, яка відрізняється тим, що до складу системи обробки сигналів приймальної цифрової антенної решітки додатково введено другу об'єднавчу (крос) плату, при цьому вхідна шина команд управління синхронізатора через перші розніми другої об'єднавчої (кроc) плати підключена до відповідної шини об'єднавчого модуля, тактові виходи синхронізатора підключені до тактових входів БЦПМ та об'єднавчого модуля через другі розніми другої об'єднавчої (крос) плати, виходи БЦПМ підключені через треті розніми другої об'єднавчої (крос) плати до сигнальних входів об'єднавчого модуля (до складу якого входять сигнальні входи, вхід зовнішньої синхронізації, внутрішній тактовий генератор, комутатор тактових сигналів (з внутрішнього тактового генератора та входу зовнішньої синхронізації), модулі оперативної пам'яті, постійний запам'ятовуючий пристрій, інтерфейсна шина, програмована логічна інтегральна схема (ПЛІС), в якій містяться приймачі-передавачі інтерфейсів Rocket I/O, модуль перетворення послідовного коду у паралельний, модуль комутації сигналів, цифровий буфер, контролер передачі даних на інтерфейсну шину, модуль управління пам'яттю, модуль формування сигналів синхронізації та управління, модуль цифрової обробки сигналів, що містить модуль цифрового діаграмоутворення, модуль вилучення відгуків активних завад, модуль синтезу частотних фільтрів, модуль формування квадратів або абсолютних значень напруг для виявлення сигналів, модуль цифрового діаграмоутворення виконаний у вигляді послідовно з'єднаних модуля завершення цифрового діаграмоутворення за першою з кутових координат та модуля цифрового діаграмоутворення за другою з кутових координат, при цьому вхід зовнішньої синхронізації та вихід внутрішнього тактового генератора підключені до відповідних входів комутатора тактових сигналів, шини даних модулів оперативної пам'яті підключені через модуль управління пам'яттю (входить до складу ПЛІС) до відповідних входів контролера передачі даних на інтерфейсну шину, а шини адресації та управління модулів оперативної пам'яті підключені до відповідних виходів модуля управління пам'яттю (входить до складу ПЛІС), постійний запам'ятовуючий пристрій підключений до входів завантаження архітектури ПЛІС, сигнальні входи підключені до відповідних входів приймачів-передавачів інтерфейсів Rocket I/O (входять до складу ПЛІС), виходи яких підключені до відповідних входів модуля перетворення послідовного коду у паралельний (входить до складу ПЛІС), виходи модуля перетворення послідовного коду у паралельний (входить до складу ПЛІС) підключені до першої групи входів модуля комутації сигналів, а також до першої групи входів модуля завершення цифрового діаграмоутворення за першою з кутових координат, виходи якого підключені до першої групи входів модуля цифрового діаграмоутворення за другою з кутових координат, виходи якого підключені до першої групи входів модуля вилучення відгуків активних завад, виходи якого підключені до першої групи входів модуля синтезу частотних фільтрів, виходи якого підключені до першої групи входів модуля формування квадратів або абсолютних значень напруг для виявлення сигналів, входи цифрового буфера підключені до відповідних виходів контролера передачі даних на інтерфейсну шину, а виходи - до другої групи входів модуля комутації сигналів, третій вхід якого підключений до першого виходу (виходу переключення режимів "Вибір режиму") модуля формування сигналів синхронізації та управління, виходи контролера передачі даних на інтерфейсну шину підключені до інтерфейсної шини пристрою, тактові входи модуля перетворення послідовного коду у паралельний, а також модуля цифрового діаграмоутворення, перші входи управління модуля управління пам'яттю підключені до другого виходу модуля формування сигналів синхронізації та управління (входить до складу ПЛІС), тактовий вхід модуля формування сигналів синхронізації та управління підключений до виходу комутатора тактових сигналів, входи управління модуля формування сигналів синхронізації та управління підключені до другої групи виходів контролера передачі даних на інтерфейсну шину, тактові входи приймачів-передавачів інтерфейсів Rocket I/O і контролера передачі даних на інтерфейсну шину підключені до другого виходу модуля формування сигналів синхронізації та управління (входить до складу ПЛІС), до якого також підключені об'єднані тактові входи модуля вилучення відгуків активних завад, модуля синтезу частотних фільтрів, модуля формування квадратів або абсолютних значень напруг для виявлення сигналів, тактовий вхід модуля цифрового діаграмоутворення утворений об'єднаними тактовими входами модуля завершення цифрового діаграмоутворення за першою з кутових координат та модуля цифрового діаграмоутворення за другою з кутових координат, друга група входів модуля вилучення відгуків активних завад підключена до третьої групи виходів модуля формування сигналів синхронізації та управління, другі входи модуля завершення цифрового діаграмоутворення за першою з кутових координат, модуля цифрового діаграмоутворення за другою з кутових координат, модуля синтезу частотних фільтрів та модуля формування квадратів або абсолютних значень напруг для виявлення сигналів підключені відповідно до четвертого, п'ятого, шостого та сьомого виходів модуля формування сигналів синхронізації та управління.

2. Система обробки сигналів приймальної цифрової антенної решітки за п. 1, яка відрізняється тим, що до складу багатоканального цифрового приймального модуля (БЦПМ) входять аналогові сигнальні входи, ланцюги узгодження та підсилення, вхід зовнішньої синхронізації, внутрішній тактовий генератор, комутатор тактових сигналів (з внутрішнього тактового генератора та входу зовнішньої синхронізації), багатоканальні АЦП, модулі оперативної пам'яті, постійний запам'ятовуючий пристрій, програмована логічна інтегральна схема (ПЛІС), в якій містяться модуль перетворення послідовного коду у паралельний, модуль цифрової обробки сигналів, контролер передачі даних на інтерфейсну шину (виходи БЦПМ), модуль управління пам'яттю, модуль формування сигналів синхронізації та управління, модуль цифрової обробки сигналів у складі ПЛІС виконується у вигляді послідовно з'єднаних модуля цифрової фільтрації сигналів, модуля цифрового коригування та модуля цифрового діаграмоутворення, при цьому перша група входів модуля цифрової фільтрації сигналів є першою групою входів модуля цифрової обробки сигналів, а виходи модуля цифрового діаграмоутворення є виходами модуля цифрової обробки сигналів, виходи модуля цифрової фільтрації сигналів підключені до першої групи входів модуля цифрового коригування, виходи якого підключені до першої групи входів модуля цифрового діаграмоутворення, тактові входи модуля цифрової фільтрації сигналів, модуля цифрового коригування, модуля цифрового діаграмоутворення, а також тактові входи АЦП, модуля перетворення послідовного коду у паралельний і перші входи управління модуля управління пам'яттю підключені до першого виходу модуля формування сигналів синхронізації та управління (входить до складу ПЛІС), другі групи входів модуля цифрової фільтрації сигналів та модуля цифрового коригування підключені відповідно до другого та третього виходів модуля формування сигналів синхронізації та управління, вхід вибору алгоритму модуля цифрового діаграмоутворення підключений до четвертого виходу модуля формування сигналів синхронізації та управління, тактовий вхід якого підключений до виходу комутатора тактових сигналів, входи управління модуля формування сигналів синхронізації та управління підключені до другої групи виходів контролера передачі даних на інтерфейсну шину (виходи БЦПМ), аналогові сигнальні входи багатоканального цифрового приймального модуля підключені через ланцюги узгодження та підсилення до відповідних аналогових входів багатоканальних АЦП, вхід зовнішньої синхронізації та вихід внутрішнього тактового генератора підключені до відповідних входів комутатора тактових сигналів, передача результатів аналого-цифрового перетворення у модуль цифрової обробки сигналів, що входить до складу ПЛІС, виконується за допомогою послідовних диференціальних інтерфейсів (по одній диференціальній парі ліній на кожен з каналів АЦП), які підключені до відповідних входів модуля перетворення послідовного коду у паралельний (входить до складу ПЛІС), виходи модуля перетворення послідовного коду у паралельний підключені до першої групи входів модуля цифрової обробки сигналів (входить до складу ПЛІС), шини даних модулів оперативної пам'яті підключені через модуль управління пам'яттю (входить до складу ПЛІС) до виходів модуля цифрової обробки сигналів та до відповідних входів контролера передачі даних на інтерфейсну шину (виходи БЦПМ), а шини адресації та управління модулів оперативної пам'яті підключені до відповідних виходів модуля управління пам'яттю (входить до складу ПЛІС), постійний запам'ятовуючий пристрій підключений до входів завантаження архітектури ПЛІС, виходи контролера передачі даних на інтерфейсну шину є виходами БЦПМ.

3. Система обробки сигналів приймальної цифрової антенної решітки за п. 1, яка відрізняється тим, що до складу багатоканального цифрового приймального модуля (БЦПМ) входять блок приймачів і блок аналого-цифрового перетворення та обробки сигналів, блок приймачів містить N приймальних модулів у складі антенного входу, підсилювача, перемножувача частоти, гетеродинного входу, входу контрольного сигналу, двох квадратурних приймальних каналів та двох аналогових виходів кожний, крім того, блок приймачів містить вхід живлення, модуль живлення блока приймачів, вхід сигналу гетеродина, підсилювач сигналу гетеродина, розгалужувач сигналу гетеродина, вхід контрольного сигналу, підсилювач контрольного сигналу, розгалужувач контрольного сигналу, блок аналого-цифрового перетворення та обробки сигналів містить 2N аналогових сигнальних входів, ланцюги узгодження та підсилення, вхід зовнішньої синхронізації, внутрішній тактовий генератор, комутатор тактових сигналів (з внутрішнього тактового генератора та входу зовнішньої синхронізації), багатоканальні АЦП, модулі оперативної пам'яті, постійний запам'ятовуючий пристрій, програмована логічна інтегральна схема (ПЛІС), в якій містяться модуль перетворення послідовного коду у паралельний, модуль комутації сигналів, цифровий буфер, модуль цифрової обробки сигналів у вигляді послідовно з'єднаних модуля цифрової фільтрації сигналів, модуля цифрового коригування та модуля цифрового діаграмоутворення, контролер передачі даних на інтерфейсну шину (виходи БЦПМ), модуль управління пам'яттю, модуль формування сигналів синхронізації та управління, при цьому всі 2N виходів блока приймачів підключені до 2N аналоговихсигнальних входів блока аналого-цифрового перетворення та обробки сигналів, у кожному з N приймальних модулів блока приймачів антенний вхід є одночасно входом підсилювача, вихід якого підключений до першого входу перемножувача частоти, другий вхід якого є одночасно гетеродинним входом приймального модуля, а другий вхід підсилювача є входом контрольного сигналу приймального модуля, квадратурні виходи перемножувача частоти підключені до відповідних входів двох квадратурних приймальних каналів, гетеродинний вхід приймального модуля підключений до одного з відповідних виходів розгалужувача сигналу гетеродина, вхід контрольного сигналу приймального модуля підключений до одного з відповідних виходів розгалужувача контрольного сигналу, вхід живлення приймального модуля підключений до відповідного виходу модуля живлення блока приймачів, вхід сигналу гетеродина блока приймачів є одночасно входом підсилювача сигналу гетеродина вихід якого підключений до входу розгалужувача сигналу гетеродина, вхід контрольного сигналу блока приймачів є входом підсилювача контрольного сигналу, вихід якого підключений до входу розгалужувана контрольного сигналу, вхід модуля живлення є входом живлення блока приймачів, у блоці аналого-цифрового перетворення та обробки сигналів аналогові сигнальні входи підключені через ланцюги узгодження та підсилення до відповідних аналогових входів багатоканальних АЦП, вхід зовнішньої синхронізації та вихід внутрішнього тактового генератора підключені до відповідних входів комутатора тактових сигналів, передача результатів аналого-цифрового перетворення у модуль цифрової обробки сигналів, що входить до складу ПЛІС, виконується за допомогою послідовних диференціальних інтерфейсів (по одній диференціальній парі ліній на кожен з каналів АЦП), які підключені до відповідних входів модуля перетворення послідовного коду у паралельний (входить до складу ПЛІС), виходи модуля перетворення послідовного коду у паралельний підключені до першої групи входів модуля цифрової обробки сигналів (входить до складу ПЛІС), шини даних модулів оперативної пам'яті підключені через модуль управління пам'яттю (входить до складу ПЛІС) до виходів модуля цифрової обробки сигналів та до відповідних входів контролера передачі даних на інтерфейсну шину (виходи БЦПМ), а шини адресації та управління модулів оперативної пам'яті підключені до відповідних виходів модуля управління пам'яттю (входить до складу ПЛІС), постійний запам'ятовуючий пристрій підключений до входів завантаження архітектури ПЛІС, виходи контролера передачі даних на інтерфейсну шину є виходами БЦПМ, перша група входів модуля цифрової фільтрації сигналів є першою групою входів модуля цифрової обробки сигналів, а виходи модуля цифрового діаграмоутворення є виходами модуля цифрової обробки сигналів, виходи модуля цифрової фільтрації сигналів підключені до першої групи входів модуля цифрового коригування, виходи якого підключені до першої групи входів модуля цифрового діаграмоутворення, тактові входи модуля цифрової фільтрації сигналів, модуля цифрового коригування, модуля цифрового діаграмоутворення, а також тактові входи АЦП, модуля перетворення послідовного коду у паралельний і перші входи управління модуля управління пам'яттю підключені до першого виходу модуля формування сигналів синхронізації та управління (входить до складу ПЛІС), другі групи входів модуля цифрової фільтрації сигналів та модуля цифрового коригування підключені відповідно до другого та третього виходів модуля формування сигналів синхронізації та управління, вхід вибору алгоритму модуля цифрового діаграмоутворення підключений до четвертого виходу модуля формування сигналів синхронізації та управління, тактовий вхід якого підключений до виходу комутатора тактових сигналів, входи управління модуля формування сигналів синхронізації та управління підключені до другої групи виходів контролера передачі даних на інтерфейсну шину (виходи БЦПМ), виходи модуля перетворення послідовного коду у паралельний (входить до складу ПЛІС) підключені до першої групи входів модуля цифрової обробки сигналів у складі тієї ж ПЛІС через модуль комутації сигналів, входи цифрового буфера підключені до контролера передачі даних на інтерфейсну шину (виходи БЦПМ), а виходи - до другої групи входів модуля комутації сигналів, третій вхід якого підключений до виходу переключення режимів "Вибір режиму" модуля формування сигналів синхронізації та управління, тактовий вхід модуля комутації сигналів підключений до першого виходу модуля формування сигналів синхронізації та управління.

Текст

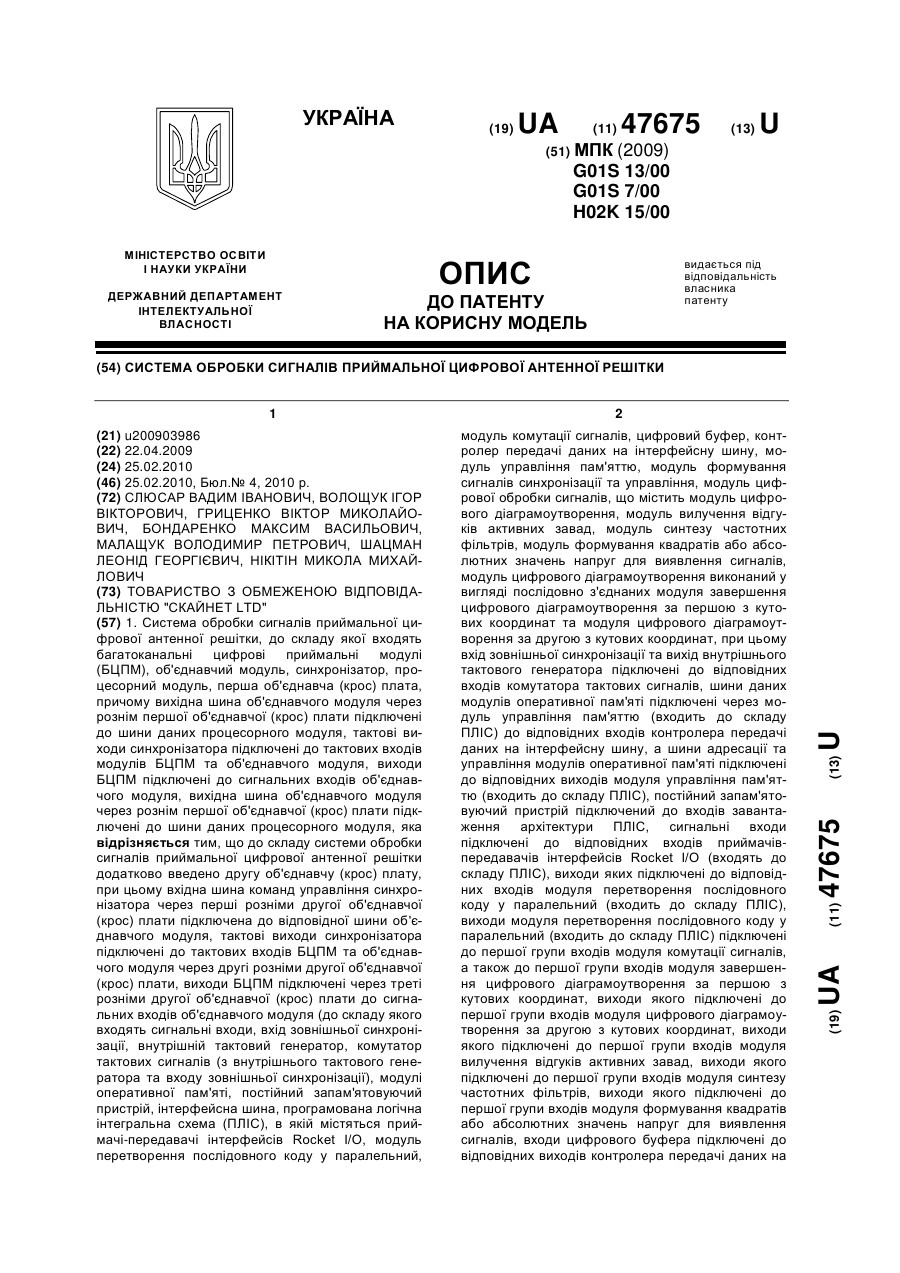

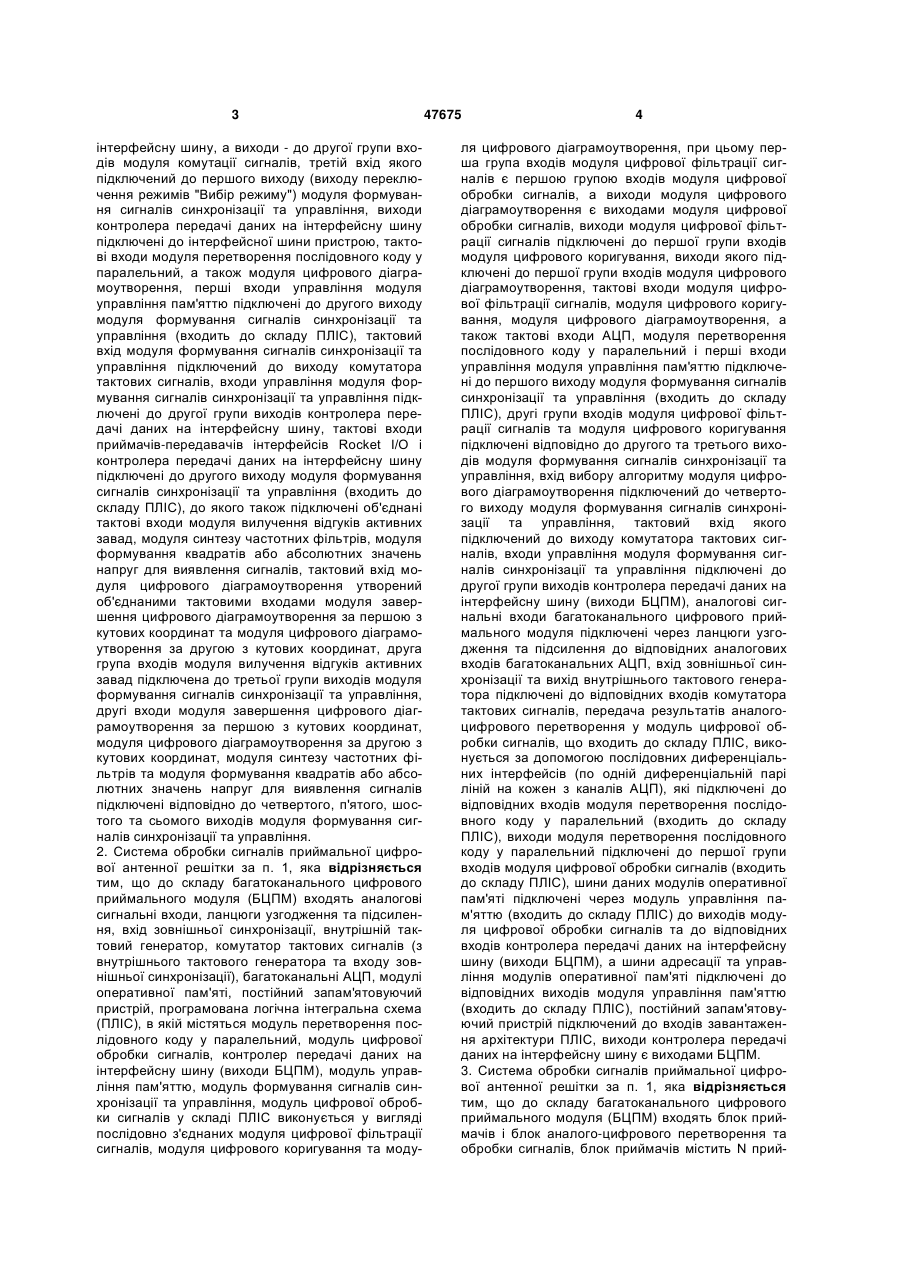

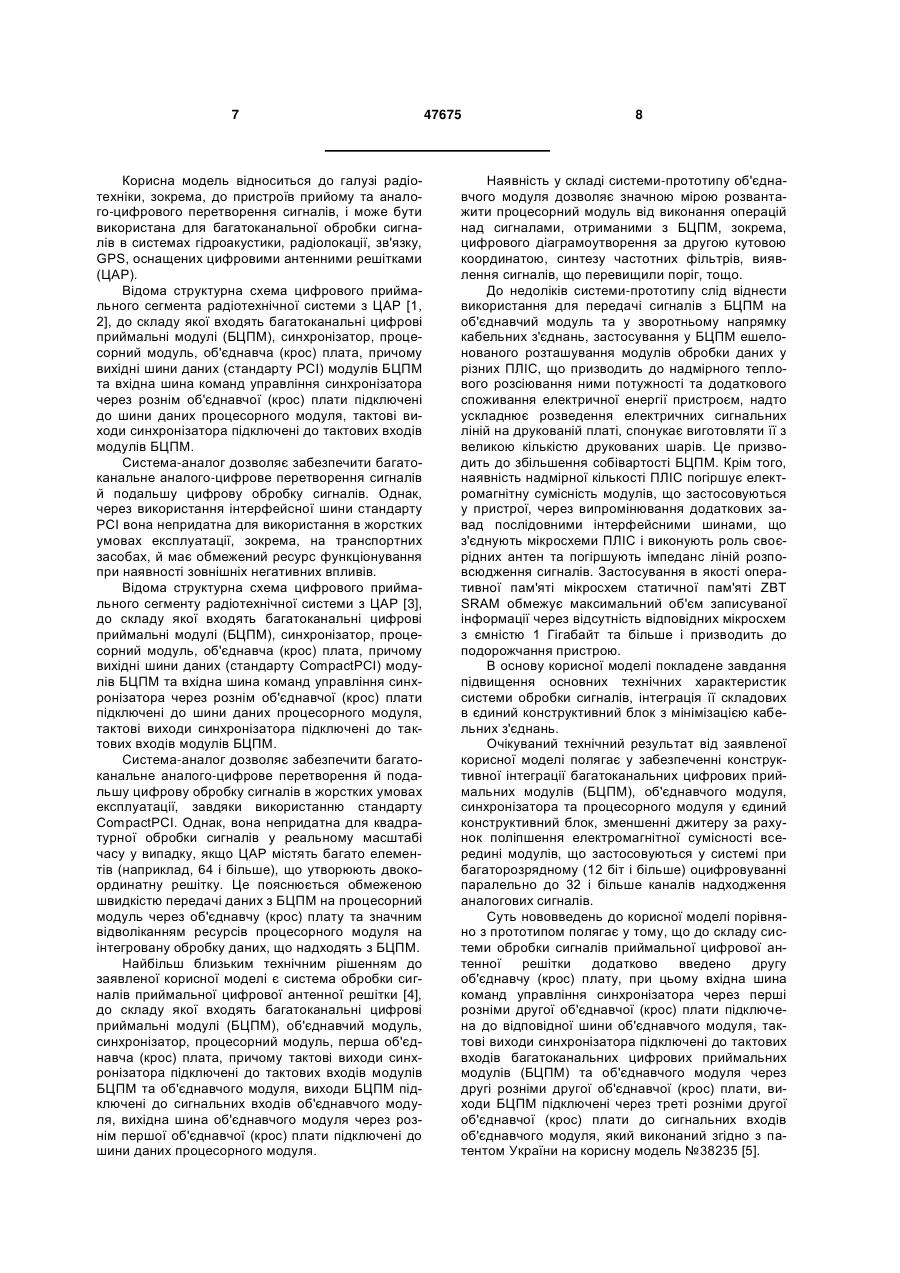

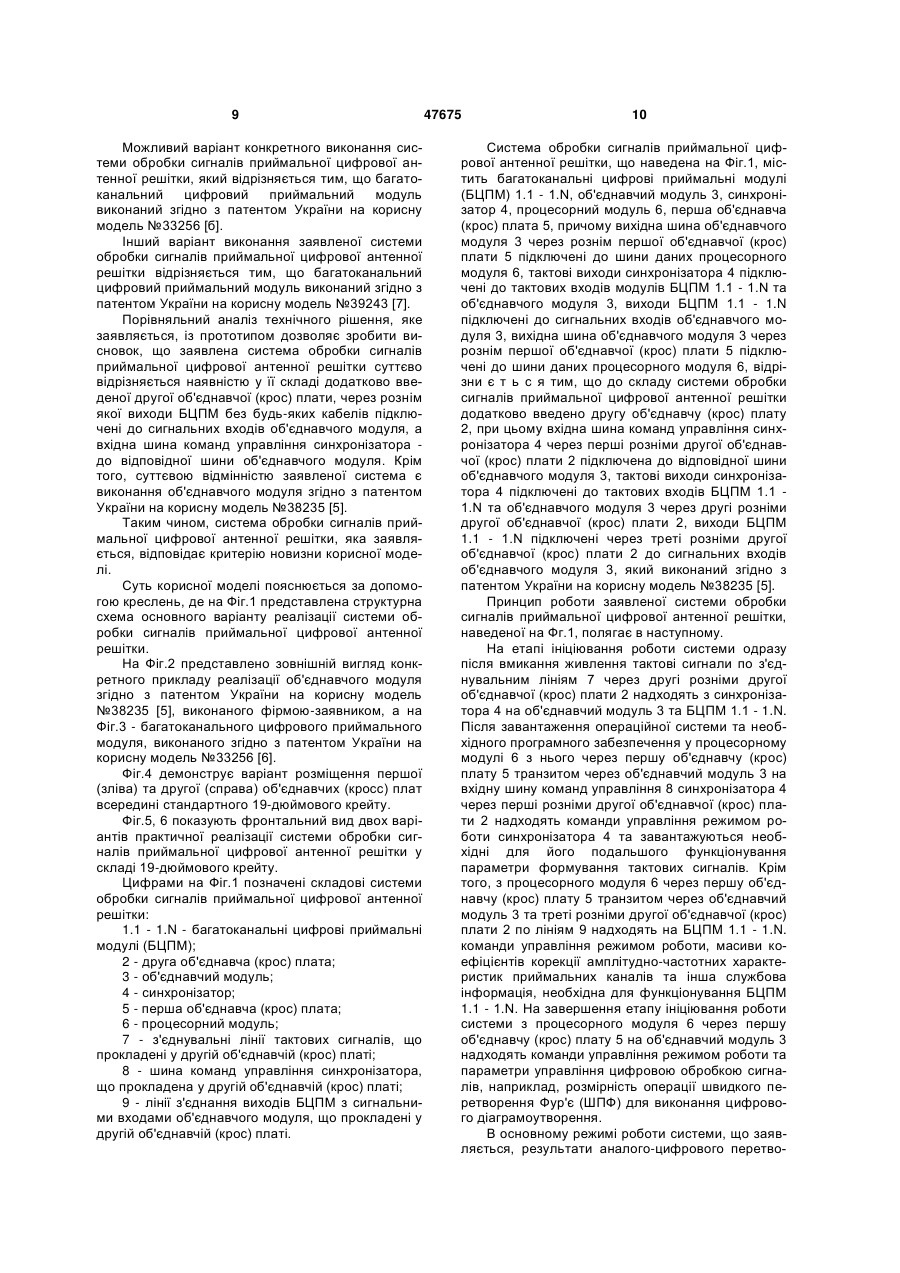

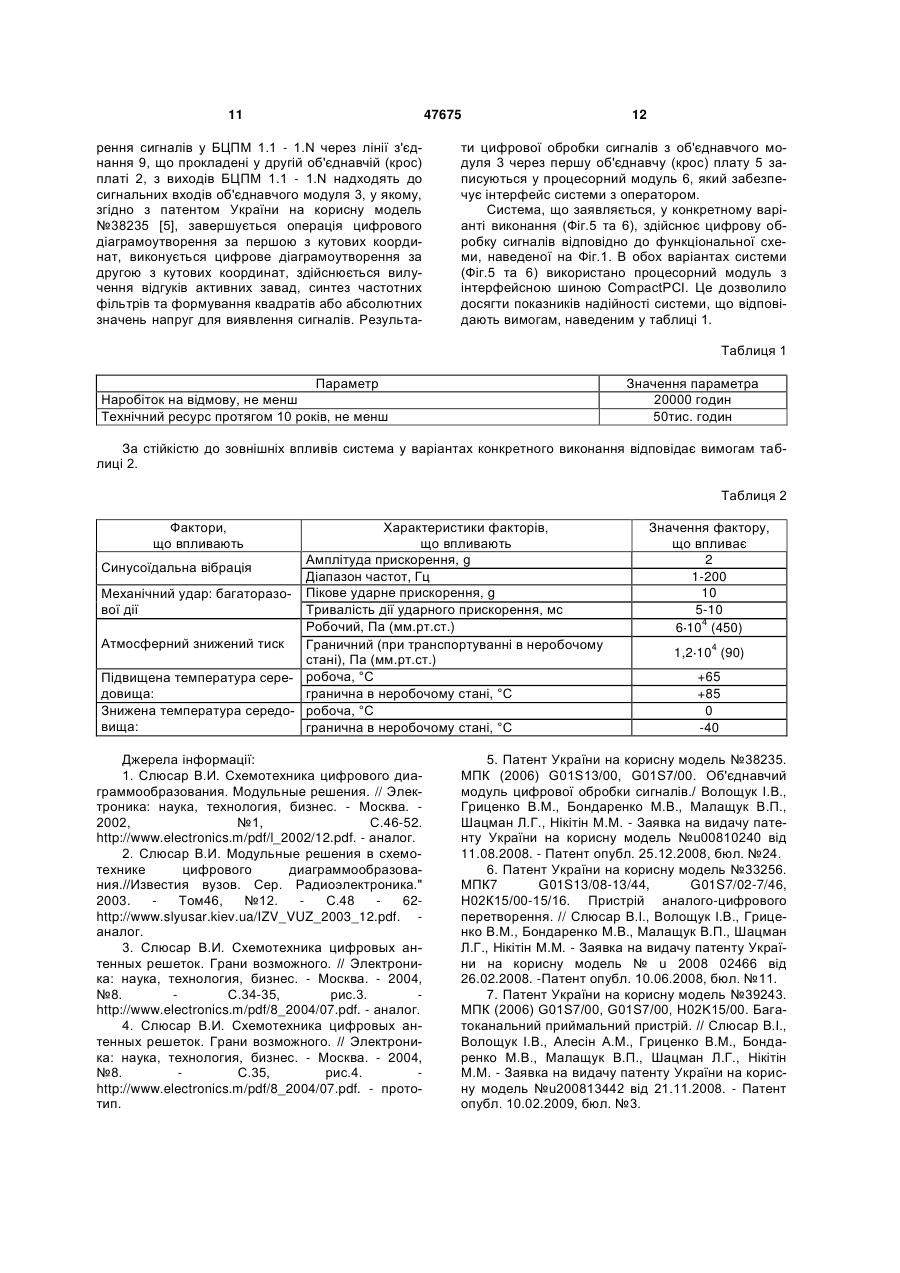

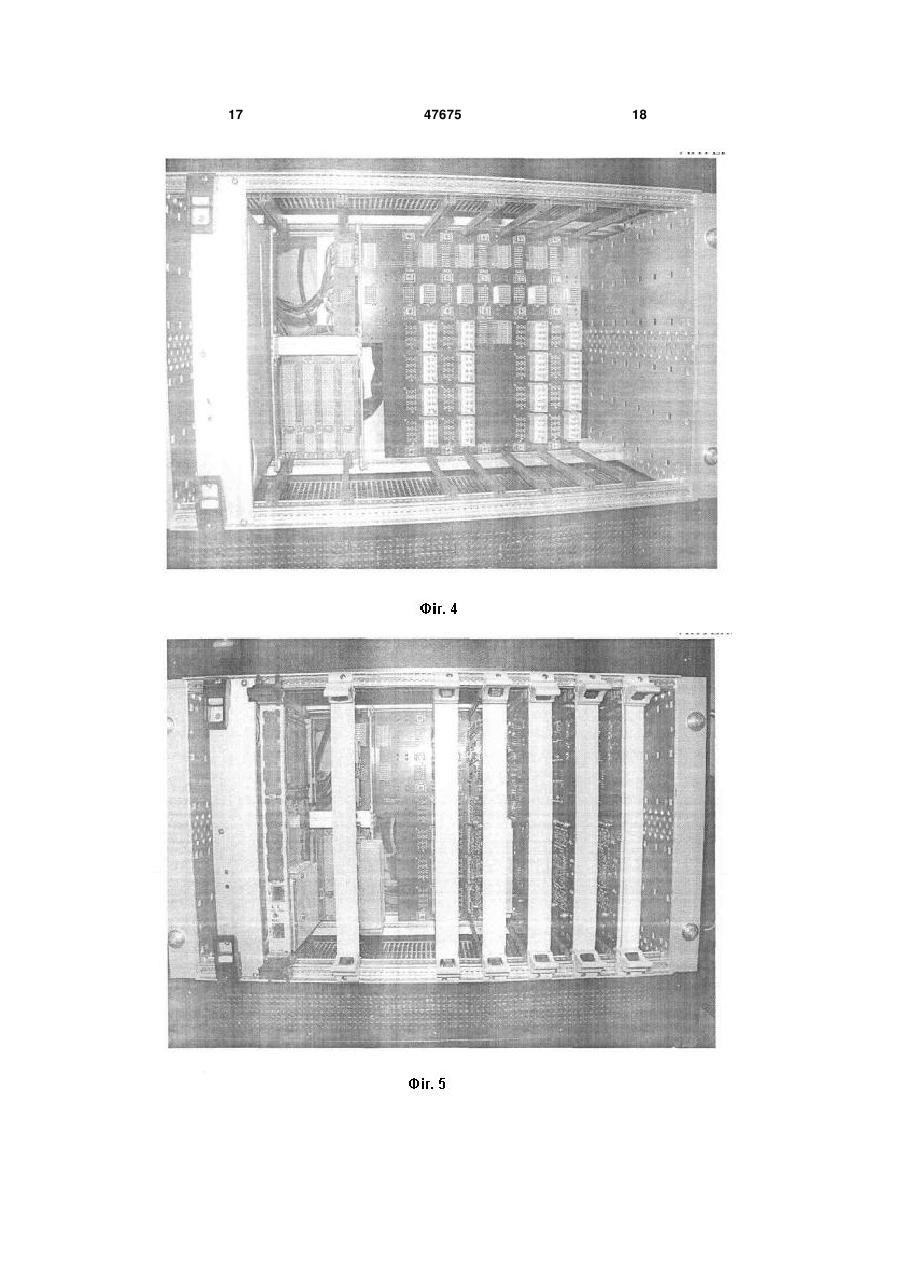

1. Система обробки сигналів приймальної цифрової антенної решітки, до складу якої входять багатоканальні цифрові приймальні модулі (БЦПМ), об'єднавчий модуль, синхронізатор, процесорний модуль, перша об'єднавча (крос) плата, причому вихідна шина об'єднавчого модуля через рознім першої об'єднавчої (крос) плати підключені до шини даних процесорного модуля, тактові виходи синхронізатора підключені до тактових входів модулів БЦПМ та об'єднавчого модуля, виходи БЦПМ підключені до сигнальних входів об'єднавчого модуля, вихідна шина об'єднавчого модуля через рознім першої об'єднавчої (крос) плати підключені до шини даних процесорного модуля, яка відрізняється тим, що до складу системи обробки сигналів приймальної цифрової антенної решітки додатково введено другу об'єднавчу (крос) плату, при цьому вхідна шина команд управління синхронізатора через перші розніми другої об'єднавчої (кроc) плати підключена до відповідної шини об'єднавчого модуля, тактові виходи синхронізатора підключені до тактових входів БЦПМ та об'єднавчого модуля через другі розніми другої об'єднавчої (крос) плати, виходи БЦПМ підключені через треті розніми другої об'єднавчої (крос) плати до сигнальних входів об'єднавчого модуля (до складу якого входять сигнальні входи, вхід зовнішньої синхронізації, внутрішній тактовий генератор, комутатор тактових сигналів (з внутрішнього тактового генератора та входу зовнішньої синхронізації), модулі оперативної пам'яті, постійний запам'ятовуючий пристрій, інтерфейсна шина, програмована логічна інтегральна схема (ПЛІС), в якій містяться приймачі-передавачі інтерфейсів Rocket I/O, модуль перетворення послідовного коду у паралельний, 3 інтерфейсну шину, а виходи - до другої групи входів модуля комутації сигналів, третій вхід якого підключений до першого виходу (виходу переключення режимів "Вибір режиму") модуля формування сигналів синхронізації та управління, виходи контролера передачі даних на інтерфейсну шину підключені до інтерфейсної шини пристрою, тактові входи модуля перетворення послідовного коду у паралельний, а також модуля цифрового діаграмоутворення, перші входи управління модуля управління пам'яттю підключені до другого виходу модуля формування сигналів синхронізації та управління (входить до складу ПЛІС), тактовий вхід модуля формування сигналів синхронізації та управління підключений до виходу комутатора тактових сигналів, входи управління модуля формування сигналів синхронізації та управління підключені до другої групи виходів контролера передачі даних на інтерфейсну шину, тактові входи приймачів-передавачів інтерфейсів Rocket I/O і контролера передачі даних на інтерфейсну шину підключені до другого виходу модуля формування сигналів синхронізації та управління (входить до складу ПЛІС), до якого також підключені об'єднані тактові входи модуля вилучення відгуків активних завад, модуля синтезу частотних фільтрів, модуля формування квадратів або абсолютних значень напруг для виявлення сигналів, тактовий вхід модуля цифрового діаграмоутворення утворений об'єднаними тактовими входами модуля завершення цифрового діаграмоутворення за першою з кутових координат та модуля цифрового діаграмоутворення за другою з кутових координат, друга група входів модуля вилучення відгуків активних завад підключена до третьої групи виходів модуля формування сигналів синхронізації та управління, другі входи модуля завершення цифрового діаграмоутворення за першою з кутових координат, модуля цифрового діаграмоутворення за другою з кутових координат, модуля синтезу частотних фільтрів та модуля формування квадратів або абсолютних значень напруг для виявлення сигналів підключені відповідно до четвертого, п'ятого, шостого та сьомого виходів модуля формування сигналів синхронізації та управління. 2. Система обробки сигналів приймальної цифрової антенної решітки за п. 1, яка відрізняється тим, що до складу багатоканального цифрового приймального модуля (БЦПМ) входять аналогові сигнальні входи, ланцюги узгодження та підсилення, вхід зовнішньої синхронізації, внутрішній тактовий генератор, комутатор тактових сигналів (з внутрішнього тактового генератора та входу зовнішньої синхронізації), багатоканальні АЦП, модулі оперативної пам'яті, постійний запам'ятовуючий пристрій, програмована логічна інтегральна схема (ПЛІС), в якій містяться модуль перетворення послідовного коду у паралельний, модуль цифрової обробки сигналів, контролер передачі даних на інтерфейсну шину (виходи БЦПМ), модуль управління пам'яттю, модуль формування сигналів синхронізації та управління, модуль цифрової обробки сигналів у складі ПЛІС виконується у вигляді послідовно з'єднаних модуля цифрової фільтрації сигналів, модуля цифрового коригування та моду 47675 4 ля цифрового діаграмоутворення, при цьому перша група входів модуля цифрової фільтрації сигналів є першою групою входів модуля цифрової обробки сигналів, а виходи модуля цифрового діаграмоутворення є виходами модуля цифрової обробки сигналів, виходи модуля цифрової фільтрації сигналів підключені до першої групи входів модуля цифрового коригування, виходи якого підключені до першої групи входів модуля цифрового діаграмоутворення, тактові входи модуля цифрової фільтрації сигналів, модуля цифрового коригування, модуля цифрового діаграмоутворення, а також тактові входи АЦП, модуля перетворення послідовного коду у паралельний і перші входи управління модуля управління пам'яттю підключені до першого виходу модуля формування сигналів синхронізації та управління (входить до складу ПЛІС), другі групи входів модуля цифрової фільтрації сигналів та модуля цифрового коригування підключені відповідно до другого та третього виходів модуля формування сигналів синхронізації та управління, вхід вибору алгоритму модуля цифрового діаграмоутворення підключений до четвертого виходу модуля формування сигналів синхронізації та управління, тактовий вхід якого підключений до виходу комутатора тактових сигналів, входи управління модуля формування сигналів синхронізації та управління підключені до другої групи виходів контролера передачі даних на інтерфейсну шину (виходи БЦПМ), аналогові сигнальні входи багатоканального цифрового приймального модуля підключені через ланцюги узгодження та підсилення до відповідних аналогових входів багатоканальних АЦП, вхід зовнішньої синхронізації та вихід внутрішнього тактового генератора підключені до відповідних входів комутатора тактових сигналів, передача результатів аналогоцифрового перетворення у модуль цифрової обробки сигналів, що входить до складу ПЛІС, виконується за допомогою послідовних диференціальних інтерфейсів (по одній диференціальній парі ліній на кожен з каналів АЦП), які підключені до відповідних входів модуля перетворення послідовного коду у паралельний (входить до складу ПЛІС), виходи модуля перетворення послідовного коду у паралельний підключені до першої групи входів модуля цифрової обробки сигналів (входить до складу ПЛІС), шини даних модулів оперативної пам'яті підключені через модуль управління пам'яттю (входить до складу ПЛІС) до виходів модуля цифрової обробки сигналів та до відповідних входів контролера передачі даних на інтерфейсну шину (виходи БЦПМ), а шини адресації та управління модулів оперативної пам'яті підключені до відповідних виходів модуля управління пам'яттю (входить до складу ПЛІС), постійний запам'ятовуючий пристрій підключений до входів завантаження архітектури ПЛІС, виходи контролера передачі даних на інтерфейсну шину є виходами БЦПМ. 3. Система обробки сигналів приймальної цифрової антенної решітки за п. 1, яка відрізняється тим, що до складу багатоканального цифрового приймального модуля (БЦПМ) входять блок приймачів і блок аналого-цифрового перетворення та обробки сигналів, блок приймачів містить N прий 5 мальних модулів у складі антенного входу, підсилювача, перемножувача частоти, гетеродинного входу, входу контрольного сигналу, двох квадратурних приймальних каналів та двох аналогових виходів кожний, крім того, блок приймачів містить вхід живлення, модуль живлення блока приймачів, вхід сигналу гетеродина, підсилювач сигналу гетеродина, розгалужувач сигналу гетеродина, вхід контрольного сигналу, підсилювач контрольного сигналу, розгалужувач контрольного сигналу, блок аналого-цифрового перетворення та обробки сигналів містить 2N аналогових сигнальних входів, ланцюги узгодження та підсилення, вхід зовнішньої синхронізації, внутрішній тактовий генератор, комутатор тактових сигналів (з внутрішнього тактового генератора та входу зовнішньої синхронізації), багатоканальні АЦП, модулі оперативної пам'яті, постійний запам'ятовуючий пристрій, програмована логічна інтегральна схема (ПЛІС), в якій містяться модуль перетворення послідовного коду у паралельний, модуль комутації сигналів, цифровий буфер, модуль цифрової обробки сигналів у вигляді послідовно з'єднаних модуля цифрової фільтрації сигналів, модуля цифрового коригування та модуля цифрового діаграмоутворення, контролер передачі даних на інтерфейсну шину (виходи БЦПМ), модуль управління пам'яттю, модуль формування сигналів синхронізації та управління, при цьому всі 2N виходів блока приймачів підключені до 2N аналогових сигнальних входів блока аналого-цифрового перетворення та обробки сигналів, у кожному з N приймальних модулів блока приймачів антенний вхід є одночасно входом підсилювача, вихід якого підключений до першого входу перемножувача частоти, другий вхід якого є одночасно гетеродинним входом приймального модуля, а другий вхід підсилювача є входом контрольного сигналу приймального модуля, квадратурні виходи перемножувача частоти підключені до відповідних входів двох квадратурних приймальних каналів, гетеродинний вхід приймального модуля підключений до одного з відповідних виходів розгалужувача сигналу гетеродина, вхід контрольного сигналу приймального модуля підключений до одного з відповідних виходів розгалужувача контрольного сигналу, вхід живлення приймального модуля підключений до відповідного виходу модуля живлення блока приймачів, вхід сигналу гетеродина блока приймачів є одночасно входом підсилювача сигналу гетеродина вихід якого підключений до входу розгалужувача сигналу гетеродина, вхід контрольного сигналу блока приймачів є входом підсилювача контрольного сигналу, вихід якого підключений до входу розгалужувача контрольного сигналу, вхід модуля живлення є входом живлення блока приймачів, у блоці аналогоцифрового перетворення та обробки сигналів аналогові сигнальні входи підключені через ланцюги узгодження та підсилення до відповідних аналогових входів багатоканальних АЦП, вхід зовнішньої синхронізації та вихід внутрішнього тактового генератора підключені до відповідних входів комутатора тактових сигналів, передача результатів аналого-цифрового перетворення у модуль цифрової 47675 6 обробки сигналів, що входить до складу ПЛІС, виконується за допомогою послідовних диференціальних інтерфейсів (по одній диференціальній парі ліній на кожен з каналів АЦП), які підключені до відповідних входів модуля перетворення послідовного коду у паралельний (входить до складу ПЛІС), виходи модуля перетворення послідовного коду у паралельний підключені до першої групи входів модуля цифрової обробки сигналів (входить до складу ПЛІС), шини даних модулів оперативної пам'яті підключені через модуль управління пам'яттю (входить до складу ПЛІС) до виходів модуля цифрової обробки сигналів та до відповідних входів контролера передачі даних на інтерфейсну шину (виходи БЦПМ), а шини адресації та управління модулів оперативної пам'яті підключені до відповідних виходів модуля управління пам'яттю (входить до складу ПЛІС), постійний запам'ятовуючий пристрій підключений до входів завантаження архітектури ПЛІС, виходи контролера передачі даних на інтерфейсну шину є виходами БЦПМ, перша група входів модуля цифрової фільтрації сигналів є першою групою входів модуля цифрової обробки сигналів, а виходи модуля цифрового діаграмоутворення є виходами модуля цифрової обробки сигналів, виходи модуля цифрової фільтрації сигналів підключені до першої групи входів модуля цифрового коригування, виходи якого підключені до першої групи входів модуля цифрового діаграмоутворення, тактові входи модуля цифрової фільтрації сигналів, модуля цифрового коригування, модуля цифрового діаграмоутворення, а також тактові входи АЦП, модуля перетворення послідовного коду у паралельний і перші входи управління модуля управління пам'яттю підключені до першого виходу модуля формування сигналів синхронізації та управління (входить до складу ПЛІС), другі групи входів модуля цифрової фільтрації сигналів та модуля цифрового коригування підключені відповідно до другого та третього виходів модуля формування сигналів синхронізації та управління, вхід вибору алгоритму модуля цифрового діаграмоутворення підключений до четвертого виходу модуля формування сигналів синхронізації та управління, тактовий вхід якого підключений до виходу комутатора тактових сигналів, входи управління модуля формування сигналів синхронізації та управління підключені до другої групи виходів контролера передачі даних на інтерфейсну шину (виходи БЦПМ), виходи модуля перетворення послідовного коду у паралельний (входить до складу ПЛІС) підключені до першої групи входів модуля цифрової обробки сигналів у складі тієї ж ПЛІС через модуль комутації сигналів, входи цифрового буфера підключені до контролера передачі даних на інтерфейсну шину (виходи БЦПМ), а виходи - до другої групи входів модуля комутації сигналів, третій вхід якого підключений до виходу переключення режимів "Вибір режиму" модуля формування сигналів синхронізації та управління, тактовий вхід модуля комутації сигналів підключений до першого виходу модуля формування сигналів синхронізації та управління. 7 Корисна модель відноситься до галузі радіотехніки, зокрема, до пристроїв прийому та аналого-цифрового перетворення сигналів, і може бути використана для багатоканальної обробки сигналів в системах гідроакустики, радіолокації, зв'язку, GPS, оснащених цифровими антенними решітками (ЦАР). Відома структурна схема цифрового приймального сегмента радіотехнічної системи з ЦАР [1, 2], до складу якої входять багатоканальні цифрові приймальні модулі (БЦПМ), синхронізатор, процесорний модуль, об'єднавча (крос) плата, причому вихідні шини даних (стандарту РСІ) модулів БЦПМ та вхідна шина команд управління синхронізатора через рознім об'єднавчої (крос) плати підключені до шини даних процесорного модуля, тактові виходи синхронізатора підключені до тактових входів модулів БЦПМ. Система-аналог дозволяє забезпечити багатоканальне аналого-цифрове перетворення сигналів й подальшу цифрову обробку сигналів. Однак, через використання інтерфейсної шини стандарту РСІ вона непридатна для використання в жорстких умовах експлуатації, зокрема, на транспортних засобах, й має обмежений ресурс функціонування при наявності зовнішніх негативних впливів. Відома структурна схема цифрового приймального сегменту радіотехнічної системи з ЦАР [3], до складу якої входять багатоканальні цифрові приймальні модулі (БЦПМ), синхронізатор, процесорний модуль, об'єднавча (крос) плата, причому вихідні шини даних (стандарту CompactPCI) модулів БЦПМ та вхідна шина команд управління синхронізатора через рознім об'єднавчої (крос) плати підключені до шини даних процесорного модуля, тактові виходи синхронізатора підключені до тактових входів модулів БЦПМ. Система-аналог дозволяє забезпечити багатоканальне аналого-цифрове перетворення й подальшу цифрову обробку сигналів в жорстких умовах експлуатації, завдяки використанню стандарту CompactPCI. Однак, вона непридатна для квадратурної обробки сигналів у реальному масштабі часу у випадку, якщо ЦАР містять багато елементів (наприклад, 64 і більше), що утворюють двокоординатну решітку. Це пояснюється обмеженою швидкістю передачі даних з БЦПМ на процесорний модуль через об'єднавчу (крос) плату та значним відволіканням ресурсів процесорного модуля на інтегровану обробку даних, що надходять з БЦПМ. Найбільш близьким технічним рішенням до заявленої корисної моделі є система обробки сигналів приймальної цифрової антенної решітки [4], до складу якої входять багатоканальні цифрові приймальні модулі (БЦПМ), об'єднавчий модуль, синхронізатор, процесорний модуль, перша об'єднавча (крос) плата, причому тактові виходи синхронізатора підключені до тактових входів модулів БЦПМ та об'єднавчого модуля, виходи БЦПМ підключені до сигнальних входів об'єднавчого модуля, вихідна шина об'єднавчого модуля через рознім першої об'єднавчої (крос) плати підключені до шини даних процесорного модуля. 47675 8 Наявність у складі системи-прототипу об'єднавчого модуля дозволяє значною мірою розвантажити процесорний модуль від виконання операцій над сигналами, отриманими з БЦПМ, зокрема, цифрового діаграмоутворення за другою кутовою координатою, синтезу частотних фільтрів, виявлення сигналів, що перевищили поріг, тощо. До недоліків системи-прототипу слід віднести використання для передачі сигналів з БЦПМ на об'єднавчий модуль та у зворотньому напрямку кабельних з'єднань, застосування у БЦПМ ешелонованого розташування модулів обробки даних у різних ПЛІС, що призводить до надмірного теплового розсіювання ними потужності та додаткового споживання електричної енергії пристроєм, надто ускладнює розведення електричних сигнальних ліній на друкованій платі, спонукає виготовляти її з великою кількістю друкованих шарів. Це призводить до збільшення собівартості БЦПМ. Крім того, наявність надмірної кількості ПЛІС погіршує електромагнітну сумісність модулів, що застосовуються у пристрої, через випромінювання додаткових завад послідовними інтерфейсними шинами, що з'єднують мікросхеми ПЛІС і виконують роль своєрідних антен та погіршують імпеданс ліній розповсюдження сигналів. Застосування в якості оперативної пам'яті мікросхем статичної пам'яті ZBT SRAM обмежує максимальний об'єм записуваної інформації через відсутність відповідних мікросхем з ємністю 1 Гігабайт та більше і призводить до подорожчання пристрою. В основу корисної моделі покладене завдання підвищення основних технічних характеристик системи обробки сигналів, інтеграція її складових в єдиний конструктивний блок з мінімізацією кабельних з'єднань. Очікуваний технічний результат від заявленої корисної моделі полягає у забезпеченні конструктивної інтеграції багатоканальних цифрових приймальних модулів (БЦПМ), об'єднавчого модуля, синхронізатора та процесорного модуля у єдиний конструктивний блок, зменшенні джитеру за рахунок поліпшення електромагнітної сумісності всередині модулів, що застосовуються у системі при багаторозрядному (12 біт і більше) оцифровуванні паралельно до 32 і більше каналів надходження аналогових сигналів. Суть нововведень до корисної моделі порівняно з прототипом полягає у тому, що до складу системи обробки сигналів приймальної цифрової антенної решітки додатково введено другу об'єднавчу (крос) плату, при цьому вхідна шина команд управління синхронізатора через перші розніми другої об'єднавчої (крос) плати підключена до відповідної шини об'єднавчого модуля, тактові виходи синхронізатора підключені до тактових входів багатоканальних цифрових приймальних модулів (БЦПМ) та об'єднавчого модуля через другі розніми другої об'єднавчої (крос) плати, виходи БЦПМ підключені через треті розніми другої об'єднавчої (крос) плати до сигнальних входів об'єднавчого модуля, який виконаний згідно з патентом України на корисну модель №38235 [5]. 9 Можливий варіант конкретного виконання системи обробки сигналів приймальної цифрової антенної решітки, який відрізняється тим, що багатоканальний цифровий приймальний модуль виконаний згідно з патентом України на корисну модель №33256 [б]. Інший варіант виконання заявленої системи обробки сигналів приймальної цифрової антенної решітки відрізняється тим, що багатоканальний цифровий приймальний модуль виконаний згідно з патентом України на корисну модель №39243 [7]. Порівняльний аналіз технічного рішення, яке заявляється, із прототипом дозволяє зробити висновок, що заявлена система обробки сигналів приймальної цифрової антенної решітки суттєво відрізняється наявністю у її складі додатково введеної другої об'єднавчої (крос) плати, через рознім якої виходи БЦПМ без будь-яких кабелів підключені до сигнальних входів об'єднавчого модуля, а вхідна шина команд управління синхронізатора до відповідної шини об'єднавчого модуля. Крім того, суттєвою відмінністю заявленої система є виконання об'єднавчого модуля згідно з патентом України на корисну модель №38235 [5]. Таким чином, система обробки сигналів приймальної цифрової антенної решітки, яка заявляється, відповідає критерію новизни корисної моделі. Суть корисної моделі пояснюється за допомогою креслень, де на Фіг.1 представлена структурна схема основного варіанту реалізації системи обробки сигналів приймальної цифрової антенної решітки. На Фіг.2 представлено зовнішній вигляд конкретного прикладу реалізації об'єднавчого модуля згідно з патентом України на корисну модель №38235 [5], виконаного фірмою-заявником, а на Фіг.3 - багатоканального цифрового приймального модуля, виконаного згідно з патентом України на корисну модель №33256 [6]. Фіг.4 демонструє варіант розміщення першої (зліва) та другої (справа) об'єднавчих (кросс) плат всередині стандартного 19-дюймового крейту. Фіг.5, 6 показують фронтальний вид двох варіантів практичної реалізації системи обробки сигналів приймальної цифрової антенної решітки у складі 19-дюймового крейту. Цифрами на Фіг.1 позначені складові системи обробки сигналів приймальної цифрової антенної решітки: 1.1 - 1.N - багатоканальні цифрові приймальні модулі (БЦПМ); 2 - друга об'єднавча (крос) плата; 3 - об'єднавчий модуль; 4 - синхронізатор; 5 - перша об'єднавча (крос) плата; 6 - процесорний модуль; 7 - з'єднувальні лінії тактових сигналів, що прокладені у другій об'єднавчій (крос) платі; 8 - шина команд управління синхронізатора, що прокладена у другій об'єднавчій (крос) платі; 9 - лінії з'єднання виходів БЦПМ з сигнальними входами об'єднавчого модуля, що прокладені у другій об'єднавчій (крос) платі. 47675 10 Система обробки сигналів приймальної цифрової антенної решітки, що наведена на Фіг.1, містить багатоканальні цифрові приймальні модулі (БЦПМ) 1.1 - 1.N, об'єднавчий модуль 3, синхронізатор 4, процесорний модуль 6, перша об'єднавча (крос) плата 5, причому вихідна шина об'єднавчого модуля 3 через рознім першої об'єднавчої (крос) плати 5 підключені до шини даних процесорного модуля 6, тактові виходи синхронізатора 4 підключені до тактових входів модулів БЦПМ 1.1 - 1.N та об'єднавчого модуля 3, виходи БЦПМ 1.1 - 1.N підключені до сигнальних входів об'єднавчого модуля 3, вихідна шина об'єднавчого модуля 3 через рознім першої об'єднавчої (крос) плати 5 підключені до шини даних процесорного модуля 6, відрізни є т ь с я тим, що до складу системи обробки сигналів приймальної цифрової антенної решітки додатково введено другу об'єднавчу (крос) плату 2, при цьому вхідна шина команд управління синхронізатора 4 через перші розніми другої об'єднавчої (крос) плати 2 підключена до відповідної шини об'єднавчого модуля 3, тактові виходи синхронізатора 4 підключені до тактових входів БЦПМ 1.1 1.N та об'єднавчого модуля 3 через другі розніми другої об'єднавчої (крос) плати 2, виходи БЦПМ 1.1 - 1.N підключені через треті розніми другої об'єднавчої (крос) плати 2 до сигнальних входів об'єднавчого модуля 3, який виконаний згідно з патентом України на корисну модель №38235 [5]. Принцип роботи заявленої системи обробки сигналів приймальної цифрової антенної решітки, наведеної на Фг.1, полягає в наступному. На етапі ініціювання роботи системи одразу після вмикання живлення тактові сигнали по з'єднувальним лініям 7 через другі розніми другої об'єднавчої (крос) плати 2 надходять з синхронізатора 4 на об'єднавчий модуль 3 та БЦПМ 1.1 - 1.N. Після завантаження операційної системи та необхідного програмного забезпечення у процесорному модулі 6 з нього через першу об'єднавчу (крос) плату 5 транзитом через об'єднавчий модуль 3 на вхідну шину команд управління 8 синхронізатора 4 через перші розніми другої об'єднавчої (крос) плати 2 надходять команди управління режимом роботи синхронізатора 4 та завантажуються необхідні для його подальшого функціонування параметри формування тактових сигналів. Крім того, з процесорного модуля 6 через першу об'єднавчу (крос) плату 5 транзитом через об'єднавчий модуль 3 та треті розніми другої об'єднавчої (крос) плати 2 по лініям 9 надходять на БЦПМ 1.1 - 1.N. команди управління режимом роботи, масиви коефіцієнтів корекції амплітудно-частотних характеристик приймальних каналів та інша службова інформація, необхідна для функціонування БЦПМ 1.1 - 1.N. На завершення етапу ініціювання роботи системи з процесорного модуля 6 через першу об'єднавчу (крос) плату 5 на об'єднавчий модуль 3 надходять команди управління режимом роботи та параметри управління цифровою обробкою сигналів, наприклад, розмірність операції швидкого перетворення Фур'є (ШПФ) для виконання цифрового діаграмоутворення. В основному режимі роботи системи, що заявляється, результати аналого-цифрового перетво 11 рення сигналів у БЦПМ 1.1 - 1.N через лінії з'єднання 9, що прокладені у другій об'єднавчій (крос) платі 2, з виходів БЦПМ 1.1 - 1.N надходять до сигнальних входів об'єднавчого модуля 3, у якому, згідно з патентом України на корисну модель №38235 [5], завершується операція цифрового діаграмоутворення за першою з кутових координат, виконується цифрове діаграмоутворення за другою з кутових координат, здійснюється вилучення відгуків активних завад, синтез частотних фільтрів та формування квадратів або абсолютних значень напруг для виявлення сигналів. Результа 47675 12 ти цифрової обробки сигналів з об'єднавчого модуля 3 через першу об'єднавчу (крос) плату 5 записуються у процесорний модуль 6, який забезпечує інтерфейс системи з оператором. Система, що заявляється, у конкретному варіанті виконання (Фіг.5 та 6), здійснює цифрову обробку сигналів відповідно до функціональної схеми, наведеної на Фіг.1. В обох варіантах системи (Фіг.5 та 6) використано процесорний модуль з інтерфейсною шиною CompactPCI. Це дозволило досягти показників надійності системи, що відповідають вимогам, наведеним у таблиці 1. Таблиця 1 Параметр Наробіток на відмову, не менш Технічний ресурс протягом 10 років, не менш Значення параметра 20000 годин 50тис. годин За стійкістю до зовнішніх впливів система у варіантах конкретного виконання відповідає вимогам таблиці 2. Таблиця 2 Фактори, що впливають Характеристики факторів, що впливають Амплітуда прискорення, g Синусоїдальна вібрація Діапазон частот, Гц Механічний удар: багаторазо- Пікове ударне прискорення, g вої дії Тривалість дії ударного прискорення, мс Робочий, Па (мм.рт.ст.) Атмосферний знижений тиск Граничний (при транспортуванні в неробочому стані), Па (мм.рт.ст.) Підвищена температура сере- робоча, °С довища: гранична в неробочому стані, °С Знижена температура середо- робоча, °С вища: гранична в неробочому стані, °С Джерела інформації: 1. Слюсар В.И. Схемотехника цифрового диаграммообразования. Модульные решения. // Электроника: наука, технология, бизнес. - Москва. 2002, №1, С.46-52. http://www.electronics.m/pdf/l_2002/12.pdf. - аналог. 2. Слюсар В.И. Модульные решения в схемотехнике цифрового диаграммообразования.//Известия вузов. Сер. Радиоэлектроника." 2003. Том46, №12. С.48 62http://www.slyusar.kiev.ua/IZV_VUZ_2003_12.pdf. аналог. 3. Слюсар В.И. Схемотехника цифровых антенных решеток. Грани возможного. // Электроника: наука, технология, бизнес. - Москва. - 2004, №8. С.34-35, рис.3. http://www.electronics.m/pdf/8_2004/07.pdf. - аналог. 4. Слюсар В.И. Схемотехника цифровых антенных решеток. Грани возможного. // Электроника: наука, технология, бизнес. - Москва. - 2004, №8. С.35, рис.4. http://www.electronics.m/pdf/8_2004/07.pdf. - прототип. Значення фактору, що впливає 2 1-200 10 5-10 6 104 (450) 1,2 104 (90) +65 +85 0 -40 5. Патент України на корисну модель №38235. МПК (2006) G01S13/00, G01S7/00. Об'єднавчий модуль цифрової обробки сигналів./ Волощук І.В., Гриценко В.М., Бондаренко М.В., Малащук В.П., Шацман Л.Г., Нікітін М.М. - Заявка на видачу патенту України на корисну модель №u00810240 від 11.08.2008. - Патент опубл. 25.12.2008, бюл. №24. 6. Патент України на корисну модель №33256. МПК7 G01S13/08-13/44, G01S7/02-7/46, H02К15/00-15/16. Пристрій аналого-цифрового перетворення. // Слюсар B.I., Волощук І.В., Гриценко В.М., Бондаренко М.В., Малащук В.П., Шацман Л.Г., Нікітін М.М. - Заявка на видачу патенту України на корисну модель № u 2008 02466 від 26.02.2008. -Патент опубл. 10.06.2008, бюл. №11. 7. Патент України на корисну модель №39243. МПК (2006) G01S7/00, G01S7/00, H02K15/00. Багатоканальний приймальний пристрій. // Слюсар B.I., Волощук І.В., Алесін A.M., Гриценко В.М., Бондаренко М.В., Малащук В.П., Шацман Л.Г., Нікітін М.М. - Заявка на видачу патенту України на корисну модель №u200813442 від 21.11.2008. - Патент опубл. 10.02.2009, бюл. №3. 13 47675 14 15 47675 16 17 47675 18 19 Комп’ютерна верстка А. Рябко 47675 Підписне 20 Тираж 26 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюSystem for signal processing of receiving digital antenna grid

Автори англійськоюSliusar Vadym Ivanovych, Voloschuk Ihor Viktorovych, Hrytsenko Viktor Mykolaiovych, Bondarenko Maksym Vasyliovych, Malaschuk Volodymyr Petrovych, Shatsman Leonid Heorhiiovych, Nikitin Mykola Mykhailovych

Назва патенту російськоюСистема обработки сигналов приемной цифровой антенной решетки

Автори російськоюСлюсар Вадим Иванович, Волощук Игорь Викторович, Гриценко Виктор Николаевич, Бондаренко Максим Васильевич, Малащук Владимир Петрович, Шацман Леонид Георгиевич, Никитин Николай Михайлович

МПК / Мітки

МПК: H02K 15/00, G01S 13/00, G01S 7/00

Мітки: приймальної, цифрової, антенної, система, обробки, решітки, сигналів

Код посилання

<a href="https://ua.patents.su/10-47675-sistema-obrobki-signaliv-prijjmalno-cifrovo-antenno-reshitki.html" target="_blank" rel="follow" title="База патентів України">Система обробки сигналів приймальної цифрової антенної решітки</a>