Відмовостійкий процесорний пристрій з підвищеною швидкодією

Номер патенту: 76984

Опубліковано: 25.01.2013

Автори: Гунченко Юрій Олександрович, Борисенко Ірина Іванівна, Мартинюк Сергій Михайлович, Лєнков Сергій Васильович, Кобозєва Алла Анатоліївна

Формула / Реферат

Відмовостійкий процесорний пристрій з підвищеною швидкодією, який містить лічильник команд, регістр копії лічильника команд, блок регістрів загального призначення, блок копії регістрів загального призначення, блок пам'яті програм, блок управління та виконання команд, блок визначення сигнатури, буфер запису, блок пам'яті даних, перший регістр сигнатури, при цьому перший вихід лічильника команд, через регістр копії лічильника команд, з'єднано з першим входом, другий вихід з'єднано з першим входом блока визначення сигнатури, а третій вихід, через блок пам'яті програм, з'єднано з першим входом блока управління та виконання команд, перший вихід якого з'єднано з другим входом лічильника команд, а другий вихід з'єднано з входом буфера запису, перший вихід якого, через блок пам'яті даних, з'єднано з другим входом блока управління та виконання команд, третій вихід якого з'єднано з першим входом блока регістрів загального призначення, перший вихід якого, через блок копії регістрів загального призначення, з'єднано з другим входом, а другий вихід - з третім входом блока управління та виконання програм та з другим входом блока визначення сигнатури, третій вхід якого з'єднано з четвертим виходом блока управління та виконання програм, а вихід - з входом першого регістра сигнатури, який відрізняється тим, що уведено другий регістр сигнатури та мажоритарно-порівняльний блок, при цьому другий вихід буфера запису з'єднано з четвертим входом блока визначення сигнатури, вихід якого додатково з'єднано з першим входом мажоритарно-порівняльного блока, вихід першого регістра сигнатури з'єднано з другим входом та, через другий регістр сигнатури, з третім входом мажоритарно-порівняльного блока, вихід якого з'єднано з четвертим входом блока управління та виконання програм.

Текст

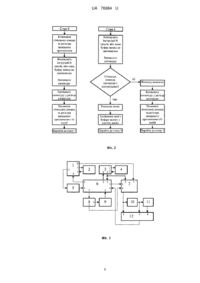

Реферат: Відмовостійкий процесорний пристрій з підвищеною швидкодією містить лічильник команд, регістр копії лічильника команд, блок регістрів загального призначення, блок копії регістрів загального призначення, блок пам'яті програм, блок управління та виконання команд, блок визначення сигнатури, буфер запису, блок пам'яті даних, перший та другий регістри сигнатури та мажоритарно-порівняльний блок. UA 76984 U (54) ВІДМОВОСТІЙКИЙ ПРОЦЕСОРНИЙ ПРИСТРІЙ З ПІДВИЩЕНОЮ ШВИДКОДІЄЮ UA 76984 U UA 76984 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель, що пропонується, належить до мікропроцесорної техніки та систем управління (СУ) і може бути використана у складних відповідальних об'єктах, для яких нормуються високі показники відмовостійкості, надійності й життєздатності у таких галузях як медицина, енергетика, космонавтика, безперервні виробництва та пристрої спеціального призначення. Сучасні СУ у складних об'єктах частіше будуються як системи з програмним управлінням (СПУ), основою яких є мікропроцесорний пристрій. Відомий пристрій підвищення завадостійкості систем з програмним управлінням, який складається з мікропроцесора, що має Μ невідповідальних виходів, які водночас є виходами пристрою, вхід скидання (реініціалізації) мікропроцесора, через логічний елемент АБО, зв'язаний з виходами блоків скидання по зниженню напруги, скидання по тайм-ауту та скидання по включенню, два додаткових регістри, Ν+1 входи першого додаткового регістра підключено до N відповідальних виходів та Ν+1-ого додаткового виходу мікропроцесора, N+2-ий вхід (скидання) першого додаткового регістра з'єднано з виходом блока скидання по включенню, N виходів першого додаткового регістра є відповідальними виходами пристрою, а також підключені до N входів другого додаткового регістра, N+1-ий вхід якого підключено до додаткового N+2-ого виходу мікропроцесора, N додаткових входів якого підключено до N виходів другого додаткового регістра [1]. Недоліки пристрою підвищення завадостійкості систем з програмним управлінням: наявність блоків скидання по зниженню напруги та скидання по тайм-ауту, що при неприпустимому знижені напруги та несанкціонованому зациклюванні програми призводить до скидання (реініціалізації) мікропроцесора; неможливість контролю функціонування мікропроцесора розпізнавання помилок, коректності виконання програми, внаслідок чого при виникненні помилок зменшується швидкість його роботи. Найбільш близьким за технічною суттю та результатом, що досягається, є пристрій архітектура мікропроцесора з визначенням одиничної помилки, який складається з лічильника команд, регістра копії лічильника команд, блока регістрів загального призначення, блока копії регістрів загального призначення, блока пам'яті програм, блока управління та виконання команд, блока визначення сигнатури, буфера запису, блока пам'яті даних, регістра сигнатури, блока порівняння, при цьому перший вихід лічильника команд, через регістр копії лічильника команд, з'єднано з першим входом, другий вихід з'єднано з першим входом блока визначення сигнатури, а третій вихід, через блок пам'яті програм, з'єднано з першим входом блока управління та виконання команд, перший вихід якого з'єднано з другим входом лічильника команд, а другий вихід з'єднано з входом буфера запису, вихід якого, через блок пам'яті даних, з'єднано з другим входом блока управління та виконання команд, третій вихід якого з'єднано з першим входом блока регістрів загального призначення, перший вихід якого, через блок копії регістрів загального призначення, з'єднано з другим входом, а другий вихід - з третім входом блока управління та виконання програм та з другим входом блока визначення сигнатури, вихід якого з'єднано з першим входом блока порівняння та, через регістр сигнатури, з другим входом блока порівняння, вихід якого з'єднано з четвертим входом блока управління та виконання команд, четвертий вихід якого з'єднано з третім входом блока визначення сигнатури [2]. Недоліки найближчого аналога - із-за наявності блоків порівняння, визначення сигнатури, регістра сигнатури, регістра копії лічильника команд та блока копії регістрів загального призначення - необхідно кожну команду (набір інструкцій) повторно додатково виконувати два рази при кожному виявлені помилки (нерівності двох сигнатур) у функціонуванні мікропроцесора, що призводить до значного зниження швидкості, особливо при великій вірогідності невірного виконання команди, що є не завжди можливим для застосувань, які потребують підвищеної швидкодії. Задачею корисної моделі є створення відмовостійкого процесорного пристрою з підвищеною швидкодією, в якому шляхом введення другого регістра сигнатури та мажоритарнопорівняльного блока, а також нових взаємозв'язків забезпечено підвищення швидкодії процесорного пристрою незалежно від вірогідності помилки виконання команди, при заданій відмовостійкості. Поставлена задача вирішується тим, що у відмовостійкий процесорний пристрій з підвищеною швидкодією, який складається з лічильника команд, регістра копії лічильника команд, блока регістрів загального призначення, блока копії регістрів загального призначення, блока пам'яті програм, блока управління та виконання команд, блока визначення сигнатури, буфера запису, блока пам'яті даних, першого регістра сигнатури, при цьому перший вихід лічильника команд, через регістр копії лічильника команд, з'єднано з першим входом, другий вихід з'єднано з першим входом блока визначення сигнатури, а третій вихід, через блок пам'яті 1 UA 76984 U 5 10 15 20 25 30 35 40 45 програм, з'єднано з першим входом блока управління та виконання команд, перший вихід якого з'єднано з другим входом лічильника команд, а другий вихід з'єднано з входом буфера запису, перший вихід якого, через блок пам'яті даних, з'єднано з другим входом блока управління та виконання команд, третій вихід якого з'єднано з першим входом блока регістрів загального призначення, перший вихід якого, через блок копії регістрів загального призначення, з'єднано з другим входом, а другий вихід - з третім входом блока управління та виконання програм та з другим входом блока визначення сигнатури, третій вхід якого з'єднано з четвертим виходом блока управління та виконання програм, а вихід - з входом першого регістра сигнатури, згідно з корисною моделлю, уведено другий регістр сигнатури та мажоритарно-порівняльний блок, при цьому другий вихід буфера запису з'єднано з четвертим входом блока визначення сигнатури, вихід якого додатково з'єднано з першим входом мажоритарно-порівняльного блока, вихід першого регістра сигнатури з'єднано з другим входом та, через другий регістр сигнатури, з третім входом мажоритарно-порівняльного блока, вихід якого з'єднано з четвертим входом блока управління та виконання програм. Технічний ефект запропонованого пристрою. Спрощений алгоритм функціонування найближчого аналога наведено на фіг. 1. У стані 0 виконується копіювання вмісту лічильника команд та регістрів загального призначення (відповідно у регістр копії лічильника команд та блок копії регістрів загального призначення), далі виконується N команд - до наповнення буфера запису, з одночасною модифікацією всіх основних регістрів. По вмісту регістрів та буфера запису обчислюється сигнатура, яка записується у регістр сигнатури. Далі поновлюється вміст лічильника команд та регістрів загального призначення з їх відповідних копій, після чого пристрій переходить у стан 1. У стані 1 виконується N тих самих команд, що й у стані 0, доки не наповниться буфер запису, з одночасною модифікацією даних всіх основних регістрів. По вмісту регістрів та буфера запису визначається нова поточна сигнатура, яка порівнюється з контрольною, з регістра сигнатури. Якщо сигнатури рівні - помилки немає, дані з буфера запису записуються у блок пам'яті даних, пристрій переходить у стан 0, де будуть виконані наступні команди. При виявлені помилки (сигнатури не рівні) поточна сигнатура записується у регістр сигнатури, поновлюється вміст лічильника команд та регістрів загального призначення з їх відповідних копій, після чого пристрій переходить у стан 0 і повторно виконує команди, доки не буде двох однакових сигнатур поспіль. При такому алгоритмі вірогідність виконання команди за n=2k кроків 2 2 k-1 P(n=2k)=q (1-q ) , де q=p-1 - вірогідність виконання команди без помилки, p - вірогідність виконання команди з помилкою. Структура найближчого аналога може функціонувати по іншому - модифікованому алгоритму, наведеному на фіг. 2. Стан 0 не відрізняється від початкового алгоритму (фіг. 1). Але, у стані 1, при виявлені помилки (сигнатури не рівні) поточна сигнатура записується у регістр сигнатури, поновлюються лічильник команд та регістри загального призначення з їх відповідних копій, після чого пристрій, на відміну від не модифікованого алгоритму, переходить у стан 1. Таким чином, модифікований алгоритм функціонування дозволяє виконувати команди, доки два рази поспіль їх результати будуть без помилок, тобто з однаковою сигнатурою. Вірогідність виконання команди за η кроківпри такому алгоритмі 2 P(2)=q , при n=2; 2 Ρ (n) =pq (1-F(n-3)), при n>2, Fn i. n 50 55 i1 де Недоліком найближчого аналога, із-за того, що при помилці кожна команда повторно виконується два рази, а при модифікованому алгоритмі до двох однакових сигнатур поспіль, є його повільність, особливо при великій вірогідності невірного виконання команди, що не завжди можливо для застосувань, які потребують підвищену швидкодію. Завдяки уведенню у пропоновану корисну модель другого регістра сигнатури та мажоритарно-порівняльного блока, дозволено порівняння трьох останніх сигнатур з їхньою мажорантою й виконання команд, доки дві з останніх трьох сигнатур (включаючи й щойно визначену) не співпадуть, в наслідок чого скорочується кількість кроків, що виконуються, незалежно від вірогідності помилки підвищується швидкодія процесорного пристрою, а також завдяки новому зв'язку між буфером запису та блоком визначення сигнатури пристрій дозволяє контролювати дані у буфері запису, що додатково підвищує його відмовостійкість. Суть корисної моделі пояснюється фіг. 3, де 1 - лічильник команд, 2 - регістр копії лічильника команд, 3 - блок регістрів загального призначення, 4 - блок копії регістрів загального 2 UA 76984 U 5 10 15 20 25 30 35 40 45 50 55 60 призначення, 5 - блок пам'яті програм, 6 - блок управління та виконання команд, 7 - блок визначення сигнатури, 8 - буфер запису, 9 - блок пам'яті даних, 10 - перший регістр сигнатури, 11 - другий регістр сигнатури, 12 - мажоритарно-порівняльний блок, при цьому перший вихід лічильника 1 команд, через регістр 2 копії лічильника команд, з'єднано з першим входом, другий вихід з'єднано з першим входом блока 7 визначення сигнатури, а третій вихід, через блок 5 пам'яті програм, з'єднано з першим входом блока 6 управління та виконання команд, перший вихід якого з'єднано з другим входом лічильника 1 команд, а другий вихід з'єднано з входом буфера 8 запису, перший вихід якого, через блок 9 пам'яті даних, з'єднано з другим входом блока 6 управління та виконання команд, третій вихід якого з'єднано з першим входом блока 3 регістрів загального призначення, перший вихід якого, через блок 4 копії регістрів загального призначення, з'єднано з другим входом, а другий вихід - з третім входом блока 6 управління та виконання програм та з другим входом блока 7 визначення сигнатури, третій вхід якого з'єднано з четвертим виходом блока 6 управління та виконання програм, а вихід - з входом першого регістра 10 сигнатури, другий вихід буфера 8 запису з'єднано з четвертим входом блока 7 визначення сигнатури, вихід якого додатково з'єднано з першим входом мажоритарнопорівняльного блока 12, вихід першого регістра 10 сигнатури з'єднано з другим входом та, через другий регістр 11 сигнатури, з третім входом мажоритарно-порівняльного блока 12, вихід якого з'єднано з четвертим входом блока 6 управління та виконання програм. Пристрій працює таким чином. Виконання команди починається зі збереження значення лічильника 1 команд у регістрі 2 копії лічильника команд, а також збереження значень основних регістрів з блока 3 регістрів загального призначення у блока 4 копії регістрів загального призначення. З блока 5 пам'яті програм вибираються команди, які виконуються у блоці 6 управління та виконання команд, при цьому відповідно змінюється вміст лічильника 1 команд та регістрів блока 3. Значення даних лічильника 1 команд та блока 3 регістрів загального призначення, по закінченню виконання команди, подаються на блок 7 визначення сигнатури, до якого, також, подаються дані з буфера 8 запису, які у ньому накопичуються перед записом у блок 9 пам'яті даних. Результат сигнатури обчислюється, та записується у перший регістр 10 сигнатури, попереднє значення сигнатури з якого записується у другий регістр 11 сигнатури. Далі відновлюються значення лічильника 1 команд з регістра 2 копії лічильника команд, а також значення блока 3 регістрів загального призначення з блока 4 копії регістрів загального призначення. Виконується та сама команда, з відповідною модифікацією лічильника 1 команд, регістрів загального призначення у блоці 3, буфера 8 запису, дані з яких подаються до блока 7 визначення сигнатури, який обчислює нову поточну сигнатуру. Нова сигнатура порівнюється з двома попередніми, відповідно з першого регістра 10 та другого регістра 11 сигнатури за допомогою мажоритарно-порівняльного блока 12. Якщо поточна сигнатура співпадає з однією з двох останніх - вважається, що результат виконання команди вірний, значення з буфера 8 запису записуються у блок 9 пам'яті даних. Якщо поточна сигнатура не співпадає з однією з попередніх - вважається, що результат невірний, відновлюються значення лічильника 1 команд та блока 2 регістрів загального призначення, виконання команди повторюється, доки поточна сигнатура не співпаде з однією з двох попередніх. Спрощений алгоритм функціонування відмовостійкого процесорного пристрою з підвищеною швидкодією наведено на фіг. 4. Стан 0 майже не відрізняється від аналогічного стану прототипу (фіг. 1, 2). У ньому виконується копіювання вмісту лічильника 1 команд та регістрів загального призначення блока 3 (відповідно у регістр 2 копії лічильника команд та блок 4 копії регістрів загального призначення), далі виконується N команд, доки не наповниться буфер 8 запису, з одночасною модифікацією всіх основних регістрів блоків 1, 3. По вмісту регістрів блоків 1, 3 та буфера 8 запису обчислюється сигнатура, яка записується у перший регістр 10 сигнатури. Далі поновлюється вміст лічильника 1 команд та блока 3 регістрів загального призначення з їх відповідних копій блоків 2 та 4, після чого пристрій переходить у стан 1. У стані 1 виконується N тих самих команд, що й у стані 0, до наповнення буфера 8 запису, з одночасною модифікацією всіх основних регістрів - блоків 1, 3. По вмісту цих регістрів та буфера 8 запису у блоці 7 визначення сигнатури обчислюється нова поточна сигнатура, яка, за допомогою мажоритарно-порівняльного блока 12, порівнюється з контрольними сигнатурами з регістрів 10 та 11 сигнатури. Якщо поточна сигнатура співпадає з сигнатурою хоч одного з них помилки немає, дані з буфера 8 запису записуються у блок 9 пам'яті даних, пристрій переходить у стан 0, де буде виконано наступні команди. Якщо поточна сигнатура не співпадає з жодною сигнатурою регістрів сигнатури - помилку виявлено. При цьому у другий регістр 11 сигнатури записується вміст першого регістра 10 сигнатури, у який записується поточна сигнатура, поновлюються дані лічильника 1 команд та 3 UA 76984 U 5 10 15 20 25 30 35 40 45 50 блока 3 регістрів загального призначення з їх відповідних копій - блоків 2 та 4, після чого пристрій переходить у стан 1 і повторно виконує команди, доки не буде двох однакових сигнатур із трьох останніх. Вірогідність виконання команди за n кроків у відмовостійкого процесорного пристрою з підвищеною швидкодією при такому алгоритмі: 2 P(2)=q , при n=2; 2 P(3)=2pq , при n=3; 2 P(4)=2(pq) , при n=4; 2 P(n)=(1-F(n-4)+pF(n-5))(pq) , при n>4. Графік на фіг. 5 демонструє залежність середньої кількості кроків N пристрою на виконання команди від вірогідності помилки p для: 1 - найближчого аналога з алгоритмом функціонування згідно з фіг. 1; 2 - найближчого аналога з алгоритмом функціонування згідно з фіг. 2; 3 відмовостійкого процесорного пристрою з підвищеною швидкодією з алгоритмом функціонування згідно з фіг. 4. Графік на фіг. 6 демонструє відносне зменшення кількості кроків на виконання команди залежно від вірогідності помилки для: 2 - найближчого аналога з алгоритмом функціонування згідно з фіг. 2; 3 - відмовостійкого процесорного пристрою з підвищеною швидкодією з алгоритмом функціонування згідно з фіг. 4, найближчого аналога з алгоритмом функціонування згідно з фіг. 1. Таким чином, запропонований відмовостійкий процесорний пристрій з підвищеною швидкодією при будь-якій вірогідності помилки виконання команд дозволяє скоротити кількість кроків на їх виконання й, як наслідок, підвищити швидкодію, при заданій відмовостійкості. Джерела інформації:. 1. Пат 67752 Україна, МПК(2006.01) G06F 12/08. Пристрій підвищення завадостійкості систем з програмним управлінням / Гунченко Ю.О., Мартинюк СМ., Лєнков СВ., Банзак О.В., Омельченко О.С, Купрацевич А.В.; власник Одеський національний університет ім. І.І. Мечникова. - № u201107423, заявл. 14.06.2011, опубл. 12.03.2012, Бюл. № 5. 2. Pat. 6,571,363 USA, МПК (20060101) G06F 11/27. Single event upset tolerant microprocessor architecture. Steiss; Donald E. May 27, 2003, 12 p. ФОРМУЛА КОРИСНОЇ МОДЕЛІ Відмовостійкий процесорний пристрій з підвищеною швидкодією, який містить лічильник команд, регістр копії лічильника команд, блок регістрів загального призначення, блок копії регістрів загального призначення, блок пам'яті програм, блок управління та виконання команд, блок визначення сигнатури, буфер запису, блок пам'яті даних, перший регістр сигнатури, при цьому перший вихід лічильника команд, через регістр копії лічильника команд, з'єднано з першим входом, другий вихід з'єднано з першим входом блока визначення сигнатури, а третій вихід, через блок пам'яті програм, з'єднано з першим входом блока управління та виконання команд, перший вихід якого з'єднано з другим входом лічильника команд, а другий вихід з'єднано з входом буфера запису, перший вихід якого, через блок пам'яті даних, з'єднано з другим входом блока управління та виконання команд, третій вихід якого з'єднано з першим входом блока регістрів загального призначення, перший вихід якого, через блок копії регістрів загального призначення, з'єднано з другим входом, а другий вихід - з третім входом блока управління та виконання програм та з другим входом блока визначення сигнатури, третій вхід якого з'єднано з четвертим виходом блока управління та виконання програм, а вихід - з входом першого регістра сигнатури, який відрізняється тим, що уведено другий регістр сигнатури та мажоритарно-порівняльний блок, при цьому другий вихід буфера запису з'єднано з четвертим входом блока визначення сигнатури, вихід якого додатково з'єднано з першим входом мажоритарно-порівняльного блока, вихід першого регістра сигнатури з'єднано з другим входом та, через другий регістр сигнатури, з третім входом мажоритарно-порівняльного блока, вихід якого з'єднано з четвертим входом блока управління та виконання програм. 4 UA 76984 U 5 UA 76984 U 6 UA 76984 U 7 UA 76984 U Комп’ютерна верстка Г. Паяльніков Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 8

ДивитисяДодаткова інформація

Назва патенту англійськоюFault-tolerant processor device with enhanced processing speed

Автори англійськоюHunchenko Yurii Oleksandrovych, Lenkov Serhii Vasyliovych, Kobozeva Alla Anatoliivna, Martyniuk Serhii Mykhailovych, Borysenko Iryna Ivanivna

Назва патенту російськоюОтказоустойчивое процессорное устройство с повышенным быстродействием

Автори російськоюГунченко Юрий Александрович, Ленков Сергей Васильевич, Кобозева Алла Анатольевна, Мартинюк Сергей Михайлович, Борисенко Ирина Ивановна

МПК / Мітки

МПК: G06F 11/27

Мітки: підвищеною, процесорний, пристрій, відмовостійкий, швидкодією

Код посилання

<a href="https://ua.patents.su/10-76984-vidmovostijjkijj-procesornijj-pristrijj-z-pidvishhenoyu-shvidkodiehyu.html" target="_blank" rel="follow" title="База патентів України">Відмовостійкий процесорний пристрій з підвищеною швидкодією</a>

Попередній патент: Спосіб одержання м’якого препарату ректального або вагінального введення

Наступний патент: Спосіб збільшення ресурсу термоелектролітичного перетворювача вологості газу

Випадковий патент: Система живлення повітрям двигуна з вільним газотурбінним наддувом