Аналоговий інтерфейс для інформаційно-вимірювальної системи з індуктивними датчиками переміщення

Номер патенту: 78475

Опубліковано: 25.03.2013

Автори: Квасніков Володимир Павлович, Осмоловський Олександр Іванович, Кулик Микола Сергійович, Орнатський Дмитро Петрович, Харченко Володимир Петрович, Ільченко Володимир Миколайович

Формула / Реферат

1. Аналоговий інтерфейс для інформаційно-вимірювальної системи з індуктивними датчиками переміщення, що містить генератор тестових та керуючих сигналів з протифазними виходами, тестовий вихід якого сполучений з індуктивним датчиком, а керуючі виходи через регулятор фази зв'язані з фазочутливим випрямлячем, вихід якого є виходом аналогового інтерфейсу, а також вимірювальний підсилювач, вхідні лінії зв'язку якого зв'язані з індуктивним датчиком, а вихід - з фазочутливим випрямлячем, який відрізняється тим, що для підвищення точності введено диференціальний мультиплексор, через який вхід вимірювального підсилювача з резисторами у своїх вхідних лініях зв'язку з'єднаний з протифазними виходами індуктивного датчиком, введено перетворювач струм-напруга, вхід якого зв'язаний з індуктивним датчиком та протифазним виходом генератора тестових та керуючих сигналів з протифазними виходами, а вихід - із входом диференціального мультиплексора, вхід диференціального мультиплексора зв'язаний з протифазними виходами генератора тестових та керуючих сигналів з протифазними виходами, а вимірювальний підсилювач виконано у вигляді підсилювача перехідного опору з напругою на виході, пропорційною вхідному струму, протифазні виходи якого підключені до входів диференціального мультиплексора, а регулятор фази виконано у вигляді цифрового мультиплексора.

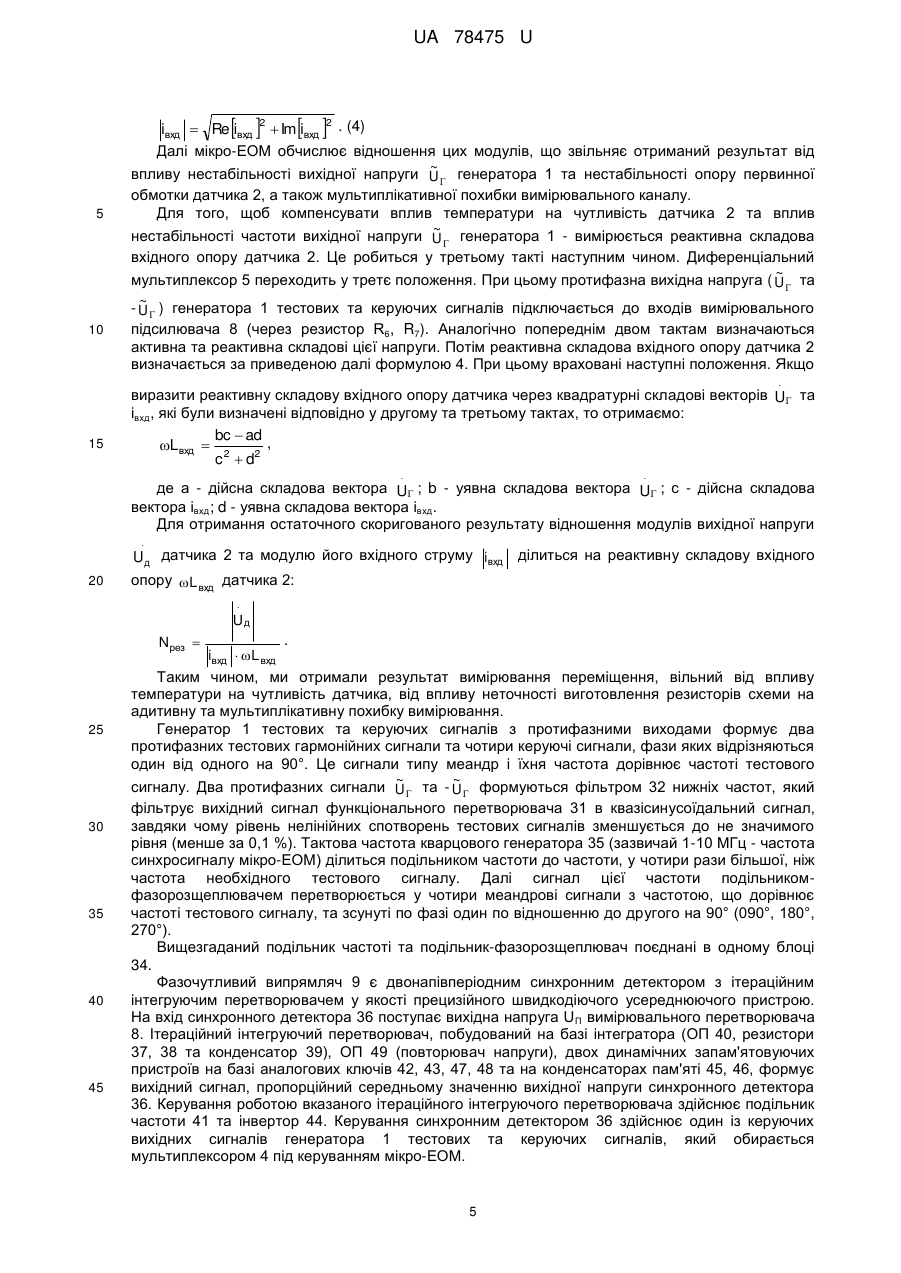

2. Аналоговий інтерфейс за п. 1, який відрізняється тим, що у його вимірювальному підсилювачі відповідно неінвертуючий вхід вимірювального підсилювача зв'язаний із входами першого і другого аналогових ключів, вихід першого аналогового ключа під'єднаний через перший резистор до виходу першого операційного підсилювача (ОП), а також через третій аналоговий ключ - до інвертуючого входу першого ОП та до виходу четвертого аналогового ключа, вхід четвертого аналогового ключа під'єднаний до виходу другого аналогового ключа та через другий резистор - до виходу першого ОП, інвертуючий вхід першого ОП під'єднаний до загальної точки схеми, інвертуючий вхід вимірювального підсилювача зв'язаний із входами п'ятого і шостого аналогових ключів, вихід п'ятого аналогового ключа підключений до виходу першого аналогового ключа та через сьомий аналоговий ключ - до інвертуючого входу другого ОП, який через восьмий аналоговий ключ під'єднаний до виходів другого та шостого аналогових ключів та через послідовно з'єднані третій резистор та дев'ятий аналоговий ключ - до виходу другого ОП, вихід другого ОП, крім того, через десятий аналоговий ключ під'єднаний до входу одинадцятого аналогового ключа та через четвертий резистор - до виходу п'ятого аналогового ключа, вихід одинадцятого аналогового ключа з'єднаний із першим входом суматора та з виходом дванадцятого аналогового ключа, вхід якого під'єднаний до третього резистора та входу дев'ятого аналогового ключа, вихід суматора є виходом вимірювального підсилювача, інвертуючий вхід другого ОП під'єднаний до загальної точки схеми, при цьому керуючі входи першого, третього, шостого, восьмого, дев'ятого та дванадцятого аналогових ключів під'єднані до першого керуючого входу вимірювального підсилювача, керуючі входи другого, четвертого, п'ятого, сьомого, десятого та одинадцятого аналогових ключів зв'язані з керуючим входом вимірювального підсилювача через інвертор, вихід першого ОП через тринадцятий аналоговий ключ під'єднаний до інвертуючого входу суматора, а другий керуючий вхід вимірювального підсилювача під'єднаний до керуючого входу тринадцятого аналогового ключа.

3. Аналоговий інтерфейс за п. 1, який відрізняється тим, що його генератор тестових та керуючих сигналів з протифазними виходами має послідовно з'єднані генератор з вихідним сигналом прямокутної форми, подільник-фазорозщеплювач, виходи якого є виходами керуючих сигналів, перетворювач прямокутної напруги у трикутну, виконаний на базі реального інтегратора, перетворювач трикутної напруги у квазісинусоїдальну, виконаний з використанням кусково-лінійної апроксимації, фільтр нижніх частот, протифазні виходи якого є виходом тестового сигналу, причому один із виходів подільника-фазорозщеплювача з'єднаний із входом перетворювача прямокутної напруги у трикутну.

4. Аналоговий інтерфейс за п. 1, який відрізняється тим, що його фазочутливий випрямляч має на вході синхронний детектор, керуючий вхід якого підключений до схеми вибору фази керуючого сигналу, а вихід через перший резистор під'єднаний до інвертуючого входу першого ОП, неінвертуючий вхід якого під'єднаний до загальної точки схеми, вихід першого ОП через перший конденсатор під'єднаний до інвертуючого входу першого ОП та через другий резистор - до виходу повторювача напруги, вихід повторювача напруги є виходом фазочутливого випрямляча, вхід повторювача напруги під'єднаний до виходів першого та другого ключів, входи яких підключені безпосередньо до виходу третього та четвертого ключів а також через другий та третій конденсатори - до загальної точки схеми, входи першого та четвертого ключів під'єднані до виходу подільника частоти, який через інвертор зв'язаний з керуючими входами другого та третього ключів, а вхід подільника частоти під'єднаний до першого виходу подільника-фазорозщеплювача.

Текст

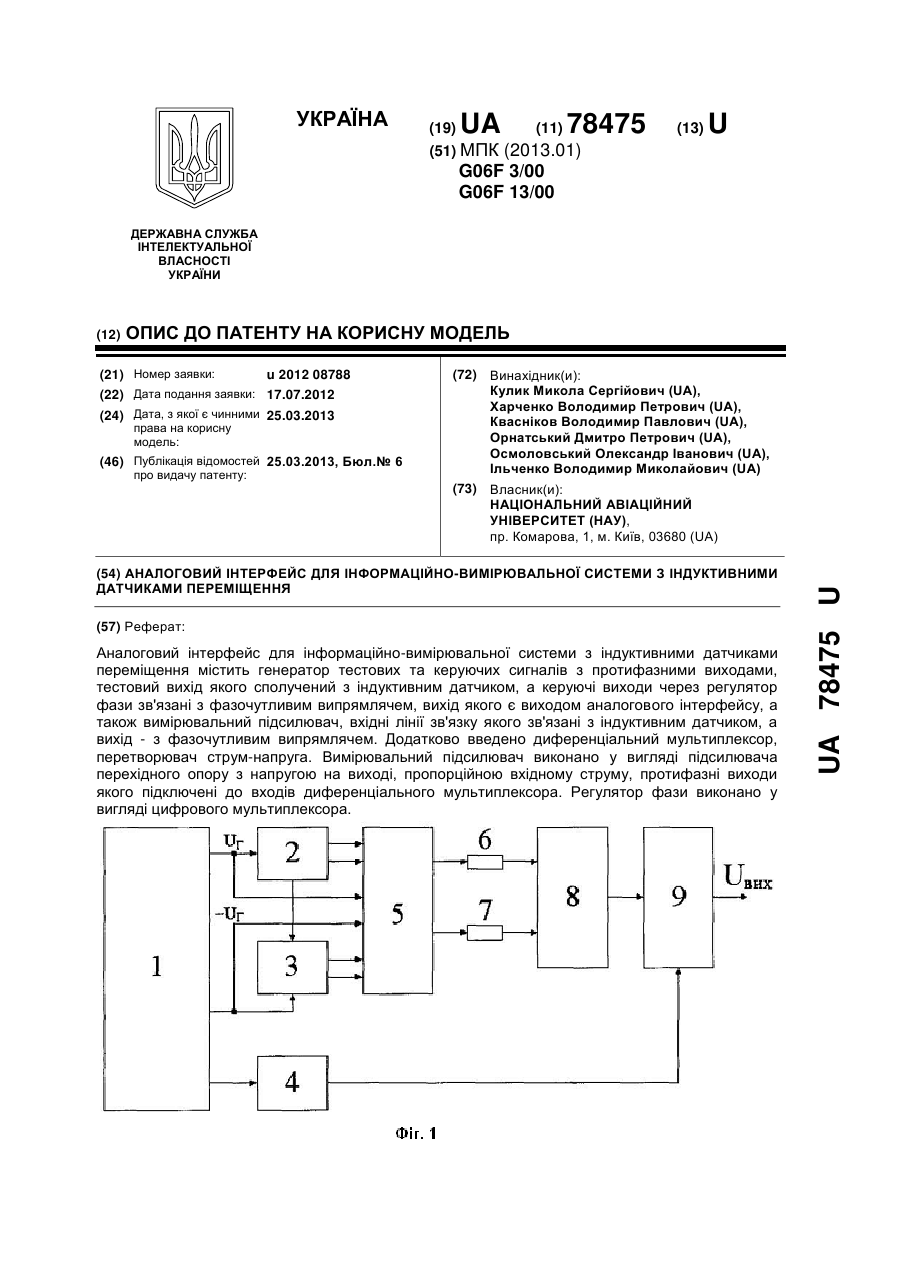

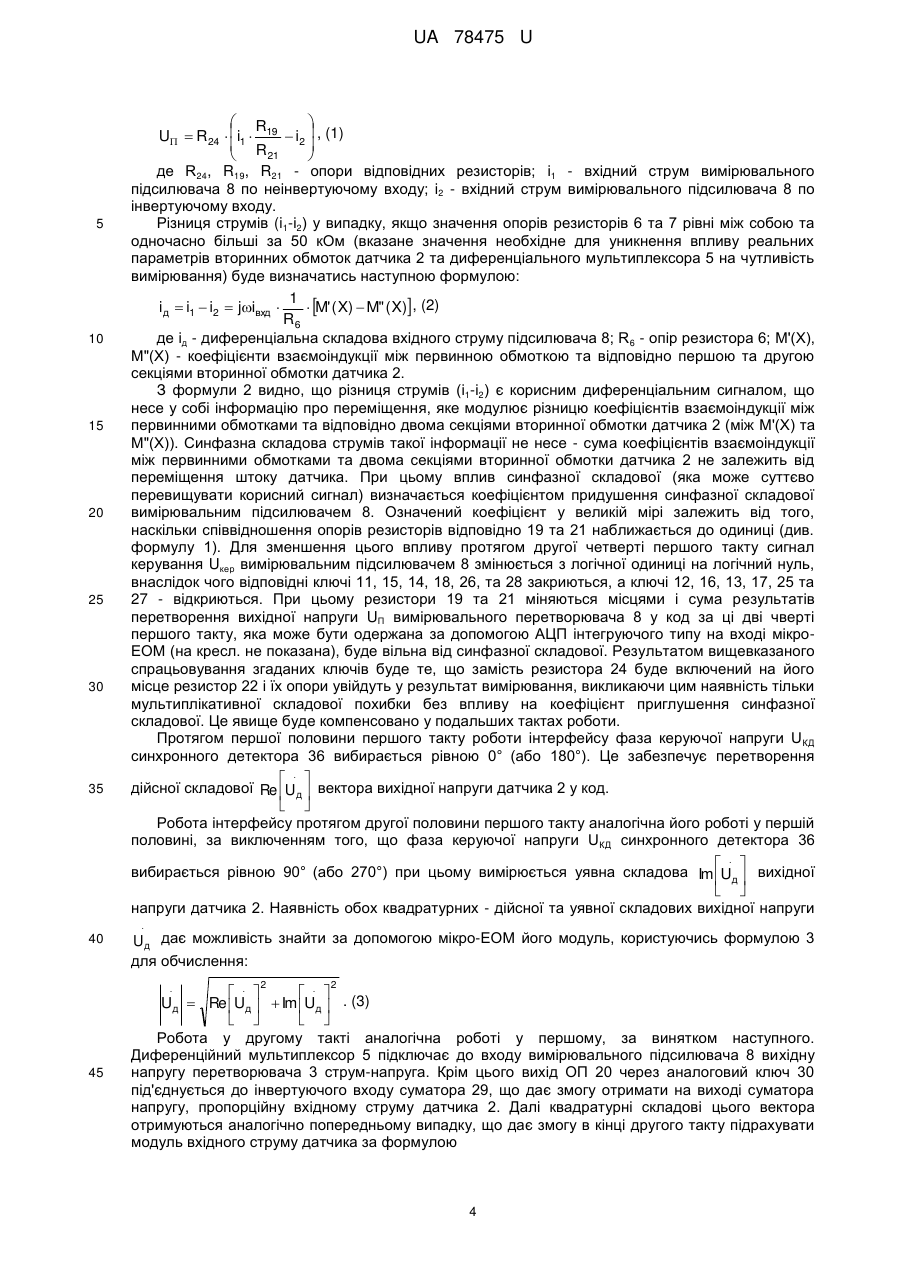

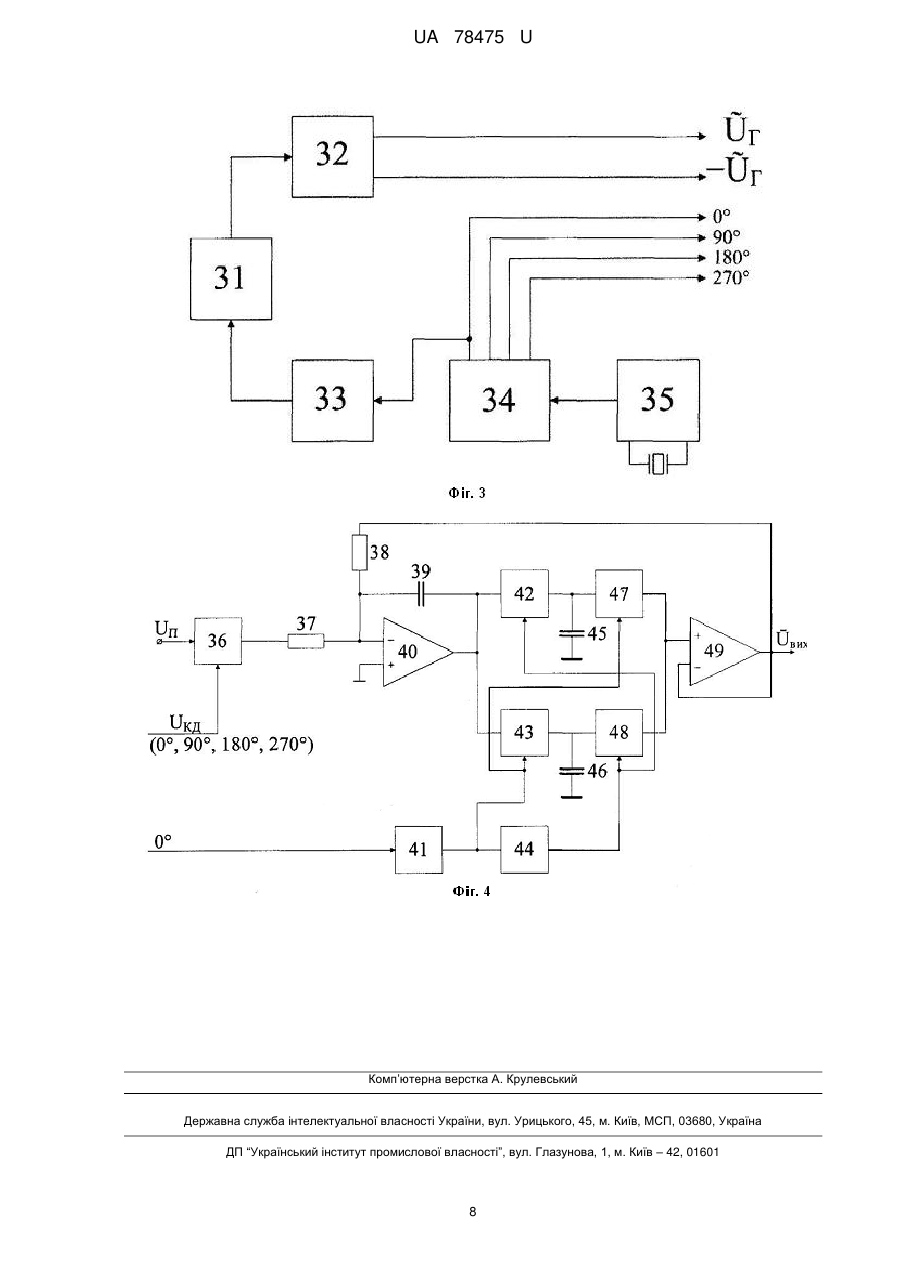

Реферат: Аналоговий інтерфейс для інформаційно-вимірювальної системи з індуктивними датчиками переміщення містить генератор тестових та керуючих сигналів з протифазними виходами, тестовий вихід якого сполучений з індуктивним датчиком, а керуючі виходи через регулятор фази зв'язані з фазочутливим випрямлячем, вихід якого є виходом аналогового інтерфейсу, а також вимірювальний підсилювач, вхідні лінії зв'язку якого зв'язані з індуктивним датчиком, а вихід - з фазочутливим випрямлячем. Додатково введено диференціальний мультиплексор, перетворювач струм-напруга. Вимірювальний підсилювач виконано у вигляді підсилювача перехідного опору з напругою на виході, пропорційною вхідному струму, протифазні виходи якого підключені до входів диференціального мультиплексора. Регулятор фази виконано у вигляді цифрового мультиплексора. UA 78475 U (12) UA 78475 U UA 78475 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до області інформаційно-вимірювальної техніки, а саме до аналогових інтерфейсів, і може бути застосована у контрольно-вимірювальних системах, вбудованих у різні технологічні процеси загальнотехнічного і спеціального призначення, у яких первинними перетворювачами є індуктивні датчики переміщення. Індуктивні датчики переміщення широко застосовуються завдяки високій надійності, порівняно низькій вартості та практично необмеженому терміну використання. їм властиві також завадозахищеність, точність, чутливість. Основні похибки у інформаційно-вимірювальних системах з виростанням індуктивних датчиків переміщення - це похибки вимірювання. При цьому значний вклад у похибку вимірювання (окрім інструментальних складових) вносять похибки від дестабілізуючих факторів в умовах вимірювання - таких, як температура, електромагнітні та синфазні завади. Ці фактори найбільше впливають на датчик та вхідні каскади аналогового інтерфейсу. Зазвичай інформативним сигналом при передачі сигналу через аналоговий інтерфейс є диференціальний сигнал. Присутній у таких системах синфазний сигнал являє собою заваду, яка із-за паразитних параметрів вхідної ланки перетворюється в диференціальний сигнал, чим також знижується точність вимірювання. Синфазний сигнал - це складова аналогового сигналу, яка є наявною на усіх інформаційних виводах датчика, причому з одним знаком, амплітудою та фазою. Коли сигнал передається з використанням напруги, синфазний сигнал зазвичай визначається як півсума напруг Uсинф.=(U1+U2)/2. Синфазний сигнал можна розрахувати, знаючи величину диференціального сигналу (U диф) та величину аналогового сигналу (U) на одному з виводів: Uсинф=U- Uдиф/2. Електронні системи кабельного зв'язку в основному побудовані за принципом передачі диференціального сигналу через кабелі, що складаються із звитих пар. Відомі аналогові інтерфейси (двупровіднi, несиметричні), у яких змінна складова синфазного сигналу зменшується зокрема ізолюванням вимірювального каналу (див. Mark Stitt, David Kimst. Ic Building Blocks form Complete Isolated 4-20ma Current-Loop Systems/ Burr-Brown Corporation, Application bulletin. - 1992). Це робиться тому, що цю складову важко розділити з корисним сигналом (після перетворення синфазної в диференціальну), особливо якщо вони лежать у одній смузі частот і відповідно неможливо здійснити вказане розділення з використанням фільтрації. Одним із основних засобів боротьби із негативним впливом синфазного сигналу на корисний є використання у вхідній ланці аналогового інтерфейсу вимірювальних підсилювачів. Зараз в основному ці підсилювачі є підсилювачами типу напруга-напруга на основі диференціального підсилювача (з напругою на виході, пропорційною напрузі на вході) - операційний підсилювач (ОП) з двома парами узгоджених резисторів. При цьому розбаланс означених пар резисторів призводить до суттєвого зниження коефіцієнта приглушення синфазної складової вхідного сигналу. Відомі технічні рішення, у яких цей недолік зменшують використовуванням попереднього підсилення диференціальної складової сигналу, не змінюючи синфазного (див., наприклад, Проектирование и применение операционных усилителей. / Под ред. Дж. Грэма, Дж. Тоби, Л. Хьюлсмана. Пер. с англ. - М.: Мир, 1974. - 510 с). Однак за високих рівнів диференціального сигналу ефективність такого рішення зменшується. Суттєвим недоліком такого рішення є також те, що, в усіх каскадах підсилення використовують неінвертуюче включення ОП. При цьому при підвищенні частоти тестового сигналу зменшується коефіцієнт придушення синфазного сигналу самим ОП (відповідно підсилюється негативний вплив синфазної завади). Наприклад, типове значення частоти тестового сигналу при ініціалізації індуктивних датчиків переміщення становить 10 кГц. На цій частоті власний коефіцієнт придушення синфазного сигналу у операційного підсилювача загального призначення становить 20-40 дБ, що призведе до похибок у декілька відсотків. Існують також вимірювальні підсилювачі напруги, які побудовані виключно на базі інвертую чого включення ОП, наприклад на базі інвертую чого підсилювача (інвертора) та суматора, але в цьому випадку вплив неточності резисторів стає ще більшим. Похибки від дестабілізуючих факторів в умовах вимірювання, а саме від впливу температури оточуючого середовища на чутливість індуктивного датчика переміщення, теж серйозно враховуються при розробці аналогових інтерфейсів. Зазвичай для корекція температурної похибки індуктивного датчика переміщення користуються методом додаткових вимірювань, що потребує відповідно і додаткового каналу вимірювання. Необхідним також є і наявність масиву апріорної інформації відносно функцій впливу температури оточуючого середовища на чутливість датчика, який до того ж потребує періодичного оновлення. Найбільш близьким до рішення, що заявляється, є аналоговий інтерфейс для інформаційновимірювальної системи з індуктивними датчиками переміщення, що містить генератор тестових та керуючих сигналів, тестовий вихід якого сполучений з індуктивним датчиком, а керуючі 1 UA 78475 U 5 10 15 20 25 30 35 40 45 50 55 60 виходи через регулятор фази зв'язані з фазочутливим випрямлячем, вихід якого є виходом аналогового інтерфейсу, а також вимірювальний підсилювач, виконаний як підсилювач напруганапруга з напругою на виході, пропорційною напрузі на вході, вхідні лінії зв'язку якого зв'язані з індуктивним датчиком, а вихід - з фазочутливим випрямлячем (див. Аш Дж. и соавторы. Датчики измерительных систем: В 2-х книгах. Кн. 1. Пер. с франц. - Μ.: Мир, 1992. - 480 с). Недоліком прототипу є те, що вищевказані негативні впливи наявності у корисному сигналі синфазної складової на точність вимірювання а також впливу температури оточуючого середовища на чутливість датчика у ньому не подолані. Запропоновані шляхи компенсації температурної похибки роботою на краях частотного діапазону не є прийнятними тому, що при підвищенні частоти збільшується вплив паразитних ємностей, а при зниженні падає чутливість. Задача корисної моделі - розробити аналоговий інтерфейс для інформаційно-вимірювальної системи з індуктивними датчиками переміщення, у якому зменшено вплив синфазної складової корисного сигналу на точність вимірювання та враховано вплив температури оточуючого середовища на чутливість датчика і відповідно підвищено точність аналогового інтерфейсу. Поставлена задача вирішується тим, що у аналоговому інтерфейсі для інформаційновимірювальної системи з індуктивними датчиками переміщення, що містить генератор тестових та керуючих сигналів з протифазними виходами, тестовий вихід якого сполучений з індуктивним датчиком, а керуючі виходи через регулятор фази зв'язані з фазочутливим випрямлячем, вихід якого є виходом аналогового інтерфейсу, а також вимірювальний підсилювач, вхідні лінії зв'язку якого зв'язані з індуктивним датчиком, а вихід - з фазочутливим випрямлячем, згідно з корисною моделлю, введено диференціальний мультиплексор, через який вхід вимірювального підсилювача з резисторами у своїх вхідних лініях зв'язку з'єднаний з протифазними виходами індуктивного датчика, введено перетворювач струм-напруга, вхід якого зв'язаний з індуктивним датчиком та протифазним виходом генератора тестових та керуючих сигналів, а вихід - iз входом диференціального мультиплексора, вхід диференціального мультиплексора зв'язаний з протифазними виходами генератора, вимірювальний підсилювач виконано у вигляді підсилювача перехідного опору з напругою на виході, пропорційною вхідному струму (диференціальному), протифазні входи якого підключені до виходів диференціального мультиплексора, а регулятор фази виконано у вигляді цифрового мультиплексора. Запропонована також, згідно з п. 2 формули корисної моделі, можлива схемна реалізація вимірювального підсилювача у аналоговому iнтерфейсі, що заявляється. У запропонованому вимірювальному підсилювачі відповідно неінвертуючий вхід вимірювального підсилювача зв'язаний із входами першого i другого аналогових ключів, вихід першого аналогового ключа під'єднаний через перший резистор до виходу першого ОП, а також через третій аналоговий ключ - до інвертуючого входу першого ОП та до виходу четвертого аналогового ключа, вхід четвертого аналогового ключа під'єднаний до виходу другого аналогового ключа та через другий резистор - до виходу першого ОП, неінвертуючий вхід першого ОП під'єднаний до загальної точки схеми, інвертуючий вхід вимірювального підсилювача зв'язаний із входами п'ятого і шостого аналогових ключів, вихід п'ятого аналогового ключа підключений до виходу першого аналогового ключа та через сьомий аналоговий ключ - до інвертуючого входу другого ОП, який через восьмий аналоговий ключ під'єднаний до виходів другого та шостого аналогових ключів та через послідовно з'єднані третій резистор та дев'ятий аналоговий ключ - до виходу другого ОП, вихід другого ОП, крім того, через десятий аналоговий ключ під'єднаний до входу одинадцятого аналогового ключа та через четвертий резистор - до виходу п'ятого аналогового ключа, вихід одинадцятого аналогового ключа з'єднаний із входом суматора та з виходом дванадцятого аналогового ключа, вхід якого під'єднаний до третього резистора та входу дев'ятого аналогового ключа, вихід суматора є виходом вимірювального підсилювача, інвертуючий вхід другого ОП під'єднаний до загальної точки схеми, при цьому керуючі входи першого, третього, шостого, восьмого, дев'ятого та дванадцятого аналогових ключів під'єднані до керуючого входу вимірювального підсилювача, керуючі входи другого, четвертого, п'ятого, сьомого, десятого та одинадцятого аналогових ключів зв'язані з керуючим входом вимірювального підсилювача через інвертор, вихід першого ОП через тринадцятий аналоговий ключ під'єднано до інвертуючого входу суматора. Запропонована також, згідно з п. 3 формули корисної моделі, можлива схемна реалізація генератора тестових та керуючих сигналів з протифазними виходами у аналоговому інтерфейсі, що заявляється. Запропонований генератор тестових та керуючих сигналів з протифазними виходами має послідовно з'єднані кварцовий генератор з вихідним сигналом прямокутної форми, подільник-фазорозщеплювач, виходи якого є виходами керуючих сигналів, перетворювач прямокутної напруги у трикутну, виконаний на базі реального інтегратора, перетворювач трикутної напруги у квазісинусоїдальну, виконаний з використанням кусково 2 UA 78475 U 5 10 15 20 25 30 35 40 45 50 55 60 лінійної апроксимації, фільтр нижніх частот, протифазнi виходи якого є виходом тестового сигналу, причому один iз виходів подільника-фазорозщеплювача з'єднаний із входом перетворювача прямокутної напруги у трикутну. Запропонована також, згідно з п. 4 формули корисної моделі, можлива схемна реалізація фазочутливого випрямляча у аналоговому інтерфейсі, що заявляється. Фазочутливий випрямляч має на вході синхронний детектор, керуючий вхід якого підключений до схеми вибору фази керуючого сигналу, а вихід через перший резистор під'єднаний до інвертуючого входу першого ОП, неінвертуючий вхід якого під'єднаний до загальної точки схеми, вихід першого ОП через перший конденсатор під'єднаний до інвертуючого входу першого ОП та через другий резистор - до виходу повторювача напруги, вихід повторювана напруги є виходом фазочутливого випрямляча, вхід повторювана напруги під'єднаний до виходів першого та другого ключів, входи яких підключені безпосередньо до виходу третього та четвертого ключів а також через другий та третій конденсатори - до загальної точки схеми, керуючі входи першого та четвертого ключів під'єднані до виходу подільника частоти, який через інвертор зв'язаний з керуючими входами другого та третього ключів, а вхід подільника частоти під'єднаний до першого виходу подільника-фазорозщеплювача. Суть корисної моделі пояснюється кресленнями на Фіг. 1, Фіг. 2, Фіг. 3, Фіг. 4, наведеними з метою ілюстрації та не обмежуючими обсяг корисної моделі, що заявляється. На кресленнях наведені: на Фіг. 1 - структурна схема аналогового інтерфейсу для інформаційно-вимірювальної системи з індуктивними датчиками переміщення диференціально-трансформаторного типу (LVDT); на Фіг. 2 - функціональна схема вимірювального підсилювача; на Фіг. 3 - структурна схема генератора керуючих та тестових сигналів з протифазними виходами; на Фіг. 4 функціональна схема фазочутливого випрямляча. Позиції на кресленнях відповідають наступним елементам: 1 - генератор керуючих та тестових сигналів з протифазними виходами, 2 - індуктивний датчик переміщення трансформаторного типу з диференціальними вихідними обмотками з диференціальною вихідною напругою Uд і вхідним струмом івхд, 3 - перетворювач струм-напруга, виконаний у вигляді шунта, 4 - цифровий мультиплексор, 5 - диференціальний мультиплексор, 6, 7 - резистори на вході лінії зв'язку, 8 - вимірювальний підсилювач, виконаний як підсилювач перехідного опору з напругою на виході, пропорційною вхідному струму (диференціальному), 9 фазочутливий випрямляч, 10 - інвертор з сигналами відповідно а - на вході та б - на виході, 1118 - аналогові ключі (на КМОП-транзисторах) з підключенням керуючих входів відповідно ключів 11, 14, 17, 18 - до точки а, ключів 12, 13, 16, 17 - до точки б, 19 - резистор, 20 - перший операційний підсилювач, 21, 22 - резистори, 23 - другий операційний підсилювач, 24 - резистор, 25-28 - аналогові ключі, 29 - суматор, 30 - аналоговий ключ, 31 - перетворювач трикутної напруги у квазісинусоїдальну з використанням кусково-лінійної апроксимації, 32 - фільтр нижніх частот, 33 - перетворювач прямокутної напруги у трикутну, 34 - подільник-фазорозщеплювач, 35 - кварцовий генератор з вихідним сигналом прямокутної форми, 36 - синхронний детектор, 37, 38 - резистори, 39 - конденсатор, 40 - операційний підсилювач, 41 - подільник частоти, 42, 43 аналогові ключі, 44 - інвертор, 45, 46 - конденсатори, 47, 48 - аналогові ключі, 49 - повторювач напруги, виконаний на операційному підсилювачі. Запропонований аналоговий інтерфейс працює у три такти. В першому - вимірюється вихідна напруга Uд індуктивного датчика 2, в другому - вхідний струм івхд датчика 2, в третьому реактивна складова опору первинної обмотки датчика 2. На початку першого такту диференціальний мультиплексор 5 підключає до входу вимірювального підсилювача 8 протифазні виходи датчика 2. На виході вимірювального підсилювача 8 формується напруга, пропорційна переміщенню штока датчика 2. Окрім залежності від змірюваного параметра напруга з підсилювача 8 буде залежати також і від співвідношення опорів резисторів 19 та 21 у ланцюзі негативного зворотного зв'язку ОП 20, від значень опорів резисторів 6, 7, які перетворюють вихідну напругу датчика 2 у струм, від значення опору резисторів 22, 24 у ланцюзі негативного зворотного зв'язку ОП 23, а також від параметрів первинної обмотки датчика 2 та від величини вихідної напруги та частоти генератора 1 тестових та керуючих сигналів, та від чутливості суматора 29. Напруга керування Uкер на вході iнвертора 10 (точка а) протягом першої четверті першого такту відповідає значенню логічної одиниці, що відкриває ключі 11, 15, 14, 18, 26, 28. За відкритості цих ключів у ланцюзі негативного зворотного зв'язку ОП 20 буде знаходитись резистор 19. При цьому через резистор 21 вихідний сигнал ОП 20 надходить на інвертуючий вхід ОП 23 і у ланцюзі негативного зворотного зв'язку ОП 23 буде включений резистор 24 і тоді вихідна напруга UП вимірювального підсилювача 8 буде: 3 UA 78475 U 5 10 15 20 25 30 35 R U R 24 i1 19 i2 , (1) R 21 де R24, R19, R21 - опори відповідних резисторів; і1 - вхідний струм вимірювального підсилювача 8 по неінвертуючому входу; і2 - вхідний струм вимірювального підсилювача 8 по інвертуючому входу. Різниця струмів (i1-і2) у випадку, якщо значення опорів резисторів 6 та 7 рівні між собою та одночасно більші за 50 кОм (вказане значення необхідне для уникнення впливу реальних параметрів вторинних обмоток датчика 2 та диференціального мультиплексора 5 на чутливість вимірювання) буде визначатись наступною формулою: 1 i д i1 i2 jівхд M' ( X) M" ( X) , (2) R6 де ід - диференціальна складова вхідного струму підсилювача 8; R 6 - опір резистора 6; М'(Х), М"(Х) - коефіцієнти взаємоіндукції між первинною обмоткою та відповідно першою та другою секціями вторинної обмотки датчика 2. З формули 2 видно, що різниця струмів (і1-і2) є корисним диференціальним сигналом, що несе у собі інформацію про переміщення, яке модулює різницю коефіцієнтів взаємоіндукції між первинними обмотками та відповідно двома секціями вторинної обмотки датчика 2 (між М'(Х) та М"(Х)). Синфазна складова струмів такої інформації не несе - сума коефіцієнтів взаємоіндукції між первинними обмотками та двома секціями вторинної обмотки датчика 2 не залежить від переміщення штоку датчика. При цьому вплив синфазної складової (яка може суттєво перевищувати корисний сигнал) визначається коефіцієнтом придушення синфазної складової вимірювальним підсилювачем 8. Означений коефіцієнт у великій мірі залежить від того, наскільки співвідношення опорів резисторів відповідно 19 та 21 наближається до одиниці (див. формулу 1). Для зменшення цього впливу протягом другої четверті першого такту сигнал керування Uкер вимірювальним підсилювачем 8 змінюється з логічної одиниці на логічний нуль, внаслідок чого відповідні ключі 11, 15, 14, 18, 26, та 28 закриються, а ключі 12, 16, 13, 17, 25 та 27 - відкриються. При цьому резистори 19 та 21 міняються місцями і сума результатів перетворення вихідної напруги UП вимірювального перетворювача 8 у код за ці дві чверті першого такту, яка може бути одержана за допомогою АЦП інтегруючого типу на вході мікроЕОМ (на кресл. не показана), буде вільна від синфазної складової. Результатом вищевказаного спрацьовування згаданих ключів буде те, що замість резистора 24 буде включений на його місце резистор 22 і їх опори увійдуть у результат вимірювання, викликаючи цим наявність тільки мультиплікативної складової похибки без впливу на коефіцієнт приглушення синфазної складової. Це явище буде компенсовано у подальших тактах роботи. Протягом першої половини першого такту роботи інтерфейсу фаза керуючої напруги U КД синхронного детектора 36 вибирається рівною 0° (або 180°). Це забезпечує перетворення дійсної складової Re U д вектора вихідної напруги датчика 2 у код. Робота інтерфейсу протягом другої половини першого такту аналогічна його роботі у першій половині, за виключенням того, що фаза керуючої напруги UКД синхронного детектора 36 вибирається рівною 90° (або 270°) при цьому вимірюється уявна складова Im Uд вихідної напруги датчика 2. Наявність обох квадратурних - дійсної та уявної складових вихідної напруги 40 U д дає можливість знайти за допомогою мікро-ЕОМ його модуль, користуючись формулою 3 для обчислення: 2 45 2 Uд Re Uд Im Uд . (3) Робота у другому такті аналогічна роботі у першому, за винятком наступного. Диференційний мультиплексор 5 підключає до входу вимірювального підсилювача 8 вихідну напругу перетворювача 3 струм-напруга. Крім цього вихід ОП 20 через аналоговий ключ 30 під'єднується до інвертуючого входу суматора 29, що дає змогу отримати на виході суматора напругу, пропорційну вхідному струму датчика 2. Далі квадратурні складові цього вектора отримуються аналогічно попередньому випадку, що дає змогу в кінці другого такту підрахувати модуль вхідного струму датчика за формулою 4 UA 78475 U 5 10 2 2 iвхд Re iвхд Im iвхд . (4) Далі мікро-ЕОМ обчислює відношення цих модулів, що звільняє отриманий результат від ~ впливу нестабільності вихідної напруги U генератора 1 та нестабільності опору первинної обмотки датчика 2, а також мультиплікативної похибки вимірювального каналу. Для того, щоб компенсувати вплив температури на чутливість датчика 2 та вплив ~ нестабільності частоти вихідної напруги U генератора 1 - вимірюється реактивна складова вхідного опору датчика 2. Це робиться у третьому такті наступним чином. Диференціальний ~ мультиплексор 5 переходить у третє положення. При цьому протифазна вихідна напруга ( U та ~ - U ) генератора 1 тестових та керуючих сигналів підключається до входів вимірювального підсилювача 8 (через резистор R6, R7). Аналогічно попереднім двом тактам визначаються активна та реактивна складові цієї напруги. Потім реактивна складова вхідного опору датчика 2 визначається за приведеною далі формулою 4. При цьому враховані наступні положення. Якщо 15 виразити реактивну складову вхідного опору датчика через квадратурні складові векторів U та івхд, які були визначені відповідно у другому та третьому тактах, то отримаємо: bc ad , Lвхд 2 c d2 де а - дійсна складова вектора U ; b - уявна складова вектора U ; с - дійсна складова вектора івхд; d - уявна складова вектора івхд. Для отримання остаточного скоригованого результату відношення модулів вихідної напруги U д датчика 2 та модулю його вхідного струму iвхд 20 ділиться на реактивну складову вхідного опору L вхд датчика 2: Uд Nрез 25 30 35 40 45 . iвхд L вхд Таким чином, ми отримали результат вимірювання переміщення, вільний від впливу температури на чутливість датчика, від впливу неточності виготовлення резисторів схеми на адитивну та мультиплікативну похибку вимірювання. Генератор 1 тестових та керуючих сигналів з протифазними виходами формує два протифазних тестових гармонійних сигнали та чотири керуючі сигнали, фази яких відрізняються один від одного на 90°. Це сигнали типу меандр і їхня частота дорівнює частоті тестового ~ ~ сигналу. Два протифазних сигнали U та - U формуються фільтром 32 нижніх частот, який фільтрує вихідний сигнал функціонального перетворювача 31 в квазісинусоїдальний сигнал, завдяки чому рівень нелінійних спотворень тестових сигналів зменшується до не значимого рівня (менше за 0,1 %). Тактова частота кварцового генератора 35 (зазвичай 1-10 МГц - частота синхросигналу мікро-ЕОМ) ділиться подільником частоти до частоти, у чотири рази більшої, ніж частота необхідного тестового сигналу. Далі сигнал цієї частоти подільникомфазорозщеплювачем перетворюється у чотири меандрові сигнали з частотою, що дорівнює частоті тестового сигналу, та зсунуті по фазі один по відношенню до другого на 90° (090°, 180°, 270°). Вищезгаданий подільник частоті та подільник-фазорозщеплювач поєднані в одному блоці 34. Фазочутливий випрямляч 9 є двонапівперіодним синхронним детектором з ітераційним інтегруючим перетворювачем у якості прецизійного швидкодіючого усереднюючого пристрою. На вхід синхронного детектора 36 поступає вихідна напруга U П вимірювального перетворювача 8. Ітераційний інтегруючий перетворювач, побудований на базі інтегратора (ОП 40, резистори 37, 38 та конденсатор 39), ОП 49 (повторювач напруги), двох динамічних запам'ятовуючих пристроїв на базі аналогових ключів 42, 43, 47, 48 та на конденсаторах пам'яті 45, 46, формує вихідний сигнал, пропорційний середньому значенню вихідної напруги синхронного детектора 36. Керування роботою вказаного ітераційного інтегруючого перетворювача здійснює подільник частоти 41 та інвертор 44. Керування синхронним детектором 36 здійснює один із керуючих вихідних сигналів генератора 1 тестових та керуючих сигналів, який обирається мультиплексором 4 під керуванням мікро-ЕОМ. 5 UA 78475 U Моделювання запропонованої схеми в Electronics Workbench підтвердило ефективність корекції вищезгаданих похибок. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 5 10 15 20 25 30 35 40 45 50 55 60 1. Аналоговий інтерфейс для інформаційно-вимірювальної системи з індуктивними датчиками переміщення, що містить генератор тестових та керуючих сигналів з протифазними виходами, тестовий вихід якого сполучений з індуктивним датчиком, а керуючі виходи через регулятор фази зв'язані з фазочутливим випрямлячем, вихід якого є виходом аналогового інтерфейсу, а також вимірювальний підсилювач, вхідні лінії зв'язку якого зв'язані з індуктивним датчиком, а вихід - з фазочутливим випрямлячем, який відрізняється тим, що для підвищення точності введено диференціальний мультиплексор, через який вхід вимірювального підсилювача з резисторами у своїх вхідних лініях зв'язку з'єднаний з протифазними виходами індуктивного датчиком, введено перетворювач струм-напруга, вхід якого зв'язаний з індуктивним датчиком та протифазним виходом генератора тестових та керуючих сигналів з протифазними виходами, а вихід - із входом диференціального мультиплексора, вхід диференціального мультиплексора зв'язаний з протифазними виходами генератора тестових та керуючих сигналів з протифазними виходами, а вимірювальний підсилювач виконано у вигляді підсилювача перехідного опору з напругою на виході, пропорційною вхідному струму, протифазні виходи якого підключені до входів диференціального мультиплексора, а регулятор фази виконано у вигляді цифрового мультиплексора. 2. Аналоговий інтерфейс за п. 1, який відрізняється тим, що у його вимірювальному підсилювачі відповідно неінвертуючий вхід вимірювального підсилювача зв'язаний із входами першого і другого аналогових ключів, вихід першого аналогового ключа під'єднаний через перший резистор до виходу першого операційного підсилювача (ОП), а також через третій аналоговий ключ - до інвертуючого входу першого ОП та до виходу четвертого аналогового ключа, вхід четвертого аналогового ключа під'єднаний до виходу другого аналогового ключа та через другий резистор - до виходу першого ОП, інвертуючий вхід першого ОП під'єднаний до загальної точки схеми, інвертуючий вхід вимірювального підсилювача зв'язаний із входами п'ятого і шостого аналогових ключів, вихід п'ятого аналогового ключа підключений до виходу першого аналогового ключа та через сьомий аналоговий ключ - до інвертуючого входу другого ОП, який через восьмий аналоговий ключ під'єднаний до виходів другого та шостого аналогових ключів та через послідовно з'єднані третій резистор та дев'ятий аналоговий ключ - до виходу другого ОП, вихід другого ОП, крім того, через десятий аналоговий ключ під'єднаний до входу одинадцятого аналогового ключа та через четвертий резистор - до виходу п'ятого аналогового ключа, вихід одинадцятого аналогового ключа з'єднаний із першим входом суматора та з виходом дванадцятого аналогового ключа, вхід якого під'єднаний до третього резистора та входу дев'ятого аналогового ключа, вихід суматора є виходом вимірювального підсилювача, інвертуючий вхід другого ОП під'єднаний до загальної точки схеми, при цьому керуючі входи першого, третього, шостого, восьмого, дев'ятого та дванадцятого аналогових ключів під'єднані до першого керуючого входу вимірювального підсилювача, керуючі входи другого, четвертого, п'ятого, сьомого, десятого та одинадцятого аналогових ключів зв'язані з керуючим входом вимірювального підсилювача через інвертор, вихід першого ОП через тринадцятий аналоговий ключ під'єднаний до інвертуючого входу суматора, а другий керуючий вхід вимірювального підсилювача під'єднаний до керуючого входу тринадцятого аналогового ключа. 3. Аналоговий інтерфейс за п. 1, який відрізняється тим, що його генератор тестових та керуючих сигналів з протифазними виходами має послідовно з'єднані генератор з вихідним сигналом прямокутної форми, подільник-фазорозщеплювач, виходи якого є виходами керуючих сигналів, перетворювач прямокутної напруги у трикутну, виконаний на базі реального інтегратора, перетворювач трикутної напруги у квазісинусоїдальну, виконаний з використанням кусково-лінійної апроксимації, фільтр нижніх частот, протифазні виходи якого є виходом тестового сигналу, причому один із виходів подільника-фазорозщеплювача з'єднаний із входом перетворювача прямокутної напруги у трикутну. 4. Аналоговий інтерфейс за п. 1, який відрізняється тим, що його фазочутливий випрямляч має на вході синхронний детектор, керуючий вхід якого підключений до схеми вибору фази керуючого сигналу, а вихід через перший резистор під'єднаний до інвертуючого входу першого ОП, неінвертуючий вхід якого під'єднаний до загальної точки схеми, вихід першого ОП через перший конденсатор під'єднаний до інвертуючого входу першого ОП та через другий резистор до виходу повторювача напруги, вихід повторювача напруги є виходом фазочутливого випрямляча, вхід повторювача напруги під'єднаний до виходів першого та другого ключів, входи 6 UA 78475 U 5 яких підключені безпосередньо до виходу третього та четвертого ключів а також через другий та третій конденсатори - до загальної точки схеми, входи першого та четвертого ключів під'єднані до виходу подільника частоти, який через інвертор зв'язаний з керуючими входами другого та третього ключів, а вхід подільника частоти під'єднаний до першого виходу подільника-фазорозщеплювача. 7 UA 78475 U Комп’ютерна верстка А. Крулевський Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 8

ДивитисяДодаткова інформація

Назва патенту англійськоюAnalog interface for information and measuring system with inductive displacement pickups

Автори англійськоюKulyk Mykola Serhiiovych, Kharchenko Volodymyr Petrovych, Kvasnikov Volodymyr Pavlovych, Ornatskyi Dmytro Petrovych, Osmolovskyi Oleksandr Ivanovych, Ilchenko Volodymyr Mykolaiovych

Назва патенту російськоюАналоговый интерфейс для информационно-измерительной системы с индуктивными датчиками перемещения

Автори російськоюКулик Николай Сергеевич, Харченко Владимир Петрович, Квасников Владимир Павлович, Орнатский Дмитрий Петрович, Осмоловский Александр Иванович, Ильченко Владимир Николаевич

МПК / Мітки

МПК: G06F 3/00, G06F 13/00

Мітки: інтерфейс, переміщення, аналоговий, індуктивними, інформаційно-вимірювальної, датчиками, системі

Код посилання

<a href="https://ua.patents.su/10-78475-analogovijj-interfejjs-dlya-informacijjno-vimiryuvalno-sistemi-z-induktivnimi-datchikami-peremishhennya.html" target="_blank" rel="follow" title="База патентів України">Аналоговий інтерфейс для інформаційно-вимірювальної системи з індуктивними датчиками переміщення</a>

Попередній патент: Шліфувальний інструмент

Наступний патент: Хірургічний інструмент