Цифровий інтегратор

Номер патенту: 80152

Опубліковано: 13.05.2013

Автори: Жуков Ігор Анатолійович, Ковальов Микола Олександрович

Формула / Реферат

Цифровий інтегратор, що містить регістр підінтегральної функції, перший блок додавання, блок множення, перший комутатор, групу входів приросту підінтегральної функції, перший вхід синхронізації пристрою, групу входів приросту аргументу, регістр приросту аргументу, другий і третій входи синхронізації пристрою, другий блок додавання, регістр результату, групу виходів пристрою, регістр залишку інтеграла, четвертий, п'ятий, шостий і сьомий входи синхронізації пристрою, групу входів початкових умов, при цьому група виходів регістра підінтегральної функції зв'язана з першою групою входів першого блока додавання, перша група виходів якого зв'язана з першими групами входів блока множення та першого комутатора, група виходів якого зв'язана з першою групою входів регістра підінтегральної функції, група входів приросту підінтегральної функції зв'язана з другою групою входів першого блока додавання, другий вхід першого комутатора зв'язаний з першим входом синхронізації пристрою, група входів приросту аргументу пристрою зв'язана з першою групою входів регістра приросту аргументу, другий вхід якого зв'язаний з другим входом синхронізації пристрою, третій вхід синхронізації пристрою зв'язаний з другим входом регістра підінтегральної функції, перша група виходів та другий вихід блока множення зв'язані з першою групою входів та другим входом другого блока додавання відповідно, група виходів регістра результату зв'язана з групою виходів пристрою, перші входи регістра залишку інтеграла та регістра результату зв'язані з четвертим та п'ятим входами синхронізації пристрою відповідно, друга група входів блока множення зв'язана з групою виходів регістра приросту аргументу, треті входи регістра підінтегральної функції, регістра приросту аргументу, першого та другого блоків додавання, блока множення, другі входи регістра результату і регістра залишку інтеграла зв'язані з шостим входом синхронізації пристрою, четвертий вхід блока множення зв'язаний з другим виходом першого блока додавання, четвертий вхід якого зв'язаний з сьомим входом синхронізації пристрою, група виходів регістра залишку інтеграла зв'язана з четвертою групою входів другого блока додавання, група входів початкових умов пристрою зв'язана з третьою групою входів першого комутатора, який відрізняється тим, що до його складу введений другий комутатор, структура другого блока додавання модифікована, при цьому група виходів якого зв'язана з третьою групою входів регістра залишку інтеграла і першою групою входів другого комутатора, група виходів якого зв'язана з третьою групою входів регістра результату, друга група входів другого комутатора зв'язана з третьою групою виходів блока множення, другий вихід якого зв'язаний з третім входом другого комутатора.

Текст

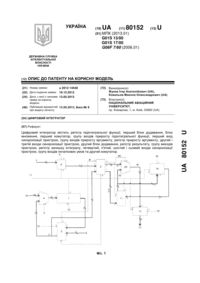

Реферат: UA 80152 U UA 80152 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до пристроїв обчислювальної техніки і може застосовуватись в однорідних цифрових інтегруючих структурах, реалізованих на базі програмувальних логічних інтегральних схем для систем керування та моделювання в реальному часу. Першим відомим пристроєм є цифровий інтегратор [1], що містить блок запам'ятовування, групу елементів І, елемент НЕ, елемент затримки, лічильник адресу та блок ітерацій. Недоліком першого відомого пристрою є низька швидкодія, зумовлена тим, що в ньому реалізують чисельне інтегрування за допомогою формування потоку одиничних приростів шляхом послідовного опитування розрядів підінтегральної функції. Завдяки цьому кількість тактів на кроці чисельного інтегрування має степеневу залежність від розрядності інтегрованих змінних. Другий відомий пристрій для обробки чисел у надлишковому послідовному коді [2] містить групу входів початкових умов, групу входів синхронізації, елементи І-АБО, групу входів приросту аргументу, регістр приросту аргументу, регістр підінтегральної функції, перший і другий блоки додавання, блок запам'ятовування таблиці множення, блоки затримки, блок запам'ятовування таблиці додавання, регістр залишку інтеграла, регістр результату, групу виходів приросту інтеграла, групу входів приросту підінтегральної функції та комутатор. Пристрій дозволяє реалізувати операцію чисельного інтегрування над даними, представленими у четвертинній надлишковій системі числення з цифрами {-2,-1, 0, 1, 2, 3}. Низька швидкодія цього пристрою зумовлена суто послідовним виконанням операції множення на кожний розряд приросту аргументу при визначенні приросту інтеграла. Тому кількість тактів на кроці чисельного інтегрування має квадратичну залежність від розрядності інтегрованих змінних. Найбільш близьким за своїми ознаками до запропонованого корисної моделі є цифровий інтегратор [3], який значно поліпшує недоліки першого і другого відомих пристроїв, і містить регістр підінтегральної функції, перший блок додавання, комутатор, групу входів приросту підінтегральної функції, групу входів початкових умов, перший вхід синхронізації пристрою, групу входів приросту аргументу, регістр приросту аргументу, другий і третій входи синхронізації пристрою, другий блок додавання, регістр результату, регістр залишку інтеграла, четвертий вхід синхронізації пристрою, групу виходів пристрою, п'ятий вхід синхронізації пристрою, блок множення, шостий і сьомий входи синхронізації пристрою. Пристрій дозволяє реалізувати операцію чисельного інтегрування над даними з фіксованою точкою однакової розрядності, по модулю меншими за одиницю, у двійковій та четвертинній симетричних надлишкових системах числення з цифрами {-1, 0, 1} та {-2,-1, 0, 1, 2} відповідно. Зазначений пристрій прийнятий авторами за прототип. Швидкодія зазначеного пристрою-прототипу може виявитися недостатньою для використання його у цифрових системах керування і моделювання реального часу. Це зумовлене низьким рівнем суміщення обчислень на різних кроках чисельного інтегрування. В основу запропонованої корисної моделі поставлено задачу підвищення швидкодії цифрового інтегратора за рахунок подальшого розпаралелювання обчислень на різних кроках чисельного інтегрування. Воно полягає в суміщенні обчислень приросту інтеграла на новому кроці чисельного інтегрування з операцією квантування на попередньому. Поставлена задача вирішується цифровим інтегратором, що містить регістр підінтегральної функції, перший блок додавання, блок множення, перший комутатор, групу входів приросту підінтегральної функції, перший вхід синхронізації пристрою, групу входів приросту аргументу, регістр приросту аргументу, другий і третій входи синхронізації пристрою, другий блок додавання, регістр результату, групу виходів пристрою, регістр залишку інтеграла, четвертий, п'ятий, шостий і сьомий входи синхронізації пристрою, групу входів початкових умов, при цьому група виходів регістра підінтегральної функції зв'язана з першою групою входів першого блока додавання, перша група виходів якого зв'язана з першими групами входів блока множення та першого комутатора, група виходів якого зв'язана з першою групою входів регістра підінтегральної функції, група входів приросту підінтегральної функції зв'язана з другою групою входів першого блока додавання, другий вхід першого комутатора зв'язаний з першим входом синхронізації пристрою, група входів приросту аргументу пристрою зв'язана з першою групою входів регістра приросту аргументу, другий вхід якого зв'язаний з другим входом синхронізації пристрою, третій вхід синхронізації пристрою зв'язаний з другим входом регістра підінтегральної функції, перша група виходів та другий вихід блока множення зв'язані з першою групою входів та другим входом другого блока додавання відповідно, група виходів регістра результату зв'язана з групою виходів пристрою, перші входи регістра залишку інтеграла та регістра результату зв'язані з четвертим та п'ятим входами синхронізації пристрою відповідно, друга група входів блока множення зв'язана з групою виходів регістра приросту аргументу, треті входи регістра підінтегральної функції, регістра приросту аргументу, першого та другого блоків додавання, блока множення, другі входи регістра результату і регістра залишку інтеграла 1 UA 80152 U 5 10 15 20 25 30 35 40 45 50 55 60 зв'язані з шостим входом синхронізації пристрою, четвертий вхід блока множення зв'язаний з другим виходом першого блока додавання, четвертий вхід якого зв'язаний з сьомим входом синхронізації пристрою, група виходів регістра залишку інтеграла зв'язана з четвертою групою входів другого блока додавання, група входів початкових умов пристрою зв'язана з третьою групою входів першого комутатора. До складу пристрою введений другий комутатор і змінено побудову другого блока додавання, при цьому група виходів якого зв'язана з третьою групою входів регістра залишку інтеграла і першою групою входів другого комутатора, група виходів якого зв'язана з третьою групою входів регістра результату, друга група входів другого комутатора зв'язана з третьою групою виходів блока множення, другий вихід якого зв'язаний з третім входом другого комутатора. На теперішній час авторам і заявнику не відома така сукупність ознак, яку наведено у формулі запропонованої корисної моделі для досягнення поставленої задачі, тому вона є новою, а запропоноване технічне рішення відповідає критерію "новизна". Усі введені у формулі корисної моделі ознаки є необхідними і разом з відомими необхідними ознаками складають нову сукупність необхідних і достатніх суттєвих ознак запропонованого технічного рішення, завдяки тому, що таке введення нових ознак дозволяє розв'язати поставлену задачу, тобто підвищити швидкодію цифрового інтегратора, яка зв'язана з подальшим розпаралелюванням обчислень на новому і попередньому кроках чисельного інтегрування. Дійсно, введення другого комутатора, зміна побудови другого блока додавання, а також введення нових зв'язків дозволяють сумістити обчислення приросту інтеграла на новому кроці чисельного інтегрування з операцією квантування на попередньому. Суть корисної моделі пояснюється кресленнями, де на фіг. 1 наведена структурна схема запропонованого пристрою, фіг. 2 - структурна схема другого блока додавання, на фіг. 3 часова діаграма роботи пристрою для розрядності даних n=11. Цифровий інтегратор (див. фіг. 1) містить регістр підінтегральної функції 1, перший блок додавання 2, блок множення 3, перший комутатор 4, групу входів приросту підінтегральної функції 5, перший вхід синхронізації пристрою 6, групу входів приросту аргументу 7, регістр приросту аргументу 8, другий і третій входи синхронізації пристрою 9 і 10 відповідно, другий блок додавання 11, регістр результату 12, групу виходів пристрою 13, регістр залишку інтеграла 14, четвертий, п'ятий, шостий і сьомий входи синхронізації пристрою 15, 16, 17 і 18 відповідно, групу входів початкових умов 19, другий комутатор 20. Група виходів регістра підінтегральної функції 1 зв'язана з першою групою входів першого блока додавання 2, перша група виходів якого зв'язана з першими групами входів блока множення 3 та першого комутатора 4, група виходів якого зв'язана з першою групою входів регістра підінтегральної функції 1. Група входів приросту підінтегральної функції 5 зв'язана з другою групою входів першого блока додавання 2. Другий вхід першого комутатора 4 зв'язаний з першим входом синхронізації пристрою 6. Група входів приросту аргументу пристрою 7 зв'язана з першою групою входів регістра приросту аргументу 8, другий вхід якого зв'язаний з другим входом синхронізації пристрою 9. Третій вхід синхронізації пристрою 10 зв'язаний з другим входом регістра підінтегральної функції 1. Перша група виходів та другий вихід блока множення 3 зв'язані з першою групою входів та другим входом другого блока додавання 11 відповідно. Група виходів регістра результату 12 зв'язана з групою виходів пристрою 13. Перші входи регістра залишку інтеграла 14 та регістра результату 12 зв'язані з четвертим та п'ятим входами синхронізації пристрою 15 і 16 відповідно. Друга група входів блока множення 3 зв'язана з групою виходів регістра приросту аргументу 8. Треті входи регістра підінтегральної функції 1, регістра приросту аргументу 8, першого та другого блоків додавання 2 і 11 відповідно, блока множення 3, другі входи регістра результату 12 і регістра залишку інтеграла 14 зв'язані з шостим входом синхронізації пристрою 17. Четвертий вхід блока множення 3 зв'язаний з другим виходом першого блока додавання 2, четвертий вхід якого зв'язаний з сьомим входом синхронізації пристрою 18. Група виходів регістра залишку інтеграла 14 зв'язана з четвертою групою входів другого блока додавання 11. Група входів початкових умов пристрою 19 зв'язана з третьою групою входів першого комутатора 4. Група виходів другого блока додавання 11 зв'язана з третьою групою входів регістра залишку інтеграла 14 і першою групою входів другого комутатора 20, група виходів якого зв'язана з третьою групою входів регістра результату 12. Друга група входів другого комутатора 20 зв'язана з третьою групою виходів блока множення 3, другий вихід якого зв'язаний з третім входом другого комутатора 20. Другий блок додавання 11 (див. фіг. 2) містить першу групу входів блока 21, регістр 22, суматор 23, другу групу входів блока 24, схему керування 25, групу виходів блока 26, перший і другий входи синхронізації блока 27 і 28 відповідно. Перша група входів блока 21 зв'язана з 2 UA 80152 U 5 10 15 першою групою входів регістра 22, друга група входів якого зв'язана з групою виходів суматора 23, перша група входів якого зв'язана з групою виходів регістра 22. Друга група входів суматора 23 зв'язана з другою групою входів блока 24. Група виходів суматора 23 зв'язана з групою входів схеми керування 25, група виходів якої зв'язана з групою виходів блока 26. Третій і четвертий входи регістра 22 зв'язані з першим і другим входами синхронізації блока 27 і 28 відповідно. Пристрій може бути побудований наступним чином. Основу пристрою складають квазіпаралельні операційні блоки додавання 2 і 11, а також блок множення 3, які функціонують в неавтономному режимі обчислень. В середині блоків інформація обробляють у паралельному вигляді, а між блоками передають порозрядно, починаючи зі старших розрядів. Алгоритми роботи і способи реалізації першого блока додавання 2 та блока множення 3 відомі [4, 5]. Обчислення в них проводять над даними з фіксованою точкою з одним знаковим і (n-1) розрядами справа від точки, по модулю меншими за одиницю, у четвертинній симетричній надлишковій системі числення з цифрами {-2,-1, 0, 1, 2}. Цифри розрядів передають по трьом сигнальним лініям і кодують наступним чином: -2 "110",-1 "111", 0 "00", 1 "001", 2 "010". Тому більшість груп входів і виходів у пристрої є 3-розрядними. Пристрій виконує чисельне інтегрування за Стілтьєсом і функціонує за таким алгоритмом: 1. ypi ypi1 ypi . 2. zi1 yqi1ypi 2n Si . 20 0 3. zi 1 Pn zi 1 . n 4. Si 1 P 2n 1zi 1 . Тут zi1 , zi1 - неквантоване та квантоване значення інтегрального приросту на (i+1)-у кроці відповідно, yqi1 - значення приросту аргументу на (i+1)-о кроці, yp i 1 - значення підінтегральної функції на (і-1)-у кроці, ypi - значення приросту підінтегральної функції на i-у 25 0 кроці, Si і Si 1 - значення залишків інтеграла на i-у та (i+1)-у кроках відповідно, Pn - операція виділення розрядів з m по l. У блоці множення 3 виконують арифметичну операцію Z 42 XY . У першому блоці додавання 2 виконують арифметичну операцію 30 35 Z 4 2 X Y . В обох випадках забезпечують суміщення порозрядного вводу операндів X та У зі старших розрядів і формування результату Z, старший розряд якого отримують із запізненням на два такти. У другому блоці додавання 11 забезпечують суміщення порозрядного вводу значення Si з послідовним формуванням спочатку 2-х молодших розрядів значення zi1 , а потім - n розрядів значення Si 1 . Алгоритм його роботи на кожному i-у такті по визначенню чергової з цих цифр zi має наступний вигляд: 1. Hi 4Ri 1 4 2 si . 40 3 2, якщо Ні 2 ; 1, якщо 3 Ні 1 ; 2 2 1 1 2. zi 0, якщо Ні ; ; 2 2 1 3 1, якщо 2 Ні 2 ; 2, якщо Ні 3 ; 2 3. Ri Hi zi . Роботу другого блока додавання 11 тактують по першому входу синхронізації блока 26. За початком сигналу на другому вході синхронізації блока 27 з першої групи входів блока 21 в регістр 22 завантажують (2n+5)-розрядне початкове значення (4R0). Кожного такту в блоці 3 UA 80152 U 5 10 15 20 25 30 виконують наступні дії. Для реалізації п. 1 приведеного алгоритму 7 старших розрядів значення (4Ri-1) з групи виходів регістра 22 подають на першу групу входів суматора 23, на другу групу входів якого з другої групи входів блока 24 подають чергову цифру si. При цьому на групі виходів суматора 23 отримують значення Hi, старші 4 розряди якого поступають на групу входів схеми керування 25. Згідно з п. 2 алгоритму вона формує чергову цифру zi, яку подають з її групи виходів на групу виходів блока 26. Одночасно з цим виконують модифікований зсув на 2 розряди вліво регістра 22, і в ньому одразу отримують нове значення (4Ri), чим реалізують п. 3 приведеного вище алгоритму. Після цього блок готовий до формування в наступному такті нової цифри zi+1 згідно приведеного алгоритму. Регістр підінтегральної функції 1, регістр приросту аргументу 8, регістр результату 12, регістр залишку інтеграла 14, регістр 22 будують на регістрах зсуву, а комутатори 4 і 20 мультиплексорах. Схема керування 25 є комбінаційною логічною схемою. Пристрій працює наступним чином. Роботу цифрового інтегратора тактують по шостому входу синхронізації 17. На кожному кроці чисельного інтегрування отримують чергове квантоване значення приросту інтеграла zi1 . Перед початком роботи пристрою виконують запис початкових умов наступним чином. За сигналами на першому і третьому входах синхронізації пристрою 6 і 10 відповідно протягом n тактів значення yp0 порозрядно завантажують з групи входів початкових умов 19 через третю групу входів першого комутатора 4 в регістр підінтегральної функції 1 через його першу групу входів. Одночасно з цим за сигналом на другому вході синхронізації пристрою 9 протягом n тактів значення y q0 порозрядно завантажують з групи входів приросту аргументу 7 в регістр приросту аргументу 8 через його першу групу входів. Після цього розпочинають роботу цифрового інтегратора, яка складається з кроків чисельного інтегрування. На i-у кроці чисельного інтегрування виконують наступні дії. Впродовж одного такту стартовий сигнал з сьомого входу синхронізації пристрою 18 подають на четвертий вхід першого блока додавання 2 і здійснюють початкову установку його регістрів. Після цього за сигналом на третьому вході синхронізації пристрою 10 тривалістю (n+2) такти з групи виходів регістра підінтегральної функції 1 на першу групу входів першого блока додавання 2 впродовж n тактів порозрядно надходить значення ypi1 . На другу групу входів першого блока додавання 2 з групи входів приросту підінтегральної функції 5 впродовж n тактів порозрядно надходить значення ypi . І на першій групі виходів блока додавання 2 із затримкою на 2 такти порозрядно отримують нове значення y pi : 35 t1 ypi ypi 1 ypi , яке за тим же сигналом на третьому вході синхронізації пристрою 10 завантажують через першу групу входів першого комутатора 4 в регістр підінтегральної функції 1 через його першу групу входів. Також воно надходить на першу групу входів блока множення 3. Тобто в регістрі підінтегральної функції 1 одночасно порозрядно зчитують попереднє значення yp i 1 і 40 завантажують нове значення y pi . Через 2 такти після подачі сигналу на сьомий вхід синхронізації пристрою 18: - впродовж n тактів сигнал з другого входу синхронізації пристрою 9 подають на другий вхід регістра приросту аргументу 8. При цьому через його першу групу входів з групи входів приросту аргументу пристрою 7 порозрядно завантажують нове значення y qi 2 . Одночасно з цим з його групи 45 виходів на другу групу входів блока множення 3 надходить попереднє значення yqi1 ; - з другого виходу блока додавання 2 на четвертий вхід блока множення 3 протягом одного такту подають сигнал st, за яким здійснюють початкову установку його регістрів. І на третій групі виходів блока множення 3 після обробки n розрядів вхідних значень yqi1 і y pi із затримкою на 2 такти отримують (n-2) старші цифри нового значення zi1 : 0 0 t2 c Pn3 zi1 Pn3 yqi1ypi , z i1 50 які надходять на другу групу входів другого комутатора 20. Після цього на другий вхід блока множення 3 протягом 2-х тактів видають сигнал st2, що подають на другий вхід другого блока додавання 11 і по передньому фронту якого на першу групу входів цього блока з першої групи виходів блока множення 3 передають початкове значення (4R0). Одразу після цього блок множення 3 може розпочинати операцію множення на наступному кроці чисельного 4 UA 80152 U 5 інтегрування, а другий блок додавання 11 завершує поточне множення і проводить квантування. Тобто з цього моменту матиме місце суміщення обчислень приросту інтеграла в блоці множення 3 на новому кроці чисельного інтегрування з операцією квантування в другому блоці додавання 11 на попередньому. Також на четверту групу входів другого блока додавання 11 з групи виходів регістра залишку інтеграла 14 за сигналом на четвертому вході синхронізації пристрою 15 порозрядно подають значення Si. Спочатку другий блок додавання 11 порозрядно 10 15 формує 2 молодші розряди значення zi 1 м , які надходять з його групи виходів (значення zi1 t3) на першу групу входів другого комутатора 20. Потім другий блок додавання 11 формує (n-1) розряд значення Si 1 , які надходять з його групи виходів на третю групу входів регістра залишку інтеграла 14. В ньому за сигналом на четвертому вході синхронізації пристрою 15 протягом (n-1) тактів одночасно порозрядно зчитують попереднє значення Si і завантажують нове значення Si 1 . За сигналом на п'ятому вході синхронізації пристрою 16 з групи виходів другого комутатора 20 (значення t4) в регістр результату 12 через його третю групу входів завантажують спочатку цифри значення c , а потім при подачі сигналу st2 на третій вхід другого комутатора 20 z i1 м . Тобто в регістрі результату 12 фіксують нове значення zi1 . z i1 20 25 30 35 40 45 50 Суть корисної моделі полягає в наступному. Зазвичай квазіпаралельний блок множення не може розпочати обчислення на новому кроці інтегрування, поки за (2n+1) такти не сформують добуток подвоєної розрядності, і його апаратні ресурси не звільнять. Саме це і визначає тривалість кроку інтегрування в пристрої-прототипі. Молодша половина розрядів цього добутку необхідна для проведення квантування. Тому пропонують до блока множення ввести додатковий квазіпаралельний блок. Тоді блок множення за n тактів обробки n розрядів вхідних аргументів сформує (n-2) старших розрядів добутку і передасть додатковому блоку поточне значення (4Ri-1) (див. алгоритм). Отримавши його, додатковий блок спочатку доробляє молодші 2 розряди добутку. Потім, порозрядно отримуючи ще й попереднє значення залишку Si, блок порозрядно формує нове значення залишку Si 1 . Одночасно з цим блок множення проводить обчислення на наступному кроці інтегрування. Тобто в ЦІ спостерігають суміщення обчислень нового інтегрального приросту та квантування з попереднього кроці інтегрування. Завдяки тому, що вхідні аргументи блока множення мають n розрядів, і додатковому блоку нема необхідності дообробляти ці операнди, а тільки розряди попереднього залишку (див. алгоритм), його структура порівняно з блоком множення можна значно скоротити. Порівняємо швидкодії запропонованого пристрою з пристроєм-прототипом [3] за умов однакової розрядності n вхідних інтегровних змінних і проведення інтегральних обчислень в четвертинній системі числення по мінімальній тривалості кроку чисельного інтегрування, на якому обчислюють квантований приріст інтеграла. В обох випадках маємо однакову тривалість такту, що визначають швидкодією однакових квазіпаралельних блоків множення. Тому тривалість кроку чисельного інтегрування можна оцінити кількістю тактів в ньому. У випадку пристрою-прототипу її визначають часом виконання операції множення в однойменному блоці: T1 2n 1 . (1) Тривалість кроку чисельного інтегрування запропонованого пристрою вже не визначають операцією множення, а, як показує часова діаграма (див. фіг. 3), часом отримання першим блоком додавання 2 всіх розрядів чергового значення підінтегральної функції y pi : T2 n 2 . (2) З урахуванням (1) і (2) при великій розрядності обчислень запропонований пристрій дозволяє підвищити швидкодію в T1 2n 1 2 рази. T2 n 2 Підвищення швидкодії запропонованого цифрового інтегратора стало можливим завдяки введенню нового блока і конструктивних зв'язків, а також зміні побудови існуючих блоків і зв'язків. Джерело інформації: 1. Авторське свідоцтво СРСР № 720427, кл. G06F 1/02, 1981. 2. Авторське свідоцтво СРСР № 1330629, кл. G06F 7/64, 1985. 5 UA 80152 U 5 3. Патент на корисна модель № 87073 Україна, МПК (2009) G01S 13/00, G01S 17/00, G06F 7/60, 2008 (прототип). 4. Жабин В.И., Корнейчук В.И., Тарасенко В.П. Некоторые машинные методы вычисления рациональных функций многих переменных // Автоматика и телемеханика.-1977. - № 12. - С. 145-154. 5. Дичка И.А., Жабина В.В. Совмещение зависимых операций на уровне обработки разрядов операндов // Искусственный интеллект.-2008. - № 3. - С. 649-654. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 10 15 20 25 30 35 40 Цифровий інтегратор, що містить регістр підінтегральної функції, перший блок додавання, блок множення, перший комутатор, групу входів приросту підінтегральної функції, перший вхід синхронізації пристрою, групувходів приросту аргументу, регістр приросту аргументу, другий і третій входи синхронізації пристрою, другий блок додавання, регістр результату, групу виходів пристрою, регістр залишку інтеграла, четвертий, п'ятий, шостий і сьомий входи синхронізації пристрою, групу входів початкових умов, при цьому група виходів регістра підінтегральної функції зв'язана з першою групою входів першого блока додавання, перша група виходів якого зв'язана з першими групами входів блока множення та першого комутатора, група виходів якого зв'язана з першою групою входів регістра підінтегральної функції, група входів приросту підінтегральної функції зв'язана з другою групою входів першого блока додавання, другий вхід першого комутатора зв'язаний з першим входом синхронізації пристрою, група входів приросту аргументу пристрою зв'язана з першою групою входів регістра приросту аргументу, другий вхід якого зв'язаний з другим входом синхронізації пристрою, третій вхід синхронізації пристрою зв'язаний з другим входом регістра підінтегральної функції, перша група виходів та другий вихід блока множення зв'язані з першою групою входів та другим входом другого блока додавання відповідно, група виходів регістра результату зв'язана з групою виходів пристрою, перші входи регістра залишку інтеграла та регістра результату зв'язані з четвертим та п'ятим входами синхронізації пристрою відповідно, друга група входів блока множення зв'язана з групою виходів регістра приросту аргументу, треті входи регістра підінтегральної функції, регістра приросту аргументу, першого та другого блоків додавання, блока множення, другі входи регістра результату і регістра залишку інтеграла зв'язані з шостим входом синхронізації пристрою, четвертий вхід блока множення зв'язаний з другим виходом першого блока додавання, четвертий вхід якого зв'язаний з сьомим входом синхронізації пристрою, група виходів регістра залишку інтеграла зв'язана з четвертою групою входів другого блока додавання, група входів початкових умов пристрою зв'язана з третьою групою входів першого комутатора, який відрізняється тим, що до його складу введений другий комутатор, структура другого блока додавання модифікована, при цьому група виходів якого зв'язана з третьою групою входів регістра залишку інтеграла і першою групою входів другого комутатора, група виходів якого зв'язана з третьою групою входів регістра результату, друга група входів другого комутатора зв'язана з третьою групою виходів блока множення, другий вихід якого зв'язаний з третім входом другого комутатора. 6 UA 80152 U 7 UA 80152 U Комп’ютерна верстка А. Крижанівський Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 8

ДивитисяДодаткова інформація

Назва патенту англійськоюDigital integrator

Автори англійськоюZhukov Ihor Anatoliiovych, Kovaliov Mykola Oleksandrovych

Назва патенту російськоюЦифровой интегратор

Автори російськоюЖуков Игорь Анатольевич, Ковалев Николай Александрович

МПК / Мітки

МПК: G06F 7/60, G01S 13/00, G01S 17/00

Мітки: інтегратор, цифровий

Код посилання

<a href="https://ua.patents.su/10-80152-cifrovijj-integrator.html" target="_blank" rel="follow" title="База патентів України">Цифровий інтегратор</a>

Попередній патент: Спосіб приготування рідких кормів для молодняка свиней

Наступний патент: Спосіб комплексної терапії психопатичних нападів-фаз у хворих з дисоціальним розладом особистості з агресивною поведінкою

Випадковий патент: Настоянка "карпатська особлива з хріном"