Цифровий інтегратор

Номер патенту: 87073

Опубліковано: 10.06.2009

Автори: Жабін Валерій Іванович, Ковальов Микола Олександрович

Формула / Реферат

Цифровий інтегратор, що містить регістр підінтегральної функції, перший блок додавання, комутатор, регістр приросту аргументу, другий блок додавання, регістр результату, регістр залишку інтеграла, а також групу входів приросту підінтегральної функції, групу входів початкових умов, групу входів приросту аргументу, перший, другий, третій, четвертий, п'ятий, шостий входи синхронізації пристрою і групу виходів пристрою, при цьому група виходів регістра приросту підінтегральної функції зв'язана з першою групою входів першого блока додавання, перша група виходів якого зв'язана з першою групою входів комутатора, група виходів якого зв'язана з першою групою входів регістра підінтегральної функції, група входів приросту підінтегральної функції з'єднана з другою групою входів першого блока додавання, третій вхід комутатора зв'язаний з першим входом синхронізації пристрою, група входів приросту аргументу пристрою зв'язана з першою групою входів регістра приросту аргументу, друга група входів якого зв'язана з другим входом синхронізації пристрою, третій вхід синхронізації пристрою зв'язаний з другим входом регістра підінтегральної функції, група виходів другого блока додавання зв'язана з першими групами входів регістра залишку інтеграла та регістра результату, група виходів якого зв'язана з групою виходів пристрою, а другі входи регістра залишку інтеграла та регістра результату зв'язані відповідно з четвертим та п'ятим входами синхронізації пристрою, який відрізняється тим, що до його складу введений блок множення квазіпаралельного типу, перший і другий блоки додавання виконані квазіпаралельного типу, крім того, пристрій містить сьомий вхід синхронізації, при цьому перша група входів блока множення зв'язана з першою групою виходів першого блока додавання, а перша група виходів та другий вихід блока множення з'єднані відповідно з першою групою входів та другим входом другого блока додавання, друга група входів блока множення зв'язана з групою виходів регістра приросту аргументу, треті входи відповідно регістра підінтегральної функції, регістра приросту аргументу, першого та другого блоків додавання, регістра залишку інтеграла, регістра результату та блока множення з'єднані з шостим входом синхронізації пристрою, четвертий вхід блока множення зв'язаний з другим виходом першого блока додавання, четвертий вхід якого зв'язаний з сьомим входом синхронізації пристрою, а група виходів регістра залишку інтеграла зв'язана з четвертою групою входів другого блока додавання.

Текст

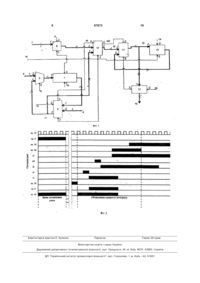

Цифровий інтегратор, що містить регістр підінтегральної функції, перший блок додавання, комутатор, регістр приросту аргументу, другий блок додавання, регістр результату, регістр залишку інтеграла, а також групу входів приросту підінтегральної функції, групу входів початкових умов, групу входів приросту аргументу, перший, другий, третій, четвертий, п'ятий, шостий входи синхронізації пристрою і групу виходів пристрою, при цьому група виходів регістра приросту підінтегральної функції зв'язана з першою групою входів першого блока додавання, перша група виходів якого зв'язана з першою групою входів комутатора, група виходів якого зв'язана з першою групою входів регістра підінтегральної функції, група входів приросту підінтегральної функції з'єднана з другою групою входів першого блока додавання, третій вхід комутатора зв'язаний з першим входом синхронізації пристрою, група входів приросту аргументу пристрою зв'язана з першою групою входів C2 2 (19) 1 3 потоку одиничних приростів шляхом послідовного опитування розрядів підінтегральної функції. Завдяки цьому кількість робочих тактів має степеневу залежність від розрядності інтегрованих змінних. Найбільш близьким за своїми ознаками до запропонованого винаходу є пристрій, для обробки чисел у надлишковому послідовному коді [3], який дещо поліпшує недоліки першого і другого відомих пристроїв і містить групу входів початкових умов, групу входів синхронізації, елементи І-АБО, групу входів приросту аргументу, регістр приросту аргументу, регістр підінтегральної функції, перший і другий блоки додавання, блок запам'ятовування таблиці множення, блоки затримки, блок запам'ятовування таблиці додавання, регістр залишку інтегралу, регістр результату, групу виходів приросту інтегралу, групу входів приросту підінтегральної функції та комутатор. Пристрій дозволяє реалізувати операцію чисельного інтегрування над даними, представленими у четвертинній надлишковій системі числення з цифрами {-2, -1, 0, 1, 2, 3}. Зазначений відомий пристрій прийнятий авторами за прототип. Швидкодія зазначеного пристрою-прототипу недостатня для використання його у цифрових системах керування і моделювання з високою швидкодією. Це зумовлене суто послідовним виконанням операції множення на кожний розряд приросту аргументу при визначенні приросту інтегралу під час виконання кроку чисельного інтегрування. Запропонованим винаходом поставлене завдання підвищення швидкодії цифрового інтегратора за рахунок значного суміщення виконання арифметичних операцій при обчисленні приросту інтегралу. Поставлене завдання розв'язується завдяки цифровому інтегратору, що містить регістр підінтегральної функції, перший блок додавання, комутатор, регістр приросту аргументу, другий блок додавання, регістр результату, регістр залишку інтегралу, а також групу входів приросту підінтегральної функції, групу входів початкових умов, групу входів приросту аргументу, перший, другий, третій, четвертий, п'ятий, шостий входи синхронізації пристрою і групу виходів пристрою, при цьому група виходів регістра приросту підінтегральної функції зв'язана з першою групою входів першого блока додавання, перша група виходів якого зв'язана з першою групою входів комутатора, група виходів якого зв'язана з першою групою входів регістра підінтегральної функції, група входів приросту підінтегральної функції з'єднана з другою групою входів першого блока додавання, третій вхід комутатора зв'язаний з першим входом синхронізації пристрою, група входів приросту аргументу пристрою зв'язана з першою групою входів регістра приросту аргументу, друга група входів якого зв'язана з другим входом синхронізації пристрою, третій вхід синхронізації пристрою зв'язаний з другим входом регістра підінтегральної функції, група виходів другого блока додавання зв'язана з першими групами входів регістра залишку інтегралу та регістра результату, група вихо 87073 4 дів якого зв'язана з групою виходів пристрою, другі групи входів регістра залишку інтегралу та регістра результату зв'язані відповідно з четвертим та п'ятим входами синхронізації пристрою. До складу пристрою введений блок множення квазіпаралельного типу, перший і другий блоки додавання виконані квазіпаралельного типу, крім того, пристрою наданий сьомий вхід синхронізації, при цьому перша група входів блока множення зв'язана з першою групою виходів першого блока додавання, а перша група виходів та другий вихід блока множення з'єднані відповідно з першою групою входів та другим входом другого блока додавання, друга група входів блока множення зв'язана з групою виходів регістра приросту аргументу, треті входи відповідно регістра підінтегральної функції, регістра приросту аргументу, першого та другого блоків додавання, регістра залишку інтегралу, регістра результату та блока множення з'єднані з шостим входом синхронізації пристрою, четвертий вхід блока множення зв'язаний з другим виходом першого блока додавання, четвертий вхід якого зв'язаний з сьомим входом синхронізації пристрою, група виходів регістра залишку інтегралу зв'язана з четвертою групою входів другого блока додавання. На теперішній час авторам і заявнику не відома така сукупність ознак, яку наведено у формулі запропонованого винаходу для досягнення поставленого завдання, тому вона являється новою, а запропоноване технічне рішення відповідає критерію „новизна". Усі введені у формулі винаходу ознаки є необхідними і разом з відомими необхідними ознаками складають нову сукупність необхідних і достатніх суттєвих ознак запропонованого технічного рішення, яке, таким чином, відповідає критерію „технічний рівень", завдяки тому, що таке введення нових ознак дозволяє розв'язати поставлене завдання, тобто підвищити швидкодію цифрового інтегратора, яка пов'язана з реалізацією неавтономних обчислень у симетричній надлишковій системі числення на кожному кроці чисельного інтегрування. Дійсно, введення блока множення квазіпаралельного типу і виконання суматорів квазіпаралельного типу, а також введення нових зв'язків дозволяють сумістити процеси порозрядного введення значень приросту підінтегральної функції, приросту аргументу підінтегральної функції та залишку інтегралу із старших розрядів і порозрядного формування приросту інтегралу із старших розрядів. Сутність винаходу пояснюється кресленнями, де на Фіг.1 наведена структурна схема запропонованого пристрою, на Фіг.2 - часова діаграма роботи пристрою для розрядності даних n=5. Цифровий інтегратор містить регістр підінтегральної функції 1 (див. Фіг.1), перший блок додавання 2, комутатор 3, групу входів приросту підінтегральної функції 4, групу входів початкових умов 5, перший вхід синхронізації пристрою 6, групу входів приросту аргументу 7, регістр приросту аргументу 8, другий і третій входи синхронізації пристрою 9 і 10 відповідно, другий блок додавання 11, регістр результату 12, регістр залишку інтегра 5 лу 13, четвертий вхід синхронізації пристрою 14, групу виходів пристрою 15, п'ятий вхід синхронізації пристрою 16, блок множення 17, шостий і сьомий входи синхронізації пристрою 18 і 19 відповідно. Група виходів регістру підінтегральної функції 1 .зв'язана з першою групою входів першого блока додавання 2, перша група виходів якого зв'язана з першою групою входів комутатора 3, група виходів якого зв'язана з першою групою входів регістра підінтегральної функції 1. Група входів приросту підінтегральної функції 4 зв'язана з другою групою входів першого блока додавання 2. Група входів початкових умов 5 зв'язана з другою групою входів комутатора 3, третій вхід якого зв'язаний з першим входом синхронізації пристрою 6, група входів приросту аргументу 7 зв'язана з першою групою входів регістра приросту аргументу 8, друга група входів якого зв'язана з другим входом синхронізації пристрою 9. Третій вхід синхронізації пристрою 10 зв'язаний з другим входом регістра підінтегральної функції 1. Група виходів другого блока додавання 11 зв'язана з першими групами входів регістру результату 12 і регістру залишку інтегралу 13. Четвертий вхід синхронізації пристрою 14 зв'язаний з другим входом регістра залишку інтегралу 13. Група виходів пристрою 15 зв'язана з групою виходів регістра результату 12, другий вхід якого зв'язаний з п'ятим входом синхронізації пристрою 16. Перша група виходів першого блока додавання 2 зв'язана з першою групою входів блока множення 17, перша група виходів якого зв'язана з першою групою входів другого блока додавання 11, другий вхід якого зв'язаний з другим виходом блока множення 17, друга група входів якого зв'язана з групою виходів регістра приросту аргументу 8, третій вхід якого зв'язаний з шостим входом синхронізації пристрою 18, який зв'язаний з третіми входами регістра підінтегральної функції 1, першого та другого блоків додавання 2 і 11 відповідно, регістра результату 12, регістра залишку інтегралу 13, блока множення 17. Другий вихід першого блока додавання 2 зв'язаний з четвертим входом блока множення 17. Сьомий вхід синхронізації пристрою 19 зв'язаний з четвертим входом першого блока додавання 2. Група виходів регістра залишку інтегралу 13 зв'язана з четвертою групою входів другого блока додавання 11. Всі групи входів і виходів у пристрої складаються з трьох сигнальних ліній. Пристрій може бути побудований наступним чином. Основу пристрою складають операційні блоки додавання 2 і 11 та блок множення 17. Ці блоки є квазіпаралельними і відрізняються неавтономним режимом функціонування. В середині блоків інформація обробляється у паралельному вигляді, а між блоками передається послідовно. Алгоритми роботи і способи реалізації таких блоків відомі [4, 5]. Обчислення в них проводиться над даними з фіксованою точкою однакової розрядності, по модулю меншими за одиницю, у таких симетричних надлишкових системах числення. 1. У двійковій з цифрами {-1, 0, 1}. У цьому випадку цифра розряду передається по двом сигнальним лініям і кодується наступним чином: -1≡"01", 0≡"00", 1≡"10". 87073 6 2. У четвертинній з цифрами {-2, -1, 0, 1, 2}. У цьому випадку цифра розряду передається по трьом сигнальним лініям і кодується наступним чином: -2≡" 110",-1≡"111", 0≡"00", 1≡"001", 2≡"010". Пристрій виконує чисельне інтегрування за Стілт'єсом і функціонує за таким алгоритмом: ( ) 1. Dz(i +1) = Dyэ (i+1) yp(i-1) + Dypi + 2-n Si , q ( ) 0 2. Dz (i+1) = P-n Dz (i +1) , 3. S(i +1) = (Dz(i+1)) , -nP-2n 1 де Dz(i+1) - неквантоване значення приросту інтегралу на (і+1)-у кроці; Dz (i+1) - квантоване значення приросту інтегралу на (і+1)-у кроці; э Dy q(i+1) - екстрапольоване значення аргументу інтегрування для (і+1)-о кроку, yp(i-1) - значення підінтегральної функції на (і1)-у кроці; Dypi - приріст підінтегральної функції на і-у кроці, Sі, S(і+1) - значення залишків інтегралу на і-у та (i+1)-у кроках відповідно, Plm - операція виділення розрядів з m по l (від'ємні значення вказують на розряд справа від точки). В блоці множення 17 виконують арифметичну операцію вид: Z=k-2XY, де k=2,4 для двійкових та четвертинних систем відповідно. У кожному з блоків додавання 2 і 11 виконують арифметичну операцію виду: Z=k-2(X+Y), В обох випадках забезпечується суміщення порозрядного введення операндів Х та У зі старших розрядів і порозрядного формування результату Z, старший розряд якого отримують із запізненням на два такти. Регістр підінтегральної функції 1, регістр приросту аргументу 8, регістр результату 12 і регістр залишку інтегралу 13 фактично є регістрами зсуву, а комутатор 3 є мультиплексором. Пристрій працює наступним чином. Роботу цифрового інтегратора тактують по шостому входу синхронізації 18. На кожному кроці процесу чисельного інтегрування отримують чергове квантоване значення приросту інтегралу Dz(i+1) . Перед початком роботи за сигналами на першому і третьому входах синхронізації пристрою 6 і 10 відповідно початкове значення підінтегральної функції yр0 через другу групу входів комутатора 3 послідовно завантажують за n тактів через першу групу входів в регістр підінтегральної функції 1. Після цього розпочинається робота цифрового інтегратора. Кожний крок обчислення Dz(i+1) починають з подачі впродовж одного такту стартового сигналу на сьомий вхід синхронізації пристрою 19. Відпові 7 дно з цим стартовим сигналом здійснюється початкова установка регістрів першого блока додавання 2. Після цього по сигналу на третьому вході синхронізації пристрою 10 впродовж n тактів на першу групу входів першого блока додавання 2 порозрядно надходить значення підінтегральної функції на (i-1)-y кроці yр(і-1), починаючи зі старших розрядів. Водночас на другу групу входів цього блока порозрядно, починаючи із старших розрядів, подають через групу входів пристрою 4 приріст підінтегральної функції на на i-у кроці Δурi. І на його першій групі виходів із затримкою на 2 такти отримують, починаючи із старших . розрядів, суму, яка має вигляд: t1=уpi=yp(i-1)+Δурi. При цьому водночас з цим завантажують отримувані розряди значення підінтегральної функції yрі в регістр підінтегральної функції 1 через першу групу входів комутатора 3 та першу групу входів регістра підінтегральної функції 1 відповідно до згаданого вище сигналу на третьому вході синхронізації пристрою 10, а також подають його на першу групу входів першого блока додавання 17. Перед отримуванням старшого розряду yрі на другому виході першого блока додавання 2 формується сигнал st тривалістю в один такт. Він надходить на четвертий вхід блока множення 17, і за цим стартовим сигналом відбувається початкове встановлення регістрів цього блока. Одночасно з цим за сигналом на другому вході синхронізації пристрою 9 тривалістю n тактів з другої групи виходів регістру приросту аргументу 8 на другу групу входів блока множення 17 порозрядно надходить екстрапольоване значення аргументу інтегрування э для (i+1)-о кроку Dy q(i+1) , починаючи із старших розрядів. Із затримкою на 2 такти на першій групі входів блока множення 17 отримують, починаючи із старших розрядів, добуток, який має вигляд: t 2 = Dz(i +1) = t1Dy э (i+1) = ypi Dy э (i+1) , q q тобто черговий неквантований приріст інтегралу розрядністю (2n). Перед отриманням старшого розряду цього значення на другому виході блока множення 17 формується сигнал st2 тривалістю в один такт. Він надходить на другий вхід другого блока додавання 11, і за цим стартовим сигналом здійснюється початкове встановлення регістрів зазначеного блока. Отримувані розряди неквантованого приросту інтегралу Dz(i+1) послідовно надходять на першу групу входів другого блока додавання 11. Водночас на його четверту групу входів протягом n тактів з другої групи виходів регістру залишку інтегралу 13 подається нульове значення, а протягом наступних n тактів згідно з сигналом на четвертому вході синхронізації пристрою 14 - значення залишку інтегралу Sі на і-у кроці. Тоді із затримкою на 2 такти на групі виходів другого блока додавання 11 отримують, починаючи із старших розрядів, суму розрядністю (2n), що має вигляд: t3=t2+2-nS, Старші n розрядів значення t3 становлять квантоване значення приросту інтегралу Dz (i+1) . Саме вони згідно з сигналом на п'ятому вході синхроні 87073 8 зації пристрою 16 тривалістю n тактів завантажуються у регістр результату 12 через його першу групу . входів. Молодші n розрядів значення t3 становлять нове значення залишку інтегралу S(i+1). Вони за згаданим вище сигналом на четвертому вході синхронізації пристрою 14 протягом n тактів завантажуються в регістр залишку інтегралу 13 через його першу групу входів. Порівняємо швидкодію запропонованого пристрою з швидкодією пристрою-прототипу за умов одного рівня точності обчислень. Крок чисельного інтегрування в пристрої-прототипі [3] відповідає визначенню приросту інтегралу. Кожний крок розбитий на цикли. Цикл включає виконання операції множення n розрядів підінтегральної функції на один розряд приросту аргументу. Очевидно, що кількість тактів в одному кроці при однакових розрядностях n змінних, які інтегруються, становить: Т1=n2. (1) У запропонованому пристрої кожен з блоків додавання та множення виконаний квазіпараллельного типу і вносить двотактову затримку при формуванні старшого розряду приросту інтегралу. Тому кількість тактів для отримання всіх розрядів результату при проведенні обчислень в четвертинній симетричній надлишковій системі числення становить Т2=6+n. (2) При проведенні обчислень в запропонованому цифровому інтеграторі в двійковій симетричній надлишковій системі числення для збереження точності обчислень необхідно подвоїти розрядність змінних інтегрування. Тоді кількість тактів для отримання всіх розрядів приросту інтегралу буде становити T3=6+2n. (3) З урахуванням (1)-(3) при великій розрядності обчислень запропонований пристрій дозволяє підвищити швидкодію в першому випадку в T1 n2 = » n раз, T2 6 + n у другому випадку в T1 n2 n = » разів. T3 6 + 2n 2 Підвищення швидкодії запропонованого цифрового інтегратора стало можливим завдяки введенню нового блока і конструктивних зв'язків, а також зміні побудови існуючих блоків і зв'язків. Література: 1. Авторське свідоцтво СРСР №637833, кл. G 06 J 1/02, 1977. 2. Авторське свідоцтво СРСР №720427, кл. G 06 F 1/02. 1981. 3. Авторське свідоцтво СРСР №1330629 кk, G 06 F 7/64. 1985 (прототип). 4. Жабин В.И., Корнейчук В.И., Тарасенко В.П. Метод быстрого неавтономного воспроизведения функций // Управляющие системы и машины. 1977. - №3. - С. 96-101. 5. Жабин В.И.. Корнейчук В.И., Тарасенко В.П. Методы вычисления некоторых функций при поразрядном вводе и выводе информации // Известия вузов. Приборостроение. - 1978 - № . - С. 6460. 9 Комп’ютерна верстка Л. Купенко 87073 Підписне 10 Тираж 28 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюDigital integrator

Автори англійськоюKovaliov Mykola Oleksandrovych, Zhabin Valerii Ivanovych

Назва патенту російськоюЦифровой интегратор

Автори російськоюКовалев Николай Александрович, Жабин Валерий Иванович

МПК / Мітки

МПК: G01S 17/00, G06F 7/60, G01S 13/00

Мітки: інтегратор, цифровий

Код посилання

<a href="https://ua.patents.su/5-87073-cifrovijj-integrator.html" target="_blank" rel="follow" title="База патентів України">Цифровий інтегратор</a>

Попередній патент: Апарат гуцуляка в.і. для корекції деформацій кісток та суглобів

Наступний патент: Моноімпульсний пошуково-вимірювальний пеленгатор

Випадковий патент: Волоконно-оптичний датчик для вимірювання вологості і температури