Пристрій для перетворення інформації

Номер патенту: 20924

Опубліковано: 07.10.1997

Автори: Кожан Володимир Петрович, Стрямець Сергій Петрович, Деркач Богдан Теодорович, Кисіль Богдан Васильович

Формула / Реферат

1. Устройство для преобразования информации, содержащее матрицу запоминающих ячеек (МЗЯ), состоящую из запоминающих ячеек (ЗЯ), входных и выходных ключей, причем группа входов данных подключена к группам входов входных и выходных ключей, выходы которых подключены к группе выходов МЗЯ, две группы входов-выходов входных ключей подключены к первым и вторым входам выходам данных запоминающих ячеек, третьи и четвертые входы-выходы данных которых подключены к двум группам входов-выходов выходных ключей, управляющие входы Г/В всех ЗЯ входных ключей соединены между собой и подключены к входу Г/В МЗЯ, входы А/В входных и выходных ключей соединены между собой и подключены к входу А/В МЗЯ, группа входов синхронизирующих импульсов с МЗЯ подключена к первым синхронизирующим входам первого столбца матрицы и к вторым синхронизирующим входам первой строки матрицы, первые выходы синхронизации первого столбца матрицы подключены к первым входам синхронизации второго столбца матрицы и т.д. вторые входы синхронизации первой строки подключены к вторым входам синхронизации строки матрицы и т.д., третьи входы-выходы данных первого столбца матрицы подключены к первым входам/выходам данных второго столбца матрицы и т.д., четвертые входы-выходы данных первой строки матрицы подключены ко вторым входам-выходам данных второй строки матрицы и т.д., входы R всех ЗЯ матрицы соединены между собой и подключены к входу R матрицы, входы Тр ЗЯ, находящихся на диагонали матрицы соединены между собой и подключены к входу ТрЗ матрицы, входы Тр ЗЯ, находящихся выше диагонали матрицы, соединены между собой и подключены к входу Тр2 матрицы, входы Тр ЗЯ, находящихся ниже диагонали матрицы соединены между собой и подключены к входу Тр1 матрицы, отличающееся тем, что в него введены два инвертора (И), два блока коммутаторов (БК), блок диагностики (БД), два блока управления коммутаторами (БУК), блок управления матрице (БУМ), генератор тактовых импульсов (ГТИ), причем группа входов данных устройства подключена к группе входов данных инвертора, группа выходов данных которого подключена к группе входов данных первого коммутатора, выходы данных которого подключены к группе входов данных МЗЯ, группа выходов данных которой подключена к группе входов данных второго коммутатора, группа выходов данных которого подключена к группе входов данных второго инвертора выходы данных которого являются выходами данных устройства, две группы управляющих входов блока диагностики (БД) являются управляющими входами устройства, вход ОРЗ БД подключен к выходу ОРЗ ГТИ и к входам ОРЗ первого блока управления коммутаторами (БУК), вход Сч блока диагностики подключен к выходу Сч. ГТИ и к входам СЧ блоков управления коммутаторами, выходы УИ1 и УИ2 блока диагностики (БД) подключены к управляющим входам первого и второго инверторов, управляющие выходы 1,2,3 и 4,5,6 БД подключены к управляющим входам 1,2,3 и 4,5,6 второго и первого БУК соответственно, выходы А/В, Тр1, Тр2, ТрЗ БД подключены к входам А/В, Тр1, Тр2 и ТрЗ МЗЯ, кроме того, выход ТрЗ подключен к входу ТрЗ ГТИ и к входу ТрЗ первого БУК, выходы Г/В, S, Р Сдв БД подключены к входам Г/В, S, Р, Сдв блока управления матрицей, выход Г БД подключен к входу Г ГТИ, выходы ТЙ которого подключены к входу ТИ БУМ и к входам ТИ первого и второго БУК, выход ОРЗ ГТИ подключен к входам ОРЗ и ТрЗ второго БУК, входы N ГТИ, БУК1 и БУК2 объединены и являются входами N устройства, входы R ГТИ, МЗЯ БУК1 и БУК2 соединены между собой и подключены к входу R устройства, выход Гот. ГТИ подключен к выходу Год устройства, группы управляющих выходов БУК1 и БУК2 подключены к группам управляющих входов первого и второго БК соответственно, выход Г/В БУМ подключены к входу Г/В МЗЯ, группа управляющих входов (С) которой подключена к группе управляющих выходов в БУМ.

2. Устройство для преобразования информации по п. 1,отличающееся тем, что запоминающая ячейка содержит регистр, инвертор, два элемента И, группу ' ключей, причем первая и вторая группы входов-выходов ЗЯ соединены между собой и подключены к входам А регистра и к первой группе входов-выходов ключей, вторые и третьи входы-выходы которых подключены к вторым и третьим входам-выходам данных ЗЯ и к первым и вторым входам синхронизации, четвертая группа входов-выходов ключей подключена к входам В регистра, один из входов-выходов четвертой группы ключей подключены к первому и второму входам синхронизации и к входу С регистра, вход A/S которого подключен к входу R ЗЯ и к входу инвертора, выход которого подключен к первому входу первого элемента И, второй вход которого подключен к входу Тр ЗЯ, а выход к первому управляющему входу ключей и к первому входу второго элемента И, второй вход которого подключен к входу А/В ЗЯ а выход подключен к входу А/В регистра, второй управляющий вход ключей подключен к входу Г/В ЗЯ.

3. Устройство для преобразования по п. 1, отличающееся тем, что блок управления матрицей содержит регистр, элемент И, инвертор, первую и вторую группы элементов И, причем вход Г/В блока управления матрицей подключен к выходу Г/В блока управления, к первым входам второй группы элементов И, и к входу инвертора, выход которого подключен к первым входам первой группы элементов И, последовательный вход регистра подключен к шине питания, а входы S и Р к входам S и Р блока управления матрицей, вход Сдв которого подключен к первому входу элемента И, второй вход которого подключен к входу ТИ блока управления и ко всем третьим входам первой и второй групп элементов И, а выход элемента И подключен к входу С регистра, вход R которого подключен к входу R блока управления, а выходы регистра подключены к вторым входам первой и второй групп элементов И, выходы которых подключены к группе управляющих выходов блока управления матрицей.

4. Устройство для преобразования информации по п. 1,отличающееся тем, что инвертор содержит первую и вторую группу ключей и элемент ИЛИ-НЕ, причем управляющий вход инвертора подключен ко всем управляющим входам второй группы ключей и к входу элемента ИЛИ-НЕ, выход которого подключен ко всем управляющим входам первой группы ключей, входы данных которых подключены к группе входов данных инвертора, входы данных второй группы ключей подключены к группе входов данных инвертора в обратном порядке, первый к последнему, второй к предпоследнему и т.д., последний вход ключей подключен к первому входу данных инвертора, выходы первой и второй групп ключей объединены и подключены к группе выходов данных инвертора.

5. Устройство для преобразования информации по п. 1, отличающееся тем, что блок коммутаторов содержит К групп мультиплексоров-демультиплексоров, при чем все входы управления в группах соединены параллельно и подключены к группе управляющих входов блока коммутаторов, все синхронизирующие входы мультиплексоров-демультиплексоров соединены вместе и подключены к синхронизирующему входу группы управляющих входов, выходы всех мультиплексоров-демультиплексоров подключены к группе выходов данных блока коммутаторов, группа входов данных которого подключена к входам данных первого мультиплексора-демультиплексора, ко всем последующим подключаются со сдвигом на один разряд.

6. Устройство для преобразования информации по п. 1, отличающееся тем, что блок управления коммутаторами содержит первый, второй и третий регистры сдвига, счетчик, ПЗУ, две группы элементов И, три элемента И, два инвертора, элемент И-НЕ, элемент ИЛИ, причем группа управляющих выходов блока управления коммутаторами подключена к выходам регистров, входы последовательной записи которых подключены к выходам первой группы элементов И, выходы второй группы элементов И подключены к входам Р регистров; входы С которых объединены и подключены к входу С счетчика, к выходу первого элемента И и к группе управляющих выходов блока управления, входы Д всех регистров объединены и подключены к нулевой шине, входы S всех регистров объединены и подключены к первым входам первой группы элементов И, к входу первого инвертора и к первому управляющему входу группы управляющих входов, третий управляющий вход группы управляющих входов подключен к входу второго инвертора, к первому входу первого элемента И, и к первому входу второго элемента И, выходы которого подключены к входу S счетчика, а второй вход подключен к первому входу третьего элемента И, к входам R всех регистров и к входу R блока управления коммутаторами, входы Тр 3 и ОРЗ которого подключены к первому и второму входам элемента И-НЕ, выход которого подключен к второму входу первого элемента И, третий вход которого подключен к входу ТИ блока управления коммутаторами, входы N которого подключены к адресным входам ПЗУ, вход считывания которого подключен к входу Сч блока управления коммутаторами, второй управляющий вход группы управляющих входов которого подключен к одному из адресных входов ПЗУ и к входу И счетчика, входы D которого подключены к выходам ПЗУ, а вход R к выходу элемента ИЛИ 6 первый вход которого подключен к выходу третьего элемента И, второй вход которого подключен к выходу второго инвертора, второй вход элемента ИЛИ подключен к выходу 8 счетчика, выходы 1, 2, 4 которого подключены к вторым входам первой и второй групп элементов И, первые входы второй группы элементов И объединены и подключены к выходу первого инвертора.

7. Устройство для преобразования информации по п. 1, отличающееся тем, что блок диагностики содержит ПЗУ, четыре элемента И, два элемента ИЛИ-НЕ, элемент И-ИЕ, два элемента ИЛИ, причем первые разряды первой и второй групп входов блока диагностики подключены к выходам УИ1 и УИ2, входы вторых и третьих разрядов первой и второй групп входов блока диагностики подключены к адресным входам ПЗУ, вход четвертого разряда первой группы входов подключен к одному из разрядов ПЗУ, к входу первого элемента ИЛИ-НЕ, и к первому входу первого элемента И, выход которого подключен к первому выходу группы управляющих выходов блока диагностики, второй выход которой подключен к выходу элемента И-НЕ первый вход которого подключен к выходу первого элемента ИЛИ-НЕ, пятый разряд первой группы управляющих входов подключен к второму входу первого элемента И и к первому входу первого элемента ИЛИ, выход которого подключен к третьему выходу группы управляющих выходов, шестой разряд первой группы управляющих входов подключен к вторым входам, элемента И-НЕ и элемента ИЛИ, четвертый разряд второй группы управляющих входов блока диагностики подключен к входу элемента ИЛИ-НЕ, к первому входу второго элемента И и к одному из разрядов ПЗУ, выходы . которого подключены к выходам А/В, Г/В, S, Р, Сдв, Тр1, Тр2, Г блока диагностики, четвертый и пятый выходы группы управляющих выходов которого подключены к выходам второго и третьего элементов И, пятый разряд второй группы управляющих входов блока диагностики подключен к второму входу второго элемента И и к первому входу элемента ИЛИ, выход которого подключен к шестому выходу группы управляющих выходов блока диагностики, выход ТрЗ которого подключен к выходу четвертого элемента И к входам которого подключены выходы Тр1 и Тр2 ПЗУ, шестой разряд второй группы управляющих входов блока диагностики подключен к вторым входам третьего элемента И и второго элемента ИЛИ, управляющий вход ОРЗ блока диагностики подключен к одному из адресных входов ПЗУ, вход считывания которого подключен к входу Сч блока диагностики.

8. Устройство для преобразования информации по п. 1, отличающееся тем, что блок ключей содержит N группы ключей и два инвертора, причем одноименные разряды четырех входов-выходов данных блока ключей подключены к входам четырех ключей первой группы, управляющие входы первых ключей подключены к выходу первого инвертора, вход которого подключен к управляющим входам вторых ключей и к входу А/В блока ключей, вход Г/В которого подключен к управляющим входам четвертых ключей и к входу второго инвертора, выход которого подключен к управляющим входам третьих ключей, выходы всех ключей одноименных разрядов соединены между собой.

9. Устройство для преобразования информации по п. 1, отличающееся тем, что генератор тактовых импульсов содержит генератор импульсов, счетчик, компаратор, ПЗУ, два триггера, три элемента и инвертор, элемент ИЛИ, причем группа входов кодов размерности матрицы подключены к адресным входам ПЗУ, выходы которого подключены к первой группе входсів компаратора, вторая группа входов которого подключена к выходам счетчика, вход "+1" которого подключен к выходу ТИ генератора тактовых импульсов и к выходу первого элемента И, первый вход которого подключен к выходу генератора импульсов, к входу считывания ПЗУ и к выходу Сч генератора тактовых импульсов, вход Г которого подключен к одному из адресных входов ПЗУ, а вход ТрЗ подключен к одному из адресных входов ПЗУ и к входу инвертора, выход которого подключен к первому входу второго элемента И, второй вход которого подключен к первому входу третьего элемента И, к входу R счетчика, к выходу компаратора и к входу S первого триггера, вход R которого подключен к входу S второго триггера и к выходу элемента ИЛИ, первый и второй входы которого подключены к выходам второго и третьего элементов И, второй вход третьего элемента И подключен к прямому выходу первого триггера и к выходу, ОРЗ генератора тактовых импульсов, выход ОРЗ которого подключен к инверсному выходу первого триггера, вход R второго триггера подключен к входу R генератора тактовых импульсов, выход Гот которого подключен к прямому выходу второго триггера, инверсный выход которого подключен к второму входу первого элемента И.

Текст

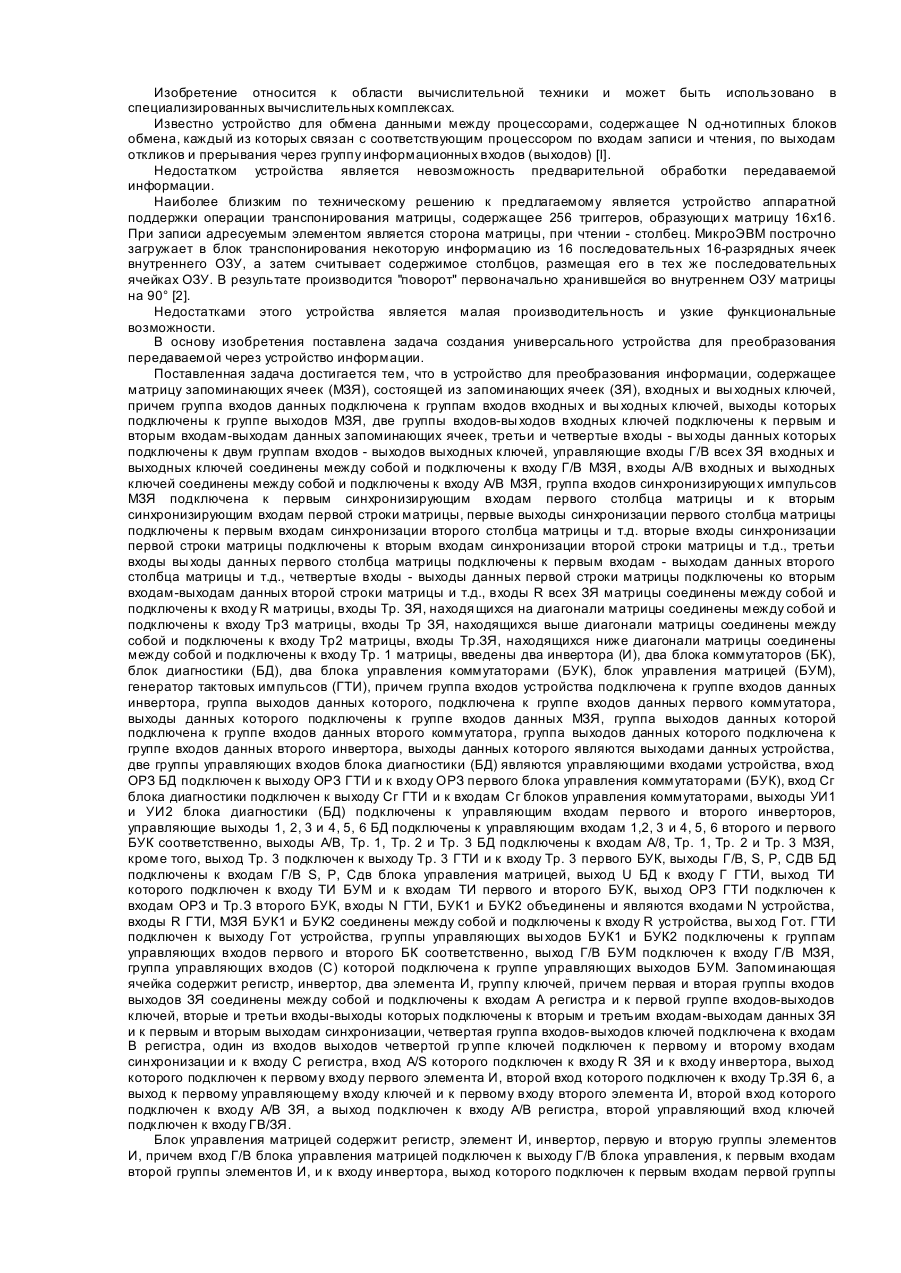

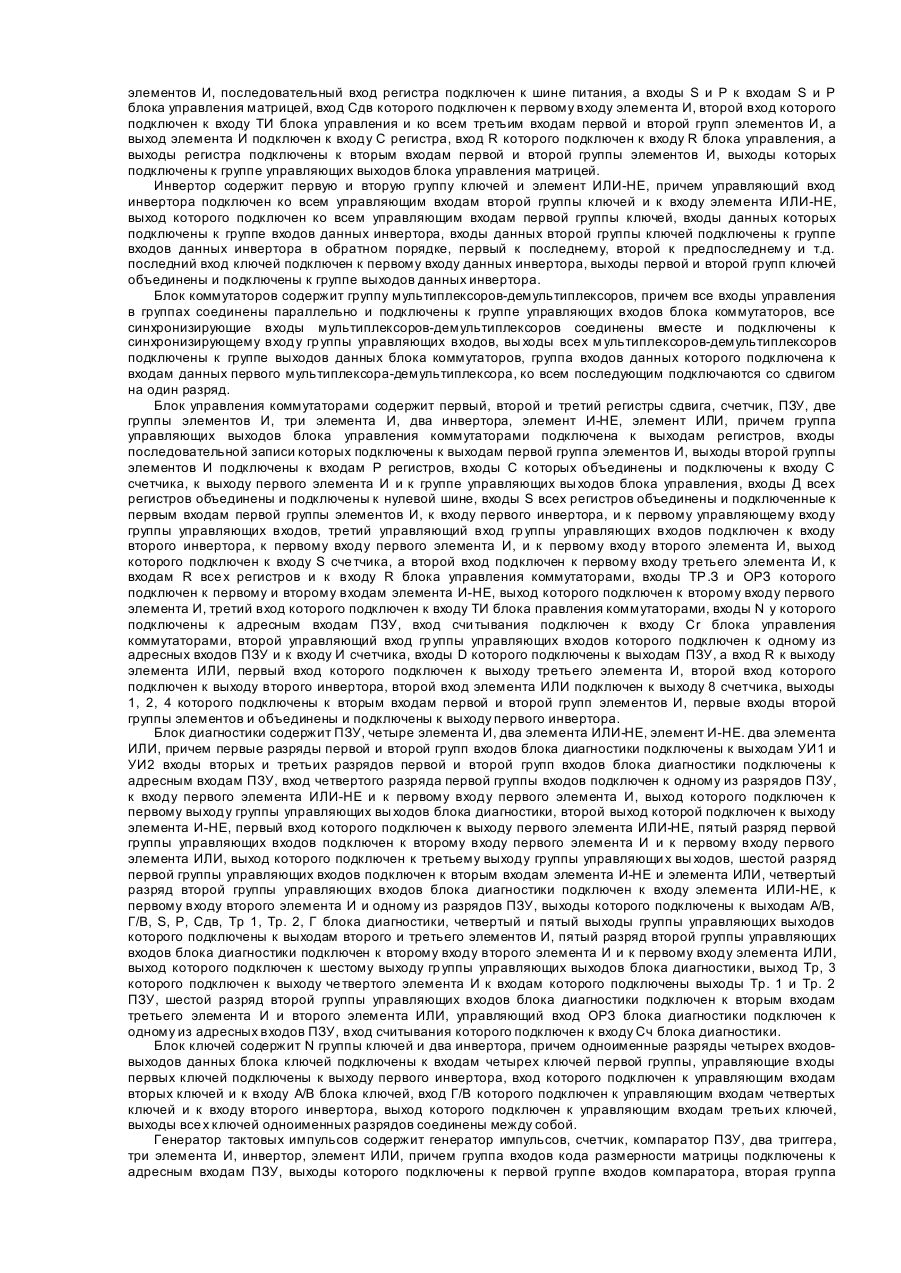

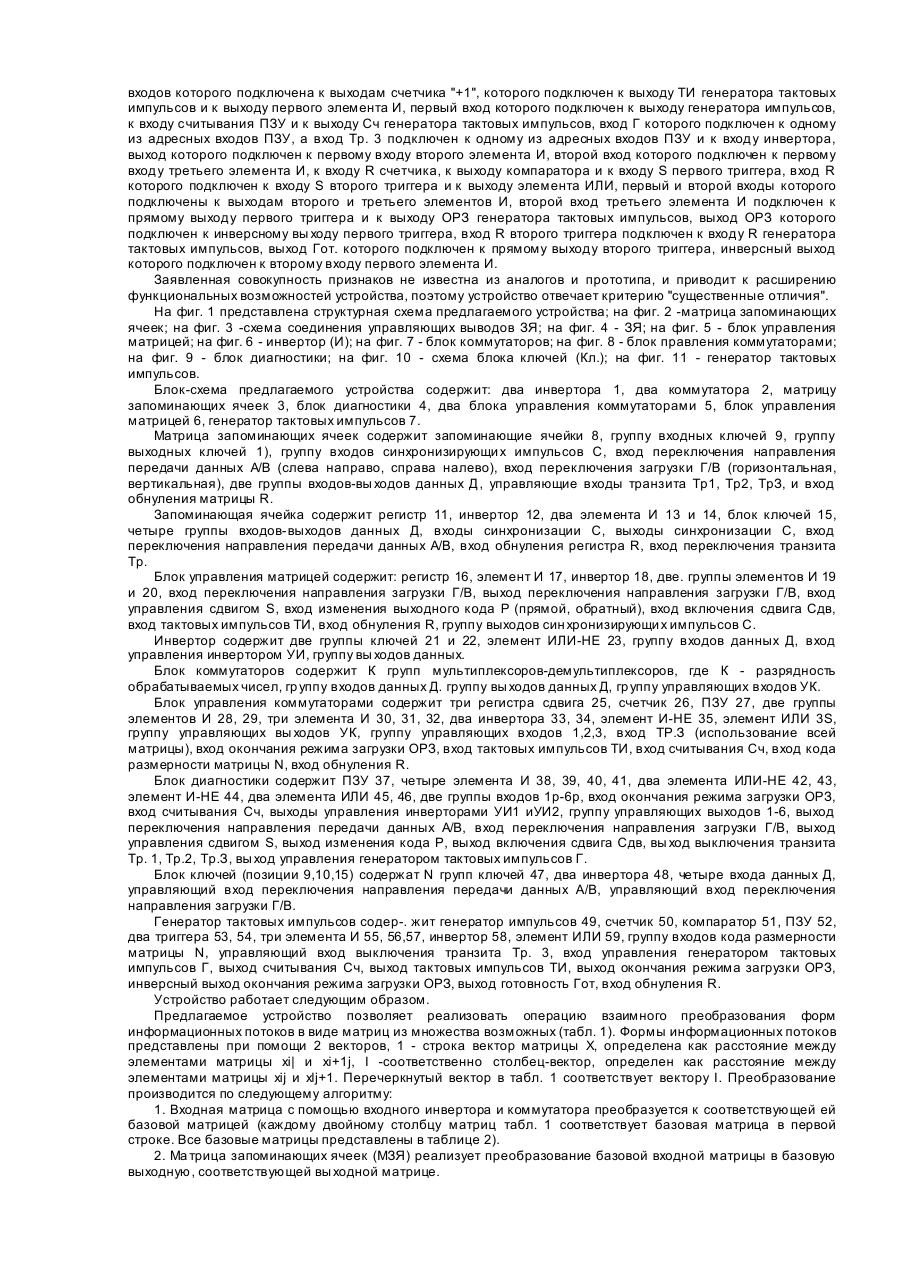

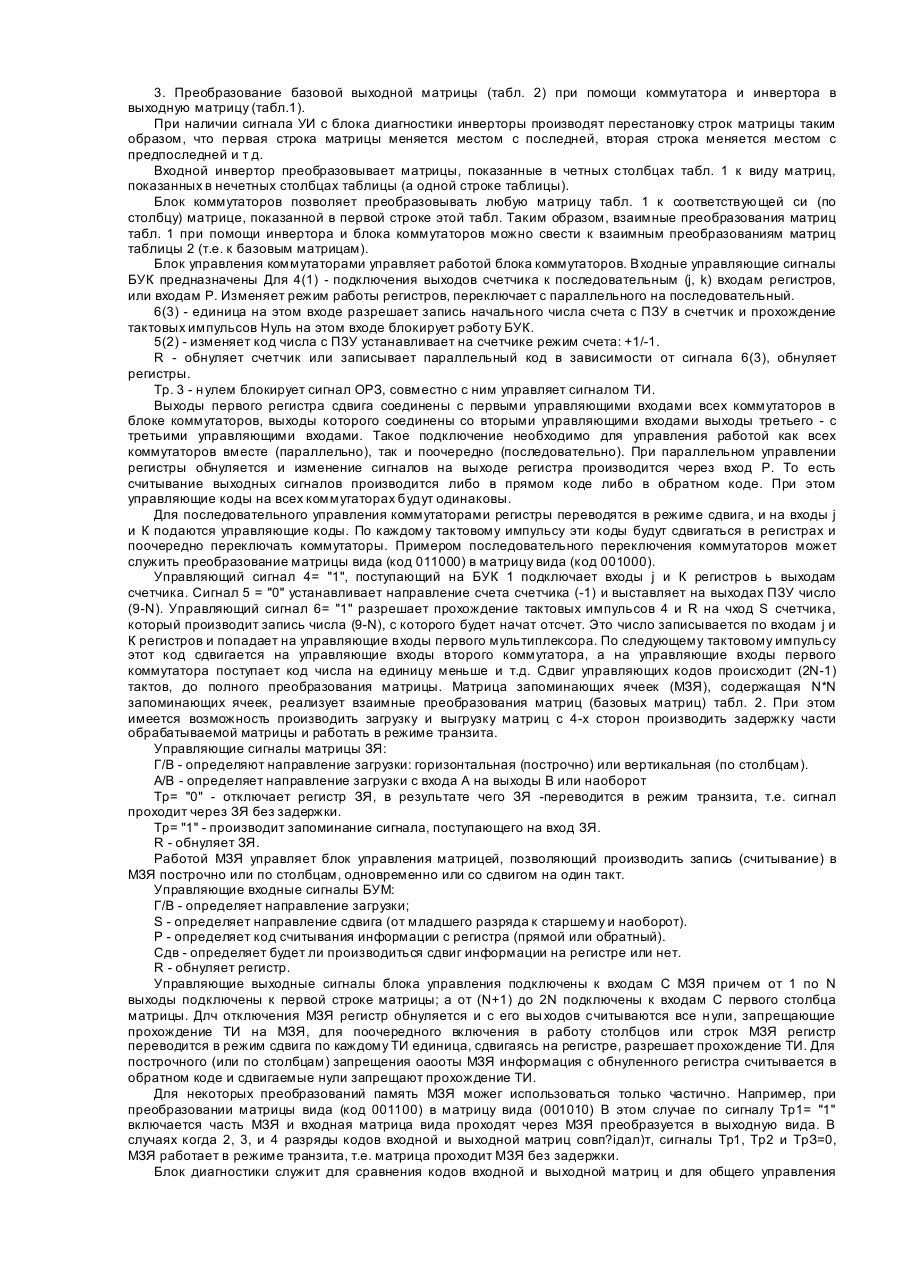

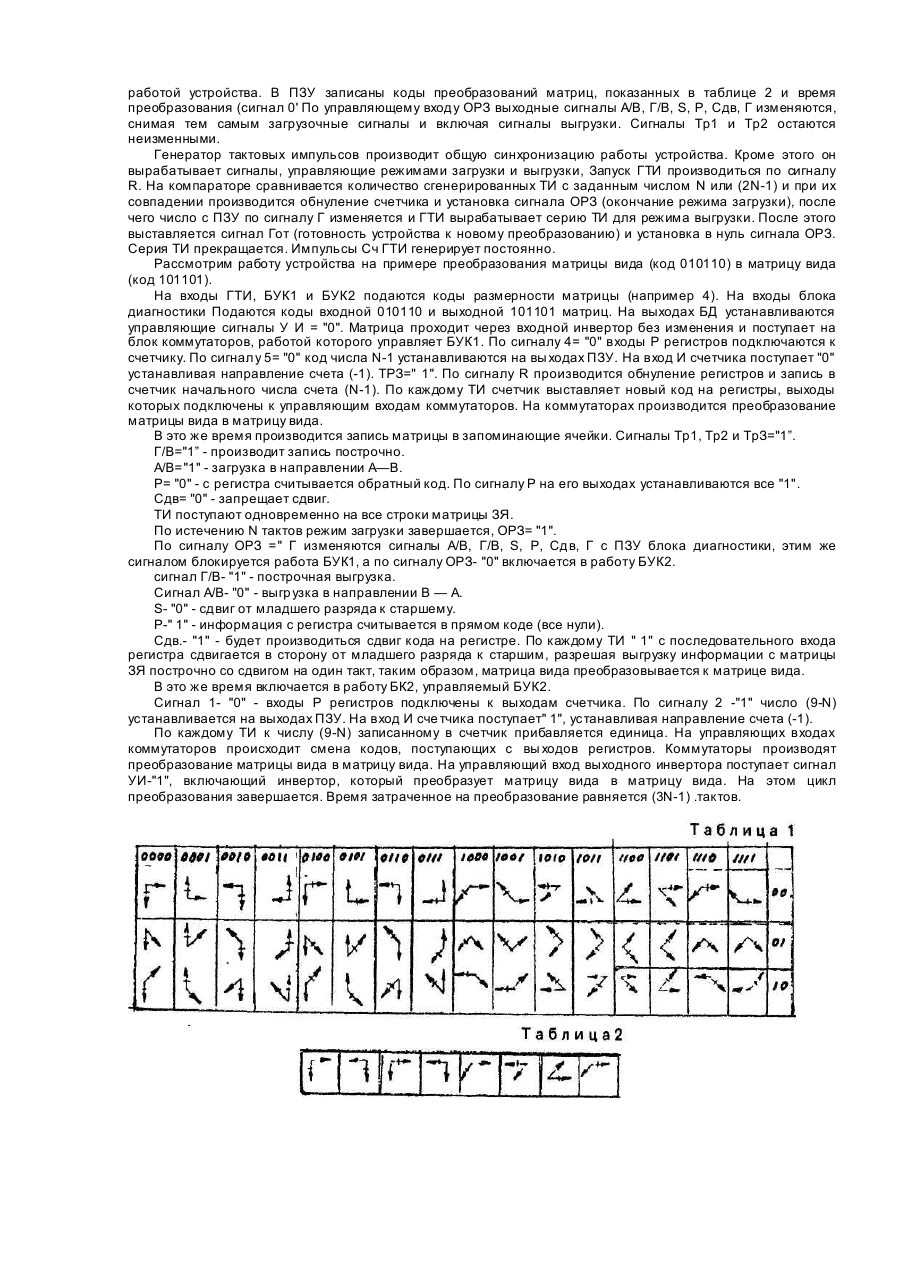

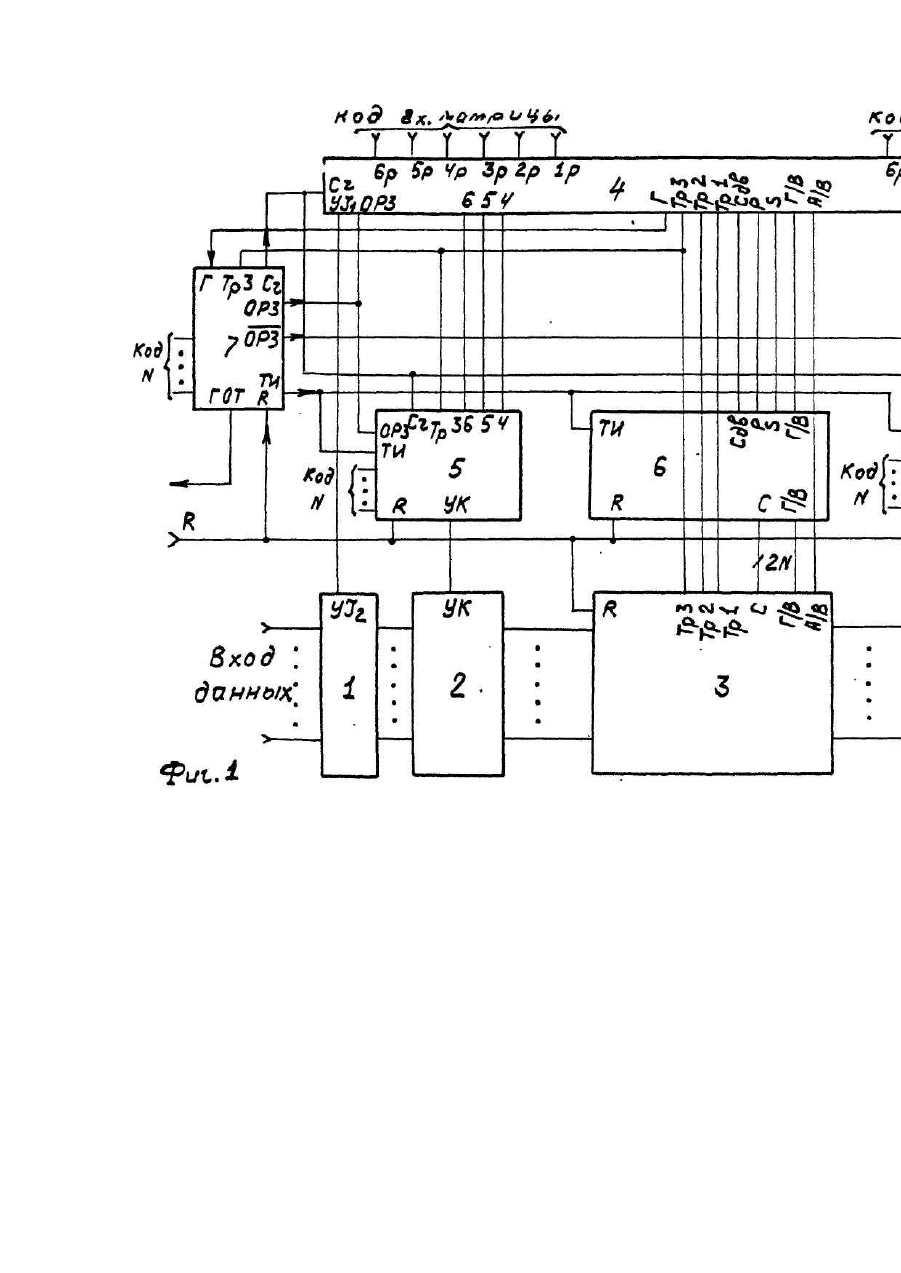

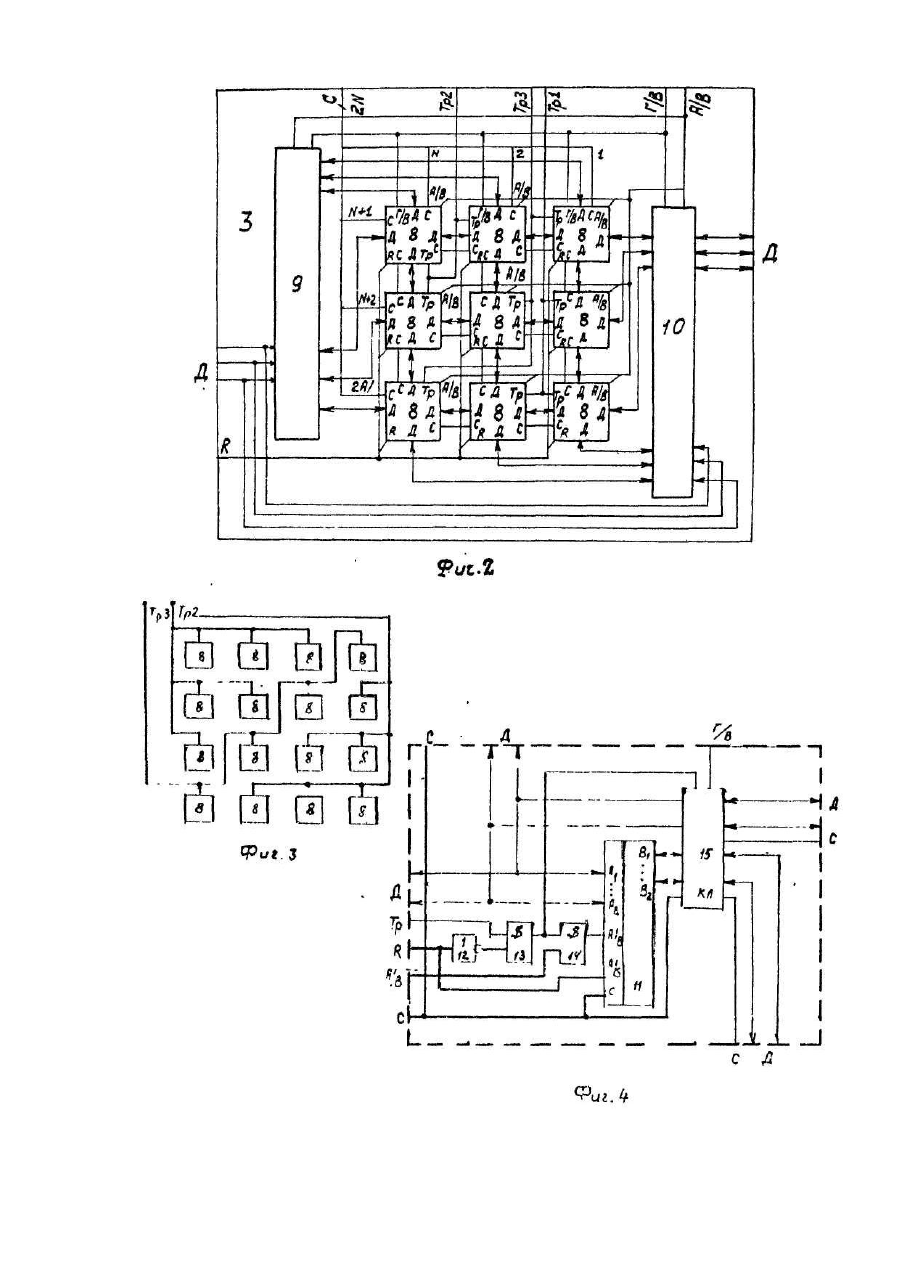

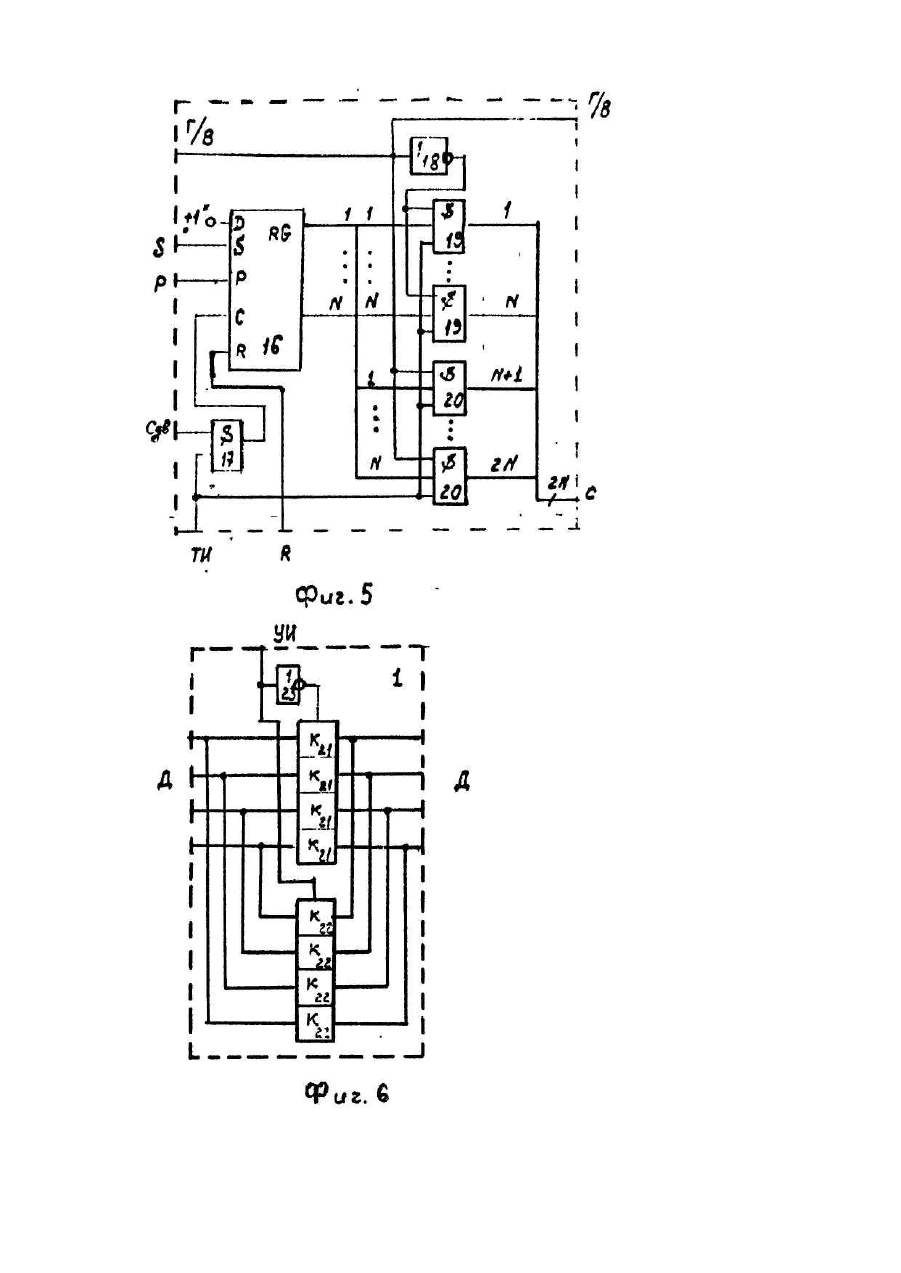

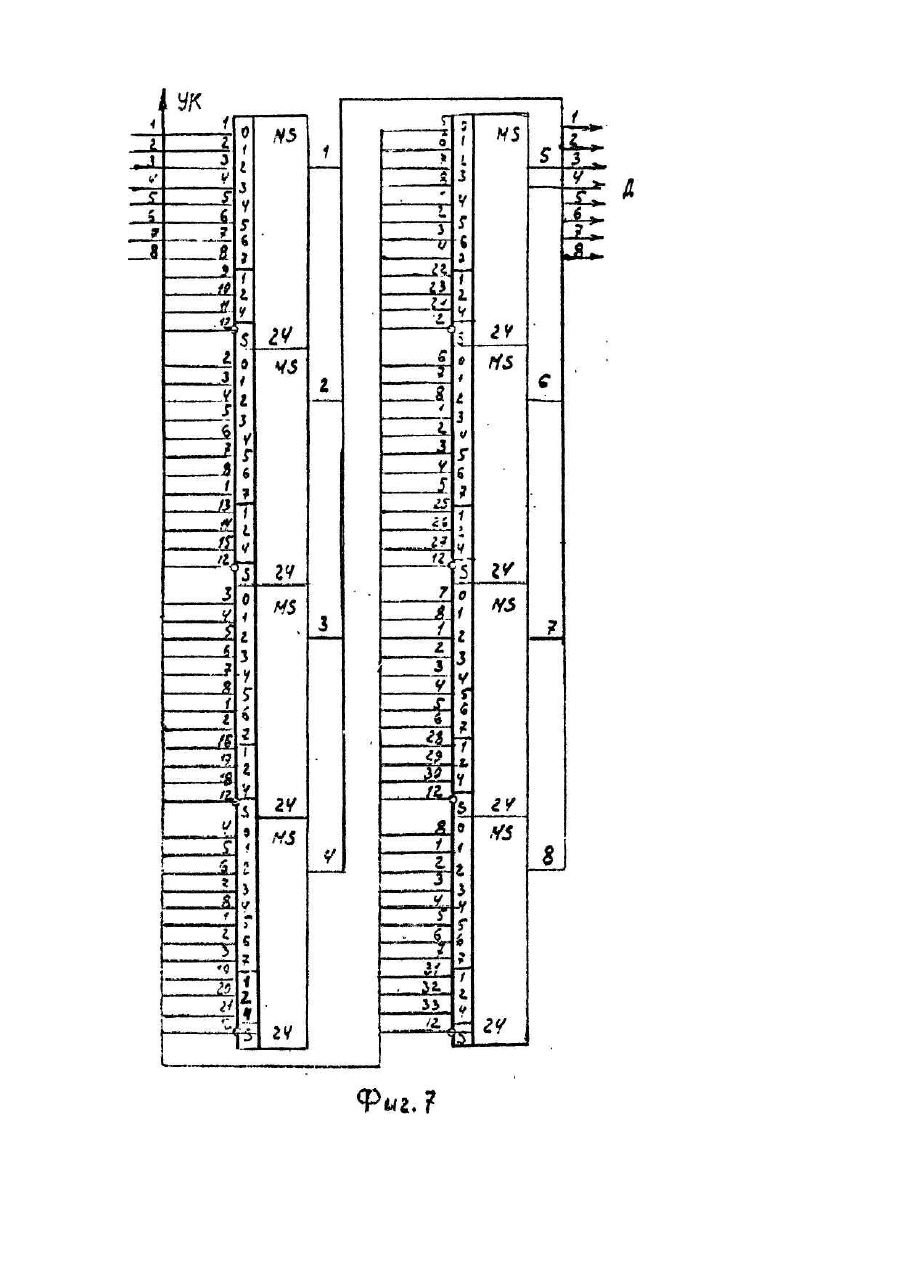

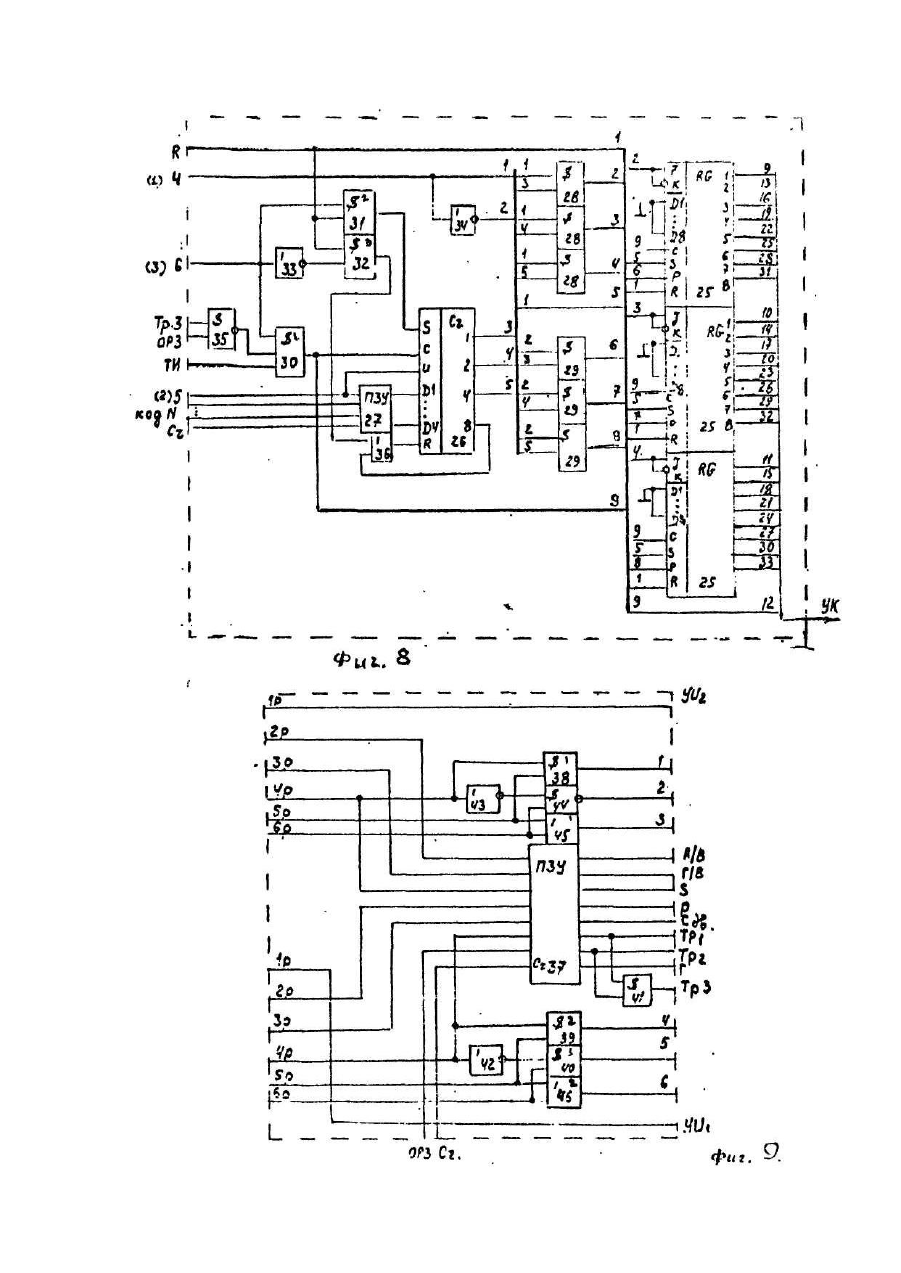

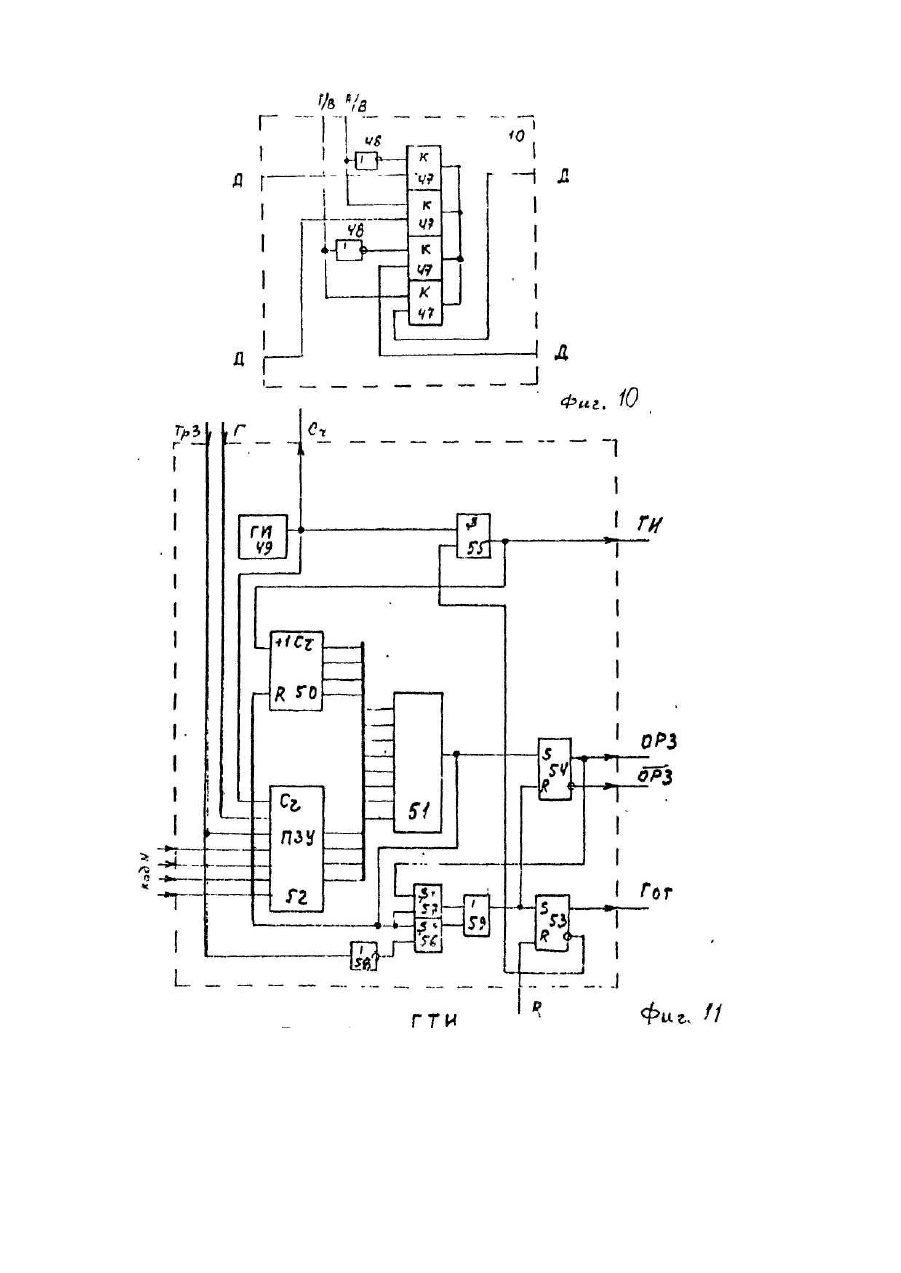

Изобретение относится к области вычислительной техники и может быть использовано в специализированных вычислительных комплексах. Известно устройство для обмена данными между процессорами, содержащее N од-нотипных блоков обмена, каждый из которых связан с соответствующим процессором по входам записи и чтения, по выходам откликов и прерывания через группу информационных входов (выходов) [I]. Недостатком устройства является невозможность предварительной обработки передаваемой информации. Наиболее близким по техническому решению к предлагаемому является устройство аппаратной поддержки операции транспонирования матрицы, содержащее 256 триггеров, образующи х матрицу 16x16. При записи адресуемым элементом является сторона матрицы, при чтении - столбец. МикроЭВМ построчно загружает в блок транспонирования некоторую информацию из 16 последовательных 16-разрядных ячеек внутреннего ОЗУ, а затем считывает содержимое столбцов, размещая его в тех же последовательных ячейках ОЗУ. В результате производится "поворот" первоначально хранившейся во внутреннем ОЗУ матрицы на 90° [2]. Недостатками этого устройства является малая производительность и узкие функциональные возможности. В основу изобретения поставлена задача создания универсального устройства для преобразования передаваемой через устройство информации. Поставленная задача достигается тем, что в устройство для преобразования информации, содержащее матрицу запоминающих ячеек (МЗЯ), состоящей из запоминающих ячеек (ЗЯ), входных и вы ходных ключей, причем группа входов данных подключена к группам входов входных и вы ходных ключей, выходы которых подключены к группе выходов МЗЯ, две группы входов-вы ходов входных ключей подключены к первым и вторым входам-выходам данных запоминающих ячеек, третьи и четвертые входы - вы ходы данных которых подключены к двум группам входов - выходов выходных ключей, управляющие входы Г/В всех ЗЯ входных и выходных ключей соединены между собой и подключены к входу Г/В МЗЯ, входы А/В входных и выходных ключей соединены между собой и подключены к входу А/В МЗЯ, группа входов синхронизирующи х импульсов МЗЯ подключена к первым синхронизирующим входам первого столбца матрицы и к вторым синхронизирующим входам первой строки матрицы, первые выходы синхронизации первого столбца матрицы подключены к первым входам синхронизации второго столбца матрицы и т.д. вторые входы синхронизации первой строки матрицы подключены к вторым входам синхронизации второй строки матрицы и т.д., третьи входы вы ходы данных первого столбца матрицы подключены к первым входам - выходам данных второго столбца матрицы и т.д., четвертые входы - выходы данных первой строки матрицы подключены ко вторым входам-выходам данных второй строки матрицы и т.д., входы R всех ЗЯ матрицы соединены между собой и подключены к входу R матрицы, входы Тр. ЗЯ, находя щихся на диагонали матрицы соединены между собой и подключены к входу ТрЗ матрицы, входы Тр ЗЯ, находящихся выше диагонали матрицы соединены между собой и подключены к входу Тр2 матрицы, входы Тр.ЗЯ, находящихся ниже диагонали матрицы соединены между собой и подключены к входу Тр. 1 матрицы, введены два инвертора (И), два блока коммутаторов (БК), блок диагностики (БД), два блока управления коммутаторами (БУК), блок управления матрицей (БУМ), генератор тактовых импульсов (ГТИ), причем группа входов устройства подключена к группе входов данных инвертора, группа выходов данных которого, подключена к группе входов данных первого коммутатора, выходы данных которого подключены к группе входов данных МЗЯ, группа выходов данных которой подключена к группе входов данных второго коммутатора, группа выходов данных которого подключена к группе входов данных второго инвертора, выходы данных которого являются выходами данных устройства, две группы управляющих входов блока диагностики (БД) являются управляющими входами устройства, вход ОРЗ БД подключен к выходу ОРЗ ГТИ и к входу ОРЗ первого блока управления коммутаторами (БУК), вход Сг блока диагностики подключен к выходу Сг ГТИ и к входам Сг блоков управления коммутаторами, выходы УИ1 и УИ2 блока диагностики (БД) подключены к управляющим входам первого и второго инверторов, управляющие выходы 1, 2, 3 и 4, 5, 6 БД подключены к управляющим входам 1,2, 3 и 4, 5, 6 второго и первого БУК соответственно, выходы А/В, Тр. 1, Тр. 2 и Тр. 3 БД подключены к входам А/8, Тр. 1, Тр. 2 и Тр. 3 МЗЯ, кроме того, выход Тр. 3 подключен к выходу Тр. 3 ГТИ и к входу Тр. 3 первого БУК, выходы Г/В, S, Р, СДВ БД подключены к входам Г/В S, Р, Сдв блока управления матрицей, выход U БД к входу Г ГТИ, выход ТИ которого подключен к входу ТИ БУМ и к входам ТИ первого и второго БУК, выход ОРЗ ГТИ подключен к входам ОРЗ и Тр.З второго БУК, входы N ГТИ, БУК1 и БУК2 объединены и являются входами N устройства, входы R ГТИ, МЗЯ БУК1 и БУК2 соединены между собой и подключены к входу R устройства, вы ход Гот. ГТИ подключен к выходу Гот устройства, гр уппы управляющих вы ходов БУК1 и БУК2 подключены к группам управляющих входов первого и второго БК соответственно, выход Г/В БУМ подключен к входу Г/В МЗЯ, группа управляющих входов (С) которой подключена к группе управляющих выходов БУМ. Запоминающая ячейка содержит регистр, инвертор, два элемента И, группу ключей, причем первая и вторая группы входов выходов ЗЯ соединены между собой и подключены к входам А регистра и к первой группе входов-выходов ключей, вторые и третьи входы-выходы которых подключены к вторым и третьим входам-выходам данных ЗЯ и к первым и вторым выходам синхронизации, четвертая группа входов-выходов ключей подключена к входам В регистра, один из входов выходов четвертой гр уппе ключей подключен к первому и второму входам синхронизации и к входу С регистра, вход A/S которого подключен к входу R ЗЯ и к входу инвертора, выход которого подключен к первому входу первого элемента И, второй вход которого подключен к входу Тр.ЗЯ 6, а выход к первому управляющему входу ключей и к первому входу второго элемента И, второй вход которого подключен к входу А/В ЗЯ, а выход подключен к входу А/В регистра, второй управляющий вход ключей подключен к входу ГВ/ЗЯ. Блок управления матрицей содержит регистр, элемент И, инвертор, первую и вторую группы элементов И, причем вход Г/В блока управления матрицей подключен к выходу Г/В блока управления, к первым входам второй группы элементов И, и к входу инвертора, выход которого подключен к первым входам первой группы элементов И, последовательный вход регистра подключен к шине питания, а входы S и Р к входам S и Р блока управления матрицей, вход Сдв которого подключен к первому входу элемента И, второй вход которого подключен к входу ТИ блока управления и ко всем третьим входам первой и второй групп элементов И, а выход элемента И подключен к входу С регистра, вход R которого подключен к входу R блока управления, а выходы регистра подключены к вторым входам первой и второй группы элементов И, выходы которых подключены к группе управляющих выходов блока управления матрицей. Инвертор содержит первую и вторую группу ключей и элемент ИЛИ-НЕ, причем управляющий вход инвертора подключен ко всем управляющим входам второй группы ключей и к входу элемента ИЛИ-НЕ, выход которого подключен ко всем управляющим входам первой группы ключей, входы данных которых подключены к группе входов данных инвертора, входы данных второй группы ключей подключены к группе входов данных инвертора в обратном порядке, первый к последнему, второй к предпоследнему и т.д. последний вход ключей подключен к первому входу данных инвертора, выходы первой и второй групп ключей объединены и подключены к группе выходов данных инвертора. Блок коммутаторов содержит группу мультиплексоров-демультиплексоров, причем все входы управления в группах соединены параллельно и подключены к группе управляющих входов блока коммутаторов, все синхронизирующие входы мультиплексоров-демультиплексоров соединены вместе и подключены к синхронизирующему входу гр уппы управляющих входов, вы ходы всех м ультиплексоров-демультиплексоров подключены к группе выходов данных блока коммутаторов, группа входов данных которого подключена к входам данных первого мультиплексора-демультиплексора, ко всем последующим подключаются со сдвигом на один разряд. Блок управления коммутаторами содержит первый, второй и третий регистры сдвига, счетчик, ПЗУ, две группы элементов И, три элемента И, два инвертора, элемент И-НЕ, элемент ИЛИ, причем группа управляющих выходов блока управления коммутаторами подключена к выходам регистров, входы последовательной записи которых подключены к выходам первой группа элементов И, выходы второй группы элементов И подключены к входам Р регистров, входы С которых объединены и подключены к входу С счетчика, к выходу первого элемента И и к группе управляющих вы ходов блока управления, входы Д всех регистров объединены и подключены к нулевой шине, входы S всех регистров объединены и подключенные к первым входам первой группы элементов И, к входу первого инвертора, и к первому управляющему входу группы управляющих входов, третий управляющий вход гр уппы управляющих входов подключен к входу второго инвертора, к первому входу первого элемента И, и к первому входу второго элемента И, выход которого подключен к входу S сче тчика, а второй вход подключен к первому входу третьего элемента И, к входам R все х регистров и к входу R блока управления коммутаторами, входы ТР.З и ОРЗ которого подключен к первому и второму входам элемента И-НЕ, выход которого подключен к второму входу первого элемента И, третий вход которого подключен к входу ТИ блока правления коммутаторами, входы N у которого подключены к адресным входам ПЗУ, вход счи тывания подключен к входу Сr блока управления коммутаторами, второй управляющий вход гр уппы управляющих входов которого подключен к одному из адресных входов ПЗУ и к входу И счетчика, входы D которого подключены к выходам ПЗУ, а вход R к выходу элемента ИЛИ, первый вход которого подключен к выходу третьего элемента И, второй вход которого подключен к выходу второго инвертора, второй вход элемента ИЛИ подключен к выходу 8 счетчика, выходы 1, 2, 4 которого подключены к вторым входам первой и второй групп элементов И, первые входы второй группы элементов и объединены и подключены к выходу первого инвертора. Блок диагностики содержит ПЗУ, четыре элемента И, два элемента ИЛИ-НЕ, элемент И-НЕ. два элемента ИЛИ, причем первые разряды первой и второй групп входов блока диагностики подключены к выходам УИ1 и УИ2 входы вторых и третьих разрядов первой и второй групп входов блока диагностики подключены к адресным входам ПЗУ, вход четвертого разряда первой группы входов подключен к одному из разрядов ПЗУ, к входу первого элемента ИЛИ-НЕ и к первому входу первого элемента И, выход которого подключен к первому выходу группы управляющих вы ходов блока диагностики, второй выход которой подключен к выходу элемента И-НЕ, первый вход которого подключен к выходу первого элемента ИЛИ-НЕ, пятый разряд первой группы управляющих входов подключен к второму входу первого элемента И и к первому входу первого элемента ИЛИ, выход которого подключен к третьему выходу группы управляющи х вы ходов, шестой разряд первой группы управляющих входов подключен к вторым входам элемента И-НЕ и элемента ИЛИ, четвертый разряд второй группы управляющих входов блока диагностики подключен к входу элемента ИЛИ-НЕ, к первому входу второго элемента И и одному из разрядов ПЗУ, выходы которого подключены к выходам А/В, Г/В, S, Р, Сдв, Тр 1, Тр. 2, Г блока диагностики, четвертый и пятый выходы группы управляющих выходов которого подключены к выходам второго и третьего элементов И, пятый разряд второй группы управляющих входов блока диагностики подключен к второму входу второго элемента И и к первому входу элемента ИЛИ, выход которого подключен к шестому выходу гр уппы управляющих выходов блока диагностики, выход Тр, 3 которого подключен к выходу че твертого элемента И к входам которого подключены выходы Тр. 1 и Тр. 2 ПЗУ, шестой разряд второй группы управляющих входов блока диагностики подключен к вторым входам третьего элемента И и второго элемента ИЛИ, управляющий вход ОРЗ блока диагностики подключен к одному из адресных входов ПЗУ, вход считывания которого подключен к входу Сч блока диагностики. Блок ключей содержит N группы ключей и два инвертора, причем одноименные разряды четырех входоввыходов данных блока ключей подключены к входам четырех ключей первой группы, управляющие входы первых ключей подключены к выходу первого инвертора, вход которого подключен к управляющим входам вторых ключей и к входу А/В блока ключей, вход Г/В которого подключен к управляющим входам четвертых ключей и к входу второго инвертора, выход которого подключен к управляющим входам третьих ключей, выходы все х ключей одноименных разрядов соединены между собой. Генератор тактовых импульсов содержит генератор импульсов, счетчик, компаратор ПЗУ, два триггера, три элемента И, инвертор, элемент ИЛИ, причем группа входов кода размерности матрицы подключены к адресным входам ПЗУ, выходы которого подключены к первой группе входов компаратора, вторая группа входов которого подключена к выходам счетчика "+1", которого подключен к выходу ТИ генератора тактовых импульсов и к выходу первого элемента И, первый вход которого подключен к выходу генератора импульсов, к входу считывания ПЗУ и к выходу Сч генератора тактовых импульсов, вход Г которого подключен к одному из адресных входов ПЗУ, а вход Тр. 3 подключен к одному из адресных входов ПЗУ и к входу инвертора, выход которого подключен к первому входу второго элемента И, второй вход которого подключен к первому входу третьего элемента И, к входу R счетчика, к выходу компаратора и к входу S первого триггера, вход R которого подключен к входу S второго триггера и к выходу элемента ИЛИ, первый и второй входы которого подключены к выходам второго и третьего элементов И, второй вход третьего элемента И подключен к прямому выходу первого триггера и к выходу ОРЗ генератора тактовых импульсов, выход ОРЗ которого подключен к инверсному вы ходу первого триггера, вход R второго триггера подключен к входу R генератора тактовых импульсов, выход Гот. которого подключен к прямому выходу второго триггера, инверсный выход которого подключен к второму входу первого элемента И. Заявленная совокупность признаков не известна из аналогов и прототипа, и приводит к расширению функциональных возможностей устройства, поэтому устройство отвечает критерию "существенные отличия". На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 -матрица запоминающих ячеек; на фиг. 3 -схема соединения управляющих выводов ЗЯ; на фиг. 4 - ЗЯ; на фиг. 5 - блок управления матрицей; на фиг. 6 - инвертор (И); на фиг. 7 - блок коммутаторов; на фиг. 8 - блок правления коммутаторами; на фиг. 9 - блок диагностики; на фиг. 10 - схема блока ключей (Кл.); на фиг. 11 - генератор тактовых импульсов. Блок-схема предлагаемого устройства содержит: два инвертора 1, два коммутатора 2, матрицу запоминающих ячеек 3, блок диагностики 4, два блока управления коммутаторами 5, блок управления матрицей 6, генератор тактовых импульсов 7. Матрица запоминающих ячеек содержит запоминающие ячейки 8, группу входных ключей 9, группу выходных ключей 1), группу входов синхронизирующи х импульсов С, вход переключения направления передачи данных А/В (слева направо, справа налево), вход переключения загрузки Г/В (горизонтальная, вертикальная), две группы входов-вы ходов данных Д, управляющие входы транзита Тр1, Тр2, ТрЗ, и вход обнуления матрицы R. Запоминающая ячейка содержит регистр 11, инвертор 12, два элемента И 13 и 14, блок ключей 15, четыре группы входов-выходов данных Д, входы синхронизации С, выходы синхронизации С, вход переключения направления передачи данных А/В, вход обнуления регистра R, вход переключения транзита Тр. Блок управления матрицей содержит: регистр 16, элемент И 17, инвертор 18, две. группы элементов И 19 и 20, вход переключения направления загрузки Г/В, выход переключения направления загрузки Г/В, вход управления сдвигом S, вход изменения выходного кода Р (прямой, обратный), вход включения сдвига Сдв, вход тактовых импульсов ТИ, вход обнуления R, группу выходов син хронизирующи х импульсов С. Инвертор содержит две группы ключей 21 и 22, элемент ИЛИ-НЕ 23, группу входов данных Д, вход управления инвертором УИ, группу вы ходов данных. Блок коммутаторов содержит К групп мультиплексоров-демультиплексоров, где К - разрядность обрабатываемых чисел, гр уппу входов данных Д. группу вы ходов данных Д, гр уппу управляющих входов УК. Блок управления коммутаторами содержит три регистра сдвига 25, счетчик 26, ПЗУ 27, две группы элементов И 28, 29, три элемента И 30, 31, 32, два инвертора 33, 34, элемент И-НЕ 35, элемент ИЛИ 3S, группу управляющих вы ходов УК, группу управляющих входов 1,2,3, вход ТР.З (использование всей матрицы), вход окончания режима загрузки ОРЗ, вход тактовых импульсов ТИ, вход считывания Сч, вход кода размерности матрицы N, вход обнуления R. Блок диагностики содержит ПЗУ 37, четыре элемента И 38, 39, 40, 41, два элемента ИЛИ-НЕ 42, 43, элемент И-НЕ 44, два элемента ИЛИ 45, 46, две группы входов 1р-6р, вход окончания режима загрузки ОРЗ, вход считывания Сч, выходы управления инверторами УИ1 иУИ2, группу управляющих выходов 1-6, выход переключения направления передачи данных А/В, вход переключения направления загрузки Г/В, выход управления сдвигом S, выход изменения кода Р, выход включения сдвига Сдв, вы ход выключения транзита Тр. 1, Тр.2, Тр.З, вы ход управления генератором тактовых импульсов Г. Блок ключей (позиции 9,10,15) содержат N групп ключей 47, два инвертора 48, четыре входа данных Д, управляющий вход переключения направления передачи данных А/В, управляющий вход переключения направления загрузки Г/В. Генератор тактовых импульсов содер-. жит генератор импульсов 49, счетчик 50, компаратор 51, ПЗУ 52, два триггера 53, 54, три элемента И 55, 56,57, инвертор 58, элемент ИЛИ 59, группу входов кода размерности матрицы N, управляющий вход выключения транзита Тр. 3, вход управления генератором тактовых импульсов Г, выход считывания Сч, выход тактовых импульсов ТИ, выход окончания режима загрузки ОРЗ, инверсный выход окончания режима загрузки ОРЗ, выход готовность Гот, вход обнуления R. Устройство работает следующим образом. Предлагаемое устройство позволяет реализовать операцию взаимного преобразования форм информационных потоков в виде матриц из множества возможных (табл. 1). Формы информационных потоков представлены при помощи 2 векторов, 1 - строка вектор матрицы X, определена как расстояние между элементами матрицы хi| и xi+1j, I -соответственно столбец-вектор, определен как расстояние между элементами матрицы xij и xlj+1. Перечеркнутый вектор в табл. 1 соответствует вектору I. Преобразование производится по следующему алгоритму: 1. Входная матрица с помощью входного инвертора и коммутатора преобразуется к соответствующей ей базовой матрицей (каждому двойному столбцу матриц табл. 1 соответствует базовая матрица в первой строке. Все базовые матрицы представлены в таблице 2). 2. Ма трица запоминающих ячеек (МЗЯ) реализует преобразование базовой входной матрицы в базовую выходную, соответствующей вы ходной матрице. 3. Преобразование базовой выходной матрицы (табл. 2) при помощи коммутатора и инвертора в выходную матрицу (табл.1). При наличии сигнала УИ с блока диагностики инверторы производят перестановку строк матрицы таким образом, что первая строка матрицы меняется местом с последней, вторая строка меняется местом с предпоследней и т д. Входной инвертор преобразовывает матрицы, показанные в четных столбцах табл. 1 к виду матриц, показанных в нечетных столбцах таблицы (а одной строке таблицы). Блок коммутаторов позволяет преобразовывать любую матрицу табл. 1 к соответствующей си (по столбцу) матрице, показанной в первой строке этой табл. Таким образом, взаимные преобразования матриц табл. 1 при помощи инвертора и блока коммутаторов можно свести к взаимным преобразованиям матриц таблицы 2 (т.е. к базовым матрицам). Блок управления коммутаторами управляет работой блока коммутаторов. Входные управляющие сигналы БУК предназначены Для 4(1) - подключения выходов счетчика к последовательным (j, k) входам регистров, или входам Р. Изменяет режим работы регистров, переключает с параллельного на последовательный. 6(3) - единица на этом входе разрешает запись начального числа счета с ПЗУ в счетчик и прохождение тактовых импульсов Нуль на этом входе блокирует рэботу БУК. 5(2) - изменяет код числа с ПЗУ устанавливает на счетчике режим счета: +1/-1. R - обнуляет счетчик или записывает параллельный код в зависимости от сигнала 6(3), обнуляет регистры. Тр. 3 - н улем блокирует сигнал ОРЗ, совместно с ним управляет сигналом ТИ. Выходы первого регистра сдвига соединены с первыми управляющими входами всех коммутаторов в блоке коммутаторов, выходы которого соединены со вторыми управляющими входами выходы третьего - с третьими управляющими входами. Такое подключение необходимо для управления работой как всех коммутаторов вместе (параллельно), так и поочередно (последовательно). При параллельном управлении регистры обнуляется и изменение сигналов на выходе регистра производится через вход Р. То есть считывание выходных сигналов производится либо в прямом коде либо в обратном коде. При этом управляющие коды на всех коммутаторах будут одинаковы. Для последовательного управления коммутаторами регистры переводятся в режиме сдвига, и на входы j и К подаются управляющие коды. По каждому тактовому импульсу эти коды будут сдвигаться в регистрах и поочередно переключать коммутаторы. Примером последовательного переключения коммутаторов может служить преобразование матрицы вида (код 011000) в матрицу вида (код 001000). Управляющий сигнал 4= "1", поступающий на БУК 1 подключает входы j и К регистров ь выходам счетчика. Сигнал 5 = "0" устанавливает направление счета счетчика (-1) и выставляет на выходах ПЗУ число (9-N). Управляющий сигнал 6= "1" разрешает прохождение тактовых импульсов 4 и R на чход S счетчика, который производит запись числа (9-N), с которого будет начат отсчет. Это число записывается по входам j и К регистров и попадает на управляющие входы первого мультиплексора. По следующему тактовому импульсу этот код сдвигается на управляющие входы второго коммутатора, а на управляющие входы первого коммутатора поступает код числа на единицу меньше и т.д. Сдвиг управляющих кодов происходит (2N-1) тактов, до полного преобразования матрицы. Матрица запоминающих ячеек (МЗЯ), содержащая N*N запоминающих ячеек, реализует взаимные преобразования матриц (базовых матриц) табл. 2. При этом имеется возможность производить загрузку и выгрузку матриц с 4-х сторон производить задержку части обрабатываемой матрицы и работать в режиме транзита. Управляющие сигналы матрицы ЗЯ: Г/В - определяют направление загрузки: горизонтальная (построчно) или вертикальная (по столбцам). А/В - определяет направление загрузки с входа А на выходы В или наоборот Тр= "0" - отключает регистр ЗЯ, в результате чего ЗЯ -переводится в режим транзита, т.е. сигнал проходит через ЗЯ без задержки. Тр= "1" - производит запоминание сигнала, поступающего на вход ЗЯ. R - обнуляет ЗЯ. Работой МЗЯ управляет блок управления матрицей, позволяющий производить запись (считывание) в МЗЯ построчно или по столбцам, одновременно или со сдвигом на один такт. Управляющие входные сигналы БУМ: Г/В - определяет направление загрузки; S - определяет направление сдвига (от младшего разряда к старшему и наоборот). Р - определяет код считывания информации с регистра (прямой или обратный). Сдв - определяет будет ли производиться сдвиг информации на регистре или нет. R - обнуляет регистр. Управляющие выходные сигналы блока управления подключены к входам С МЗЯ причем от 1 по N выходы подключены к первой строке матрицы; а от (N+1) дo 2N подключены к входам С первого столбца матрицы. Длч отключения МЗЯ регистр обнуляется и с его вы ходов считываются все н ули, запрещающие прохождение ТИ на МЗЯ, для поочередного включения в работу столбцов или строк МЗЯ регистр переводится в режим сдвига по каждому ТИ единица, сдвигаясь на регистре, разрешает прохождение ТИ. Для построчного (или по столбцам) запрещения оаооты МЗЯ информация с обнуленного регистра считывается в обратном коде и сдвигаемые нули запрещают прохождение ТИ. Для некоторых преобразований память МЗЯ можег использоваться только частично. Например, при преобразовании матрицы вида (код 001100) в матрицу вида (001010) В этом случае по сигналу Тр1= "1" включается часть МЗЯ и входная матрица вида проходят через МЗЯ преобразуется в выходную вида. В случаях когда 2, 3, и 4 разряды кодов входной и выходной матриц совп?ідал)т, сигналы Тр1, Тр2 и ТрЗ=0, МЗЯ работает в режиме транзита, т.е. матрица проходит МЗЯ без задержки. Блок диагностики служит для сравнения кодов входной и выходной матриц и для общего управления работой устройства. В ПЗУ записаны коды преобразований матриц, показанных в таблице 2 и время преобразования (сигнал 0' По управляющему входу ОРЗ выходные сигналы А/В, Г/В, S, Р, Сдв, Г изменяются, снимая тем самым загрузочные сигналы и включая сигналы выгрузки. Сигналы Тр1 и Тр2 остаются неизменными. Генератор тактовых импульсов производит общую синхронизацию работы устройства. Кроме этого он вырабатывает сигналы, управляющие режимами загрузки и выгрузки, Запуск ГТИ производиться по сигналу R. На компараторе сравнивается количество сгенерированных ТИ с заданным числом N или (2N-1) и при их совпадении производится обнуление счетчика и установка сигнала ОРЗ (окончание режима загрузки), после чего число с ПЗУ по сигналу Г изменяется и ГТИ вырабатывает серию ТИ для режима выгрузки. После этого выставляется сигнал Гот (готовность устройства к новому преобразованию) и установка в нуль сигнала ОРЗ. Серия ТИ прекращается. Импульсы Сч ГТИ генерирует постоянно. Рассмотрим работу устройства на примере преобразования матрицы вида (код 010110) в матрицу вида (код 101101). На входы ГТИ, БУК1 и БУК2 подаются коды размерности матрицы (например 4). На входы блока диагностики Подаются коды входной 010110 и выходной 101101 матриц. На выходах БД устанавливаются управляющие сигналы У И = "0". Матрица проходит через входной инвертор без изменения и поступает на блок коммутаторов, работой которого управляет БУК1. По сигналу 4= "0" входы Р регистров подключаются к счетчику. По сигналу 5= "0" код числа N-1 устанавливаются на вы ходах ПЗУ. На вход И счетчика поступает "0" устанавливая направление счета (-1). ТРЗ=" 1". По сигналу R производится обнуление регистров и запись в счетчик начального числа счета (N-1). По каждому ТИ счетчик выставляет новый код на регистры, выходы которых подключены к управляющим входам коммутаторов. На коммутаторах производится преобразование матрицы вида в матрицу вида. В это же время производится запись матрицы в запоминающие ячейки. Сигналы Тр1, Тр2 и ТрЗ="1”. Г/В="1” - производит запись построчно. А/В="1" - загрузка в направлении А—В. Р= "0" - с регистра считывается обратный код. По сигналу Р на его выходах устанавливаются все "1". Сдв= "0" - запрещает сдвиг. ТИ поступают одновременно на все строки матрицы ЗЯ. По истечению N тактов режим загрузки завершается, ОРЗ= "1". По сигналу ОРЗ =" Г изменяются сигналы А/В, Г/В, S, Р, Сдв, Г с ПЗУ блока диагностики, этим же сигналом блокируется работа БУК1, а по сигналу ОРЗ- "0" включается в работу БУК2. сигнал Г/В- "1" - построчная выгрузка. Сигнал А/В- "0" - выгр узка в направлении В — А. S- "0" - сдвиг от младшего разряда к старшему. Р-" 1" - информация с регистра считывается в прямом коде (все нули). Сдв.- "1" - будет производиться сдвиг кода на регистре. По каждому ТИ " 1" с последовательного входа регистра сдвигается в сторону от младшего разряда к старшим, разрешая выгрузку информации с матрицы ЗЯ построчно со сдвигом на один такт, таким образом, матрица вида преобразовывается к матрице вида. В это же время включается в работу БК2, управляемый БУК2. Сигнал 1- "0" - входы Р регистров подключены к выходам счетчика. По сигналу 2 -"1" число (9-N) устанавливается на выходах ПЗУ. На вход И сче тчика поступает" 1", устанавливая направление счета (-1). По каждому ТИ к числу (9-N) записанному в счетчик прибавляется единица. На управляющих входах коммутаторов происходит смена кодов, поступающих с вы ходов регистров. Коммутаторы производят преобразование матрицы вида в матрицу вида. На управляющий вход выходного инвертора поступает сигнал УИ-"1", включающий инвертор, который преобразует матрицу вида в матрицу вида. На этом цикл преобразования завершается. Время затраченное на преобразование равняется (3N-1) .тактов.

ДивитисяДодаткова інформація

Автори англійськоюStriamets Serhii Petrovych, Kozhan Volodymyr Petrovych, Derkach Bohdan Teodorovych, Kysil Bohdan Vasyliovych

Автори російськоюСтрямец Сергей Петрович, Кожан Владимир Петрович, Деркач Богдан Теодорович, Кисиль Богдан Васильевич

МПК / Мітки

МПК: G06F 15/16, G06F 17/00

Мітки: інформації, пристрій, перетворення

Код посилання

<a href="https://ua.patents.su/11-20924-pristrijj-dlya-peretvorennya-informaci.html" target="_blank" rel="follow" title="База патентів України">Пристрій для перетворення інформації</a>

Попередній патент: Пристрій для спорудження паль

Наступний патент: Електромагнітний клапан

Випадковий патент: Автоматизована система імітаційного моделювання загальновійськового бою