Пристрій для обробки дискретної інформації

Номер патенту: 1664

Опубліковано: 25.10.1994

Автори: Єрзаков Євген Михайлович, Деніщенко Ігор Якович, Головін Віктор Іванович

Формула / Реферат

1. Устройство обработки дискретной информации, содержащее три процессора и N мажоритарных элементов, отличающееся тем, что, с целью повышения надежности связи с абонентом, оно содержит четыре магистральных усилителя, элемент НЕ, блок контроля и блок синхронизации, причем информационные входы-выходы четырех магистральных усилителей подключены соответственно к информационным входам-выходам трех процессоров и устройства, информационные входы первого, второго и третьего магистральных усилителей подключены к выходу четвертого магистрального усилителя, а і-е разряды информационных выходов j-го магистрального усилителя (і = 1 —N, j — разрядность информации, j = 1—3) подключены к j-м входам і-го мажоритарного элемента, выходы N мажоритарных элементов объединены и подключены к информационному входу четвертого магистрального усилителя, группы управляющих выходов трех процессоров подключены соответственно к трем группам входом блока синхронизации, группа выходов которого подключена к группе управляющих выходов устройства, первый выход блока синхронизации подключен к первому управляющему входу четвертого магистрального усилителя, второй управляющий вход которого соединен со вторым выходом блока синхронизации, с выходом элемента НЕ и с первыми управляющими входами первого, второго и третьего магистральных усилителей, вторые управляющие входы которых подключены к выходу элемента НЕ, информационные выходы первого, второго и третьего магистральных усилителей подключены соответственно к первому, второму и третьему входам блока контроля, первый, второй, третий выходы которого подключены соответственно к входам количества сбоев трех процессоров, четвертый выход блока контроля подключен к первому входу блока синхронизации, второй вход которого соединен с входом конца обмена устройства, причем блок контроля содержит группу дешифраторов, три элемента ИЛИ, элемент НЕ, три счетчика и мажоритарный элемент, при этом і-й разряд j-го входа блока контроля подключен к j- му входу i-го дешифратора группы, j-е выходы дешифраторов группы объединены и подключены к входам j-го элемента ИЛИ, выход которого подключен к j-му входу мажоритарного элемента и к счетному входу j-го счетчика, выход которого подключен к j- му выходу блока контроля, выход мажоритарного элемента через элемент НЕ подключен к четвертому выходу блока контроля.

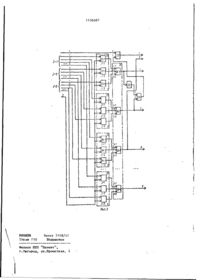

2. Устройство по п.1, отличающееся тем, что блок синхронизации содержит К групп элементов задержек (К — разрядность группы управляющих выходов), группу из К мажоритарных элементов, элемент И-НЕ, элемент ИЛИ-НЕ и формирователь импульса, выход которого соединен с первым входом элемента ИЛИ-НЕ, выход которого соединен с первым входом элемента И-НЕ, второй вход которого подключен к первому входу блока, выход элемента И-НЕ подключен к первому выходу блока, l-и разряд j-й группы входов (l=1—К, j = 1—3) блока подключен к первому входу j-го элемента задержки l-и группы, вторые входы элементов задержки К групп объединены и подключены ко второму входу блока, выход j-го элемента задержки l-и группы подключен к j- му входу l-го мажоритарного элемента группы, выход которого подключен к l- му разряду группы выходов блока, выходы первого и второго мажоритарных элементов группы соединены соответственно со входом формирователя импульса и вторым входом элемента ИЛИ-НЕ.

Текст

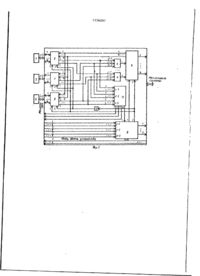

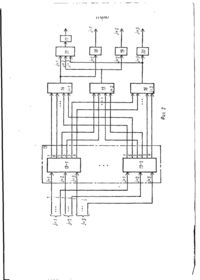

1. УСТРОЙСТВО ОБРАБОТКИ ДИСКРЕТНОЙ ИНФОРМАЦИИ, содержащее.три процессора и N мажоритарных элементов, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности связи с абонентом, оно содержит четыре магистральных усилителя, элемент НЕ, блок контроля и блок синхронизации, причем информационные входы - выходы четырех магистральных усилителей подключены соответственно к информационным входам-выходам трех процессоров и устройства,информационные входы первого, второго и третьего магистральных, усилителей подключены к выходу четвертого магистрального усилителя, а і -є разряды информационных выходов (-го магистрального усилителя (i=1-W, j - разрядность информации, j=l~3) подключены к / -м входам 1 -го мажоритарного элемента, выходы N мажоритарных элементов объединены и подключены к информационному входу четвертого магистрального усилителя, группы управляющих выходов трех процессоров подключены соответственно к трем группам входом блока синхронизации, группа выходов которого подключена к группе управляющих выходов устройства, первый выход блока синхронизации подключен к первому управляющему входу четвертого магистрального усилителя, второй управляющий вход которого соединен с вторым выходом блока синхронизации, с выходом элемента НЕ и с первыми управляющими входами первого, второго и третьего магистральных усилителей, вторые управляющие входы кото- ' рых подключены к выходу элемента НЕ, информационные выходы первого, второго и третьего магистральных усилителей подключены соответственно к первому, второму и третьему входам блока контроля, первый, второй, третий выходы которого подключены соответственно к входам количества сбоев трех процессоров, четвертый выход блока контроля подключен к первому входу блока синхронизации, второй вход которого соединен с входом конца обмена устройства, причем блок контроля содержит группу дешифраторов, три элемента ИЛИ, элемент НЕ, три счетчика и мажоритарный элемент, при этом і -и разряд j -го входа блока контроля подключен к j-му входу \ -го дешифратора группы, j-e выходы дешифраторов группы объединены и подключены к входам J-го элемента ИЛИ, выход которого подключен к j-му входу мажоритарного элемента и к счетному входу j-^ro счетчика, выход которого подключен K J - м у выходу блока контроля, выход мажоритарного" элемента через элемент НЕ подключен к четвертому вы* ходу блока контроля. Зі з зо ч 11 56087 входов (ft=1-K, j=1-3) блока подклю2. Устройство по п. 1 , о т л и чен к первому входу j-го элемента зач а ю щ е е с я тем, что блок синхдержки І- й группы, вторые входы элеронизации содержит К групп элементов ментов задержки К групп объединены задержек (К - разрядность группы и подключены к второму входу блока, управляющих выходов), группу из К выход j-ro элемента задержки t-й мажоритарных элементов, элемент И-НЕ» группы подключен к j-му входу а-го элемент ИЛИ-НЕ и формирователь иммажоритарного элемента группы, выход пульса, выход которого соединен с которого подключен к £ -му разряду первым входом элемента ИЛИ-НЕ, выход группы выходов блока, выходы первокоторого соединен с первым входом го и второго мажоритарных элементов элемента И-НЕ, второй вход которого группы соединены соответственно с подключен к первому входу блока, вывходом формирователя импульса и BTO-J ход элемента И-НЕ подключен к первому рым входом элемента ИЛИ-НЕ. выходу блока, I -й разряд j-й группы 1 Изобретение относится к вычислительной технике и может быть использовано в качестве главного центрального процессора многомашинных комплексов. 5 Цель изобретения - повышение надежности связи с внешними устройствами. На фиг. 1 приведена функциональная схема устройства обработки диск- 10 ретной информации; на фиг. 2 - функциональная схема блока контроля (БК); на фиг. 3 - функциональная схема блока синхронизации (БС). Устройство (фиг. 1) содержит про- 15 цессоры 1-3, мажоритарные элементы к, блок 5 синхронизации, магистральные усилители 6-9, элемент НЕ 10, блок 11 контроля, вход 12 устройства. Блок I1 контроля (фиг. 2) содер- 20 жит группу дешифраторов 13 элементы ИЛИ 14-16, элемент НЕ 17, счетчик 18-20, мажоритарный элемент 21. Блок 5 синхронизации (фиг. 3) содержит К групп элементов задержки 22,25 элемент И-НЕ 23, элемент ИЛИ-НЕ 24. формирователь 25 импульса, группу из К мажоритарных элементов 26. Устройство работает следующим образом. 30 В исходном состоянии первый, второй и третий магистральные усилители 6-8 находятся в режиме "Ввод", а четвертый 9 - в закрытом состоянии. На первые управляющие входы посту пает сигнал лог. " 0 " с выхода элемента НЕ 10. По информационным шинам каждого j-го процессора (j=1-3) передаются информационные сигналы адреса, которые поступают на входывыходы первого, второго, третьего усилителя 6-8. С их выходом информационные сигналы адреса поступают на j-е (j=1-3) входы и на і-е (ї=1-л/) входы каждой j —її группы (j = 1-3) , блока 11. С {-х выходов (Ї=1-Ю информационные сигналы адреса поступают на информационные входы четвертого усилителя 9. При равенстве не менее двух групп информационных сигналов адреса на четвертом выходе блока 11 формируется сигнал лог. " 1 " который поступает на второй вход элемента И-НЕ 23, который является первым входом блока 12. Синхронизация передачи адреса осуществляется первыми управляющими сигналами, поступающими по первым выходным управляющим шинам каждого процессора (1-3). При поступлении не менее двух управляющих сигналов на вход элемента 26-1 на его выходе формируется сигнал лог. " 0 " , по переднему фронту которого формирователь 25 передает сигнал лог. " 0 м , поступающий на первый вход элемента ИЛИ-НЕ 24. На выходе элемента ИЛИ-НЕ 24 формируется сигнал лог. " 1 " и поступает на первый вход элемента И-НЕ 23. 1156087 4 На соответствующие t—о нходы Если на втором входе элемента И-НЕ 23 И1 И (j=1-3) дешиФраторор 1 } ност^ 1 ТО присутствует сигнал лог J-e группы (j= 1-3) информационных на его выходе формируется сигнал сигналов (по і информационных сигналог. "0", который поступает на пер5 лов (i-1-(V) в каждой группе) . При вый управляющий вход усилителя 9 искажении информации в j -м процессои разрешает передачу информационных ре (j^i) сигналы лог. " 1 " формирусигналов адреса в унифицированную ются на первых и шестых выходах демагистраль системы. По окончании шифраторов 13, которые поступают па передачи адреса усилитель 9 возвра10 входы элемента ИЛИ 14. При искажении щается в исходное состояние. информации в J -м (j-2) процессоре Аналогичным образом осуществлясигналы лог. "і" формируются на втоется передача информационных сигнарых и пятых выходах дешифраторов 13, лов данных, которые синхронизируюткоторые поступают на входы элемента ся вторым управляющим сигналом, пос тупаюшим на вторые выходные управля- 15 ИЛИ 15. При искажении информации в j-м процессоре (]=3) сигналы пог."1" формируются на третьих и четвертых выходах дешифраторов 13, которые поступают на Р Х О Д Ы элементов ИЛИ 16. 20 Каждый случай искажения информации в j-м микропроцессоре (1=1-3) фиксируется соответственно в первом, втоВвод информационных сигналов в ром и третьем двоичных счетчиках 1-е процессоры (i=1-3) синхронизиру18-20. При переполнении двоичных ется третьим управляющим сигналом, счетчиков формируются j-e управляюпоступающим по третьим выходным уп- 25 щие сигналы, по которым соответствуюравляющим шинам каждого \ -го процесщие j-e процессоры (j = 1,2,3) устасора Cj=1-3). При поступлении не менавливаются в режим работы с пульта нее двух третьих управляющих сигналов (т.е. останавливаются). Продолжение на вход элемента 26-3 на его выходе формируется сигнал лог. " 0 м , который і« его работы осуществляется после устпоступает на вход элемента НЕ 10, вте ранения неисправности по команде рой управляющий вход усилителя 9 и оператора. первые управляющие входы усилителей В случае искажения информации в 6-8. Усилитель 9 устанавливается в двух и более процессорах (1-3) с режим "Ввод", а усилители 6-8 - в ревыхода элемента 21 формируется сиг35 жим "Вывод". Информационные сигналы нал лог. "1", который инвертируется элементом НЕ 17 и поступает на вход с выхода усилителя 9 поступают на инэлемента И-НЕ 23, который формирует формационные входы усилителей 6-8 сигнал лог. "і", запрещающий переи далее на входные информационные дачу информации с выхода делителя 9 шины I -х процессоров (j=1-3). в информационные шины унифицированной Блок 1Т работает следующим обрамагистрали. зом. ющие шины каждого j-ro процессора (J-1-3), на входы элементов 26-2. С его выхода сигнал лог. " 0 " поступает на второй вход элемента ИЛИ-НЕ 24. 1156087 1 1 Ґ! J__) І S —> JjLi.b 1м 2 ^ ^ U ) 1 Ы-* * і N • J--7 7 ? Г 1 и І і t , Магистраль системы г 4^t • 2_4 3 ^ 7 Ц f ^ 1 $ S ... J--2 Г / > 2 К 1 ? г . . 2 ••' з І І J ••' С S • * "- ' Д t с і' /rtJrff^ пІЇнена устройства 1 12 S608/ _ 1156087 риг.З ВНИИПИ Тираж 710 Заказ 3148/47 Подписное Филиал ППП "Патент"» г.Ужгород, ул.Проектная, 4

ДивитисяДодаткова інформація

Назва патенту англійськоюDescrete information processing unit

Автори англійськоюDenischenko Ihor Yakovych, Yerzakov Yevhen Mykhailovych, Holovin Viktor Ivanovych

Назва патенту російськоюУстройство для обработки дискретной информации

Автори російськоюДенищенко Игорь Яковлевич, Ерзаков евгений Михайлович, Головин Виктор Иванович

МПК / Мітки

МПК: G06F 15/16

Мітки: обробки, пристрій, інформації, дискретної

Код посилання

<a href="https://ua.patents.su/6-1664-pristrijj-dlya-obrobki-diskretno-informaci.html" target="_blank" rel="follow" title="База патентів України">Пристрій для обробки дискретної інформації</a>

Попередній патент: Ходове колесо підйомно-транспортного засобу

Наступний патент: Валкова жниварка

Випадковий патент: Біогазовий реактор