Підсумовувальний пороговий пристрій

Номер патенту: 55790

Опубліковано: 15.04.2003

Автори: Барський Семен Борисович, Скорюкова Яніна Германівна, Баранов Роман Костянтинович, Мартинюк Тетяна Борисівна

Формула / Реферат

Підсумовувальний пороговий пристрій, що містить n блоків порівняння групи, блок порівняння, блок послідовного підсумовування, причому входи групи пристрою з'єднані з першими входами блоків порівняння групи, другі входи яких з'єднані з виходом блока порівняння, перші виходи підключені до першої групи входів даних блока порівняння і до перших входів відповідних блоків порівняння групи, а другі виходи підключені до відповідних входів групи блока послідовного підсумовування, інформаційний вхід якого з'єднаний з виходом блока порівняння, який відрізняється тим, що він містить блок віднімання, входи скидання, синхронізації, керування і завдання порогу пристрою, причому перший вхід блока віднімання є входом порога пристрою, другий вхід підключений до виходу блока послідовного підсумовування, а вихід є виходом пристрою, входи скидання, синхронізації та керування з'єднані з відповідними входами кожного блока порівняння групи, а другі виходи блоків порівняння групи підключені до групи знакових входів блока порівняння, крім того, блок порівняння містить [n/2] вузлів порівняння першого рівня, де [а] - найближче до а мінімальне ціле число, [n/4] вузлів порівняння другого рівня і т.д., а всього [log2n] рівнів пірамідальної структури, кожний k-й вузол порівняння якої містить два знакових входи і два входи даних і знаковий вихід і вихід даних, причому входи даних k-го вузла порівняння першого рівня підключені до(2k-1)-х і 2k-х входів даних блока порівняння, а знакові входи цього вузла підключені до (2k-l)-x і 2k-x знакових входів блока порівняння, крім того, виходи даних і знакові виходи двох сусідніх вузлів порівняння молодшого рівня підключені до двох входів даних і двох знакових входів вузла порівняння старшого рівня і т.д., останній рівень має один вузол порівняння, який містить тільки один вихід даних, який є виходом блока порівняння, при цьому кожний вузол порівняння складається з 3-х блоків: першого блока ознаки, що формується без урахування знаків операндів, другого блока ознаки, що формується з урахуванням знаків і нульових значень операндів і селектора, причому перший блок ознаки складається з (m-1) однакових схем, кожна з яких містить чотири елементи І, два інвертори і два елементи АБО, крім того, перша схема містить також інвертор, j-ті розряди (j=l,2,...m) двох операндів з виходу і-го блока порівняння групи з'єднані з (2k-l)-M і 2k-м входами даних k-го вузла порівняння і підключені до входів першого елемента І та першого і другого інверторів, виходи яких з'єднані з входами другого елемента І, виходи першого і другого елементів І з'єднані із входами першого елемента АБО, перший вхід третього елемента І з'єднаний із входом першого інвертора, а другий з'єднаний з виходом другого інвертора, вихід кожної схеми є виходом другого елемента АБО, входами якого є виходи третього і четвертого елементів І, перший вхід четвертого елемента І з'єднаний з виходом першого елемента АБО, другий вхід з'єднаний з виходом попередньої схеми, в першій схемі другий вхід четвертого елемента І підключений до виходу третього інвертора, а його третій вхід і вхід третього інвертора з'єднані з першими розрядами операндів Ai, Вi відповідно, вихід другого елемента АБО (m-1)-ої схеми є виходом першого блока ознаки, що формується без урахування знаків операндів, другий блок ознаки, що формується з урахуванням знаків і нульових значень операндів, складається з чотирьох інверторів, чотирьох елементів І та двох елементів АБО, причому знакові входи операндів попарно з'єднані з входами перших елементів І та АБО, знаковий вхід другого операнда з'єднаний з першим входом другого елемента І, другий вхід якого з'єднаний через перший інвертор зі знаковим входом першого операнда, вихід першого елемента І є знаковим виходом вузла порівняння, а виходи другого елемента І та першого елемента АБО з'єднані з входами третього елемента І, перший вхід четвертого елемента І з'єднаний з виходом другого інвертора, вхід якого підключений до виходу першого блока ознаки, а другий вхід четвертого елемента І через третій інвертор з'єднаний з виходом першого елемента АБО, виходи третього і четвертого елементів І з'єднані з входами другого елемента АБО, вихід якого є першим виходом другого блока ознаки, знаковий вихід якого через четвертий інвертор з'єднаний з другим виходом другого блока ознаки, селектор складається з трьох груп елементів І, інвертора та групи елементів АБО, причому входи даних вузла порівняння з'єднані з першими входами відповідних першої і другої груп елементів І, другі входи першої групи елементів І з'єднані з першим виходом другого блока ознаки, а другі входи другої групи елементів І з'єднані з першим виходом другого блока ознаки через інвертор, виходи першої і другої групи елементів І попарно з'єднані з першими і другими входами групи елементів АБО, другий вихід другого блока ознаки з'єднаний з першими входами третьої групи елементів І, другі входи яких з'єднані з відповідними виходами групи елементів АБО, виходи третьої групи елементів І селектора є відповідно т-розрядним виходом вузла порівняння.

Текст

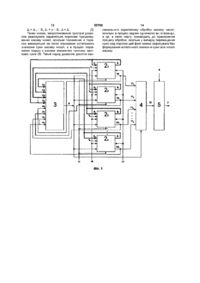

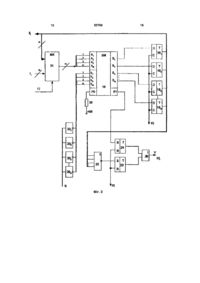

Підсумовувальний пороговий пристрій, що містить п блоків порівняння групи, блок порівняння, блок послідовного підсумовування, причому входи групи пристрою з'єднані з першими входами блоків порівняння групи, другі входи яких з'єднані з виходом блока порівняння, перші виходи підключені до першої групи входів даних блока порівняння і до перших входів ВІДПОВІДНИХ блоків порівняння групи, а другі виходи підключені до ВІДПОВІДНИХ ВХОДІВ групи блока послідовного підсумовування, інформаційний вхід якого з'єднаний з виходом блока порівняння, який відрізняється тим, що він містить блок віднімання, входи скидання, синхронізації, керування і завдання порогу пристрою, причому перший вхід блока віднімання є входом порога пристрою, другий вхід підключений до виходу блока послідовного підсумовування, а вихід є виходом пристрою, входи скидання, синхронізації та керування з'єднані з ВІДПОВІДНИМИ входами кожного блока порівняння групи, а другі виходи блоків порівняння групи підключені до групи знакових входів блока порівняння, крім того, блок порівняння містить [п/2] вузлів порівняння першого рівня, де [а] - найближче до а мінімальне ціле число, [п/4] вузлів порівняння другого рівня і т д , а всього [Іодгп] рівнів пірамідальної структури, кожний к-й вузол порівняння якої містить два знакових входи і два входи даних і знаковий вихід і вихід даних, причому входи даних k-го вузла порівняння першого рівня підключені до(2к-1)-х і 2к-х входів даних блока порівняння, а знакові входи цього вузла підключені до (2k-l)-x і 2к-х знакових входів блока порівняння, крім того, виходи даних і знакові виходи двох сусідніх вузлів порівняння молодшого рівня підключені до двох входів даних і двох знакових входів вузла порівняння старшого рівня і т д , останній рівень має один вузол порівняння, який містить тільки один вихід даних, який є виходом блока порівняння, при цьому кожний вузол порів няння складається з 3-х блоків першого блока ознаки, що формується без урахування знаків операндів, другого блока ознаки, що формується з урахуванням знаків і нульових значень операндів і селектора, причому перший блок ознаки складається з (т-1) однакових схем, кожна з яких МІСТИТЬ чотири елементи І, два інвертори і два елементи АБО, крім того, перша схема містить також інвертор, J-TI розряди 0=1,2, т ) двох операндів з виходу і-го блока порівняння групи з'єднані з (2к-І)-М і 2к-м входами даних к-го вузла порівняння і підключені до входів першого елемента І та першого і другого інверторів, виходи яких з'єднані з входами другого елемента І, виходи першого і другого елементів І з'єднані із входами першого елемента АБО, перший вхід третього елемента І з'єднаний із входом першого інвертора, а другий з'єднаний з виходом другого інвертора, вихід кожної схеми є виходом другого елемента АБО, входами якого є виходи третього і четвертого елементів І, перший вхід четвертого елемента І з'єднаний з виходом першого елемента АБО, другий вхід з'єднаний з виходом попередньої схеми, в першій схемі другий вхід четвертого елемента І підключений до виходу третього інвертора, а його третій вхід і вхід третього інвертора з'єднані з першими розрядами операндів А,, В, ВІДПОВІДНО, вихід другого елемента АБО (т-1)-оі схеми є виходом першого блока ознаки, що формується без урахування знаків операндів, другий блок ознаки, що формується з урахуванням знаків і нульових значень операндів, складається з чотирьох інверторів, чотирьох елементів І та двох елементів АБО, причому знакові входи операндів попарно з'єднані з входами перших елементів І та АБО, знаковий вхід другого операнда з'єднаний з першим входом другого елемента І, другий вхід якого з'єднаний через перший інвертор зі знаковим входом першого операнда, вихід першого елемента І є знаковим виходом вузла порівняння, а виходи другого елемента І та першого елемента АБО з'єднані з входами третього елемента І, перший вхід четвертого елемента І з'єднаний з виходом другого інвертора, вхід якого підключений до виходу першого блока ознаки, а другий вхід четвертого елемента І через третій інвертор з'єднаний з виходом першого елемента АБО, виходи третього і четвертого елементів І з'єднані з входами другого елемента АБО, вихід якого є першим виходом дру О ю ю 55790 гого блока ознаки, знаковий вихід якого через четвертий інвертор з'єднаний з другим виходом другого блока ознаки, селектор складається з трьох груп елементів І, інвертора та групи елементів АБО, причому входи даних вузла порівняння з'єднані з першими входами ВІДПОВІДНИХ першої і другої груп елементів І, другі входи першої групи елементів І з'єднані з першим виходом другого блока ознаки, а другі входи другої групи елементів І з'єд нані з першим виходом другого блока ознаки через інвертор, виходи першої і другої групи елементів І попарно з'єднані з першими і другими входами групи елементів АБО, другий вихід другого блока ознаки з'єднаний з першими входами третьої групи елементів І, другі входи яких з'єднані з ВІДПОВІДНИМИ виходами групи елементів АБО, виходи третьої групи елементів І селектора є ВІДПОВІДНО Трозрядним виходом вузла порівняння Винахід відноситься до обчислювальної техніки та може бути використаний в обчислювальних пристроях для порогової обробки масиву чисел Відомий підсумовуючий пристрій (ас СССР № 1396139, кл G06F7/50, 1986), який містить постійний запам'ятовуючий блок, першу та другу групи елементів І, групу елементів затримки, перетворювач двійкового коду в ущільнений код, групу елементів НІ, причому перші входи елементів І першої групи підключені до входу синхронізації пристрою, входи першої групи перетворювача двійкового коду в ущільнений код з'єднані з виходами ВІДПОВІДНИХ елементів затримки групи, виходи перетворювача двійкового коду в ущільнений код із п-го по другий (де n=2m-l, m - КІЛЬКІСТЬ операндів) з'єднані з першими входами ВІДПОВІДНИХ елементів І другої групи з (п-І)-го по перший, причому інформаційні входи пристрою з'єднані з другими входами ВІДПОВІДНИХ елементів І першої групи, входи елементів НІ групи з'єднані з ВІДПОВІДНИМИ виходами перетворювача двійкового коду в ущільнений код, виходи елементів НІ групи, крім п-го, з'єднаю з другими входамиг ВІДПОВІДНИХ елементів І другої групи, адресні входи постійного запам'ятовуючого блока з'єднані ВІДПОВІДНО З виходами п-го елемента НІ групи, виходами елементів І другої групи та першим виходом перетворювача двійкового коду в ущільнений код, перший розрядний вихід постійного запам'ятовуючого блока з'єднаний з виходом результату пристрою, а ІНШІ розрядні виходи підключені до входів ВІДПОВІДНИЙ елементів затримки групи, виходи елементів І першої групи з'єднані ВІДПОВІДНО З входами другої групи перетворювача двійкового коду в ущільнений код ди яких підключені до адресних входів постійного запам'ятовуючого блока, перший вихід якого з'єднаний з виходом результату десяткового підсумовування пристрою, ІНШІ виходи постійного запам'ятовуючого блока з'єднані з входами розрядів регістра зберігання переносу, вихід якого підключений до першого входу елемента І, другий вхід якого з'єднаний з першою шиною синхронізації пристрою та тактовими входами регістрів зсуву групи та регістра зберіганню переносу, входи, розрядів кожного регістра зсуву групи з'єднані з входами розрядів ВІДПОВІДНОГО операнда пристрою, виходи регістрів зсуву групи з'єднані з першими входами елементів І другої групи, другі входи яких підключені до першої шини синхронізації пристрою, виходи асоціативного запам'ятовуючого блока з'єднані через ВІДПОВІДНІ елементи затримки групи з першими входами елементів І третьої групи, виходи яких підключені до перших входів признаку асоціативного запам'ятовуючого блока, другі входи елементів І першої групи з'єднані з другою шиною синхронізації пристрою, виходи елементів І другої групи з'єднані з другими входами признаку асоціативного запам'ятовуючого блока, вихід елемента підключений до третього входу признаку асоціативного запам'ятовуючого блока, тактовий вхід регістра проміжного результату з'єднаний з першою шиною синхронізації пристрою Недоліком відомого пристрою є вузькі функціональні можливості за рахунок неможливості виконання процесу одночасного підсумовування та порівняння із порогом масиву чисел Відомо асоціативний підсумовуючий пристрій (ас СССР № 1424011, кл G06F7/50, 1986), який містить асоціативний запам'ятовуючий блок, три групи елементів І, елемент І, групу елементів затримки, регістр зберігання переносу, групу регістрів зсуву, регістр проміжного результату та постійний запам'ятовуючий блок, причому вхід молодшого розряду регістра проміжного результату з'єднаний із виходом результату асоціативного запам'ятовуючого блока і з виходом результату двійкового підсумовування пристрою, виходи розрядів регістра проміжного результату з'єднані з першими входами елементів І першої групи, вихо На відомому пристрої неможливе виконання порогової обробки масиву чисел через несумісність використованого способу підсумовування початкових чисел і операції порівняння із порогом Найбільш близьким по технічній суті до пристрою, який пропонується, є пристрій (ас СССР № 1119035, кл G06G7/14, 1984), який містить блоки порівняння групи, блок порівняння, блок послідовного підсумовування, причому входи групи пристрою з'єднані з першими входами блоків порівняння групи, другі входи яких з'єднані з виходом блока порівняння, перші виходи підключені до ВІДПОВІДНИХ входів блока порівняння і до перших входів ВІДПОВІДНИХ блоків порівняння групи, а другі виходи підключені до ВІДПОВІДНИХ входів групи блока послідовного підсумовування, вхід якого з'єднаний з виходом блока порівняння , а вихід підключений до виходу пристрою Відомий пристрій реалізує тільки паралельне додавання групи операнда, представлених тривалостями часових інтервалів, в той час як функціональна надлишковість, що притаманна цьому способу паралельного додавання, дозволяє реалізувати на кожному етапі підсумовування по 55790 рівняння часткових сум із порогом В основу винаходу поставлено задачу створення підсумовуючого порогового пристрою, в якому за рахунок введення нових блоків та зв'язків між ними досягається можливість паралельної порогової обробки вхідної інформації Поставлена задача вирішується тим, що в підсумовуючому пристрої, який містить п блоків порівняння групи, блок порівняння, блок послідовного підсумовування, причому входи групи пристрою з'єднані з першими входами блоків порівняння групи, другі входи яких з'єднані з виходом блока порівняння, перші виходи підключені до групи входів даних блока порівняння і до перших входів ВІДПОВІДНИХ блоків порівняння групи, а другі виходи підключені до ВІДПОВІДНИХ входів групи блока послідовного підсумовування, інформаційний вхід якого з'єднаний з виходом блока порівняння, додатково введено блок віднімання, входи скидання, синхронізації, керування і завдання порогу пристрою, причому перший вхід блока віднімання є входом порога пристрою, другий вхід підключений до виходу блока послідовного підсумовування, а вихід є виходом пристрою, входи скидання, синхронізації та керування з'єднані з ВІДПОВІДНИМИ входами кожного блока порівняння групи, а другі виходи блоків порівняння групи підключені до групи знакових входів блока порівняння, крім того, блок порівняння містить [n/2j вузлів порівняння першого рівня, де [а] — найближче до а мінімальне ціле число, [п/4] вузлів порівняння другого рівня і т д , а всього [Іодгп] рівнів пірамідальної структури, кожний k-й вузол порівняння якої містить два знакових входи і два входи даних і знаковий вихід і вихід даних, причому входи даних k-го вузла порівняння першого рівня підключені до (2к-1)-х і 2к-х входів даних блока порівняння, а знакові входи цього вузла підключені до (2к-1)-х і 2к-х знакових входів блока порівняння, крім того, виходи даних і знакові виходи двох сусідніх вузлів порівняння молодшого рівня підключені до двох входів даних і двох знаковим входів вузла порівняння старшого рівня і т д , останній рівень має один вузол порівняння, який містить тільки один вихід даних, який є виходом блока порівняння, при цьому кожний вузол порівняння складається з 3-х блоків першого блока ознаки, що формується без урахування знаків операнда, другого блока ознака, що формується з урахуванням знаків і нульових значень операнда і селектора, причому перший блок ознаки складається з (т-1) однакових схем, кожна з яких МІСТИТЬ чотири елемента І, два інвертора і два елемента АБО, крім того, перша схема містить також інвертор, J-TI розряди Q=1,2, m) двох операндів з виходу і-го блока порівняння групи з'єднані з (2к-1)-м і 2к-м входами даних к-го вузла порівняння і підключені до входів першого елемента І та першого і другого інверторів, виходи яких з'єднані з входами другого елемента І, виходи першого і другого елементів І з'єднані із входами першого елемента АБО, перший вхід третього елемента І з'єднаний із входом першого інвертора, а другий з'єднаний з виходом другого інвертора, вихід кожної схеми є виходом другого елемента АБО, входами якого є виходи третього і четвертого елементів І, перший вхід четвертого елемента І з'єднаний з виходом першого елемента АБО, другий вхід з'єднаний з виходом попередньої схеми, в першій схем другий вхід четвертого елемента І підключений до виходу третього інвертора, а його третій вхід і вхід третього інвертора з'єднані з першими розрядами операндів А,, В, ВІДПОВІДНО, ВИХІД другого елемента АБО (т-1)-оі схеми є виходом першого блока ознаки, що формується без урахування знаків операндів, другий блок ознаки, що формується з урахуванням знаків і нульових значень операндів, складається з чотирьох інверторів, чотирьох елементів І та двох елементів АБО, причому знакові входи операндів попарно з'єднані з входами перших елементів І та АБО, знаковий вхід другого операнда з'єднаний з першим входом другого елемента І, другий вхід якого з'єднаний через перший інвертор зі знаковим входом першого операнда, вихід першого елемента І є знаковим виходом вузла порівняння, а виходи другого елемента І та першого елемента АБО з'єднані з входами третього елемента І, перший вхід четвертого елемента І з'єднаний з виходом другого інвертора, вхід якого підключений до виходу першого блока ознаки, а другий вхід четвертого елемента І через третій інвертор з'єднаний з виходом першого елемента АБО, виходи третього і четвертого елементів І з'єднані з входами другого елемента АБО, вихід якого є першим виходом другого блока ознаки, знаковий вихід якого через четвертий інвертор з'єднаний з другим виходом другого блока ознаки, селектор складається з трьох груп елементів І, інвертора та групи елементів АБО, причому входи даних вузла порівняння з'єднані з першими входами ВІДПОВІДНИХ першої і другої груп елементів І, другі входи першої груди елементів І з'єднані з першим виходом другого блока ознаки, а другі входи другої групи елементів І з'єднані з першим виходом другого блока ознаки через інвертор, виходи першої і другої групи елементів І попарно з'єднані з першими і другими входами групи елементів АБО, другий вихід другого блока ознаки з'єднаний з першими входами третьої групи елементів І, другі входи яких з'єднані з ВІДПОВІДНИМИ виходами групи елементів АБО, виходи третьої групи елементів І селектора є ВІДПОВІДНО т розрядним виходом вузла порівняння На фіг 1 представлена структурна схема підсумовуючого порогового пристрою, на фіг 2 показана функціональна схема блока порівняння групи, на фіг 3 показана функціональна схема блока порівняння, на фіг 4, 5 показані функціональні схеми двох блоків ознак і селектора, на фіг 6 показана функціональна схема блока послідовного підсумовування Пристрій (фиг 1) містить входи 1-і, , 1 П , блоки 2-і, , 2П порівняння, блок 3 порівняння, блок 4 послідовного підсумовування, блок 5 віднімання, вхід 6 порогу, вихід 7 пристрою Перші входи блоків 2-і, , 2П порівняння з'єднані з входами 1-і, , 1 П пристрою і першими виходами 8-і, , 8П блоків 2-і, , 2П порівняння ВІДПОВІДНО, другі входи яких підключені до виходу 9 блока 3 порівняння Виходи 10-І, , 10п блоків 2-і, , 2 П порівняння підключені до групи входів 11-І, , 11 п блока 4 послідовного підсумовування, а вихід 9 блока 3 порівняння з'єднаний із входом блока 4 послідовного підсумову 55790 вання, вихід 12 якого підключений до другого входу блока 5 віднімання, перший вхід якого підключений до входу 6 порога пристрою, а вихід є виходом 7 пристрою Крім того, виходи 8-і, , 8 П блоків 2-і, , 2 П порівняння з'єднані з групою входів 13-і, , 13 П блока 3 порівняння, а виходи 10і, , 10 п — з групою входів 14-І, , 14 П блока 3 порівняння Вхід 15 синхронізації, вхід 16 скидання і керуючий вхід 17 з'єднані з ВІДПОВІДНИМИ входами блоків 2-і, , 2 П порівняння Блок 2і порівняння, де і=1, 2, , п (фіг 2), містить m-розрядний суматор 18, групу із m Dтригерів 19-І, , 1 9 т , групу із m інверторів 20і, 2 0 т , мультиплексор 2 1 , схему АБО-НІ 22, RSтригери 23, 24, елемент АБО 25 причому перший вхід мультиплексора 21 підключений до входу 1і блока 2і, другий вхід з'єднаний із прямими виходами групи D-тригерів 19-І, , 1 9 т , т-розрядний вихід — до першої групи входів суматора 21, друга група входів якого підключена до виходів групи інверторів 20-І, , 2 0 т , входи яких підключені до виходу 9 блока 3 порівняння Вхід перенесення РО суматора 18 підключений через резистор 26 до входу живлення +5В Крім того, С-входи групи Dтригерів 19-І, , 1 9 т з'єднані з входом 15 синхронізації пристрою, а виходи підключені до m входів елемента АБО-НІ 22, вихід якого з'єднаний з Sвходом RS-тригера 23, R-вхід якого підключений до входу 16 скидання пристрою, а прямий вихід підключений до першого входу елемента АБО 25 Крім того, виходи групи D-тригерів 19-І, , 1 9 т являються m-розрядним виходом 8, блока 2і, а адресний вхід мультиплексора 21 підключений до входу керування 17 пристрою Вихід знаку Р1 суматора 18 підключений до S-входу RS-тригера 24, R-вхід якого підключений до входу 16 скидання пристрою, вихід якого підключений до другого входу елемента АБО 25, вихід V якого є виходом 10і блока 2і Блок 3 порівняння (фіг 3) містить [п/2] вузлів 27 порівняння першого рівня, де [а] — найближче до а мінімальне ціле число, [п/4] вузлів 27 порівняння другого рівня і т д , а всього [Іодгп] рівнів пірамідальної структури Кожний k-й вузол 27 порівняння (к=1,2, ) містить чотири входи (два знакових входи і два входи даних) і два виходи (знаковий вихід 28k і вихід даних 29k) Входи даних к-го вузла 27 порівняння першого рівня підключені до входів 13(2кі), 13гк блока 3 порівняння, а знакові ВХОДИ ЦЬОГО ВуЗЛа ПІДКЛЮЧеНІ ДО ВХОДІВ 14(2к1), 14гк блока 3 порівняння Останній рівень має один вузол 27 порівняння, який містить тільки один вихід даних 29-І, який є виходом 9 блока 3 порівняння Вузол 27 порівняння складається з 3-х блоків блока Зі ознаки, що формується без урахування знаків операнда (фіг 4), блока За ознаки, що формується з урахуванням знаків і нульових значень операндів і селектора Зз (фіг 5) Блок Зі ознаки (фіг 4) складається з (т-1) однакових схем ЗО Кожна схема ЗО МІСТИТЬ чотири елемента І 3 1 , 32, 33, 34, два інвертора 35, 36 і два елемента АБО 37, 38 Крім того, перша схема ЗО містить також інвертор 39, а елемент І 33 має три входи Отже, J-TI розряди ()=1,2, т ) двох операндів А,, В, з виходу 8, блока 2і з'єднані з входами 13J(2ki), 13J2k k-ro вузла 27 блока 3 і підключені до 8 входів елемента І 31 та інверторів 35, 36, виходи яких з'єднані з входами елемента І 32 Виходи елементів І 3 1 , 32 з'єднані із входами елемента АБО 37 Перший вхід елемента І 34 з'єднаний із входом інвертора 35, а другий з'єднаний з виходом інвертора 36 Вихід схеми ЗО є виходом елемента АБО 38, входами якого є виходи елементів І 33, 34 Перший вхід елемента І 33 з'єднаний з виходом елемента АБО 37, другий вхід з'єднаний з виходом попередньої схеми ЗО В першій схемі ЗО другий вхід елемента І 33 підключений до виходу інвертора 39, а його третій вхід і вхід інвертора 39 з'єднані з першими розрядами 13 1 (2кі), 1312к операндів А, В, ВІДПОВІДНО Вихід елемента АБО 38 ( т 1)-оі схеми ЗОО є виходом 40 (Mm) блока Зі Блок 32 ознаки (фіг 5) складається з чотирьох інверторів 4 1 , 42, 43, 44, чотирьох елементів І 45,46,47,48 та двох елементів АБО 49, 50 Входи VA, VB блока 32, які є входами 14(2кі), 142к знаків операндів А, В блока 3, попарно з'єднані з входами елементів І 45та АБО 49 Вхід 14k (VB) з'єднаний з першим входом елемента І 46, другий вхід якого з'єднаний через інвертор 41 з входом 14(2кі) (VA) блока 3 Вихід елемента І 45 є виходом 28k (Vc) вузла 27k блока 3, а виходи елементів І 46 та АБО 49 з'єднані з входами елемента І 47 Перший вхід елемента І 48 з'єднаний з виходом інвертора 44, вхід якого підключений до виходу 40 блока 3-і, а другий вхід елемента І 48 через інвертор 42 з'єднаний з виходом елемента АБО 49 Виходи елементів І 47, 48 з'єднані з входами елемента АБО 50, вихід (S) якого є виходом 51 блока Зг Знаковий вихід 28k (Vc) через інвертор 43 з'єднаний з виходом 52 блока Зг Селектор Зз (фіг 5) складається з груп елементів І 53,, 54,, 55,, інвертора 56 та групи елементів АБО 571, ( J - 1 . m ) Входи 13 (2 к ц, 132к операндів А,, В, з'єднані з першими входами ВІДПОВІДНИХ груп елементів І 53,, 54, Другі входи групи елементів І 53, з'єднані з виходом 51 блока Зг, а другі входи групи елементів І 54, з'єднані з виходом 51 блока Зг через інвертор 56 Виходи групи елементів І 53,, 54, попарно з'єднані з першими і другими входами групи елементів АБО 57, Вихід 52 блока Зг з'єднаний з першими входами групи елементів І 55,, другі входи яких з'єднані з ВІДПОВІДНИМИ виходами групи елементів АБО 57, Виходи с, 0 = 1> т ) групи елементів І 55, блока Зз є ВІДПОВІДНО т-розрядним виходом 29k вузла 27k порівняння блока З Блок 4 послідовного підсумовування (фіг 6) МІСТИТЬ входи 11-І, , 11 п і т-розрядний вхід 9, які з'єднані ВІДПОВІДНО з інверсним входом і т прямими входами групи (т+1)-розрядних елементів І 58, (і — 1, т ) В И Х о д и яких з'єднано попарно з входами групи [п/2] суматорів 59 першого рівня, виходи яких з'єднано попарно з входами групи [п/4] суматорів 59 другого рівня і т д Всього блок 4 має [Іодгп] рівнів пірамідальної структури Останній рівень має один суматор 59, вихід якого є виходом 12 блока 4 послідовного підсумовування Пристрій працює наступним чином Розглянемо приклад паралельного підсумовування масиву з п'яти чисел Підсумовуються числа, рівні 1 1 , 3, 5, 8, 15, та порівнюються з порогом, 10 55790 який дорівнює 31 П'ять чисел подаються ВІДПОВІДНО на входи 1-1-15 , утворюючи початковий масив для підсумовування Оскільки В початковому стані на виході 9 блока 3 присутній нульовий сигнал, то в першій дії підсумовування від кожного початкового числа віднімається нуль з блока 3 і на виходах 81-85 блоків 2i-2s отримують різниці, фактично рівні початковим числам 1 1 , 3, 5, 8, 15, які паралельно подаються по п'яти входах ІЗ1-ІЗ5 на блок 3, де відбувається виділення найменшого числа з п'яти початкових чисел, яке дорівнює 3, та подається на вхід блока 4 Разом з тим з других виходів Ю1-Ю5 блоків 1\2б на входи 11-1-11-1 блока 4 подаються сигнали ознак, що дорівнюють одиниці при наявності ненульової додатної інформації на перших виходах 8-і85 ВІДПОВІДНИХ блоків 2-І-25, тобто при наявності ненульової різниці у поточній дії Таким чином, у блоці 4 відбувається утворення п'ятикратного мінімального числа що дорівнює 15, кратність якого визначається КІЛЬКІСТЮ ненульових чисел першого масиву, після чого відбувається порівняння з порогом 31 у блоці 5, і оскільки значення різниці між порогом і першою частковою сумою, що дорівнює 16, більше нуля, то формується нульовий поточний підсумковий сигнал на виході 7 пристрою і дії продовжуються В другій дії в блоках 2-і-2s формуються різниці між початковими числами 1 1 , 3, 5, 8, 15 та мінімальним числом першого масиву, що дорівнює трьом Утворюються різниці 8, 0, 2, 5, 12 другого масиву Найменше ненульове значення числа другого масиву, що дорівнює двом, формуєтеся в блоці 3, а далі подасться до блока 4, де підсумовується в чотирикратному розмірі, тобто формується часткова сума чисел 8, кратність якої визначається КІЛЬКІСТЮ ненульових чисел другого масиву Після ЦЬОГО поточна часткова сума 8 порівнюється з поточним значенням порогу, яке дорівнює 16, і оскільки значення поточного порогу більше значення поточної часткової суми, то формується нульовий поточний підсумковий сигнал на виході 7 пристрою і дії продовжуються В третій дії в блоках 2-і-2s формуються різниці між числами 8, 0, 2, 5, 12 другого масиву та мінімальним числом другого масиву Утворюються різниці 6, -2, 0, 3, 10 третього масиву Мінімальне число третього масиву дорівнює трьом, оскільки від'ємне число не приймає участь в порівнянні Мінімальне число з блока 3 подається до блока 4, де формується поточна часткова сума в трикратному розмірі, що дорівнює 9, кратність якої визначається КІЛЬКІСТЮ ненульових чисел третього масиву, після чого знов відбувається порівняння її з поточним порогом 8, і оскільки значення поточного порогу менше отриманої суми, то підсумовування припиняється і формується одиничний підсумковий сигнал на виході 7 пристрою У разі, якщо поточний поріг перевищує значення остаточної поточної суми чисел початкового масиву, то процес підсумовуванням виконується до моменту отримання мінімального числа, що дорівнює нулю У цьому випадку підсумковий сигнал залишається нульовим Блок 2і віднімання працює таким чином Спочатку RS-тригери 23 і 24 скидаються в нульовий стан, а мультиплексор 21 встановлюється по сигналу на вході керування 17 пристрою для передавання на вихід інформації з т-розрядного входу 1і пристрою Інформація з мультиплексор 21 подається на перший вхід суматора 18, на другий вхід якого подається прошвертована інформація з виходу 9 блока 3 порівняння Крім того, на вхід перенесення РО суматора 18 завжди подається " 1 " таким чином, суматор 18 працює в режимі віднімання В результаті різниця з виходу суматора 18 записується в групу D-тригерів 19-і, , 1 9 т при наявності синхросигналу на їх С-входах В наступних тактах роботи пристрою мультиплексор 21 встановлюється по сигналу на вході керування 17 пристрою на передавання інформації, що поступає з виходів групи D-тригерів 19-І, , 1 9 т Крім того, при наявності в D тригерах 19-і, , 1 9 т нульової інформації на вході елемента АБО-НІ 23 з'являється " 1 " , що поступає на S-вхід RS-тригера 23, який встановлюється в одиничний стан Якщо при відніманні в суматорі 18 отримано від'ємний результат, то на його виході Р1 формується " 1 " , яка подається на S-вхід RS-тригера 24, який встановлюється в одиничний стан При наявності на одному з входів елемента АБО 25 одиниці з RSтригерів 23, 24 на виході V, який є виходом 10і блока 2і з'являється " 1 " , яка вказує на те що інформація від'ємна або нульова Блок 3 порівняння (фіг 3) працює в такий спосіб На його входи 13(2кі), 13гк і 14(2кі), 14гк де к=1,2 попарно подаються числа А, і В, та їхні знаки VA, VB ВІДПОВІДНО В КОЖНІЙ парі чисел визначається мінімальне число за такими правилами 1 Якщо обидва числа додатні і не дорівнюють нулю, то мінімальне є мінімальне за модулем число 2 Якщо обидва числа додатні і не дорівнюють нулю та однакові за модулем, то мінімальне число А 3 Якщо одне число додатне і не дорівнює нулю, а інше число від'ємне, то мінімальне є додатне число 4 Якщо обидва числа ВІД'ЄМНІ І не дорівнюють нулю, то результатом буде нудь 5 Якщо обидва числа ВІД'ЄМНІ І не дорівнюють нулю та однакові за модулем, то результатом буде нуль 6 Якщо одне число додатне і не дорівнює нулю, а інше число дорівнює нулю, то мінімальне є додатне число 7 Якщо одне число від'ємне, а інше число дорівнює нулю, то результат буде нуль 8 Якщо обидва числа дорівнюють нулю, то результат буде нуль Блок 3-і ознаки, що формується без урахування знаківоперандов А, В (фіг 4) визначає такі сигнали на виході 40 А>В А п) , на (т+1)-й інверсний вхід яких подається сигнал ознаки з виходів 10, ВІДПОВІДНИХ блоків 2, порівняння групи Отже, якщо сигнал ознаки з виходу 10, ВІДПОВІДНОГО блоку 2, дорівнює нулю, тобто на виході 8, блока 2, інформація є ненульовою і додатньою, то величина визначеного мінімального числа у початковому масиві чисел проходить через елемент І 58, і подається на вхід ВІДПОВІДНОГО суматора 59 Дані, що надходять на входи суматорів 59 першого рівня, послідовно підсумовуються на всіх [Іодгп] рівнях обробки пірамідальної структури, а результат підсумовування, тобто поточна часткова сума формується на виході 12 блока 4 послідовного підсумовування Процес порогового підсумовування масиву чисел на даному пристрої можна представити таким чином с 0 0 0 A A A VB -0) -0) -0) -0) -0) -0) + (0) + (0) + (0) + (0) + (0) + (0) В В В В А А Vc -0) -0) -0) + (0) + (0) + (0) + (0) + (0) + (0) + (0) + (0) + (0) 1, якщоБ > р, (1) [О.якщоБ < р, де у — підсумковий сигнал на виході 7 пристрою, S - остаточна сума масиву чисел, р - поріг обробки, причому У= де Si - поточна часткова сума, яка формується на 1-му циклі обробки в блоці 4 послідовного підсумовування Тоді важливим є остаточне значення різниці Д виду А = р - S = р - (Si + S2+ +S| + +SL) (2) Або Д = ( ((p-SO-Ss)- - S J (2) Отже вираз (1) з використанням співвідношення (2) набуває такого вигляду У= М, якщоД 0 В результаті можна записати таю співвідношення 55790 13 Ді = Ді 1 - Si, Д і = p - S i , Д = Д| (З) Таким чином, запропонований пристрій дозволяє реалізувати паралельне порогове підсумовування масиву чисел, оскільки порівняння із порогом виконується не після отримання остаточного значення суми масиву чисел, а в процесі порівняння порогу з кожним значенням поточної часткової суми (3) Такий ПІДХІД дозволяє досягти мак ФІГ. 1 14 симального паралелізму обробки масиву чисел, оскільки в процесі задіяні одночасно всі операнди, а це, в свою чергу, призводить до прискорення процесу обробки, оскільки у випадку перевищення суми над порогом цей факт можна зафіксувати без формування остаточного значення суми всіх чисел масиву 15 16 55790 10. 16 Фіг. 2 17 55790 18 27 Фіг. З 19 55790 20 Ь,.13'2к & 33 31 3 із at 37 L 3 6 35 32 3 4 36 1Э1 (2к-1> 13* 2К L — 1 ї L а зо. L М і п 1і Фіг. 4 40 21 55790 22 Vc 45 VA 41 47 46 50 42 48 49 40 Min 44 51 52 53. 97, 53h 13 %*) 55, 53 55, 53L 56 57 57. 55_ ТІ 54. 54 Фіг. 5 23 55790 24 11. 11. 8. 59 & 11. & 12 м •л-Э 5а м ) 11л-2 & Й-: 59 ш г 1 11. п-1 ) 11. •h * 59 я I ' п Фіг. 6 Підписано до друку 05 05 2003 р Тираж 39 прим ТОВ "Міжнародний науковий комітет" вул Артема, 77, м Київ, 04050, Україна (044)236-47-24

ДивитисяДодаткова інформація

Назва патенту англійськоюThreshold summing unit

Автори англійськоюMartyniuk Tetiana Borysivna

Назва патенту російськоюПороговое суммирующее устройство

Автори російськоюМартынюк Татьяна Борисовна

МПК / Мітки

МПК: G06G 7/14

Мітки: підсумовувальний, пристрій, пороговий

Код посилання

<a href="https://ua.patents.su/12-55790-pidsumovuvalnijj-porogovijj-pristrijj.html" target="_blank" rel="follow" title="База патентів України">Підсумовувальний пороговий пристрій</a>

Попередній патент: Глушник шуму випуску

Наступний патент: Пристрій для вимірювання кутової швидкості

Випадковий патент: Дорожньобудівельна машина