Спосіб прямого мікропроцесорного керування тиристорним перетворювачем та пристрій для його здійснення

Номер патенту: 6673

Опубліковано: 29.12.1994

Автори: Кипенський Андрій Володимирович, Сокіл Євген Іванович, Савченко Ігор Анатолійович, Долбня Віктор Тимофійович

Формула / Реферат

(57) 1. Способ прямого микропроцессорного управления тиристорным преобразователем, включающий запись в таймер числа N, отсчет этого числа путем уменьшения его на единицу с приходом каждого тактового импульса, начиная с момента перехода напряжения питающей сети через нуль, иформирование по окончании отсчета числа управляющих импульсов тиристорами, отличающийся тем, что частоту следования тактовых импульсов формируют пропорционально модулю напряжения питающей сети.

2. Способ по п.1, отличающийся тем, что число до записи в таймер преобразуют в соответствии с выражением где Nmax - максимальное значение числа, которое может быть записано в таймер.

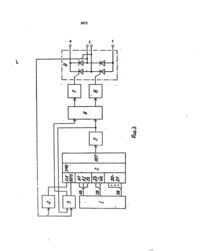

3. Устройство для прямого микропроцессорного управления тиристорным преобразователем, содержащее задатчик сигналов управления, выходами подключенный к соответствующим входам таймера, выход таймера через формирователь импульсов подключен ко входу импульсов управления распределителя импульсов, выходы первого и второго каналов управления которого подключены к соответствующим управляющим входам тиристорного преобразователя, блок связи с сетью, вход окончания счета таймера которого подключен к выходу формирователя импульсов, а вход синхронизации с сетью, определяющий начало отсчета и выбор канала управления, соединен с выводами для подключения питающей сети, выход разрешения счета блока связи с сетью соединен с управляющим входом таймера, а выход выбора канала управления - со входом выбора канала управления распределителя импульсов, отличающееся тем, что введен функциональный преобразователь модуля напряжения в частоту импульсов, включенный между выводами для подключения питающей сети и синхровходом таймера.

4. Устройство по п.3, отличающее-с я тем, что блок связи с сетью выполнен в виде трансформатора, вход которого является входом синхронизации с сетью блока связи с сетью, а выход подключен ко входам компаратора, выход которого является выходом выбора канала управления блока связи с сетью, а также подключен к первым входам первого D-триггера и первого логического элемента И, и через логический инвертор - к первым входам второго D-триггера и второго логического элемента И, прямые выходы первого и второго D-триггеров подключены, соответственно, к первым входам первого и второго логических элементов ИЛИ, вторые входы которых объединены в общую точку и являются входом окончания счета блока связи с сетью, выходы первого и второго логических элементов ИЛИ подключены соответственно, ко вторым входам первого и второго D-триггеров, инверсные выходы которых подключены, соответственно, ко вторым входам первого и второго логических элементов И, выходы логических элементов И подключены ко входам третьего логического элемента ИЛИ, выход которого является выходом разрешения счета блока связи с сетью.

5. Устройство по п.3, отличающееся тем, что распределитель импульсов выполнен в виде логических элементов И и ЗАПРЕТ, причем первый вход логического элемента И и прямой вход логического элемента ЗАПРЕТ объединены в общую точку и являются входом импульса управления распределителя импульсов второй вход логического элемента И и инверсный вход логического элемента ЗАПРЕТ объединены в общую точку и являются входом выбора канала управления распределителя импульсов, выходы логических элементов ЗАПРЕТ и И являются выходами первого и второго каналов управления распределителя импульсов.

Текст

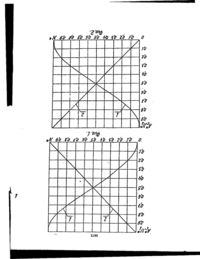

1. Способ прямого микропроцессорного управления тиристорным преобразователем, включающий запись в таймер числа N, отсчет этого числа путем уменьшения его на единицу с приходом каждого тактового импульса, начиная с момента перехода напряжения питающей сети через нуль, и формирование по окончании отсчета числа управляющих импульсов тиристорами, о тл и ч а ю щ и й с я тем, что частоту следования тактовых импульсов формируют пропорционально модулю напряжения питающей сети. 2. Способ по п . 1 , о т л и ч а ю щ и й с я тем, что число до записи в таймер преобразуют в соответствии с выражением где Nmax - максимальное значение числа, которое может быть записано в таймер. 3. Устройство для прямого микропроцессорного управления тиристорным преобразователем, содержащее задатчик сигналов управления, выходами подключенный к соответствующим входам таймера, выход таймера через формирователь импульсов подключен ко входу импульсов управления распределителя импульсов, выходы первого и второго каналов управления которого подключены к соответствующим управляющим входам тиристорного преобразователя, блок связи с сетью, вход окончания счета таймера которого подключен к выходу формирователя импульсов, а вход синхронизации с сетью, определяющий начало отсчета и выбор канала управления, соединен с выводами для подключения питающей сети, выход разрешения счета блока связи с сетью соединен с управляющим входом таймера, а выход выбора канала управления - со входом выбора канала управления распределителя импульсов, о т л и ч а ю щ е е с я тем, что введен функциональный преобразователь модуля напряжения в частоту импульсов, включенный между выводами для подключения питающей сети и синхровходом таймера. 4. Устройство по п.З, о т л и ч а ю щ е е с я тем, что блок связи с сетью выполнен в виде трансформатора, вход которого является входом синхронизации с сетью блока связи с сетью, а выход подключен ко входам компаратора, выход которого является выходом выбора канала управления блока связи с сетью, а также подключен к первым входам первого D-триггера и первого логического элемента И, и через логический инвертор - к первым входам второго D-триггера и второго логического элемента И, прямые выходы первого и второго D-триггеров подключены, соответственно, к первым входам первого и второго логических элементов ИЛИ, вторые входы которых объединены в общую точку и являются входом окончания счета блока связи с сетью, выходы первого и второго логических элементов ИЛИ подключены соответственно, ко вторым входам первого и второго D-триггеров, инверсные выходы которых подключены, со с > ON ON со о 6673 ответственно, ко вторым входам первого и второго логических элементов И, выходы логических элементов И подключены ко входам третьего логического элемента ИЛИ, выход которого является выходом разрешения счета блока связи с сетью. 5. Устройство по п.З, о т л и - ч а ю щ е е с я тем, что распределитель импульсов выполнен в виде логических элементов И и ЗАПРЕТ, причем первый вход логического элемента И и прямой вход логического эле мента ЗАПРЕТ объединены в общую точку и являются входом импульса управления распределителя импульсов второй вход логического элемента И и инверсный вход логического элемента ЗАПРЕТ объединены в общую точку и являются входом выбора канала управления распределителя импульсов, выходы логических элементов ЗАПРЕТ и И являются выходами перрого и второго каналов управления распределителя импульсов. Изобретение относится к электротехниемый таймер числа, соответствующего вреке и может быть использовано для управлеменной задержке заданного угла управления тиристорными преобразователями. ния, непосредственной синхронизации программируемого таймера с напряжением Известен способ прямого микропроцессорного управления тиристорным преобра- 5 питающей сети за счет формирования на его зователем, в соответствии с которым по управляющем входе фронта импульса насигналу, выработанному микроЭВМ, в пропряжения, соответствующего уровню логиграммируемый таймер производится заческой единицы в момент перехода грузка числа, соответствующего временной напряжения питающей сети через нуль, и задержке импульса управления от начала 10 отсчете после этого загруженного в таймер отсчета. По окончании счета, который прочисла путем его уменьшения на единицу с изводится путем уменьшения на единицу приходом каждого импульса от генератора начального содержимого программируемосинхронизации [2] го таймера с приходом каждого импульса от Известное устройство, выбранное в кагенератора синхронизации, таймер форми- 15 честве прототипа, содержит блок связи с рует сигнал управления прерыванием По сетью, первый вход которого предназначен этому сигналу микроЭВМ выдает в буфердля подключения питающей сети, а первый ный регистр сигнал управления, соответствыход подключен к управляющему входу вующий номеру тиристора, который программируемого таймера, синхровход конеобходимо включить в данный момент. В 20 торого подключен к выходу генератора синбуферном регистре производится дешифрахронизации, каналы данных, адреса и ция сигнала управления и формируется упуправления программируемого таймера равляющий импульс, который поступает на предназначены для подключения, соответуправляющий электрод соответствующего ственнро, к шинам данных, адреса и управтиристора [1, стр 176, рис.7.2,а]. 25 ления микроЭВМ, выход программируемого таймера через формирователь импульсов Недостатком известного способа пряподключен к первому входу распределителя мого микропроцесорного управления явимпульсов и ко второму входу блока связи с ляется то, что для синхронизации работы сетью ко второму входу распределителя имтаймеров с напряжением питающей сети кроме переферийных блоков синхрониза- 30 пульсов подключен второй выход блока свяции необходимы затраты программных и зи с сетью, выходы распределителя аппаратных ресурсов самой микроЭВМ. импульсов через выходные усилители подИспользование микроЭВМ для синхрониключены к управляющим входам тиристорзации с напряжением питающей сети ограного преобразователя [2]. ничивает ее возможности при 35 При реализации известным устройством регулировании, что в конечном итоге приизвестного способа регулировочная характеводит к ухудшению работы тиристорного ристика тиристорного преобразователя окапреобразователя. зывается нелинейной, что затрудняет Наиболее близким по технической сущиспользование такого устройства в замкнутых ности к предлагаемому является способ, ре- 40 системах авторегулирования. ализуемый цифровым устройством для Целью изобретения является улучшение управления вентильным преобразователем, регулировочной характеристики тиристорзаключающийся в загрузке в программируного преобразователя путем ее линеариза 6673 ции системой прямого микропроцессорного управления. Указанная цель достигается тем, что в способе прямого микропроцессорного управления тиристорным преобразователем, 5 включающим запись в таймер числа, отсчет этого числа путем уменьшения его на единицу с приходом каждого тактового импульса, начиная с момента перехода напряжения питающей сети через нуль, и формирование, 10 по окончании отсчета числа, управляющих импульсов тиристорами, согласно изобретению, частоту следования тактовых импульсов формируют пропорциональной модулю напряжения питающей сети. 15 Для получения возрастающей регулировочной характеристики тиристорного преобразователя способ по п.2 формулы характеризуется тем, что число до записи в таймер преобразуют в соответствии с выра- 20 жением F(N)-Nmax-N, где Nmax - максимальное значение числа, 25 которое может быть записано в таймер. Поставленная цель достигается также тем, что в устройство для прямого микропроцессорного управления, тиристорным преобразователем, содержащее задатчик 30 сигналов управления, выходами подключенный к соответствующим входам таймера, выход таймера через формирователь импульсов подключен ко входу импульсов управления формирователя импульсов, вы- 35 ходы первого и второго каналов управления которого подключены к соответствующим управляющим входам тиристорного преобразователя, блок связи с сетью, вход окончания счета таймера которого подключен к 40 выходу формирователя импульсов, а вход синхронизации с сетью, определяющий начало отсчета и выбор канала управления, соединен с выходом для подключения питающей сети, выход разрешения счета блока 45 связи с сетью соединен с управляющим входом таймера, а выход выбора канала управления - со входом выбора канала управления распределителя импульсов, согласно изобретению, введен функциональ- 50 ный преобразователь модуля напряжения в частоту, включенный между выводами для подключения к питающей сети и синхровходом таймера. Устройство характеризуется также тем, 55 что* блок связи с сетью выполнен в виде трансформатора, вход которого является входом синхронизации с сетью блока связи с сетью, а выход подключен ко входам компаратора, выход которого является выходом выбора канала управления блока связи с сетью, а также подключен к первым входам первого D-триггера и первого логического элемента И, и через логический инвертор к первым входам второго D-триггера и второго логического элемента И, прямые выходы первого и второго D-триггеров подключены, соответственно, к первым входам первого и второго логических элементов ИЛИ, вторые ^входы которых объединены в общую точку и являются входом окончания счета блока связи с сетью, выходы первого и второго логических элементов ИЛИ подключены, соответственно, ко вторым входам первого и второго D-трмггеров, инверсные входы которых подключены, соответственно, ко вторым входам первого и второго логических элементов И, выходы логических элементов И подключены ко входам третьего логического элемента ИЛИ, выход которого является выходом разрешения счета блока связи с сетью. Устройство характеризуется тем, что распределитель импульсов устройства управления тиристорным преобразователем выполнен в виде логических элементов И и ЗАПРЕТ, причем первый вход логического элемента И и прямой вход логического элемента ЗАПРЕТ объединены в общую точку и являются входом импульса управления распределителя импульсов, второй вход логического элемента И и инверсный вход логического элемента ЗАПРЕТ объединены в общую точку и ЙВЛЯЮТСЯ входом выбора канала управления распределителя импульсов, выходы логических элементов ЗАПРЕТ и И являются выходами первого и второго канала управления распределителя импульсов. Осуществление заявляемого способа прямого микропроцессорного управления тиристорным преобразователем поясняется с помощью устройства, приведенного на чертежах. На фиг. 1 и 2 приведены фазовые (1) и регулировочные (2) характеристики устройства. На фиг.З приведена функциональная схема устройства. На фиг.4, 5 и 6 приведены примеры реализации функционального преобразователя, блока связи с сетью и распределителя импульсов соответственно. На фиг.7 приведены временные диаграммы напряжений на элементах устройства. На фиг.8 приведена блок-схема алгоритма организации ввода управляющего слова (УС) и начального содержимого таймера. На фиг.9 приведена блок-схема специального алгоритма организации ввода УС и начального содержимого таймера, обеспечивающего возрастную регулировочную характеристику. 6673 8 Система для прямого микропроцессоррого подключен к С-входу D-триггера 19, ного управления тиристорным преобразовавторые входы логических элементов ИЛИ 18 телем (фиг.З) содержит задатчик сигналов и 21 объединены в общую точку, и образуют управления 1, программируемый таймер 2, вход окончания счета таймера блока 3 связи имеющий с задатчиком 1 общую шинную 5 с сетью, выходы логических элементов И 17, организацию за счет^шины адреса АВ, подИ 20 подключены ко входам логического элеключаемой к АО, А1, CS входам, шины управмента ИЛИ 22, выход которого является выления СВ, подключаемой к RD, WR входам и ходом разрешения счета таймера блока 3 шины данных DB, подключаемой к DO - D7 связи с сетью. Распределитель 6 импульсов входам, управляющий GATE вход таймера 2 10 (фиг.6) выполнен в виде двух логических элеподключен к выходу разрешения счета тайментов И 23 и ЗАПРЕТ 24, первый вход ломера блока 3 связи с сетью, вход CLK синхгического элемента И 23 и прямой вход ронизации таймера 2 подключен к выходу логического элемента ЗАПРЕТ 24 объединефункционального преобразователя 4, выход ны в общую точку и образуют вход импульса OUT таймера 2 через формирователь 5 им- 15 управления распределителя 6 импульсов, пульсов подключен ко входу импульса упвторой вход логического элемента И 23 объравления распределителя 6 импульсов и ко единен в общую точку с инверсным входом входу окончания счета таймера блока 3 свялогического элемента ЗАПРЕТ 24, и они обзи с сетью, вход синхронизации с сетью которазуют вход выбора сигнала управления рого и вход функционального преобразователя 20 распределителя 6 импульсов, выходы логи4 подключены к выводам для подключения пических элементов ЗАПРЕТ 24 и И 23 являюттающей сети, выход выбора канала управления ся выходами первого и второго каналов блока 3 связи с сетью подключен ко входу управления распределителя 6 импульсов. выбора канала управления распределителя 6 Способ прямого микропроцессорного импульсов, выходы первого и второго каналов 25 управления тиристорным преобразоватеуправления распределителя 6 импульсов челем заключается в том, что реализацию расрез выходные усилители 7 и 8 подключены к четного времени запаздывания импульса соответствующим управляющим электроуправления тиристором относительно модам тиристорного преобразователя 9. Фунмента перехода напряжений питающей сети кциональный преобразователь 4 (фиг.4) 30 через нуль осуществляют при помощи провыполнен в виде согласующего трансформаграммируемого таймера, отсчетом заранее тора 10, вход которого является входом фунзаписанного в него числа N. Отсчет числа N кционального преобразователя 4, выход производится путем уменьшения его на едисогласующего трансформатора 10 через выницу с поступлением на синхровход таймеделитель 11 модуля подключен ко входу пре35 ра каждого тактового импульса, причем образователя 12 напряжение - частота, частоту следования тактовых импульсов выход которого является выходом функциоформируют пропорционально модулю нанального преобразователя 4. Блок 3 связи с пряжения питающей сети: сетью (фиг.9) выполнен в виде согласующего трансформатора 13, вход которого является 40 f™(t)=kllm I s l n & t l О) входом синхронизации с сетью блока 3 связи с сетью, выходы согласующего трансфорПри этом линейному приращению числа матора 13 подключены ко входам N будет соответствовать линейное приракомпаратора 14, выход которого является щение среднего значения выпрямленного выходом выбора канала управления блока 3 45 напряжения связи с сетью, кроме того, выход компаратора 14 подключен ко входу инвертора 15, DN ± 1 = Ud ± AU (2) входу D-триггера 16 и к первому входу логического элемента И17, второй вход коЗначение AU определяется параметраторого подключен к инверсному выходу D- 50 ми функционального преобразователя мо' триггера 16, прямой выход D-триггера 16 дуля напряжения питающей сети в частоту и подключен к первому входу логического элеограничивается ч а с т о т н ы ^ свойствами мента ИЛИ 18, выход которого подключен к таймера. Минимальное значение AU может С-входу D-триггера 16, выход инвертора 15 быть определено следующим образом. При подключен к D-входу D-триггера 19 и к пер- 55 синусоидальной форме напряжения питаювому входу логического элемента И 20, ко щей сети максимальное приращение вывторому входу которого подключен инверспрямленного напряжения при уменьшении ный выход D-триггера 19, прямой выход Dчисла Ni на единицу будет в том случае, триггера 19 подключен к первому входу когда угол управления, соответствующий логического элемента ИЛИ 21, выход кото 6673 (N|-1), составит (л:- Тти.гр. Q0/2. Приращение Аи в этом случае определяется выражением 10 ровочную характеристику тиристорного преобразователя -N* - (л:-ТтигрО:)/2 UmslnQ:tdQ;t ^ / U (6) Таким образом, изменяя частоту тактовых импульсов пропорционально модулю напряжения питающей сети, получают ли2Um _:n /Тти.гр О: нейную убывающую регулировочную харакs m ~1C 2 10 теристику тиристорного преобразователя фиг.1 (кривая 2). где Тта.гр - период граничного значения частоты Для получения возрастающей регулиросинхронизации программируемого таймера; вочной характеристики тактовую частоту Ос - угловая частота напряжения питаюпрограммируемого таймера изменяют щей сети; 15 прежним образом, а число N до записи в Um - амплитудное значение напряжения таймер преобразуют по выражению питающей сети. Фазовая характеристика устройства, (7) представляющая собой зависимость угла управления а от числа N, загруженного в тай- 20 Фазовая характеристика в этом случае мер, будет при этом иметь вид: будет иметь вид N а\ (N) - arccos (3) arccos (8) 25 Зависимость (3) приведена на фиг.1 (кривая 1) в относительных единицах или в относительных единицах = ^ arccos ( 2 N * - 1 ) ~arccos(1-2N*), п (4) 30 здесь 35 (9) и приведена на фиг.2 (кривая 1). Среднее значение выпрямленного напряжения тиристорного преобразователя в этом случае определяется выражением Ud2 - N AU, (Ю) а регулировочная характеристика имеет вид а максимальное значение числа N определяется как (11) 40 U2* - N* Udmax _ и приведена на фиг.2 (кривая 2). Согласно заявляемому способу устройство управления работает следующим обрзгде Udmax ~ максимальное значение выпрям- 45 зом. ленного напряжения (де* 0) До начала процесса управления в соответствии с алгоритмом (фиг.8) в память заUdmax датчика сигнала управления 1, а затем в программируемый таймер 2 производится Среднее значение выходного напряжения 50 запись управляющих слов (УС) и числа N. тиристорного полууправляемого выпрямителя, При изменении знака напряжения на выхоработающего на активно-индуктивную нагрузде трансформатора 13 с отрицательного на ку, будет в этом случае определяться выражеположительный и с положительного на отринием цательный (фиг.7,а) сигнал U H на выходе 55 компаратора 14 изменяется от значения логического нуля до значения логической еди(5) ницы и от значения логической единицы до значения логического нуля соответственно Разделив обе части выражения (5) на (фиг.7,6). Сигнал, инверсный сигналу Ui4 Udmax и выразив N через N*. получим регулиформируется на выходе инвертора 15 Nmax 11 6673 (фиг.7,в). Поскольку в исходном состоянии D-триггера 16 сигнал 1Иб инв на его инверсном выходе соответствует уровню логической единицы (фиг.7,г), то его произведение с сигналом U14, соответствующим положи- 5 тельной полуволне напряжения 1Из, также будет соответствовать уровню- логической единицы (фиг.7,к) 12 импульсов управления 1)з по выходным усилителям 7 и 8, где происходит усиление управляющих импульсов (фиг.7,п.р). Кроме того импульсы управления Us через логический элемент ИЛИ 18 поступают на С-вход D-триггера 16, что при совпадении сигналов на его обоих входах приводит к изменению состояния D-триггера 16 и на его инверсном выходе устанавливается напряинв = U14 10 жение, соответствующее уровню логического нуля (фиг.7, г). В результате изменения состояния D-триггера 16 на входе GATE тайСигнал U17 с выхода логического элемера 2 устанавливается сигнал, соответствумента И 17 через логический элемент ИЛИ ющий уровню логического нуля, что 22 поступает на вход GATE таймера 2 (фиг.7, м). По фронту сигнала U22 в таймере 2 начи- 15 является запрещением для работы таймера нается отсчет ранее записанного числа N. в этом такте тиристорного преобразователя Отсчет числа N производится путем его 9 (фиг.7, м). По окончании действия сигнала уменьшения на единицу с приходом каждого U14, соответствующего логической единице, импульса от функционального преобразована D-входе D-триггера 16, последний перетеля 4. Частота следования тактовых им- 20 ходит в свое исходное состояние (фиг.7,г.д). пульсов на выходе преобразователя 4 Второй канал блока 3 связи с сетью, включаизменяется пропорционально модулю нающий D-триггер 19 и логические элементы И пряжения питающей сети 20 и ИЛИ 21, работает аналогичным образом, но со сдвигом на 130 эл.град. (фиг.7, ж, 25 з, и, л). Таким образом изменение частоты на выходе функционального преобразователя где Кю и Кі2 - коэффициент трансформации 4 по закону, определяемому выражением (1), трансформатора 10 и коэффициент пропоробеспечивает линейную регулировочную хациональности преобразователя 12, выбира30 рактеристику тиристорного преобразоватеемые таким образом, чтобы выполнялось ля 9 (фиг.1, кривая 2). Для получения условие возрастающей регулировочной характеристики число N, согласно способу, до записи в таймер преобразуют в соответствии с вы35 ражением (7). Блок-схема алгоритма для реПо истечении времени ализации такой зависимости приведена на фиг.9. Принцип работы аппаратной части сиг = гт arccos И — (N стемы управления при этом не изменяется. Использование предлагаемого способа т.е. за один такт до окончания счета, сигнал 40 прямого микропроцессорного управления и устройства для его реализации позволяет на выходе OUN таймера 2 в течение одного получать линейные регулировочные харакпериода Ї 4 устанавливается соответствуютеристики тиристорного преобразователя, щим уровню логического нуля (фиг.7,н). По что облегчает использование последнего в фронтам импульсов Ifc формирователь 5 импульсов формирует импульсы управления 45 системах авторегулирования, поскольку позволяет оставить без изменения коэффицидлительностью, необходимой для надежноент усиления отрицательной обратной связи го отпирания тиристоров (фиг.7,о). В распрево всем диапазоне изменения угла управледелителе 6 импульсов в соответствии с ния тиристорами. сигналом U14 происходит распределение БЮ 'д'Щ б'О Ч'О Ґ0 6Ь 9'0 So ҐО / \ / і Ґ0 / і і \ / / ч N / < О А 7 \ / / 7' 60 S'O i'D 9O S'O t'O i'O 70 70 \ s'o s'o t'o s'o б'о 1 0. Ґ0 7'0 Я'О Ь'О д'о t'o s'o 7 б'о ЕІ99 їй'/У 6673 'О" I Г V Г £ШО г ZJ ЄІ99 6673 S) п*на "/6 9 t9 *) з 'і t

ДивитисяДодаткова інформація

Назва патенту англійськоюDirect microprocessor control method for thyristor converter and device to realize it

Автори англійськоюKypenskyi Andrii Volodymyrovych, Dolbnia Viktor Tymofiiovych, Sokil Yevhen Ivanovych, Savchenko Ihor Anatoliiovych

Назва патенту російськоюСпособ прямого микропроцессорного управления тиристорным преобразователем и устройство для его осуществления

Автори російськоюКипенский Андрей Владимирович, Долбня Виктор Тимофеевич, Сокол Евгений Иванович, Савченко Игорь Анатольевич

МПК / Мітки

МПК: H02M 7/12

Мітки: пристрій, тиристорним, перетворювачем, прямого, мікропроцесорного, керування, здійснення, спосіб

Код посилання

<a href="https://ua.patents.su/12-6673-sposib-pryamogo-mikroprocesornogo-keruvannya-tiristornim-peretvoryuvachem-ta-pristrijj-dlya-jjogo-zdijjsnennya.html" target="_blank" rel="follow" title="База патентів України">Спосіб прямого мікропроцесорного керування тиристорним перетворювачем та пристрій для його здійснення</a>

Попередній патент: Спосіб одержання композиційних покриттів на основі нікелю

Наступний патент: Ротор електричної машини

Випадковий патент: Пристрій утилізації боєприпасів шляхом підриву з отриманням електричної енергії