Процесор з інтервальним контролем

Номер патенту: 90315

Опубліковано: 26.04.2010

Автори: Конорев Борис Михайлович, Манжос Юрій Семенович, Харченко Вячеслав Сергійович, Чертков Георгій Миколайович

Формула / Реферат

Процесор з інтервальним контролем, що містить блок регістрів загального призначення, блок комунікаційних регістрів, блок тимчасових регістрів, арифметико-логічний пристрій, регістр ознак, додавач адреси, блок черги інструкцій, блок управління виконавчого модуля та блок управління шиною, перший вхід-вихід якого є входом-виходом процесора, другий вхід-вихід з'єднаний першою шиною даних з виходом і першим входом додавача адреси та першим входом-виходом блока комунікаційних регістрів, вихід блока управління шиною з'єднаний з входом блока черги інструкцій, вихід якого з'єднаний з входом блока управління виконавчого модуля, а через другу шину даних - з другим входом-виходом блока комунікаційних регістрів, входами-виходами блоків регістрів загального призначення та тимчасових регістрів, а також з виходом результату арифметико-логічного пристрою та виходом регістра ознак, відповідні виходи першої групи виходів блока управління виконавчого модуля з'єднані з керуючими входами регістра ознак, арифметико-логічного пристрою та блоків управління шиною і черги інструкцій, входами блоків регістрів загального призначення та тимчасових регістрів, а також блока комунікаційних регістрів, вихід якого з'єднаний з другим входом додавача адреси, перший та другий виходи блока тимчасових регістрів з'єднані відповідно з першим та другим інформаційними входами арифметико-логічного пристрою, вихід ознак якого з'єднаний з першим інформаційним входом регістра ознак, який відрізняється тим, що додатково має блок регістрів інтервальних даних, блок регістрів тимчасових інтервальних ознак, додавач-віднімач мінімальної границі, додавач-віднімач максимальної границі, блок множення-ділення, дешифратор команд, регістр мінімальної границі, регістр максимальної границі, мультиплексор границь першого операнда, мультиплексор границь другого операнда, мультиплексор першої мінімальної границі, мультиплексор другої мінімальної границі, мультиплексор першої максимальної границі, мультиплексор другої максимальної границі, перший, другий, третій, четвертий та п'ятий елементи АБО, перший та другий елементи І, перший та другий елементи НІ, причому відповідні виходи першої групи виходів блока управління виконавчого модуля з'єднані з входами блока регістрів тимчасових інтервальних ознак, блока регістрів інтервальних даних, вхід-вихід якого через другу шину даних з'єднаний з входом-виходом блока регістрів тимчасових інтервальних ознак, вихід блока черги інструкцій з'єднаний зі входом дешифратора команд, перший вихід якого з'єднаний з першим входом першого елемента І та першим входом першого елемента АБО, вихід якого з'єднаний зі входом першого елемента НІ, вихід якого з'єднаний з першим входом другого елемента АБО, вихід якого з'єднаний з другим інформаційним входом регістра ознак, а другий вихід дешифратора команд з'єднаний з другим входом першого елемента АБО та першим входом другого елемента І, вихід якого з'єднаний з другим входом другого елемента АБО, третій вхід якого з'єднаний з виходом першого елемента І, крім того перший вихід блока регістрів тимчасових інтервальних ознак з'єднаний з першим інформаційним входом мультиплексора границь першого операнда, а другий вихід блока регістрів тимчасових інтервальних ознак з'єднаний з другим інформаційним входом мультиплексора границь першого операнда, а третій вихід блока регістрів тимчасових інтервальних ознак з'єднаний з першим інформаційним входом мультиплексора границь другого операнда, а четвертий вихід блока регістрів тимчасових інтервальних ознак з'єднаний з другим інформаційним входом мультиплексора границь другого операнда, крім того інформаційні виходи мультиплексорів границь першого та другого операндів з'єднані відповідно з першим та другим інформаційними входами блока множення-ділення, вихід якого з'єднаний з першими інформаційними входами мультиплексорів другої мінімальної та максимальної границь, а також інформаційним входом регістра мінімальної границі та інформаційним входом регістра максимальної границі, вихід якого з'єднаний з першим інформаційним входом мультиплексора першої максимальної границі та другою шиною даних, а інформаційний вихід регістра мінімальної границі з'єднаний з першим інформаційним входом мультиплексора першої мінімальної границі та другою шиною даних, до того ж перший вихід блока регістрів тимчасових інтервальних ознак з'єднаний з другим і третім інформаційними входами мультиплексора першої мінімальної границі, а четвертий вихід блока регістрів тимчасових інтервальних ознак з'єднаний з четвертим і п'ятим інформаційними входами мультиплексора першої мінімальної границі, вихід якого з'єднаний з першим інформаційним входом додавача-віднімача мінімальної границі, інформаційний вихід якого з'єднаний з другою шиною даних, а третій вихід блока регістрів тимчасових інтервальних ознак з'єднаний з другим та третім інформаційними входами мультиплексора другої мінімальної границі, до того ж перший вихід блока регістрів тимчасових інтервальних ознак з'єднаний з четвертим та п'ятим входами мультиплексора другої мінімальної границі, вихід якого з'єднаний з другим інформаційним входом додавача-віднімача мінімальної границі, крім того, четвертий вихід блока регістрів тимчасових інтервальних ознак з'єднаний з другим інформаційним входом мультиплексора першої максимальної границі, а другий вихід блока регістрів тимчасових інтервальних ознак з'єднаний з третім інформаційним входом мультиплексора першої максимальної границі, а третій вихід блока регістрів тимчасових інтервальних ознак з'єднаний з четвертим інформаційним входом мультиплексора першої максимальної границі, до того ж другий вихід блока регістрів тимчасових інтервальних ознак з'єднаний з п'ятим інформаційним входом мультиплексора першої максимальної границі, вихід якого з'єднаний з першим входом додавача-віднімача максимальної границі, а також четвертий вихід блока регістрів тимчасових інтервальних ознак з'єднаний з третім інформаційним входом мультиплексора другої максимальної границі, крім того, другий вихід блока регістрів тимчасових інтервальних ознак з'єднаний з четвертим інформаційним входом мультиплексора другої максимальної границі, а третій вихід блока регістрів тимчасових інтервальних ознак з'єднаний з п'ятим інформаційним входом мультиплексора другої максимальної границі, вихід якого з'єднаний з другим інформаційним входом додавача-віднімача максимальної границі, причому перший ознаковий вихід додавача-віднімача максимальної границі з'єднаний з першим входом третього елемента АБО та з першим входом четвертого елемента АБО, вихід якого з'єднаний з керуючим входом регістра максимальної границі, до того ж другий ознаковий вихід додавача-віднімача максимальної границі з'єднаний з другим входом першого елемента І, крім того перший ознаковий вихід додавача-віднімача мінімальної границі з'єднаний з третім входом першого елемента І, а другий ознаковий вихід додавача-віднімача мінімальної границі з'єднаний з другим входом третього елемента АБО, вихід якого з'єднаний зі входом другого елемента НІ, вихід якого з'єднаний з другим входом другого елемента І, а третій ознаковий вихід додавача-віднімача мінімальної границі з'єднаний з першим входом п'ятого елемента АБО, вихід якого з'єднаний з керуючим входом регістра мінімальної границі, причому відповідні виходи другої групи входів блока управління виконавчого модуля з'єднані з керуючими входами мультиплексорів границь першого та другого операндів, а також мультиплексорів першої та другої мінімальної та максимальної границі, додавачів-віднімачів мінімальної та максимальної границь, блока множення-ділення, а також з другим входом четвертого елемента АБО та з другим входом п'ятого елемента АБО.

Текст

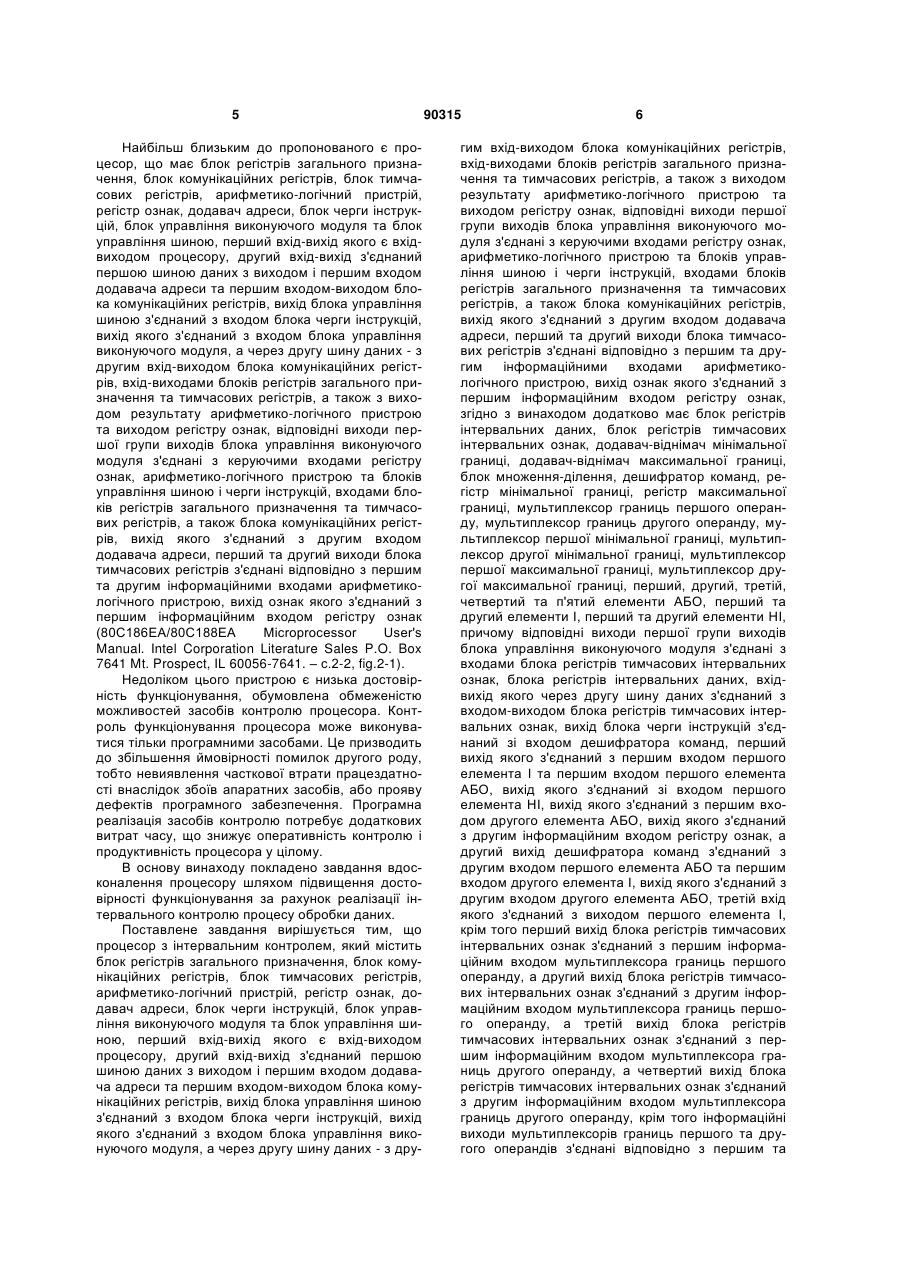

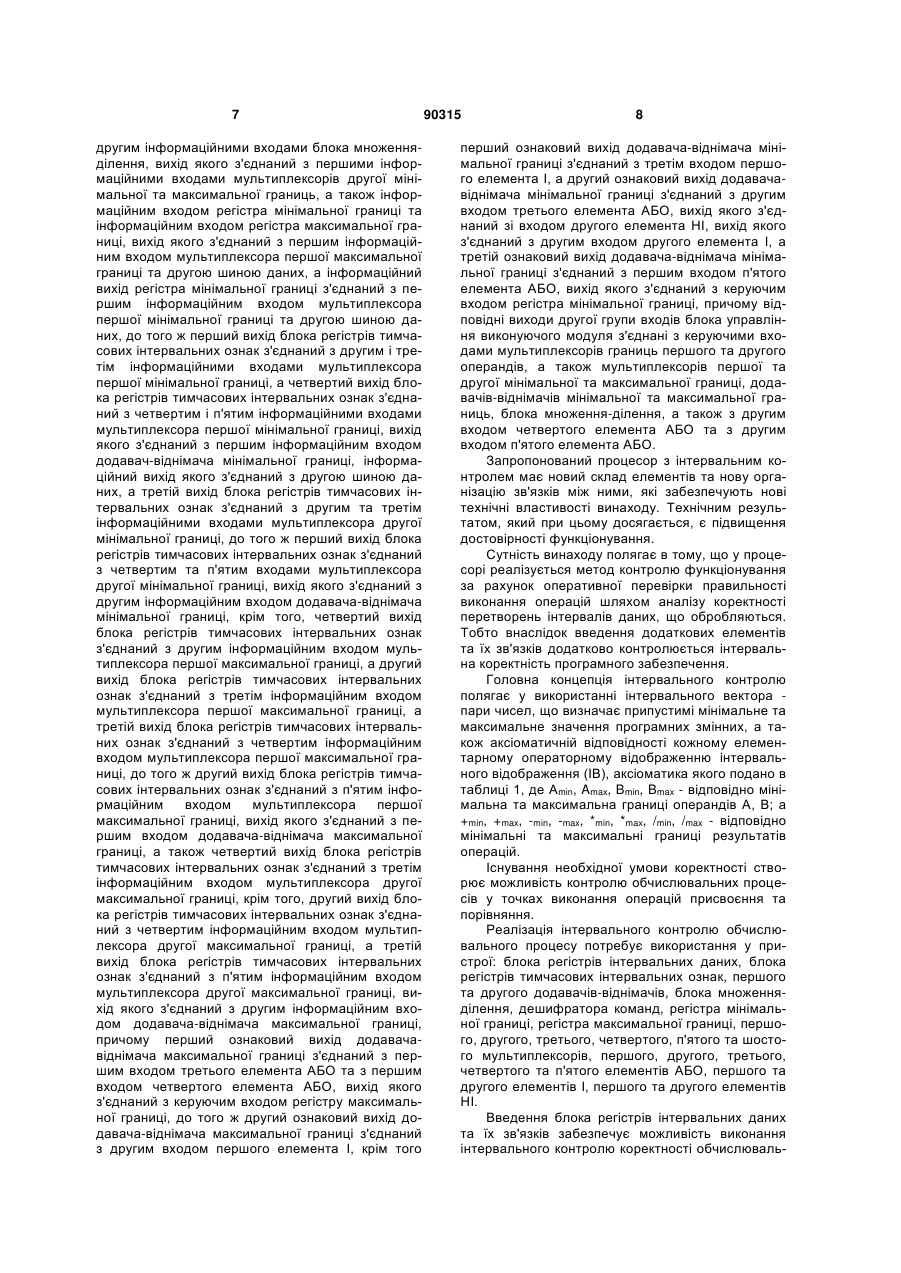

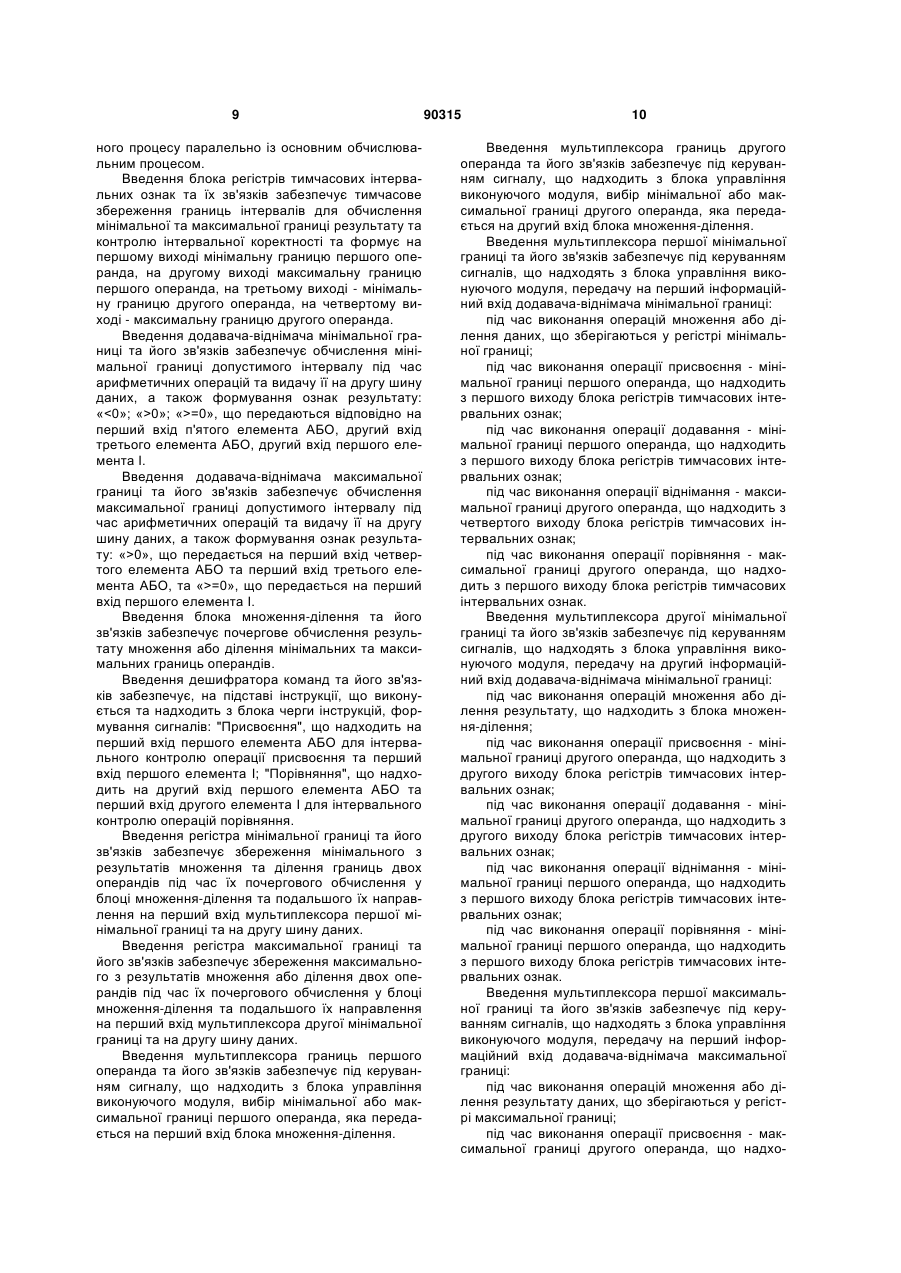

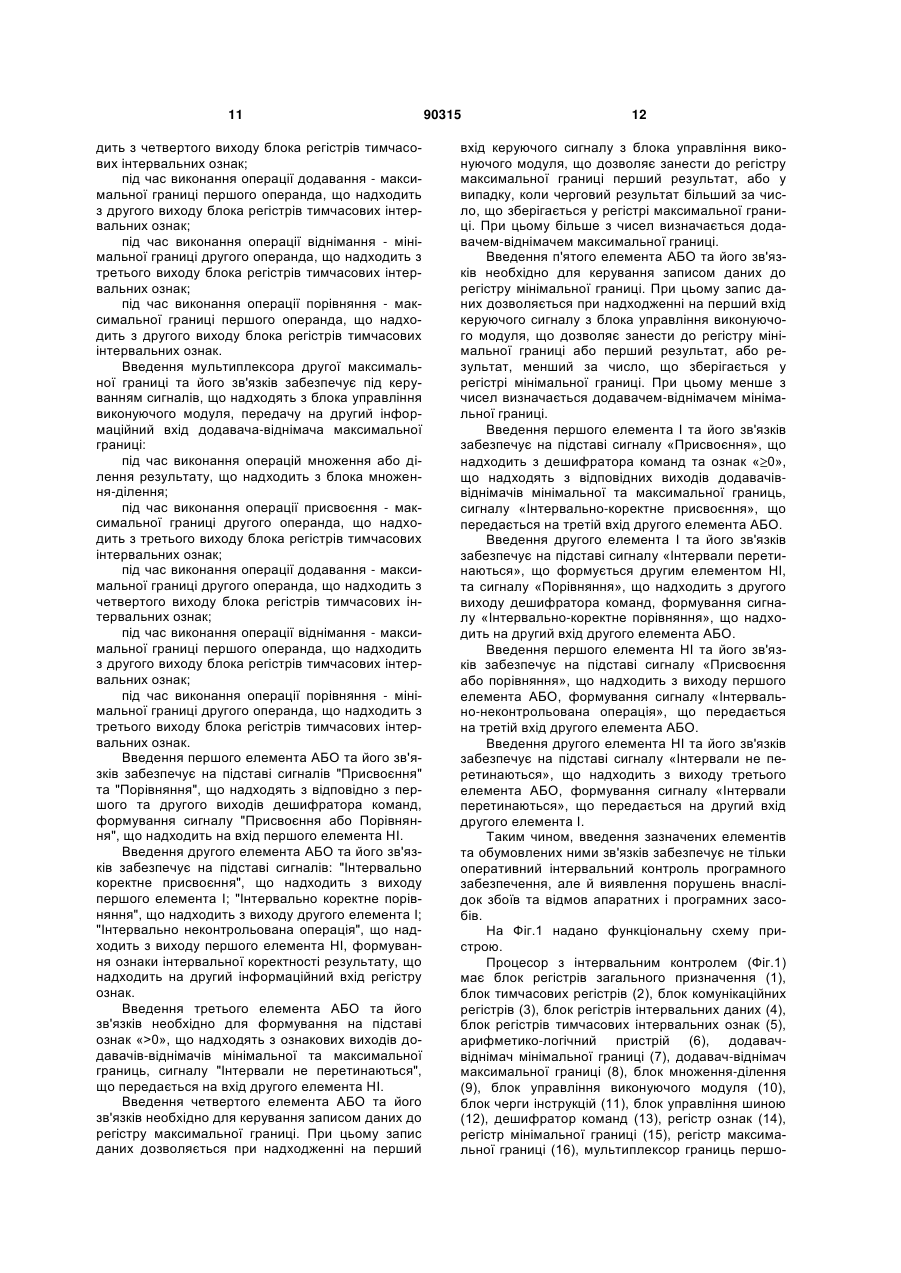

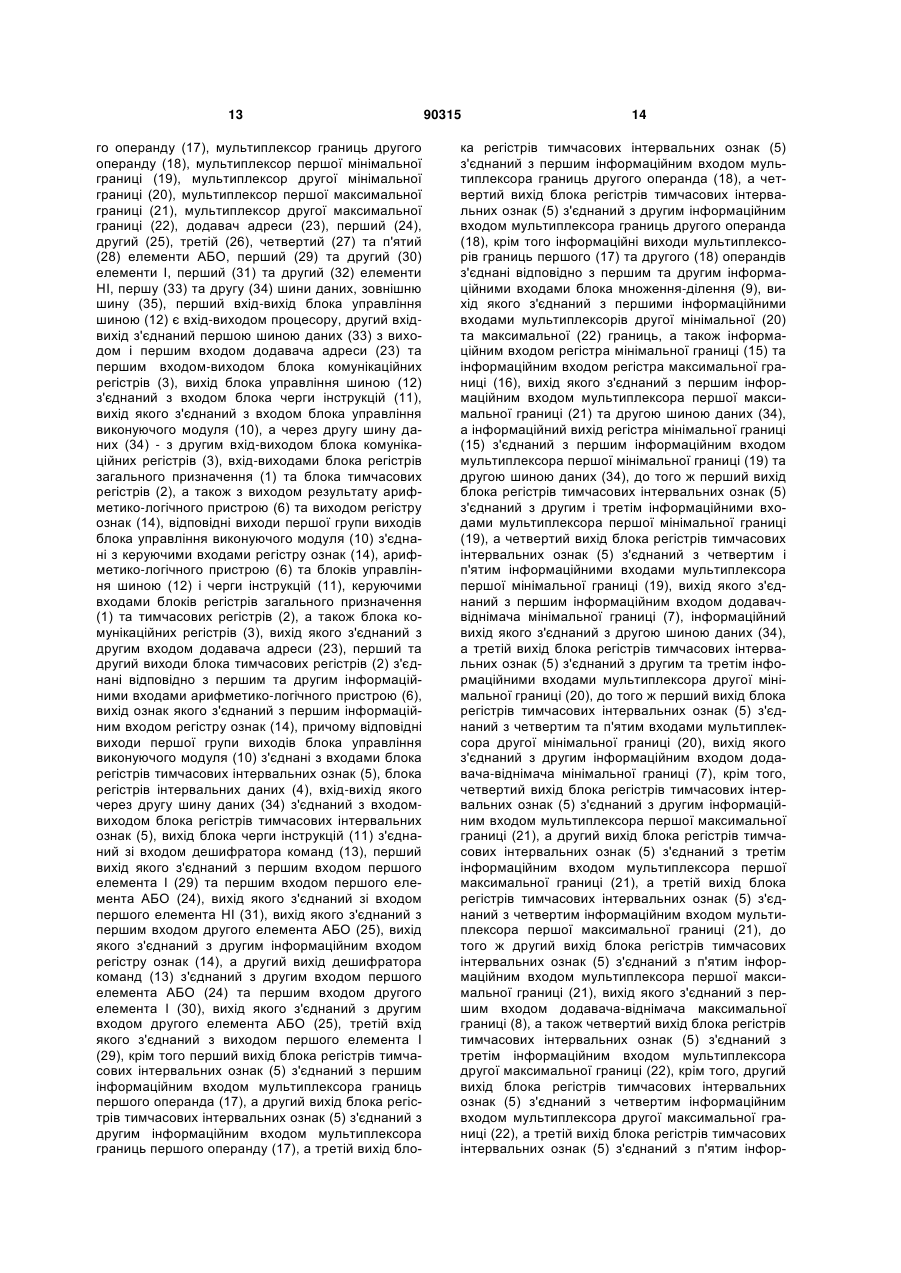

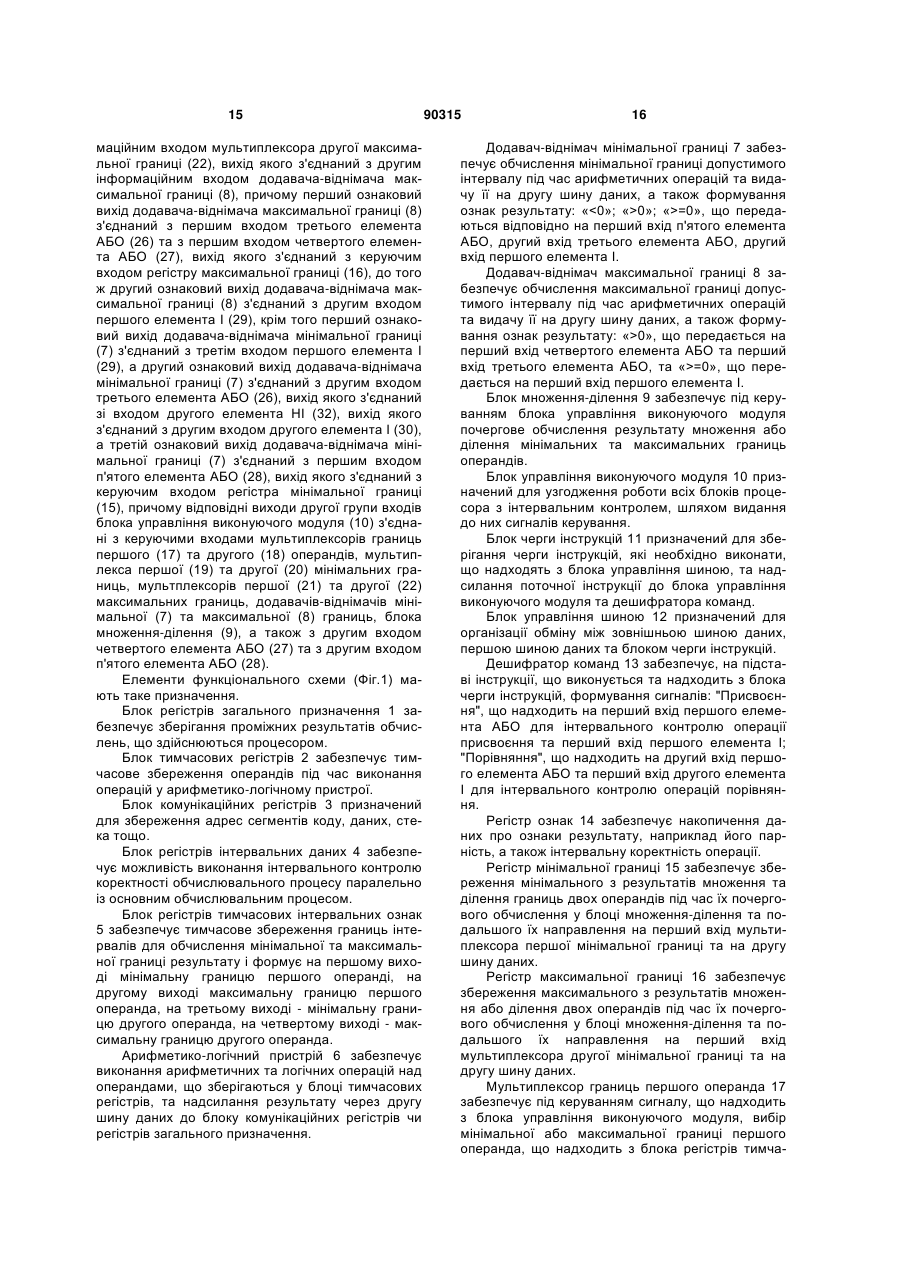

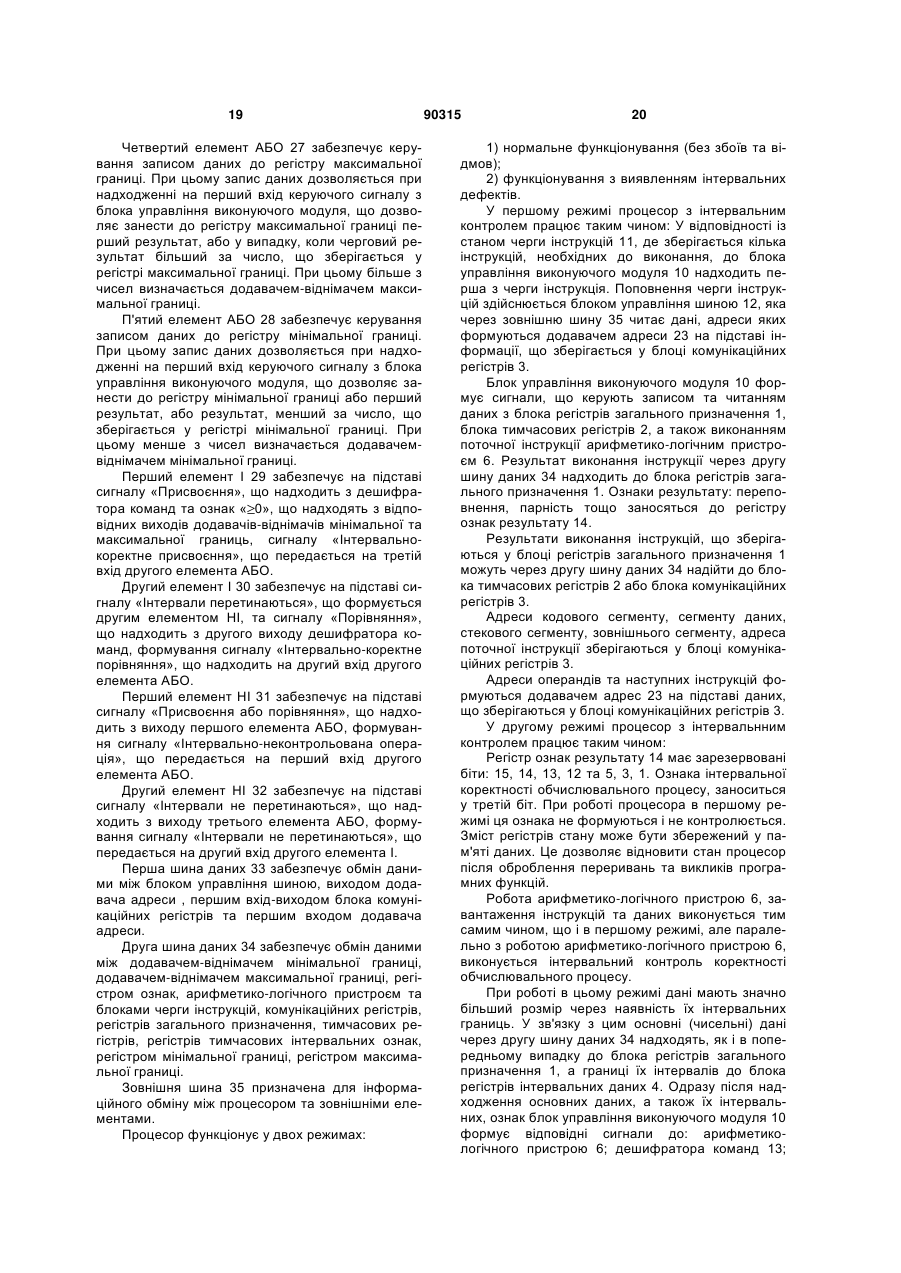

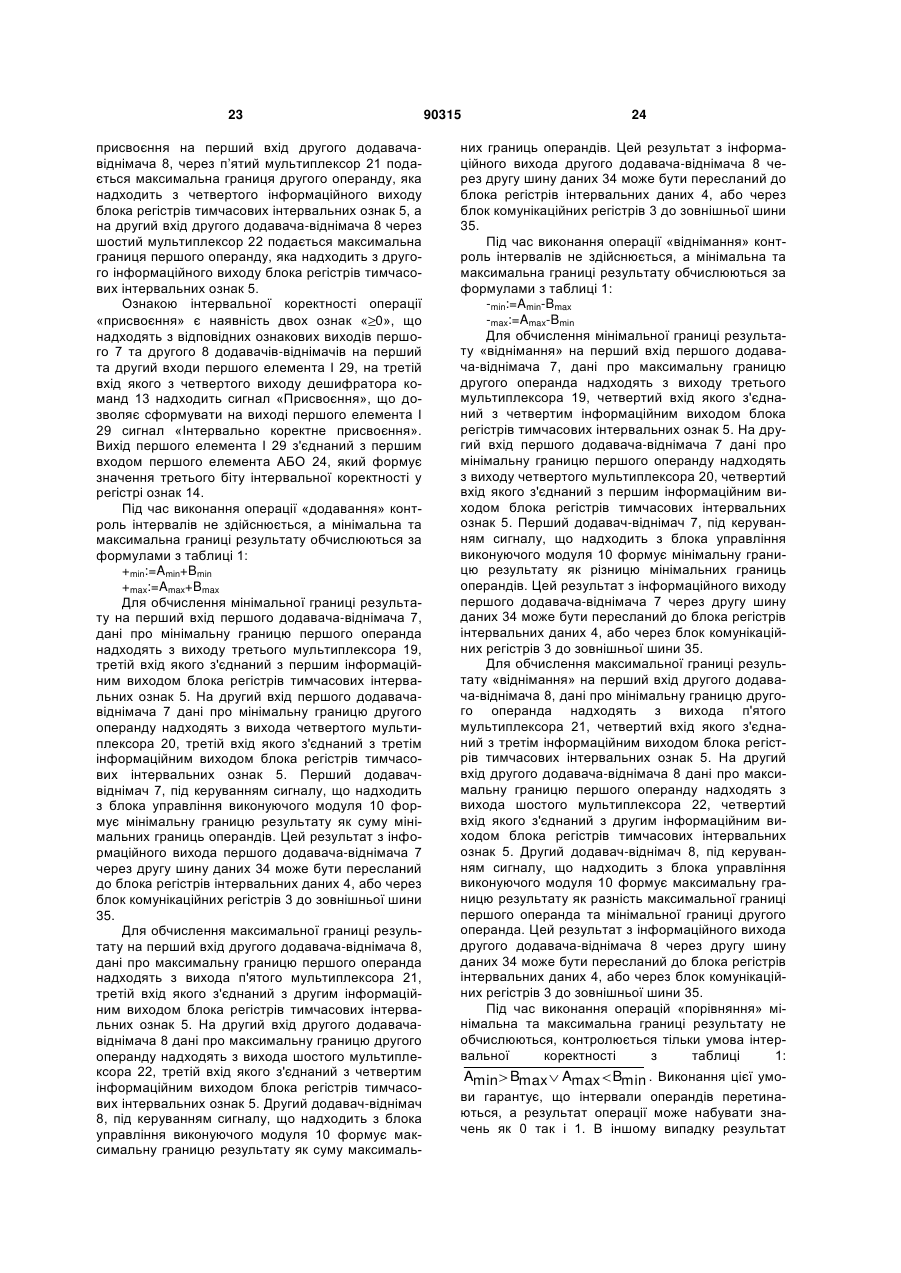

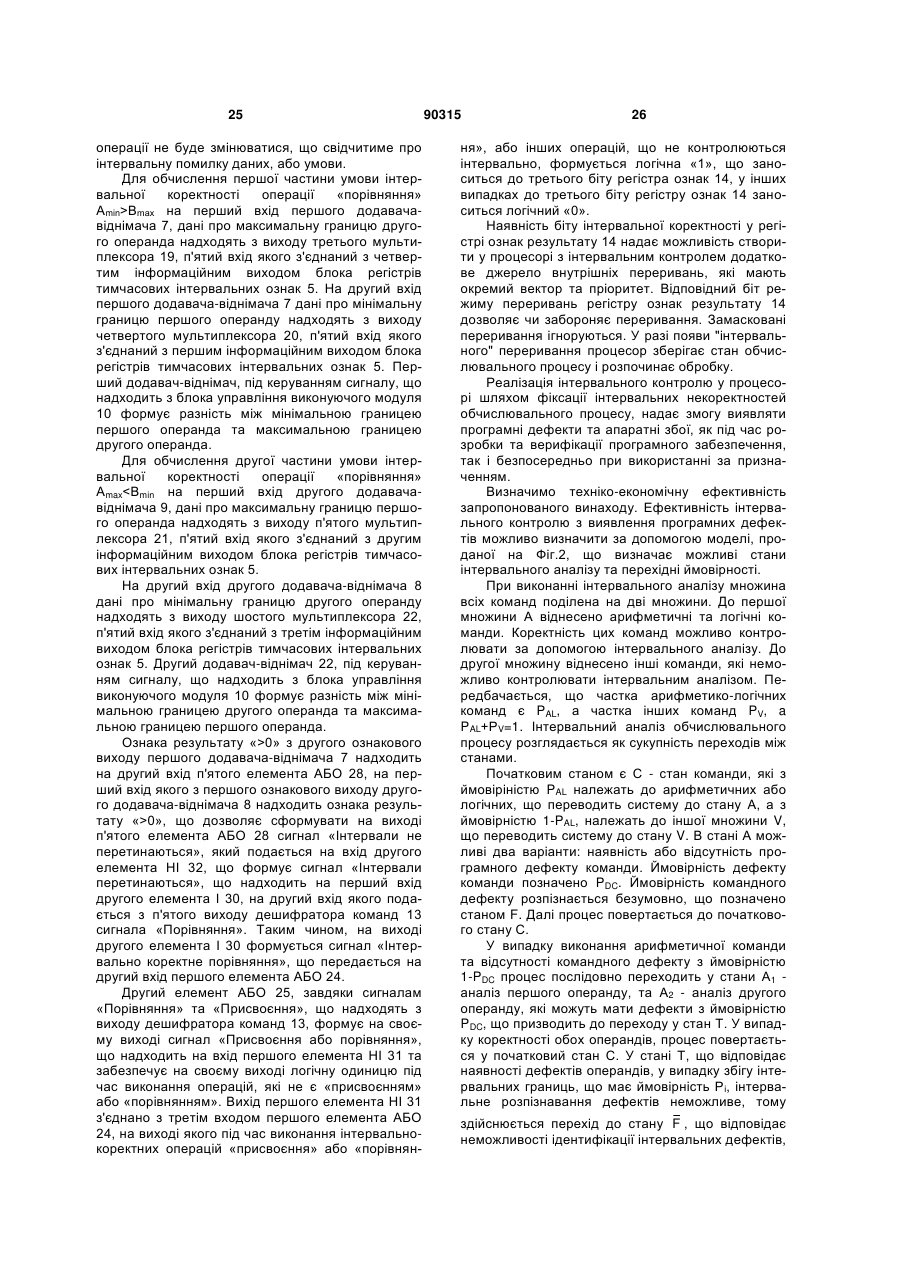

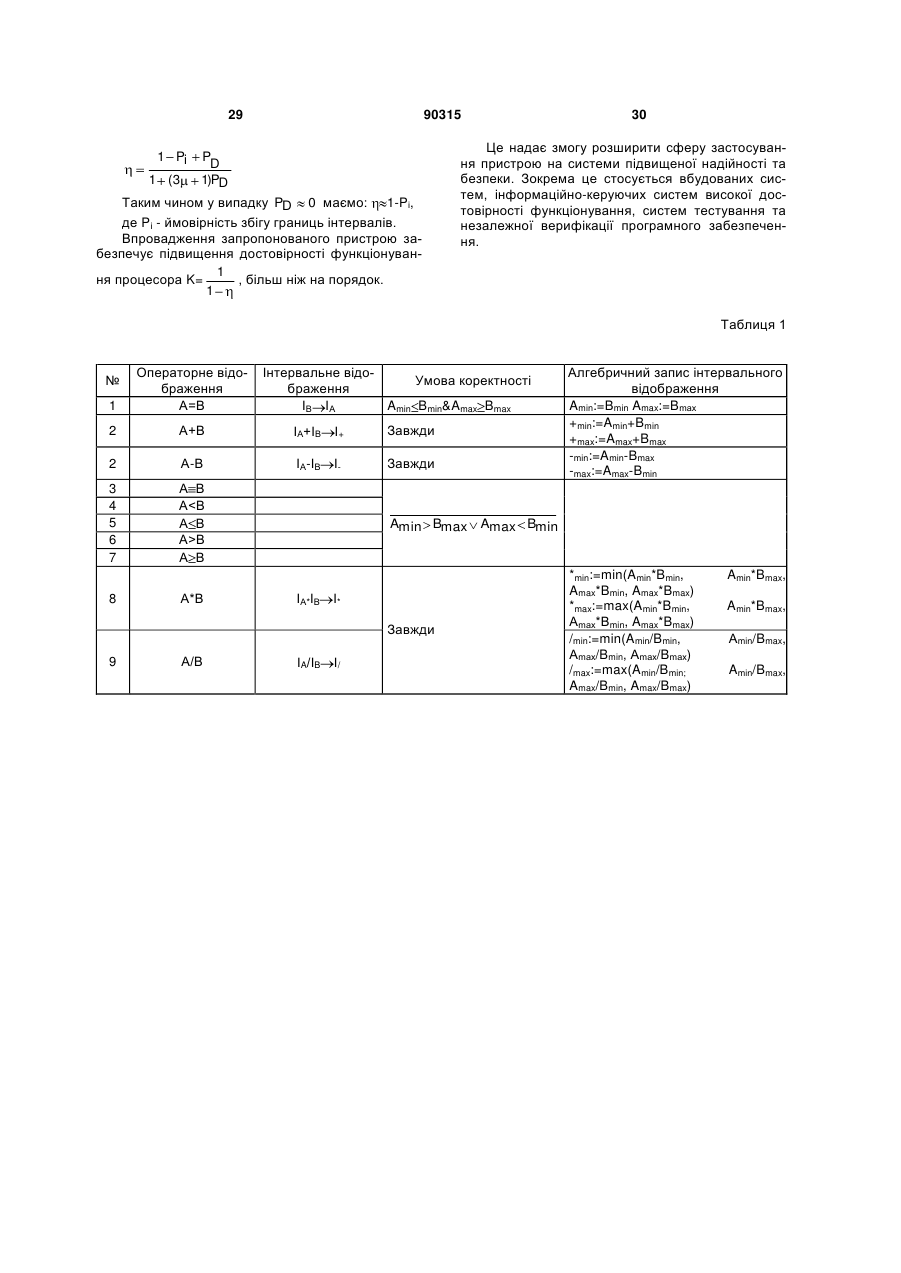

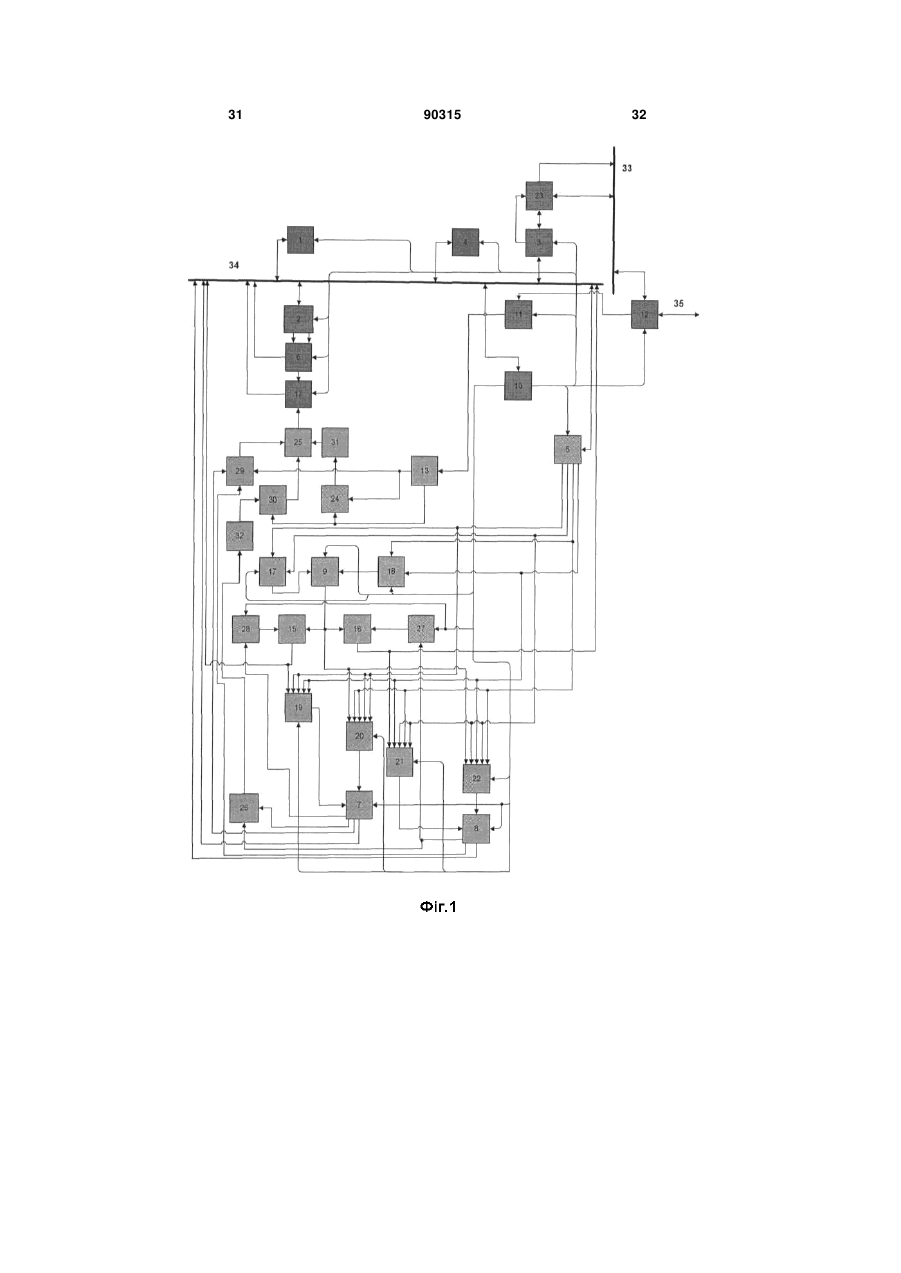

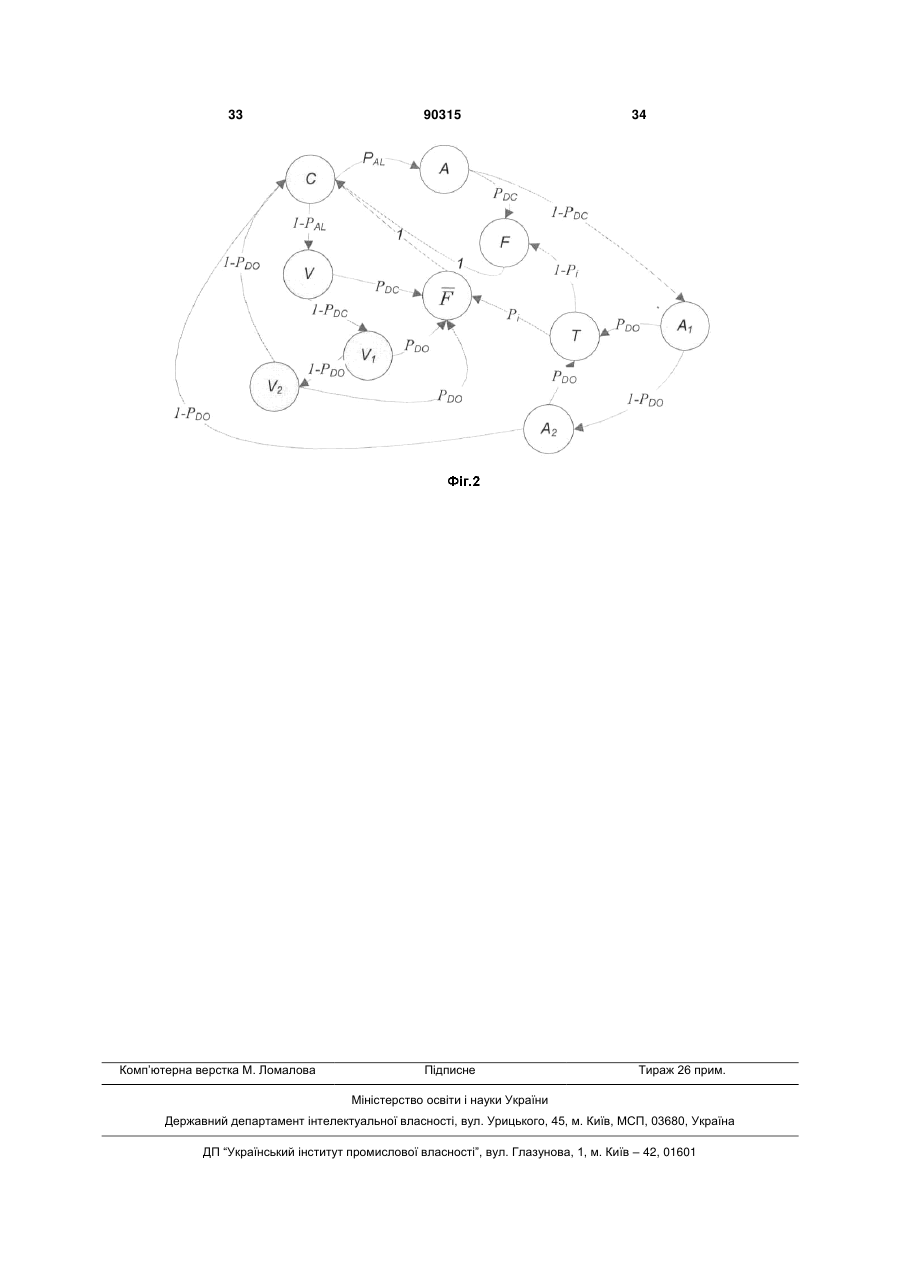

Процесор з інтервальним контролем, що містить блок регістрів загального призначення, блок комунікаційних регістрів, блок тимчасових регістрів, арифметико-логічний пристрій, регістр ознак, додавач адреси, блок черги інструкцій, блок управління виконавчого модуля та блок управління шиною, перший вхід-вихід якого є входомвиходом процесора, другий вхід-вихід з'єднаний першою шиною даних з виходом і першим входом додавача адреси та першим входом-виходом блока комунікаційних регістрів, вихід блока управління шиною з'єднаний з входом блока черги інструкцій, вихід якого з'єднаний з входом блока управління виконавчого модуля, а через другу шину даних - з другим входом-виходом блока комунікаційних регістрів, входами-виходами блоків регістрів загального призначення та тимчасових регістрів, а також з виходом результату арифметико-логічного пристрою та виходом регістра ознак, відповідні виходи першої групи виходів блока управління виконавчого модуля з'єднані з керуючими входами регістра ознак, арифметико-логічного пристрою та блоків управління шиною і черги інструкцій, входами бло 2 (19) 1 3 90315 4 операнда, а другий вихід блока регістрів тимчасових інтервальних ознак з'єднаний з другим інформаційним входом мультиплексора границь першого операнда, а третій вихід блока регістрів тимчасових інтервальних ознак з'єднаний з першим інформаційним входом мультиплексора границь другого операнда, а четвертий вихід блока регістрів тимчасових інтервальних ознак з'єднаний з другим інформаційним входом мультиплексора границь другого операнда, крім того інформаційні виходи мультиплексорів границь першого та другого операндів з'єднані відповідно з першим та другим інформаційними входами блока множенняділення, вихід якого з'єднаний з першими інформаційними входами мультиплексорів другої мінімальної та максимальної границь, а також інформаційним входом регістра мінімальної границі та інформаційним входом регістра максимальної границі, вихід якого з'єднаний з першим інформаційним входом мультиплексора першої максимальної границі та другою шиною даних, а інформаційний вихід регістра мінімальної границі з'єднаний з першим інформаційним входом мультиплексора першої мінімальної границі та другою шиною даних, до того ж перший вихід блока регістрів тимчасових інтервальних ознак з'єднаний з другим і третім інформаційними входами мультиплексора першої мінімальної границі, а четвертий вихід блока регістрів тимчасових інтервальних ознак з'єднаний з четвертим і п'ятим інформаційними входами мультиплексора першої мінімальної границі, вихід якого з'єднаний з першим інформаційним входом додавача-віднімача мінімальної границі, інформаційний вихід якого з'єднаний з другою шиною даних, а третій вихід блока регістрів тимчасових інтервальних ознак з'єднаний з другим та третім інформаційними входами мультиплексора другої мінімальної границі, до того ж перший вихід блока регістрів тимчасових інтервальних ознак з'єднаний з четвертим та п'ятим входами мультиплексора другої мінімальної границі, вихід якого з'єднаний з другим інформаційним входом додавача-віднімача мінімальної границі, крім того, четвертий вихід блока регістрів тимчасових інтервальних ознак з'єднаний з другим інформаційним входом мультиплексора першої максимальної границі, а другий вихід блока регістрів тимчасових інтервальних ознак з'єднаний з третім інформаційним входом мультиплексора першої максимальної границі, а третій вихід блока регістрів тимчасових інтервальних ознак з'єднаний з четвертим інформаційним входом мультиплексора першої максимальної границі, до того ж другий вихід блока регістрів тимчасових інтервальних ознак з'єднаний з п'ятим інформаційним входом мультиплексора першої максимальної границі, вихід якого з'єднаний з першим входом додавача-віднімача максимальної границі, а також четвертий вихід блока регістрів тимчасових інтервальних ознак з'єднаний з третім інформаційним входом мультиплексора другої максимальної границі, крім того, другий вихід блока регістрів тимчасових інтервальних ознак з'єднаний з четвертим інформаційним входом мультиплексора другої максимальної границі, а третій вихід блока регістрів тимчасових інтервальних ознак з'єднаний з п'ятим інформаційним входом мультиплексора другої максимальної границі, вихід якого з'єднаний з другим інформаційним входом додавача-віднімача максимальної границі, причому перший ознаковий вихід додавачавіднімача максимальної границі з'єднаний з першим входом третього елемента АБО та з першим входом четвертого елемента АБО, вихід якого з'єднаний з керуючим входом регістра максимальної границі, до того ж другий ознаковий вихід додавача-віднімача максимальної границі з'єднаний з другим входом першого елемента І, крім того перший ознаковий вихід додавача-віднімача мінімальної границі з'єднаний з третім входом першого елемента І, а другий ознаковий вихід додавачавіднімача мінімальної границі з'єднаний з другим входом третього елемента АБО, вихід якого з'єднаний зі входом другого елемента НІ, вихід якого з'єднаний з другим входом другого елемента І, а третій ознаковий вихід додавача-віднімача мінімальної границі з'єднаний з першим входом п'ятого елемента АБО, вихід якого з'єднаний з керуючим входом регістра мінімальної границі, причому відповідні виходи другої групи входів блока управління виконавчого модуля з'єднані з керуючими входами мультиплексорів границь першого та другого операндів, а також мультиплексорів першої та другої мінімальної та максимальної границі, додавачів-віднімачів мінімальної та максимальної границь, блока множення-ділення, а також з другим входом четвертого елемента АБО та з другим входом п'ятого елемента АБО. Винахід належить до обчислювальної техніки і може бути використаний при розробці засобів обробки та контролю даних в інформаційноаналітичних та інформаційно-керуючих системах підвищеної надійності, зокрема, при проектуванні вбудованих відмовостійких систем, систем тестування, верифікації тощо. Відомий пристрій для контролю арифметикологічних пристроїв (авторське свідоцтво СРСР №1815639, кл. G 0611/00, 1993), що має блок порівняння, додавач, чотири мультиплексори. Недо ліком цього пристрою є обмежені функціональні можливості, оскільки він не забезпечує інтервального контролю даних, що обробляються. Відомий пристрій для ділення (авторське свідоцтво СРСР №1667077, G06F11/00, 7/52, 1991), що містить групу додавачів, вузли згортки за модулем два, два блоки порівняння. Недоліком цього пристрою є низька достовірність функціонування. Вона обмежена через те, що правильність виконання операцій контролюється тільки за рахунок перевірки даних на парність. 5 Найбільш близьким до пропонованого є процесор, що має блок регістрів загального призначення, блок комунікаційних регістрів, блок тимчасових регістрів, арифметико-логічний пристрій, регістр ознак, додавач адреси, блок черги інструкцій, блок управління виконуючого модуля та блок управління шиною, перший вхід-вихід якого є вхідвиходом процесору, другий вхід-вихід з'єднаний першою шиною даних з виходом і першим входом додавача адреси та першим входом-виходом блока комунікаційних регістрів, вихід блока управління шиною з'єднаний з входом блока черги інструкцій, вихід якого з'єднаний з входом блока управління виконуючого модуля, а через другу шину даних - з другим вхід-виходом блока комунікаційних регістрів, вхід-виходами блоків регістрів загального призначення та тимчасових регістрів, а також з виходом результату арифметико-логічного пристрою та виходом регістру ознак, відповідні виходи першої групи виходів блока управління виконуючого модуля з'єднані з керуючими входами регістру ознак, арифметико-логічного пристрою та блоків управління шиною і черги інструкцій, входами блоків регістрів загального призначення та тимчасових регістрів, а також блока комунікаційних регістрів, вихід якого з'єднаний з другим входом додавача адреси, перший та другий виходи блока тимчасових регістрів з'єднані відповідно з першим та другим інформаційними входами арифметикологічного пристрою, вихід ознак якого з'єднаний з першим інформаційним входом регістру ознак (80С186ЕА/80С188ЕА Microprocessor User's Manual. Intel Corporation Literature Sales P.O. Box 7641 Mt. Prospect, IL 60056-7641. – с.2-2, fig.2-1). Недоліком цього пристрою є низька достовірність функціонування, обумовлена обмеженістю можливостей засобів контролю процесора. Контроль функціонування процесора може виконуватися тільки програмними засобами. Це призводить до збільшення ймовірності помилок другого роду, тобто невиявлення часткової втрати працездатності внаслідок збоїв апаратних засобів, або прояву дефектів програмного забезпечення. Програмна реалізація засобів контролю потребує додаткових витрат часу, що знижує оперативність контролю і продуктивність процесора у цілому. В основу винаходу покладено завдання вдосконалення процесору шляхом підвищення достовірності функціонування за рахунок реалізації інтервального контролю процесу обробки даних. Поставлене завдання вирішується тим, що процесор з інтервальним контролем, який містить блок регістрів загального призначення, блок комунікаційних регістрів, блок тимчасових регістрів, арифметико-логічний пристрій, регістр ознак, додавач адреси, блок черги інструкцій, блок управління виконуючого модуля та блок управління шиною, перший вхід-вихід якого є вхід-виходом процесору, другий вхід-вихід з'єднаний першою шиною даних з виходом і першим входом додавача адреси та першим входом-виходом блока комунікаційних регістрів, вихід блока управління шиною з'єднаний з входом блока черги інструкцій, вихід якого з'єднаний з входом блока управління виконуючого модуля, а через другу шину даних - з дру 90315 6 гим вхід-виходом блока комунікаційних регістрів, вхід-виходами блоків регістрів загального призначення та тимчасових регістрів, а також з виходом результату арифметико-логічного пристрою та виходом регістру ознак, відповідні виходи першої групи виходів блока управління виконуючого модуля з'єднані з керуючими входами регістру ознак, арифметико-логічного пристрою та блоків управління шиною і черги інструкцій, входами блоків регістрів загального призначення та тимчасових регістрів, а також блока комунікаційних регістрів, вихід якого з'єднаний з другим входом додавача адреси, перший та другий виходи блока тимчасових регістрів з'єднані відповідно з першим та другим інформаційними входами арифметикологічного пристрою, вихід ознак якого з'єднаний з першим інформаційним входом регістру ознак, згідно з винаходом додатково має блок регістрів інтервальних даних, блок регістрів тимчасових інтервальних ознак, додавач-віднімач мінімальної границі, додавач-віднімач максимальної границі, блок множення-ділення, дешифратор команд, регістр мінімальної границі, регістр максимальної границі, мультиплексор границь першого операнду, мультиплексор границь другого операнду, мультиплексор першої мінімальної границі, мультиплексор другої мінімальної границі, мультиплексор першої максимальної границі, мультиплексор другої максимальної границі, перший, другий, третій, четвертий та п'ятий елементи АБО, перший та другий елементи І, перший та другий елементи НІ, причому відповідні виходи першої групи виходів блока управління виконуючого модуля з'єднані з входами блока регістрів тимчасових інтервальних ознак, блока регістрів інтервальних даних, вхідвихід якого через другу шину даних з'єднаний з входом-виходом блока регістрів тимчасових інтервальних ознак, вихід блока черги інструкцій з'єднаний зі входом дешифратора команд, перший вихід якого з'єднаний з першим входом першого елемента І та першим входом першого елемента АБО, вихід якого з'єднаний зі входом першого елемента НІ, вихід якого з'єднаний з першим входом другого елемента АБО, вихід якого з'єднаний з другим інформаційним входом регістру ознак, а другий вихід дешифратора команд з'єднаний з другим входом першого елемента АБО та першим входом другого елемента І, вихід якого з'єднаний з другим входом другого елемента АБО, третій вхід якого з'єднаний з виходом першого елемента І, крім того перший вихід блока регістрів тимчасових інтервальних ознак з'єднаний з першим інформаційним входом мультиплексора границь першого операнду, а другий вихід блока регістрів тимчасових інтервальних ознак з'єднаний з другим інформаційним входом мультиплексора границь першого операнду, а третій вихід блока регістрів тимчасових інтервальних ознак з'єднаний з першим інформаційним входом мультиплексора границь другого операнду, а четвертий вихід блока регістрів тимчасових інтервальних ознак з'єднаний з другим інформаційним входом мультиплексора границь другого операнду, крім того інформаційні виходи мультиплексорів границь першого та другого операндів з'єднані відповідно з першим та 7 другим інформаційними входами блока множенняділення, вихід якого з'єднаний з першими інформаційними входами мультиплексорів другої мінімальної та максимальної границь, а також інформаційним входом регістра мінімальної границі та інформаційним входом регістра максимальної границі, вихід якого з'єднаний з першим інформаційним входом мультиплексора першої максимальної границі та другою шиною даних, а інформаційний вихід регістра мінімальної границі з'єднаний з першим інформаційним входом мультиплексора першої мінімальної границі та другою шиною даних, до того ж перший вихід блока регістрів тимчасових інтервальних ознак з'єднаний з другим і третім інформаційними входами мультиплексора першої мінімальної границі, а четвертий вихід блока регістрів тимчасових інтервальних ознак з'єднаний з четвертим і п'ятим інформаційними входами мультиплексора першої мінімальної границі, вихід якого з'єднаний з першим інформаційним входом додавач-віднімача мінімальної границі, інформаційний вихід якого з'єднаний з другою шиною даних, а третій вихід блока регістрів тимчасових інтервальних ознак з'єднаний з другим та третім інформаційними входами мультиплексора другої мінімальної границі, до того ж перший вихід блока регістрів тимчасових інтервальних ознак з'єднаний з четвертим та п'ятим входами мультиплексора другої мінімальної границі, вихід якого з'єднаний з другим інформаційним входом додавача-віднімача мінімальної границі, крім того, четвертий вихід блока регістрів тимчасових інтервальних ознак з'єднаний з другим інформаційним входом мультиплексора першої максимальної границі, а другий вихід блока регістрів тимчасових інтервальних ознак з'єднаний з третім інформаційним входом мультиплексора першої максимальної границі, а третій вихід блока регістрів тимчасових інтервальних ознак з'єднаний з четвертим інформаційним входом мультиплексора першої максимальної границі, до того ж другий вихід блока регістрів тимчасових інтервальних ознак з'єднаний з п'ятим інформаційним входом мультиплексора першої максимальної границі, вихід якого з'єднаний з першим входом додавача-віднімача максимальної границі, а також четвертий вихід блока регістрів тимчасових інтервальних ознак з'єднаний з третім інформаційним входом мультиплексора другої максимальної границі, крім того, другий вихід блока регістрів тимчасових інтервальних ознак з'єднаний з четвертим інформаційним входом мультиплексора другої максимальної границі, а третій вихід блока регістрів тимчасових інтервальних ознак з'єднаний з п'ятим інформаційним входом мультиплексора другої максимальної границі, вихід якого з'єднаний з другим інформаційним входом додавача-віднімача максимальної границі, причому перший ознаковий вихід додавачавіднімача максимальної границі з'єднаний з першим входом третього елемента АБО та з першим входом четвертого елемента АБО, вихід якого з'єднаний з керуючим входом регістру максимальної границі, до того ж другий ознаковий вихід додавача-віднімача максимальної границі з'єднаний з другим входом першого елемента І, крім того 90315 8 перший ознаковий вихід додавача-віднімача мінімальної границі з'єднаний з третім входом першого елемента І, а другий ознаковий вихід додавачавіднімача мінімальної границі з'єднаний з другим входом третього елемента АБО, вихід якого з'єднаний зі входом другого елемента НІ, вихід якого з'єднаний з другим входом другого елемента І, а третій ознаковий вихід додавача-віднімача мінімальної границі з'єднаний з першим входом п'ятого елемента АБО, вихід якого з'єднаний з керуючим входом регістра мінімальної границі, причому відповідні виходи другої групи входів блока управління виконуючого модуля з'єднані з керуючими входами мультиплексорів границь першого та другого операндів, а також мультиплексорів першої та другої мінімальної та максимальної границі, додавачів-віднімачів мінімальної та максимальної границь, блока множення-ділення, а також з другим входом четвертого елемента АБО та з другим входом п'ятого елемента АБО. Запропонований процесор з інтервальним контролем має новий склад елементів та нову організацію зв'язків між ними, які забезпечують нові технічні властивості винаходу. Технічним результатом, який при цьому досягається, є підвищення достовірності функціонування. Сутність винаходу полягає в тому, що у процесорі реалізується метод контролю функціонування за рахунок оперативної перевірки правильності виконання операцій шляхом аналізу коректності перетворень інтервалів даних, що обробляються. Тобто внаслідок введення додаткових елементів та їх зв'язків додатково контролюється інтервальна коректність програмного забезпечення. Головна концепція інтервального контролю полягає у використанні інтервального вектора пари чисел, що визначає припустимі мінімальне та максимальне значення програмних змінних, а також аксіоматичній відповідності кожному елементарному операторному відображенню інтервального відображення (IB), аксіоматика якого подано в таблиці 1, де Amin, Amax, Bmin, Bmax - відповідно мінімальна та максимальна границі операндів А, В; a +min, +max, -min, -max, *min, *max, /min, /max - відповідно мінімальні та максимальні границі результатів операцій. Існування необхідної умови коректності створює можливість контролю обчислювальних процесів у точках виконання операцій присвоєння та порівняння. Реалізація інтервального контролю обчислювального процесу потребує використання у пристрої: блока регістрів інтервальних даних, блока регістрів тимчасових інтервальних ознак, першого та другого додавачів-віднімачів, блока множенняділення, дешифратора команд, регістра мінімальної границі, регістра максимальної границі, першого, другого, третього, четвертого, п'ятого та шостого мультиплексорів, першого, другого, третього, четвертого та п'ятого елементів АБО, першого та другого елементів І, першого та другого елементів НІ. Введення блока регістрів інтервальних даних та їх зв'язків забезпечує можливість виконання інтервального контролю коректності обчислюваль 9 ного процесу паралельно із основним обчислювальним процесом. Введення блока регістрів тимчасових інтервальних ознак та їх зв'язків забезпечує тимчасове збереження границь інтервалів для обчислення мінімальної та максимальної границі результату та контролю інтервальної коректності та формує на першому виході мінімальну границю першого операнда, на другому виході максимальну границю першого операнда, на третьому виході - мінімальну границю другого операнда, на четвертому виході - максимальну границю другого операнда. Введення додавача-віднімача мінімальної границі та його зв'язків забезпечує обчислення мінімальної границі допустимого інтервалу під час арифметичних операцій та видачу її на другу шину даних, а також формування ознак результату: «0»; «>=0», що передаються відповідно на перший вхід п'ятого елемента АБО, другий вхід третього елемента АБО, другий вхід першого елемента І. Введення додавача-віднімача максимальної границі та його зв'язків забезпечує обчислення максимальної границі допустимого інтервалу під час арифметичних операцій та видачу її на другу шину даних, а також формування ознак результату: «>0», що передається на перший вхід четвертого елемента АБО та перший вхід третього елемента АБО, та «>=0», що передається на перший вхід першого елемента І. Введення блока множення-ділення та його зв'язків забезпечує почергове обчислення результату множення або ділення мінімальних та максимальних границь операндів. Введення дешифратора команд та його зв'язків забезпечує, на підставі інструкції, що виконується та надходить з блока черги інструкцій, формування сигналів: "Присвоєння", що надходить на перший вхід першого елемента АБО для інтервального контролю операції присвоєння та перший вхід першого елемента І; "Порівняння", що надходить на другий вхід першого елемента АБО та перший вхід другого елемента І для інтервального контролю операцій порівняння. Введення регістра мінімальної границі та його зв'язків забезпечує збереження мінімального з результатів множення та ділення границь двох операндів під час їх почергового обчислення у блоці множення-ділення та подальшого їх направлення на перший вхід мультиплексора першої мінімальної границі та на другу шину даних. Введення регістра максимальної границі та його зв'язків забезпечує збереження максимального з результатів множення або ділення двох операндів під час їх почергового обчислення у блоці множення-ділення та подальшого їх направлення на перший вхід мультиплексора другої мінімальної границі та на другу шину даних. Введення мультиплексора границь першого операнда та його зв'язків забезпечує під керуванням сигналу, що надходить з блока управління виконуючого модуля, вибір мінімальної або максимальної границі першого операнда, яка передається на перший вхід блока множення-ділення. 90315 10 Введення мультиплексора границь другого операнда та його зв'язків забезпечує під керуванням сигналу, що надходить з блока управління виконуючого модуля, вибір мінімальної або максимальної границі другого операнда, яка передається на другий вхід блока множення-ділення. Введення мультиплексора першої мінімальної границі та його зв'язків забезпечує під керуванням сигналів, що надходять з блока управління виконуючого модуля, передачу на перший інформаційний вхід додавача-віднімача мінімальної границі: під час виконання операцій множення або ділення даних, що зберігаються у регістрі мінімальної границі; під час виконання операції присвоєння - мінімальної границі першого операнда, що надходить з першого виходу блока регістрів тимчасових інтервальних ознак; під час виконання операції додавання - мінімальної границі першого операнда, що надходить з першого виходу блока регістрів тимчасових інтервальних ознак; під час виконання операції віднімання - максимальної границі другого операнда, що надходить з четвертого виходу блока регістрів тимчасових інтервальних ознак; під час виконання операції порівняння - максимальної границі другого операнда, що надходить з першого виходу блока регістрів тимчасових інтервальних ознак. Введення мультиплексора другої мінімальної границі та його зв'язків забезпечує під керуванням сигналів, що надходять з блока управління виконуючого модуля, передачу на другий інформаційний вхід додавача-віднімача мінімальної границі: під час виконання операцій множення або ділення результату, що надходить з блока множення-ділення; під час виконання операції присвоєння - мінімальної границі другого операнда, що надходить з другого виходу блока регістрів тимчасових інтервальних ознак; під час виконання операції додавання - мінімальної границі другого операнда, що надходить з другого виходу блока регістрів тимчасових інтервальних ознак; під час виконання операції віднімання - мінімальної границі першого операнда, що надходить з першого виходу блока регістрів тимчасових інтервальних ознак; під час виконання операції порівняння - мінімальної границі першого операнда, що надходить з першого виходу блока регістрів тимчасових інтервальних ознак. Введення мультиплексора першої максимальної границі та його зв'язків забезпечує під керуванням сигналів, що надходять з блока управління виконуючого модуля, передачу на перший інформаційний вхід додавача-віднімача максимальної границі: під час виконання операцій множення або ділення результату даних, що зберігаються у регістрі максимальної границі; під час виконання операції присвоєння - максимальної границі другого операнда, що надхо 11 дить з четвертого виходу блока регістрів тимчасових інтервальних ознак; під час виконання операції додавання - максимальної границі першого операнда, що надходить з другого виходу блока регістрів тимчасових інтервальних ознак; під час виконання операції віднімання - мінімальної границі другого операнда, що надходить з третього виходу блока регістрів тимчасових інтервальних ознак; під час виконання операції порівняння - максимальної границі першого операнда, що надходить з другого виходу блока регістрів тимчасових інтервальних ознак. Введення мультиплексора другої максимальної границі та його зв'язків забезпечує під керуванням сигналів, що надходять з блока управління виконуючого модуля, передачу на другий інформаційний вхід додавача-віднімача максимальної границі: під час виконання операцій множення або ділення результату, що надходить з блока множення-ділення; під час виконання операції присвоєння - максимальної границі другого операнда, що надходить з третього виходу блока регістрів тимчасових інтервальних ознак; під час виконання операції додавання - максимальної границі другого операнда, що надходить з четвертого виходу блока регістрів тимчасових інтервальних ознак; під час виконання операції віднімання - максимальної границі першого операнда, що надходить з другого виходу блока регістрів тимчасових інтервальних ознак; під час виконання операції порівняння - мінімальної границі другого операнда, що надходить з третього виходу блока регістрів тимчасових інтервальних ознак. Введення першого елемента АБО та його зв'язків забезпечує на підставі сигналів "Присвоєння" та "Порівняння", що надходять з відповідно з першого та другого виходів дешифратора команд, формування сигналу "Присвоєння або Порівняння", що надходить на вхід першого елемента НІ. Введення другого елемента АБО та його зв'язків забезпечує на підставі сигналів: "Інтервально коректне присвоєння", що надходить з виходу першого елемента І; "Інтервально коректне порівняння", що надходить з виходу другого елемента І; "Інтервально неконтрольована операція", що надходить з виходу першого елемента НІ, формування ознаки інтервальної коректності результату, що надходить на другий інформаційний вхід регістру ознак. Введення третього елемента АБО та його зв'язків необхідно для формування на підставі ознак «>0», що надходять з ознакових виходів додавачів-віднімачів мінімальної та максимальної границь, сигналу "Інтервали не перетинаються", що передається на вхід другого елемента НІ. Введення четвертого елемента АБО та його зв'язків необхідно для керування записом даних до регістру максимальної границі. При цьому запис даних дозволяється при надходженні на перший 90315 12 вхід керуючого сигналу з блока управління виконуючого модуля, що дозволяє занести до регістру максимальної границі перший результат, або у випадку, коли черговий результат більший за число, що зберігається у регістрі максимальної границі. При цьому більше з чисел визначається додавачем-віднімачем максимальної границі. Введення п'ятого елемента АБО та його зв'язків необхідно для керування записом даних до регістру мінімальної границі. При цьому запис даних дозволяється при надходженні на перший вхід керуючого сигналу з блока управління виконуючого модуля, що дозволяє занести до регістру мінімальної границі або перший результат, або результат, менший за число, що зберігається у регістрі мінімальної границі. При цьому менше з чисел визначається додавачем-віднімачем мінімальної границі. Введення першого елемента І та його зв'язків забезпечує на підставі сигналу «Присвоєння», що надходить з дешифратора команд та ознак « 0», що надходять з відповідних виходів додавачіввіднімачів мінімальної та максимальної границь, сигналу «Інтервально-коректне присвоєння», що передається на третій вхід другого елемента АБО. Введення другого елемента І та його зв'язків забезпечує на підставі сигналу «Інтервали перетинаються», що формується другим елементом НІ, та сигналу «Порівняння», що надходить з другого виходу дешифратора команд, формування сигналу «Інтервально-коректне порівняння», що надходить на другий вхід другого елемента АБО. Введення першого елемента НІ та його зв'язків забезпечує на підставі сигналу «Присвоєння або порівняння», що надходить з виходу першого елемента АБО, формування сигналу «Інтервально-неконтрольована операція», що передається на третій вхід другого елемента АБО. Введення другого елемента НІ та його зв'язків забезпечує на підставі сигналу «Інтервали не перетинаються», що надходить з виходу третього елемента АБО, формування сигналу «Інтервали перетинаються», що передається на другий вхід другого елемента І. Таким чином, введення зазначених елементів та обумовлених ними зв'язків забезпечує не тільки оперативний інтервальний контроль програмного забезпечення, але й виявлення порушень внаслідок збоїв та відмов апаратних і програмних засобів. На Фіг.1 надано функціональну схему пристрою. Процесор з інтервальним контролем (Фіг.1) має блок регістрів загального призначення (1), блок тимчасових регістрів (2), блок комунікаційних регістрів (3), блок регістрів інтервальних даних (4), блок регістрів тимчасових інтервальних ознак (5), арифметико-логічний пристрій (6), додавачвіднімач мінімальної границі (7), додавач-віднімач максимальної границі (8), блок множення-ділення (9), блок управління виконуючого модуля (10), блок черги інструкцій (11), блок управління шиною (12), дешифратор команд (13), регістр ознак (14), регістр мінімальної границі (15), регістр максимальної границі (16), мультиплексор границь першо 13 го операнду (17), мультиплексор границь другого операнду (18), мультиплексор першої мінімальної границі (19), мультиплексор другої мінімальної границі (20), мультиплексор першої максимальної границі (21), мультиплексор другої максимальної границі (22), додавач адреси (23), перший (24), другий (25), третій (26), четвертий (27) та п'ятий (28) елементи АБО, перший (29) та другий (30) елементи І, перший (31) та другий (32) елементи НІ, першу (33) та другу (34) шини даних, зовнішню шину (35), перший вхід-вихід блока управління шиною (12) є вхід-виходом процесору, другий вхідвихід з'єднаний першою шиною даних (33) з виходом і першим входом додавача адреси (23) та першим входом-виходом блока комунікаційних регістрів (3), вихід блока управління шиною (12) з'єднаний з входом блока черги інструкцій (11), вихід якого з'єднаний з входом блока управління виконуючого модуля (10), а через другу шину даних (34) - з другим вхід-виходом блока комунікаційних регістрів (3), вхід-виходами блока регістрів загального призначення (1) та блока тимчасових регістрів (2), а також з виходом результату арифметико-логічного пристрою (6) та виходом регістру ознак (14), відповідні виходи першої групи виходів блока управління виконуючого модуля (10) з'єднані з керуючими входами регістру ознак (14), арифметико-логічного пристрою (6) та блоків управління шиною (12) і черги інструкцій (11), керуючими входами блоків регістрів загального призначення (1) та тимчасових регістрів (2), а також блока комунікаційних регістрів (3), вихід якого з'єднаний з другим входом додавача адреси (23), перший та другий виходи блока тимчасових регістрів (2) з'єднані відповідно з першим та другим інформаційними входами арифметико-логічного пристрою (6), вихід ознак якого з'єднаний з першим інформаційним входом регістру ознак (14), причому відповідні виходи першої групи виходів блока управління виконуючого модуля (10) з'єднані з входами блока регістрів тимчасових інтервальних ознак (5), блока регістрів інтервальних даних (4), вхід-вихід якого через другу шину даних (34) з'єднаний з входомвиходом блока регістрів тимчасових інтервальних ознак (5), вихід блока черги інструкцій (11) з'єднаний зі входом дешифратора команд (13), перший вихід якого з'єднаний з першим входом першого елемента І (29) та першим входом першого елемента АБО (24), вихід якого з'єднаний зі входом першого елемента НІ (31), вихід якого з'єднаний з першим входом другого елемента АБО (25), вихід якого з'єднаний з другим інформаційним входом регістру ознак (14), а другий вихід дешифратора команд (13) з'єднаний з другим входом першого елемента АБО (24) та першим входом другого елемента І (30), вихід якого з'єднаний з другим входом другого елемента АБО (25), третій вхід якого з'єднаний з виходом першого елемента І (29), крім того перший вихід блока регістрів тимчасових інтервальних ознак (5) з'єднаний з першим інформаційним входом мультиплексора границь першого операнда (17), а другий вихід блока регістрів тимчасових інтервальних ознак (5) з'єднаний з другим інформаційним входом мультиплексора границь першого операнду (17), а третій вихід бло 90315 14 ка регістрів тимчасових інтервальних ознак (5) з'єднаний з першим інформаційним входом мультиплексора границь другого операнда (18), а четвертий вихід блока регістрів тимчасових інтервальних ознак (5) з'єднаний з другим інформаційним входом мультиплексора границь другого операнда (18), крім того інформаційні виходи мультиплексорів границь першого (17) та другого (18) операндів з'єднані відповідно з першим та другим інформаційними входами блока множення-ділення (9), вихід якого з'єднаний з першими інформаційними входами мультиплексорів другої мінімальної (20) та максимальної (22) границь, а також інформаційним входом регістра мінімальної границі (15) та інформаційним входом регістра максимальної границі (16), вихід якого з'єднаний з першим інформаційним входом мультиплексора першої максимальної границі (21) та другою шиною даних (34), а інформаційний вихід регістра мінімальної границі (15) з'єднаний з першим інформаційним входом мультиплексора першої мінімальної границі (19) та другою шиною даних (34), до того ж перший вихід блока регістрів тимчасових інтервальних ознак (5) з'єднаний з другим і третім інформаційними входами мультиплексора першої мінімальної границі (19), а четвертий вихід блока регістрів тимчасових інтервальних ознак (5) з'єднаний з четвертим і п'ятим інформаційними входами мультиплексора першої мінімальної границі (19), вихід якого з'єднаний з першим інформаційним входом додавачвіднімача мінімальної границі (7), інформаційний вихід якого з'єднаний з другою шиною даних (34), а третій вихід блока регістрів тимчасових інтервальних ознак (5) з'єднаний з другим та третім інформаційними входами мультиплексора другої мінімальної границі (20), до того ж перший вихід блока регістрів тимчасових інтервальних ознак (5) з'єднаний з четвертим та п'ятим входами мультиплексора другої мінімальної границі (20), вихід якого з'єднаний з другим інформаційним входом додавача-віднімача мінімальної границі (7), крім того, четвертий вихід блока регістрів тимчасових інтервальних ознак (5) з'єднаний з другим інформаційним входом мультиплексора першої максимальної границі (21), а другий вихід блока регістрів тимчасових інтервальних ознак (5) з'єднаний з третім інформаційним входом мультиплексора першої максимальної границі (21), а третій вихід блока регістрів тимчасових інтервальних ознак (5) з'єднаний з четвертим інформаційним входом мультиплексора першої максимальної границі (21), до того ж другий вихід блока регістрів тимчасових інтервальних ознак (5) з'єднаний з п'ятим інформаційним входом мультиплексора першої максимальної границі (21), вихід якого з'єднаний з першим входом додавача-віднімача максимальної границі (8), а також четвертий вихід блока регістрів тимчасових інтервальних ознак (5) з'єднаний з третім інформаційним входом мультиплексора другої максимальної границі (22), крім того, другий вихід блока регістрів тимчасових інтервальних ознак (5) з'єднаний з четвертим інформаційним входом мультиплексора другої максимальної границі (22), а третій вихід блока регістрів тимчасових інтервальних ознак (5) з'єднаний з п'ятим інфор 15 маційним входом мультиплексора другої максимальної границі (22), вихід якого з'єднаний з другим інформаційним входом додавача-віднімача максимальної границі (8), причому перший ознаковий вихід додавача-віднімача максимальної границі (8) з'єднаний з першим входом третього елемента АБО (26) та з першим входом четвертого елемента АБО (27), вихід якого з'єднаний з керуючим входом регістру максимальної границі (16), до того ж другий ознаковий вихід додавача-віднімача максимальної границі (8) з'єднаний з другим входом першого елемента І (29), крім того перший ознаковий вихід додавача-віднімача мінімальної границі (7) з'єднаний з третім входом першого елемента І (29), а другий ознаковий вихід додавача-віднімача мінімальної границі (7) з'єднаний з другим входом третього елемента АБО (26), вихід якого з'єднаний зі входом другого елемента НІ (32), вихід якого з'єднаний з другим входом другого елемента І (30), а третій ознаковий вихід додавача-віднімача мінімальної границі (7) з'єднаний з першим входом п'ятого елемента АБО (28), вихід якого з'єднаний з керуючим входом регістра мінімальної границі (15), причому відповідні виходи другої групи входів блока управління виконуючого модуля (10) з'єднані з керуючими входами мультиплексорів границь першого (17) та другого (18) операндів, мультиплекса першої (19) та другої (20) мінімальних границь, мультплексорів першої (21) та другої (22) максимальних границь, додавачів-віднімачів мінімальної (7) та максимальної (8) границь, блока множення-ділення (9), а також з другим входом четвертого елемента АБО (27) та з другим входом п'ятого елемента АБО (28). Елементи функціонального схеми (Фіг.1) мають таке призначення. Блок регістрів загального призначення 1 забезпечує зберігання проміжних результатів обчислень, що здійснюються процесором. Блок тимчасових регістрів 2 забезпечує тимчасове збереження операндів під час виконання операцій у арифметико-логічному пристрої. Блок комунікаційних регістрів 3 призначений для збереження адрес сегментів коду, даних, стека тощо. Блок регістрів інтервальних даних 4 забезпечує можливість виконання інтервального контролю коректності обчислювального процесу паралельно із основним обчислювальним процесом. Блок регістрів тимчасових інтервальних ознак 5 забезпечує тимчасове збереження границь інтервалів для обчислення мінімальної та максимальної границі результату і формує на першому виході мінімальну границю першого операнді, на другому виході максимальну границю першого операнда, на третьому виході - мінімальну границю другого операнда, на четвертому виході - максимальну границю другого операнда. Арифметико-логічний пристрій 6 забезпечує виконання арифметичних та логічних операцій над операндами, що зберігаються у блоці тимчасових регістрів, та надсилання результату через другу шину даних до блоку комунікаційних регістрів чи регістрів загального призначення. 90315 16 Додавач-віднімач мінімальної границі 7 забезпечує обчислення мінімальної границі допустимого інтервалу під час арифметичних операцій та видачу її на другу шину даних, а також формування ознак результату: «0»; «>=0», що передаються відповідно на перший вхід п'ятого елемента АБО, другий вхід третього елемента АБО, другий вхід першого елемента І. Додавач-віднімач максимальної границі 8 забезпечує обчислення максимальної границі допустимого інтервалу під час арифметичних операцій та видачу її на другу шину даних, а також формування ознак результату: «>0», що передається на перший вхід четвертого елемента АБО та перший вхід третього елемента АБО, та «>=0», що передається на перший вхід першого елемента І. Блок множення-ділення 9 забезпечує під керуванням блока управління виконуючого модуля почергове обчислення результату множення або ділення мінімальних та максимальних границь операндів. Блок управління виконуючого модуля 10 призначений для узгодження роботи всіх блоків процесора з інтервальним контролем, шляхом видання до них сигналів керування. Блок черги інструкцій 11 призначений для зберігання черги інструкцій, які необхідно виконати, що надходять з блока управління шиною, та надсилання поточної інструкції до блока управління виконуючого модуля та дешифратора команд. Блок управління шиною 12 призначений для організації обміну між зовнішньою шиною даних, першою шиною даних та блоком черги інструкцій. Дешифратор команд 13 забезпечує, на підставі інструкції, що виконується та надходить з блока черги інструкцій, формування сигналів: "Присвоєння", що надходить на перший вхід першого елемента АБО для інтервального контролю операції присвоєння та перший вхід першого елемента І; "Порівняння", що надходить на другий вхід першого елемента АБО та перший вхід другого елемента І для інтервального контролю операцій порівняння. Регістр ознак 14 забезпечує накопичення даних про ознаки результату, наприклад його парність, а також інтервальну коректність операції. Регістр мінімальної границі 15 забезпечує збереження мінімального з результатів множення та ділення границь двох операндів під час їх почергового обчислення у блоці множення-ділення та подальшого їх направлення на перший вхід мультиплексора першої мінімальної границі та на другу шину даних. Регістр максимальної границі 16 забезпечує збереження максимального з результатів множення або ділення двох операндів під час їх почергового обчислення у блоці множення-ділення та подальшого їх направлення на перший вхід мультиплексора другої мінімальної границі та на другу шину даних. Мультиплексор границь першого операнда 17 забезпечує під керуванням сигналу, що надходить з блока управління виконуючого модуля, вибір мінімальної або максимальної границі першого операнда, що надходить з блока регістрів тимча 17 сових інтервальних ознак та передається на перший вхід блока множення-ділення. Мультиплексор границь другого операнда 18 забезпечує під керуванням сигналу, що надходить з блока управління виконуючого модуля, вибір мінімальної або максимальної границі другого операнда, що надходить з блока регістрів тимчасових інтервальних ознак та передається на другий вхід блока множення-ділення. Мультиплексом першої мінімальної границі 19 забезпечує під керуванням сигналів, що надходять з блока управління виконуючого модуля, передачу на перший інформаційний вхід додавача-віднімача мінімальної границі: під час виконання операцій множення або ділення даних, що зберігаються у регістрі мінімальної границі; під час виконання операції присвоєння - мінімальної границі першого операнда, що надходить з першого виходу блока регістрів тимчасових інтервальних ознак; під час виконання операції додавання - мінімальної границі першого операнда, що надходить з першого виходу блока регістрів тимчасових інтервальних ознак; під час виконання операції віднімання - максимальної границі другого операнда, що надходить з четвертого виходу блока регістрів тимчасових інтервальних ознак; під час виконання операції порівняння - максимальної границі другого операнда, що надходить з першого виходу блока регістрів тимчасових інтервальних ознак. Мультиплексор другої мінімальної границі 20 забезпечує під керуванням сигналів, що надходять з блока управління виконуючого модуля, передачу на другий інформаційний вхід додавача-віднімача мінімальної границі: під час виконання операцій множення або ділення результату, що надходить з блока множення-ділення; під час виконання операції присвоєння - мінімальної границі другого операнда, що надходить з другого виходу блока регістрів тимчасових інтервальних ознак; під час виконання операції додавання - мінімальної границі другого операнда, що надходить з другого виходу блока регістрів тимчасових інтервальних ознак; під час виконання операції віднімання - мінімальної границі першого операнда, що надходить з першого виходу блока регістрів тимчасових інтервальних ознак; під час виконання операції порівняння - мінімальної границі першого операнда, що надходить з першого виходу блока регістрів тимчасових інтервальних ознак. Мультиплексор першої максимальної границі 21 забезпечує під керуванням сигналів, що надходять з блока управління виконуючого модуля, передачу на перший інформаційний вхід додавачавіднімача максимальної границі: під час виконання операцій множення або ділення результату даних, що зберігаються у регістрі максимальної границі; 90315 18 під час виконання операції присвоєння - максимальної границі другого операнда, що надходить з четвертого виходу блока регістрів тимчасових інтервальних ознак; під час виконання операції додавання - максимальної границі першого операнда, що надходить з другого виходу блока регістрів тимчасових інтервальних ознак; під час виконання операції віднімання - мінімальної границі другого операнда, що надходить з третього виходу блока регістрів тимчасових інтервальних ознак; під час виконання операції порівняння - максимальної границі першого операнда, що надходить з другого виходу блока регістрів тимчасових інтервальних ознак. Мультиплексор другої максимальної границі 22 забезпечує під керуванням сигналів, що надходять з блока управління виконуючого модуля, передачу на другий інформаційний вхід додавачавіднімача максимальної границі: під час виконання операцій множення або ділення результату, що надходить з блока множення-ділення; під час виконання операції присвоєння - максимальної границі другого операнда, що надходить з третього виходу блока регістрів тимчасових інтервальних ознак; під час виконання операції додавання - максимальної границі другого операнда, що надходить з четвертого виходу блока регістрів тимчасових інтервальних ознак; під час виконання операції віднімання - максимальної границі першого операнда, що надходить з другого виходу блока регістрів тимчасових інтервальних ознак; під час виконання операції порівняння - мінімальної границі другого операнда, що надходить з третього виходу блока регістрів тимчасових інтервальних ознак. Додавач адреси 23 забезпечує обчислення необхідної адреси даних, які доступні через зовнішню шину. Перший елемент АБО 24 забезпечує на підставі сигналів "Присвоєння" та "Порівняння", що надходять відповідно з першого та другого виходів дешифратора команд, формування сигналу "Присвоєння або Порівняння", що надходить на вхід першого елемента НІ. Другий елемент АБО 25 забезпечує на підставі сигналів: "Інтервально коректне присвоєння", що надходить з виходу першого елемента І; "Інтервально коректне порівняння", що надходить з виходу другого елемента І; "Інтервально неконтрольована операція", що надходить з виходу першого елемента НІ, формування ознаки інтервальної коректності результату, що надходить на другий інформаційний вхід регістру ознак. Третій елемент АБО 26 забезпечує формування на підставі ознак «>0», що надходять з ознакових виходів додавачів-віднімачів мінімальної та максимальної границь, сигналу "Інтервали не перетинаються", що передається на вхід другого елемента НІ. 19 Четвертий елемент АБО 27 забезпечує керування записом даних до регістру максимальної границі. При цьому запис даних дозволяється при надходженні на перший вхід керуючого сигналу з блока управління виконуючого модуля, що дозволяє занести до регістру максимальної границі перший результат, або у випадку, коли черговий результат більший за число, що зберігається у регістрі максимальної границі. При цьому більше з чисел визначається додавачем-віднімачем максимальної границі. П'ятий елемент АБО 28 забезпечує керування записом даних до регістру мінімальної границі. При цьому запис даних дозволяється при надходженні на перший вхід керуючого сигналу з блока управління виконуючого модуля, що дозволяє занести до регістру мінімальної границі або перший результат, або результат, менший за число, що зберігається у регістрі мінімальної границі. При цьому менше з чисел визначається додавачемвіднімачем мінімальної границі. Перший елемент І 29 забезпечує на підставі сигналу «Присвоєння», що надходить з дешифратора команд та ознак « 0», що надходять з відповідних виходів додавачів-віднімачів мінімальної та максимальної границь, сигналу «Інтервальнокоректне присвоєння», що передається на третій вхід другого елемента АБО. Другий елемент І 30 забезпечує на підставі сигналу «Інтервали перетинаються», що формується другим елементом НІ, та сигналу «Порівняння», що надходить з другого виходу дешифратора команд, формування сигналу «Інтервально-коректне порівняння», що надходить на другий вхід другого елемента АБО. Перший елемент НІ 31 забезпечує на підставі сигналу «Присвоєння або порівняння», що надходить з виходу першого елемента АБО, формування сигналу «Інтервально-неконтрольована операція», що передається на перший вхід другого елемента АБО. Другий елемент НІ 32 забезпечує на підставі сигналу «Інтервали не перетинаються», що надходить з виходу третього елемента АБО, формування сигналу «Інтервали не перетинаються», що передається на другий вхід другого елемента І. Перша шина даних 33 забезпечує обмін даними між блоком управління шиною, виходом додавача адреси , першим вхід-виходом блока комунікаційних регістрів та першим входом додавача адреси. Друга шина даних 34 забезпечує обмін даними між додавачем-віднімачем мінімальної границі, додавачем-віднімачем максимальної границі, регістром ознак, арифметико-логічного пристроєм та блоками черги інструкцій, комунікаційних регістрів, регістрів загального призначення, тимчасових регістрів, регістрів тимчасових інтервальних ознак, регістром мінімальної границі, регістром максимальної границі. Зовнішня шина 35 призначена для інформаційного обміну між процесором та зовнішніми елементами. Процесор функціонує у двох режимах: 90315 20 1) нормальне функціонування (без збоїв та відмов); 2) функціонування з виявленням інтервальних дефектів. У першому режимі процесор з інтервальним контролем працює таким чином: У відповідності із станом черги інструкцій 11, де зберігається кілька інструкцій, необхідних до виконання, до блока управління виконуючого модуля 10 надходить перша з черги інструкція. Поповнення черги інструкцій здійснюється блоком управління шиною 12, яка через зовнішню шину 35 читає дані, адреси яких формуються додавачем адреси 23 на підставі інформації, що зберігається у блоці комунікаційних регістрів 3. Блок управління виконуючого модуля 10 формує сигнали, що керують записом та читанням даних з блока регістрів загального призначення 1, блока тимчасових регістрів 2, а також виконанням поточної інструкції арифметико-логічним пристроєм 6. Результат виконання інструкції через другу шину даних 34 надходить до блока регістрів загального призначення 1. Ознаки результату: переповнення, парність тощо заносяться до регістру ознак результату 14. Результати виконання інструкцій, що зберігаються у блоці регістрів загального призначення 1 можуть через другу шину даних 34 надійти до блока тимчасових регістрів 2 або блока комунікаційних регістрів 3. Адреси кодового сегменту, сегменту даних, стекового сегменту, зовнішнього сегменту, адреса поточної інструкції зберігаються у блоці комунікаційних регістрів 3. Адреси операндів та наступних інструкцій формуються додавачем адрес 23 на підставі даних, що зберігаються у блоці комунікаційних регістрів 3. У другому режимі процесор з інтервальнним контролем працює таким чином: Регістр ознак результату 14 має зарезервовані біти: 15, 14, 13, 12 та 5, 3, 1. Ознака інтервальної коректності обчислювального процесу, заноситься у третій біт. При роботі процесора в першому режимі ця ознака не формуються і не контролюється. Зміст регістрів стану може бути збережений у пам'яті даних. Це дозволяє відновити стан процесор після оброблення переривань та викликів програмних функцій. Робота арифметико-логічного пристрою 6, завантаження інструкцій та даних виконується тим самим чином, що і в першому режимі, але паралельно з роботою арифметико-логічного пристрою 6, виконується інтервальний контроль коректності обчислювального процесу. При роботі в цьому режимі дані мають значно більший розмір через наявність їх інтервальних границь. У зв'язку з цим основні (чисельні) дані через другу шину даних 34 надходять, як і в попередньому випадку до блока регістрів загального призначення 1, а границі їх інтервалів до блока регістрів інтервальних даних 4. Одразу після надходження основних даних, а також їх інтервальних, ознак блок управління виконуючого модуля 10 формує відповідні сигнали до: арифметикологічного пристрою 6; дешифратора команд 13; 21 блока регістрів тимчасових інтервальних ознак 5; мультиплексора границь першого операнда 17, мультиплексора границь другого операнда 18, мультиплексора першої мінімальної границі 19, мультиплексора другої мінімальної границі 20, мультиплексора першої максимальної границі 21, мультиплексора другої максимальної границі 22; блока множення-ділення 9; додавача-віднімача мінімальної границі 7; додавача-віднімача максимальної границі 8. Реалізація інтервального контролю обчислювального процесу здійснюється завдяки контролю інтервалів операндів операцій присвоєння та порівняння, а також обчисленню інтервалів результатів інших арифметичних операцій. Для цього доцільно інтервальний контроль розглянути окремо для п'яти груп команд: множення та ділення; присвоєння; додавання; віднімання; порівняння. При виконанні цих груп команд мультиплексор першої мінімальної границі 19, мультиплексор другої мінімальної границі 20, мультиплексор першої максимальної границі 21, мультиплексор другої максимальної границі 22, що керуються сигналами з блока управління виконуючого модуля 10, на свої інформаційні виходи передають дані відповідно з першого, другого, третього, четвертого та п'ятого інформаційних входів. Під час виконання операцій множення та ділення інтервальний контроль не здійснюється, а границі результату обчислюються на підставі границь інтервалів операндів за формулами з таблиці 1: *min:=min (Amin*Bmin, Amin*Bmax, Amax*Bmin, Amax*Bmax) *max:=max (Amin*Bmin, Amin*Bmax, Amax*Bmin, Amax*Bmax) /min:=min (Amin/Bmin, Amin/Bmax, Amax/Bmin, Amax/Bmax) /max:=max (Amin/Bmin, Amin/Bmax, Amax/Bmin, Amax/Bmax) Для визначення мінімального та максимального значення з усіх комбінацій границь операндів на перший та другий входи мультиплексора границь першого операнду 17 відповідно з першого та другого виходів блока регістрів тимчасових інтервальних ознак 5 надходять мінімальна та максимальна границі першого операнду, а на перший та другий входи мультиплексора границь другого операнду 20 відповідно з третього та четвертого виходів блока регістрів тимчасових інтервальних ознак 5 надходять мінімальна та максимальна границі другого операнду. Під керуванням сигналів, що надходять з блока управління виконуючого модуля 10 на виходах мультиплексорів границь першого 17 та другого 18 операндів почергово з'являються всі чотири комбінації границь операндів, які передаються на вхід блока множення-ділення 9. Під керуванням сигналу з блока управління виконуючого модуля 10, що надходить через п'ятий 28 та четвертий 27 елементи АБО на керуючі входи регістрів мінімальної 15 та максимальної 16 границь, перший результат, отриманий блоком множенняділення 9, заноситься до регістрів мінімальної 15 та максимальної 16 границь, виходи яких з'єднані з першими інформаційними входами мультиплексо 90315 22 ра першої мінімальної границі 19 та мультиплексора першої максимальної границі 21. Другий, третій та четвертий результати з виходу блока множення-ділення 9 через перші інформаційні входи мультиплексора другої мінімальної границі 20 та мультиплексора другої максимальної границі 22 надходять до других входів відповідно першого 7 та другого 8 додавачів-віднімачів, на перші інформаційні входи яких через третій 19 та п'ятий 21 мультиплексори в цей час надходять дані відповідно з регістрів мінімальної 15 та максимальної 16 границь. Перший додавач-віднімач 7 обчислює різницю між черговим результатом, що надходить з блока множення-ділення 9 через четвертий мультиплексор 20 на другий вхід другого додавача-віднімача 8, та даними, що зберігаються у регістрі мінімальної границі 15 та надходять через третій мультиплексор 19. У випадку, якщо черговий результат з блока множення-ділення 9 менше за результат, що зберігається у регістрі мінімальної границі 17 першим додавачем-віднімачем 7 на першому ознаковому виході формується ознака «0», що надходить на перший вхід четвертого елемента АБО 27, вихід якого з'єднаний з керуючим входом регістра максимальної границі 16, що дозволяє занести до регістру максимальної границі 16 нове значення. Таким чином після обчислення всіх чотирьох варіантів множення або ділення у регістрі мінімальної границі 15 та регістрі максимальної границі 16 будуть зберігатися потрібні дані, що через другу шину даних 34 можуть бути переслані до блока регістрів інтервальних даних 4 чи до зовнішньої шини 35. Під час здійснення операцій присвоєння, яку умовно можливо позначити як А:=В визначається її інтервальна коректність, тобто перевіряється умова: Amin Bmin&Amax Bmax. Для перевірки першої частини умови інтервальної коректності операції «присвоєння» на перший вхід першого додавачавіднімача 7, через третій мультиплексор 19 подається мінімальна границя першого операнду, яка надходить з першого інформаційного виходу блока регістрів тимчасових інтервальних ознак 5, а на другий вхід першого додавача-віднімача 7 через четвертий мультиплексор 20 подається мінімальна границя другого операнду, яка надходить з третього інформаційного виходу блока регістрів тимчасових інтервальних ознак 5. Для перевірки другої частини умови інтервальної коректності операції 23 присвоєння на перший вхід другого додавачавіднімача 8, через п’ятий мультиплексор 21 подається максимальна границя другого операнду, яка надходить з четвертого інформаційного виходу блока регістрів тимчасових інтервальних ознак 5, а на другий вхід другого додавача-віднімача 8 через шостий мультиплексор 22 подається максимальна границя першого операнду, яка надходить з другого інформаційного виходу блока регістрів тимчасових інтервальних ознак 5. Ознакою інтервальної коректності операції «присвоєння» є наявність двох ознак « 0», що надходять з відповідних ознакових виходів першого 7 та другого 8 додавачів-віднімачів на перший та другий входи першого елемента І 29, на третій вхід якого з четвертого виходу дешифратора команд 13 надходить сигнал «Присвоєння», що дозволяє сформувати на виході першого елемента І 29 сигнал «Інтервально коректне присвоєння». Вихід першого елемента І 29 з'єднаний з першим входом першого елемента АБО 24, який формує значення третього біту інтервальної коректності у регістрі ознак 14. Під час виконання операції «додавання» контроль інтервалів не здійснюється, а мінімальна та максимальна границі результату обчислюються за формулами з таблиці 1: +min:=Amin+Bmin +max:=Amax+Bmax Для обчислення мінімальної границі результату на перший вхід першого додавача-віднімача 7, дані про мінімальну границю першого операнда надходять з виходу третього мультиплексора 19, третій вхід якого з'єднаний з першим інформаційним виходом блока регістрів тимчасових інтервальних ознак 5. На другий вхід першого додавачавіднімача 7 дані про мінімальну границю другого операнду надходять з вихода четвертого мультиплексора 20, третій вхід якого з'єднаний з третім інформаційним виходом блока регістрів тимчасових інтервальних ознак 5. Перший додавачвіднімач 7, під керуванням сигналу, що надходить з блока управління виконуючого модуля 10 формує мінімальну границю результату як суму мінімальних границь операндів. Цей результат з інформаційного вихода першого додавача-віднімача 7 через другу шину даних 34 може бути пересланий до блока регістрів інтервальних даних 4, або через блок комунікаційних регістрів 3 до зовнішньої шини 35. Для обчислення максимальної границі результату на перший вхід другого додавача-віднімача 8, дані про максимальну границю першого операнда надходять з вихода п'ятого мультиплексора 21, третій вхід якого з'єднаний з другим інформаційним виходом блока регістрів тимчасових інтервальних ознак 5. На другий вхід другого додавачавіднімача 8 дані про максимальну границю другого операнду надходять з вихода шостого мультиплексора 22, третій вхід якого з'єднаний з четвертим інформаційним виходом блока регістрів тимчасових інтервальних ознак 5. Другий додавач-віднімач 8, під керуванням сигналу, що надходить з блока управління виконуючого модуля 10 формує максимальну границю результату як суму максималь 90315 24 них границь операндів. Цей результат з інформаційного вихода другого додавача-віднімача 8 через другу шину даних 34 може бути пересланий до блока регістрів інтервальних даних 4, або через блок комунікаційних регістрів 3 до зовнішньої шини 35. Під час виконання операції «віднімання» контроль інтервалів не здійснюється, а мінімальна та максимальна границі результату обчислюються за формулами з таблиці 1: -min:=Amin-Bmax -max:=Amax-Bmin Для обчислення мінімальної границі результату «віднімання» на перший вхід першого додавача-віднімача 7, дані про максимальну границю другого операнда надходять з виходу третього мультиплексора 19, четвертий вхід якого з'єднаний з четвертим інформаційним виходом блока регістрів тимчасових інтервальних ознак 5. На другий вхід першого додавача-віднімача 7 дані про мінімальну границю першого операнду надходять з виходу четвертого мультиплексора 20, четвертий вхід якого з'єднаний з першим інформаційним виходом блока регістрів тимчасових інтервальних ознак 5. Перший додавач-віднімач 7, під керуванням сигналу, що надходить з блока управління виконуючого модуля 10 формує мінімальну границю результату як різницю мінімальних границь операндів. Цей результат з інформаційного виходу першого додавача-віднімача 7 через другу шину даних 34 може бути пересланий до блока регістрів інтервальних даних 4, або через блок комунікаційних регістрів 3 до зовнішньої шини 35. Для обчислення максимальної границі результату «віднімання» на перший вхід другого додавача-віднімача 8, дані про мінімальну границю другого операнда надходять з вихода п'ятого мультиплексора 21, четвертий вхід якого з'єднаний з третім інформаційним виходом блока регістрів тимчасових інтервальних ознак 5. На другий вхід другого додавача-віднімача 8 дані про максимальну границю першого операнду надходять з вихода шостого мультиплексора 22, четвертий вхід якого з'єднаний з другим інформаційним виходом блока регістрів тимчасових інтервальних ознак 5. Другий додавач-віднімач 8, під керуванням сигналу, що надходить з блока управління виконуючого модуля 10 формує максимальну границю результату як разність максимальної границі першого операнда та мінімальної границі другого операнда. Цей результат з інформаційного вихода другого додавача-віднімача 8 через другу шину даних 34 може бути пересланий до блока регістрів інтервальних даних 4, або через блок комунікаційних регістрів 3 до зовнішньої шини 35. Під час виконання операцій «порівняння» мінімальна та максимальна границі результату не обчислюються, контролюється тільки умова інтервальної коректності з таблиці 1: Amin Bmax Amax Bmin . Виконання цієї умови гарантує, що інтервали операндів перетинаються, а результат операції може набувати значень як 0 так і 1. В іншому випадку результат 25 операції не буде змінюватися, що свідчитиме про інтервальну помилку даних, або умови. Для обчислення першої частини умови інтервальної коректності операції «порівняння» Аmin>Вmах на перший вхід першого додавачавіднімача 7, дані про максимальну границю другого операнда надходять з виходу третього мультиплексора 19, п'ятий вхід якого з'єднаний з четвертим інформаційним виходом блока регістрів тимчасових інтервальних ознак 5. На другий вхід першого додавача-віднімача 7 дані про мінімальну границю першого операнду надходять з виходу четвертого мультиплексора 20, п'ятий вхід якого з'єднаний з першим інформаційним виходом блока регістрів тимчасових інтервальних ознак 5. Перший додавач-віднімач, під керуванням сигналу, що надходить з блока управління виконуючого модуля 10 формує разність між мінімальною границею першого операнда та максимальною границею другого операнда. Для обчислення другої частини умови інтервальної коректності операції «порівняння» Аmax0», що дозволяє сформувати на виході п'ятого елемента АБО 28 сигнал «Інтервали не перетинаються», який подається на вхід другого елемента НІ 32, що формує сигнал «Інтервали перетинаються», що надходить на перший вхід другого елемента І 30, на другий вхід якого подається з п'ятого виходу дешифратора команд 13 сигнала «Порівняння». Таким чином, на виході другого елемента І 30 формується сигнал «Інтервально коректне порівняння», що передається на другий вхід першого елемента АБО 24. Другий елемент АБО 25, завдяки сигналам «Порівняння» та «Присвоєння», що надходять з виходу дешифратора команд 13, формує на своєму виході сигнал «Присвоєння або порівняння», що надходить на вхід першого елемента НІ 31 та забезпечує на своєму виході логічну одиницю під час виконання операцій, які не є «присвоєнням» або «порівнянням». Вихід першого елемента НІ 31 з'єднано з третім входом першого елемента АБО 24, на виході якого під час виконання інтервальнокоректних операцій «присвоєння» або «порівнян 90315 26 ня», або інших операцій, що не контролюються інтервально, формується логічна «1», що заноситься до третього біту регістра ознак 14, у інших випадках до третього біту регістру ознак 14 заноситься логічний «0». Наявність біту інтервальної коректності у регістрі ознак результату 14 надає можливість створити у процесорі з інтервальним контролем додаткове джерело внутрішніх переривань, які мають окремий вектор та пріоритет. Відповідний біт режиму переривань регістру ознак результату 14 дозволяє чи забороняє переривання. Замасковані переривання ігноруються. У разі появи "інтервального" переривання процесор зберігає стан обчислювального процесу і розпочинає обробку. Реалізація інтервального контролю у процесорі шляхом фіксації інтервальних некоректностей обчислювального процесу, надає змогу виявляти програмні дефекти та апаратні збої, як під час розробки та верифікації програмного забезпечення, так і безпосередньо при використанні за призначенням. Визначимо техніко-економічну ефективність запропонованого винаходу. Ефективність інтервального контролю з виявлення програмних дефектів можливо визначити за допомогою моделі, проданої на Фіг.2, що визначає можливі стани інтервального аналізу та перехідні ймовірності. При виконанні інтервального аналізу множина всіх команд поділена на дві множини. До першої множини А віднесено арифметичні та логічні команди. Коректність цих команд можливо контролювати за допомогою інтервального аналізу. До другої множину віднесено інші команди, які неможливо контролювати інтервальним аналізом. Передбачається, що частка арифметико-логічних команд є PAL, а частка інших команд PV, a PAL+РV=1. Інтервальний аналіз обчислювального процесу розглядається як сукупність переходів між станами. Початковим станом є С - стан команди, які з ймовіріністю PAL належать до арифметичних або логічних, що переводить систему до стану А, а з ймовірністю 1-PAL, належать до іншої множини V, що переводить систему до стану V. В стані А можливі два варіанти: наявність або відсутність програмного дефекту команди. Ймовірність дефекту команди позначено PDC. Ймовірність командного дефекту розпізнається безумовно, що позначено станом F. Далі процес повертається до початкового стану С. У випадку виконання арифметичної команди та відсутності командного дефекту з ймовірністю 1-PDC процес послідовно переходить у стани А1 аналіз першого операнду, та А2 - аналіз другого операнду, які можуть мати дефекти з ймовірністю PDC, що призводить до переходу у стан Т. У випадку коректності обох операндів, процес повертається у початковий стан С. У стані Т, що відповідає наявності дефектів операндів, у випадку збігу інтервальних границь, що має ймовірність Рі, інтервальне розпізнавання дефектів неможливе, тому здійснюється перехід до стану F , що відповідає неможливості ідентифікації інтервальних дефектів, 27 90315 у іншому випадку дефект розпізнається, що позначено переходом у стан F. При виконанні команд, що відповідають стану V, командні та операндні дефекти не розпізнаються і здійснюється перехід до стану F . Відсутність дефектів повертає систему до стану С. Визначимо ефективність інтервального контролю як умовну ймовірність ідентифікації інтерваF( t ) льних дефектів за формулою: ( t ) , та F( t ) F( t ) знайдемо границю цього значення як: F(t ) , де під t розуміється lim (t ) lim F(t ) F(t ) t t кількість проаналізованих на інтервальну коректність елементів коду, a F(t), F( t ) - ймовірності розпізнавання та пропуску програмних дефектів за умовою їх існування у програмному коді чи обчислювальному процесі. На підставі потоків ймовірностей складемо систему диференціальних рівнянь Колмогорова (1): dC(t ) dt dA( t ) dt dF( t ) dt dF( t ) dt F(t ) F(t ) A 2 (t )(1 PDO ) C( t )PAL T(t )(1 Pi ) T( t )Pi V2 (t )(1 PDO ) C(t ) Таким чином маємо систему алгебричнодиференціальних рівнянь (2): dA( t ) C( t )PAL A( t ) dt dF( t ) T(t )(1 Pi ) A( t )PDC F( t ) dt dF( t ) dt T( t )Pi V1( t )PDO V2 ( t )PDO dV(t ) C( t )(1 PAL ) V(t ) dt dV1( t ) V( t )(1 PDC ) V1( t ) dt dV2 ( t ) V1( t )(1 PDO ) V2 ( t ) dt dA 1( t ) A( t )(1 PDC ) A1( t ) dt dA 2 ( t ) A 1( t )(1 PDO ) A 2 ( t ) dt dT( t ) A1( t )(1 PDO ) A 2 ( t )PDO dt V( t )PDC F( t ) T( t ) С(t)+F(t)+ F (t)+T(t)+A(t)+A1(t)+A2(t)+V(t)+V1(t)+V A( t ) 2(t)=1, A( t )PDC V1( t )PDO 28 Початковою умовою системи (2) є розподіл ймовірностей на початку: F( t ) V2 ( t )PDO V( t )PDC F( t ) dV(t ) C( t )(1 PAL ) V(t ) dt dV1( t ) V( t )(1 PDC ) V1( t ) dt dV2 ( t ) V1( t )(1 PDO ) V2 ( t ) dt dA 1( t ) A( t )(1 PDC ) A1( t ) dt dA 2 ( t ) A 1( t )(1 PDO ) A 2 ( t ) dt dT( t ) A1( t )(1 PDO ) A 2 ( t )PDO T( t ) dt До яких треба додати умову нормування: С(t)+F(t)+ F (t)+T(t)+A(t)+A1(t)+A2(t)+V(t)+V1(t)+V 2(t)=1, що дозволить відкинути одне з рівнянь системи (1), наприклад (1.1). C(0)=1; F(0)=0; F (0)=0;T(0)=0; A(0)=0; A1(0)=0; A2(0)=0; V(0)=0; V1(0)=0; V2(0)=0 Визначимо граничну ефективність інтервального контролю, коли похідні системи (2) мають нульові значення. Отримаємо систему алгебричних рівнянь (3): CPAL-A=0 (1-Pi)T+APDC-F=0 TPi+V1PDO+V2PDO+VPDC- F =0 (1-PAL)C-V=0 V(1-PDC)-V1=0 V1(1-PDO)-V2=0 A(1-PDC)-A1=0 A1(1-PDO)-A2=0 (1-PDO)A1+A2PDO-T=0 C+F+ F +T+A+A1+A2+V+V1+V2=1, де C, F, F , T, A, A1, A2, V, V1, V2 – відповідні асимптоти (ймовірності знаходження інтервального аналізу у відповідних станах). Після розв'язання системи (3) ефективність інтервального контролю: PAL (1 Pi )(1 P2 )(1 PDC ) PDC DO 2 )(1 P ) (1 P ) (1 P )(2P 2 PAL (1 P DC AL DC DO PDO ) PDC DO За умовою, що PDО=PDC=PD, тобто ймовірності дефектів операндів та операцій збігаються, та поPD 1 PAL значив , маємо. 1 PD PAL PALPDC (1 Pi )(1 P 2 ) DO 2) (1 P (2PD P 2 ) D D Враховуючи низьку інтенсивність дефектів P2 D 0 маємо, що PD , тоді 29 90315 1 Pi P D 1 (3 1)PD Таким чином у випадку PD 0 маємо: 1-Pі, де Pі - ймовірність збігу границь інтервалів. Впровадження запропонованого пристрою забезпечує підвищення достовірності функціонуван1 ня процесора K= , більш ніж на порядок. 1 30 Це надає змогу розширити сферу застосування пристрою на системи підвищеної надійності та безпеки. Зокрема це стосується вбудованих систем, інформаційно-керуючих систем високої достовірності функціонування, систем тестування та незалежної верифікації програмного забезпечення. Таблиця 1 1 Операторне відображення А=В 2 А+В ІА+ІВ І+ Завжди 2 А-В ІА-ІВ І Завжди 3 4 5 6 7 А В АВ А В № 8 А*В Інтервальне відоУмова коректності браження ІВ ІА Amin Bmin&Amax Bmax Amin Bmax ІА*ІВ І* Завжди 9 А/В ІA/ІB І/ Алгебричний запис інтервального відображення Amin:=Bmin Amax:=Bmах +min:=Amin+Bmin +max:=Amax+Bmax -min:=Amin-Bmax -max:=Amax-Bmin Amax Bmin *min:=min(Amin*Bmin, Amax*Bmin, Amax*Bmax) *max:=max(Amin*Bmin, Аmах*Вmin, Amax*Bmax) /min:=min(Amin/Bmin, Аmах/Bmin, Аmах/Bmах) /max:=max(Amin/Bmin; Amax/Bmin, Amax/Bmax) Amin*Bmax, Amin*Bmax, Аmin/Bmax, Amin/Bmax, 31 90315 32 33 Комп’ютерна верстка М. Ломалова 90315 Підписне 34 Тираж 26 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюInterval control processor

Автори англійськоюManzhos Yurii Semenovych, Kharchenko Viacheslav Serhiiovych, Konorev Borys Mykhailovych, Chertkov Heorhii Mykolaiovych

Назва патенту російськоюПроцессор с интервальным контролем