Цифровий пристрій обробки часових сигналів

Формула / Реферат

Пристрій цифрової обробки часових сигналів, що містить АЦП, арифметичний блок згортки, блок керування, який відрізняється тим, що введені оперативний запам'ятовуючий пристрій (ОЗП) знакових розрядів, виконаний у вигляді m зсувних послідовно-паралельних однорозрядних регістрів ΔΝ відліків кожний, причому вхід D першого зсувного послідовно-паралельного однорозрядного регістра ΔΝ відліків з'єднаний з виходом знакового розряду АЦП, входи D інших m-1 зсувних послідовно-паралельних однорозрядних регістрів ΔΝ відліків з'єднані своїм входом D з першим послідовним виходом D попереднього зсувного послідовно-паралельного однорозрядного регістра ΔΝ відліків, синхровходи С регістрів об'єднані і підключені магістраллю керування до відповідного виходу ″Команди″ блока керування, рекурентний вимірювач середнього значення модулів відліків, виконаний у вигляді ОЗП модулів відліків, підключеного входами адреси - А, запис-зчитування - W/R, вибір кристала - Cs магістраллю керування до відповідних виходів ″Команди″ блока керування, тривходового паралельного суматора, з'єднаного першим входом D(+) із входом D ОЗП модулів відліків і підключеного до виходу модуля даних АЦП - |у|, другим входом D(-), з'єднаного з виходом D ОЗП модулів відліків, регістра суми відліків S(n), з'єднаного входом D з виходом D тривходового паралельного суматора, синхровходом С підключеного до відповідного виходу ″Команди″ блока керування, нормуючого помножувача, один вхід D якого з'єднаний з виходом D регістра суми відліків S(n) і підключений до третього входу D(-) тривходового паралельного суматора модулів відліків, а синхровходи С1, С2 магістраллю керування підключені до відповідних виходів ″Команди″ блока керування, а вихід D є виходом рекурентного вимірювача середнього значення модулів відліків, постійного запам'ятовуючого пристрою (ПЗП) нормуючих коефіцієнтів, з'єднаного виходом D із другим нормуючим входом помножувача, входами адреси - А, вибір кристала - Cs магістраллю керування, підключеного до відповідних виходів ″Команди″ блока керування, арифметичний блок згортки, виконаний у вигляді μ ПЗП табличних, часткових, синфазних/квадратурних згорток, входи адреси A(sign) кожного μ-го ПЗП табличної, часткової, синфазної/квадратурної згортки підключені до другого, паралельного виходу D m-го зсувного послідовно-паралельного однорозрядного регістра ΔΝ відліків, входи адреси А(![]() ), А(j), вибір кристала Cs кожного μ-го ПЗП табличної, часткової, синфазної/квадратурної згортки з'єднані з відповідними входами інших μ -1 постійних запам'ятовуючих пристроїв ПЗП табличних, часткових, синфазних/квадратурних згорток і підключені магістраллю даних до відповідних виходів ″Команди″ блока керування, m-входового паралельного суматора, з'єднаного своїми m входами D з m виходами D відповідних ПЗП табличних, часткових, синфазних/квадратурних згорток, а синхровходом С магістраллю керування підключеного до відповідного до виходу ″Команди″ блока керування, помножувача вихідних відліків рекурентного вимірювача середнього значення модуля відліків і m - входового паралельного суматора, вихід D якого підключений до першого входу D помножувача, а до другого входу D підключений вихід D рекурентного вимірювача середнього значення модуля відліків, синхровходи С1, С2 магістраллю керування підключені до відповідних виходів ″Команди″ блока керування, квадратора-суматора, перший і другий входи D якого об'єднані й підключені до виходу D помножувача вихідних відліків рекурентного вимірювача середнього значення модуля відліків і m-входового паралельного суматора, а синхровходи С1, С2, Встановлення 0 магістраллю керування, підключені до відповідних виходів ″Команди″ блока керування, ПЗП табличного обчислення квадратного кореня, з'єднаного входом адреси А з виходом D квадратора-суматора, входом вибір кристала - Cs підключеного до відповідного виходу ″Команди″ блока керування, а вихід D є виходом цифрового пристрою обробки часових сигналів.

), А(j), вибір кристала Cs кожного μ-го ПЗП табличної, часткової, синфазної/квадратурної згортки з'єднані з відповідними входами інших μ -1 постійних запам'ятовуючих пристроїв ПЗП табличних, часткових, синфазних/квадратурних згорток і підключені магістраллю даних до відповідних виходів ″Команди″ блока керування, m-входового паралельного суматора, з'єднаного своїми m входами D з m виходами D відповідних ПЗП табличних, часткових, синфазних/квадратурних згорток, а синхровходом С магістраллю керування підключеного до відповідного до виходу ″Команди″ блока керування, помножувача вихідних відліків рекурентного вимірювача середнього значення модуля відліків і m - входового паралельного суматора, вихід D якого підключений до першого входу D помножувача, а до другого входу D підключений вихід D рекурентного вимірювача середнього значення модуля відліків, синхровходи С1, С2 магістраллю керування підключені до відповідних виходів ″Команди″ блока керування, квадратора-суматора, перший і другий входи D якого об'єднані й підключені до виходу D помножувача вихідних відліків рекурентного вимірювача середнього значення модуля відліків і m-входового паралельного суматора, а синхровходи С1, С2, Встановлення 0 магістраллю керування, підключені до відповідних виходів ″Команди″ блока керування, ПЗП табличного обчислення квадратного кореня, з'єднаного входом адреси А з виходом D квадратора-суматора, входом вибір кристала - Cs підключеного до відповідного виходу ″Команди″ блока керування, а вихід D є виходом цифрового пристрою обробки часових сигналів.

Текст

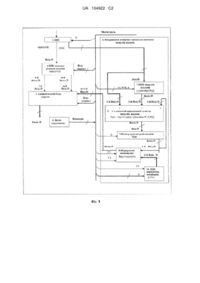

Реферат: Винахід належить до області обробки часових сигналів у цифрових приймальних трактах різного призначення і може бути використане в радіозв'язку, радіолокації, акустиці, гідроакустиці. Пристрій цифрової обробки часових сигналів за рахунок введення оперативно запам’ятовуючого пристрою знакових розрядів, рекурентного вимірювача середнього значення модулів відліків, арифметичного блока згортки, m-входового паралельного суматора, помножувача вхідних відліків рекурентного вимірювача середнього значення модуля відліків і m-входового паралельного суматора досягається підвищення швидкодії при узгодженому прийманні часових сигналів з різними законами модуляції в ковзному часовому вікні. UA 104922 C2 (12) UA 104922 C2 UA 104922 C2 5 Пропоноване технічне рішення належить до області обробки часових сигналів у цифрових приймальних трактах різного призначення і може бути використане в радіозв'язку, радіолокації, акустиці, гідроакустиці. Узгоджене приймання часових сигналів з різними законами модуляції при невідомому часі приходу в суміші із шумовою завадою виконується обчисленням згортки в ковзному часовому вікні [1]. Z,n 1 h, yn 1 ; (1) v 0 де: 10 15 20 25 30 35 h, exp i t , ; y a cos t ; (2) (3) , -v-й часовий відлік фази -й допплерівської копії сигналу; -v-й часовий відлік фази сигналу; a -v-й часовий відлік амплітуди сигналу з амплітудною модуляцією; φ - випадкова фаза; ω - початкова кругова частота; Δt=1 /F - період дискретизації; h, - v-й комплексний часовий відлік -ϊ допплерівської копії сигналу; N=Fd•Τ - число відліків за час тривалості сигналу Τ при частоті дискретизації F; у(ν) = -й часовий відлік дійсного сигналу; ΔL L=2 - число допплерівських копій. У випадку тональних сигналів , = 0 і найкращим методом узгодженої допплерівської обробки в ковзному часовому вікні за критерієм мінімізації обчислень є рекурентний Фур'є аналіз [2]. Відомий пристрій рекурентного обчислення коефіцієнтів спектра Фур'є в ковзному часовому вікні (а.c. СРСР № 560232, МПК G 06 F 17/14, G 01 R 23/16). Пристрій містить аналого-цифровий перетворювач (АЦП), блоки пам'яті, суматори, помножувачі, блок формування синусних та косинусних множників. Вихід АЦП 1 з'єднаний з першим входом першого суматора та входом першого блока пам'яті, вихід якого з'єднаний з першим входом другого суматора, перший вихід блока формування синусних та косинусних множників підключений до перших входів першого та другого помножувачів, а другий підключений до перших входів третього та четвертого помножувачів, другі входи першого та третього, а також другого та четвертого помножувачів з'єднані з першими та другими входами третього та четвертого суматорів відповідно, вихід першого суматора з'єднаний з другим входом другого суматор, підключеного своїм виходом до другого входу першого помножувач, а виходи третього та четвертого суматорів з'єднані з входами другого та третього блоків пам'яті. Пристрій здійснює рекурентне обчислення коефіцієнта спектра Фур'є Ζ( ,n) за формулою (4) на основі теореми про спектр затриманої послідовності {у(n)} - наслідок періодичності комплексних відліків коефіцієнтів матриці дискретного перетворення Фур'є - h,n . 40 Z( ,n) - Z( , n - 1) + (y(n) - y(n - N + 1) h( ,n) ; (4) (5) h( ,n) h( , n N) exp(-i 2 n/); 45 Недоліком пристрою є неможливість узгодженої рекурентної обробки пристроєм згідно з (4) частотно-модульованих (ЧМ) сигналів, що не мають періодичності (5). Модуль згортки |Ζ( ,n)|, згідно (1), при постійній амплітуді інтервалі n-Ν+1-n може бути обчислений приблизно як: Z , n a n 1 h, n 1 , (6) 0 1 UA 104922 C2 де a n yn 1 Yn ; Yn (7) 1 yn 1 ; (8) 0 (9) n 1 cosn 1 ; n 1 n 1 t n 1 ; (10) 1 h, n 1 z,n ; (11) 0 З урахуванням (6)-(11) можна наближено представити Z, n з (6) у вигляді 5 Z,n ,n an z,n ; (12) Z, n у вигляді добутку амплітудного - а(п) та модуля фазового помножувачів веде до фазової [4] обробки сигналів (13) Подання Z,n ,n z,n ; z, n (13) 10 та некогерентної [5] обробки сигналів (14). Z , n , n 1 Y n ; 15 20 25 30 35 40 (14) Відомий некогерентний виявляч сигналів у шумах включає формувач синфазного й квадратурного сигналів (в описі: перший і другий змішувачі, перші входи яких об'єднані й підключені до джерела сигналу, гетеродин, перший вихід якого через фазозсувний ланцюжок з'єднаний із другим входом першого змішувача, другий вихід з'єднаний із другим входом другого змішувача, перший і другий фільтри проміжної частоти, з'єднані входами з виходами першого і другого фільтрів проміжної частоти відповідно), аналого-цифровий перетворювач (АЦП), пристрій керування (в описі: перший та другий компаратори напруг, не інвертуючий вхід першого компаратора напруг об'єднаний з входом АЦП і підключений до виходу одного з фільтрів проміжної частоти, неінвертуючий вхід другого компаратора напруг підключений до виходу другого фільтра проміжної частоти, а інвертуючі входи з'єднані з нульовим потенціалом, логічна схема виключне АБО, з'єднана першим і другим входами з виходами компараторів напруг, лічильник-подільник на 2•N, з'єднаний входом з тактовим входом АЦП і виходом логічної схеми виключне АБО), накопичувальний суматор, підключений входом шиною до виходів розрядів квантування рівня АЦП, компаратор кодів, підключений першим входом до виходу накопичувального суматора, регістр коду порогу, вихід якого з'єднаний з другим входом компаратор кодів (патент РФ № 2199762, МПК G 01 S 7/28). Некогерентний виявляч сигналів має такі недоліки: - при малих відношеннях сигнал/завада - a/σ на вході некогерентний приймач програє багаторозрядним і знаковим кореляторам відносно завадостійкості, - через втрату інформації про фазову структуру відсутній ефект стискання ЧМ сигналів, що визначає точність виміру дальності в імпульсних локаційних системах. Типова структура фазового виявляча (знакового корелятора) для відомої затримки приходу сигналу наведена в [6]. Знаковий корелятор містить смуговий фільтр, обмежувач, включені послідовно, перемножувач, з'єднаний першим входом з виходом обмежувача, другим входом з генератором копії сигналу, пороговий пристрій, з'єднаний першим входом з виходом інтегратора, а другим входом з датчиком опорного рівня. Недоліки фазового виявляча, наведеного в [6]: - нелінійна внаслідок жорсткого обмеження амплітудна характеристика; 2 UA 104922 C2 5 10 15 20 25 - при невідомій затримці приходу сигналу повинна бути забезпечена багатоканальність по часових затримках шляхом розпаралелювання пристроїв обробки (помножувачів, інтеграторів) і генераторів копій. Найбільш близьким за призначенням, використанням амплітудної та фазової інформації із можливістю обробки сигналів з різними законами модуляції є цифровий фільтр (а. с СРСР № 443458, МПК Η 03 Η 7/02, Η 03 Η 7/28). Цифровий фільтр містить аналого-цифровий перетворювач (АЦП), арифметичний пристрій згортки (в описі помножувач квантованих відліків сигналів на вагові коефіцієнти, підключений першим входом до виходу АЦП, ОЗП вагових коефіцієнтів, підключений виходом до другого входу першого помножувача, перший і другий квадратурні канали в складі помножувачів відліків на коефіцієнти копії сигналу, накопичувального суматора, з'єднаного входом з виходом помножувача свого квадратурного каналу, перші входи помножувачів об'єднані і підключені до виходу помножувача квантованих відліків сигналів на вагові коефіцієнти, другий вхід помножувача першого квадратурного каналу з'єднаний з виходом формувача відліків синфазної копії, і другий вхід помножувачів другого квадратурного каналу - з виходом формувача відліків квадратурної копії, об'єднувач квадратурних каналів), пристрій керування (в описі генератор тактових імпульсів, реверсивний лічильник, з'єднаний входом з виходом генератора тактових імпульсів). Недоліки пристрою: - цифровий фільтр-прототип не містить буферного запам'ятовуючого пристрою на N відліків сигналу; - реалізує пряме обчислення згортки реалізації N відліків з копією згідно (1) і потребує Q 4•N арифметичних операцій множення-додавання на один вихідний відлік |Z(n)| і при великих значеннях N, Fd висуває високі вимоги до швидкодії цифрових пристроїв; - при невідомій затримці приходу сигналу і у відсутності буферного запам'ятовуючого пристрою багатоканальність по часових затримках повинна бути забезпечена шляхом розпаралелювання пристроїв обробки (помножувачів, інтеграторів) і генераторів копій сигналу. Оцінка середнього значення амплітуди може бути отримана рекурентною процедурою a n yn 1 1 yn 1 1 Yn 1 Yn 1 yn yn 1 ; (15) 0 30 Оскільки основна фазова інформація міститься в статистиці перетинань нульового рівня функцією η(n), можна обмежитися в (10) одно розрядним квантуваннямфази ψ на два рівні - 0, π шляхом жорсткого обмеження вхідного сигналу у (n) [4]. 1 x 0; n 1 0 n 1 signyn 1 ; signyx 0 x 0; (16) 1 x 0; 1 h, 0 n 1 z0 ,n ; (17) 0 35 З урахуванням (15)-(17) можна представити Z, n у вигляді Z , n , n an zo, n ; Знакова згортка - zo ,n N одно розрядних відліків - ηο(η-Ν+1+ν) з багаторозрядною копією h ,n може бути представлена як сума m часткових знакових згорток zo, ,n 40 zo,n zo, ,n, 1, m; o,L ; (18) zo, ,n h, 1 1 on 1 1 , 0, 1 ; (19) ΔΝ Послідовність ΔΝ одно розрядних відліків (ηο(μ•ΔΝ+Δν)} може приймати 2 значень. Множення кожного одно розрядного відліку ηο (μ•ΔΝ+Δν) на постійний коефіцієнт 3 UA 104922 C2 h, 1 1 перетворює множину 2 одно розрядних відліків { ηο [n-(μ -1)•ΔΝ+1+Δν]} у ΔΝ множину 2 багато розрядних відліків h, 1 1 on 1 1 . Кожній реалізації ΔΝ багато розрядних відліків h, n 1 ΔΝ підсумовування по Δν з (19) ставить у відповідність одне число і, таким чином, 2 реалізаціям ΔN ΔΝ багато розрядних відліків відповідають 2 значень zo, ,n , які можуть бути розраховані заздалегідь і записані в постійний запам'ятовуючий пристрій для подальших табличних обчислень. В основу пропонованого винаходу поставлено задачу підвищення швидкодії при узгодженому прийманні часових сигналів з різними законами модуляції в ковзному часовому вікні. Підвищення швидкодії пропонованого цифрового пристрою обробки часових сигналів за рахунок скорочення кількості операцій ґрунтується на можливості наближеного зображення вихідного сигналу пристрою у вигляді добутку "амплітудного" і "фазового" множників, розділенням і паралельною, некогерентною амплітудною обробкою, що виконується рекурентно та когерентною фазовою обробкою, здійснюється табличною знаковою згорткою. Поставлена задача розв'язується тим, що у відомий пристрій цифрової обробки часових сигналів, що містить АЦП, арифметичний блок згортки, блок керування, згідно з винаходом, введені оперативний запам'ятовуючий пристрій (ОЗП) знакових розрядів, виконаний у вигляді m зсувних послідовно-паралельних однорозрядних регістрів ΔΝ відліків кожний, причому вхід D першого зсувного послідовно-паралельного одно розрядного регістру ΔΝ відліків з'єднаний з виходом знакового розряду АЦП, входи D інших m-1 зсувних послідовно-паралельних однорозрядних регістрів ΔΝ відліків з'єднані своїм входом D з першим послідовним виходом D попереднього зсувного послідовно-паралельного одно розрядного регістру ΔΝ відліків, синхровходи С регістрів об'єднані і підключені магістраллю керування до відповідного виходу Команди блока керування, рекурентний вимірник середнього значення модулів відліків, виконаний у вигляді ОЗП модулів відліків, підключеного входами адреси - А, запис-зчитування - W/R, вибір кристала - Cs магістраллю керування до відповідних виходів Команди блока керування, три входового паралельного суматора, з'єднаного першим входом D(+) із входом D ОЗП модулів відліків і підключеного до виходу модуля даних АЦП - |у|, другим входом D(-), з'єднаного з виходом D ОЗП модулів відліків, регістру суми відліків S(n), з'єднаного входом D з виходом D три входового паралельного суматора, синхровходом С підключеного до відповідного виходу Команди блоку керування, нормуючого помножувача, один вхід D якого з'єднаний з виходом D регістру суми відліків S(n) і підключений до третього входу D (-) три входового паралельного суматора модулів відліків, а синхровходи С1, С2 магістраллю керування підключені до відповідних виходів Команди блока керування, а вихід D є виходом рекурентного вимірника середнього значення модулів відліків, постійного запам'ятовуючого пристрою (ПЗП) нормуючих коефіцієнтів, з'єднаного виходом D із другим нормуючим входом помножувача, входами адреси - А, вибір кристала - Cs магістраллю керування, підключеного до відповідних виходів Команди блока керування, а арифметичний блок згортки виконаний у вигляді m ПЗП табличних, часткових, синфазних/квадратурних згорток, входи адреси A(sign) кожного μ-го ПЗП табличної, часткової, синфазної/квадратурної, згортки підключені до другого, паралельному виходу D μ-го зсувного послідовно-паралельного одно розрядного регістру ΔΝ відліків, входи адреси Α( ), A(j). Вибір кристала Cs кожного μ-го ПЗП табличної, часткової, синфазної/квадратурної, згортки з'єднані з відповідними входами інших m-1 постійних запам'ятовуючих пристроїв ПЗП табличних, часткових, синфазних/квадратурних згорток і підключені магістраллю даних до відповідних виходів Команди блоку керування, т-входового паралельного суматора, з'єднаного своїми m входами D з m виходами D відповідних ПЗП табличних, часткових, синфазних/квадратурних згорток, а синхровходом С магістраллю керування підключеного до відповідного до виходу Команди блоку керування, помножувача вихідних відліків рекурентного вимірника середнього значення модуля відліків і m - входового паралельного суматора, вихід D якого підключений до першого входу D помножувача, а до другого входу D підключений вихід D рекурентного вимірника середнього значення модуля відліків, синхровходи С1, С2 магістраллю керування підключені до відповідних виходів Команди блока керування, квадратора-суматора, перший і другий входи D якого об'єднані й підключені до виходу D помножувача вихідних відліків рекурентного вимірника середнього значення модуля відліків і m - входового паралельного суматора, а синхровходи С1, С2, Установка 0 магістраллю керування підключені до відповідних виходів Команди блока керування, ПЗП табличного обчислення квадратного кореня, з'єднаного адресним входом А с виходом D квадратора - суматора, входом вибір кристала - Cs ΔΝ 5 10 15 20 25 30 35 40 45 50 55 4 UA 104922 C2 5 10 15 20 25 30 35 40 45 50 55 60 підключеного до відповідного виходу Команди блока керування, а вихід D є виходом цифрового пристрою обробки часових сигналів. Винахід ілюструється наступними графічними матеріалами: на фіг. 1 представлена структура цифрового пристрою обробки часових сигналів; на фіг. 2 представлена структура ОЗП знакових розрядів; на Фіг.3 представлена структура арифметичного блока згортки; на Фіг.4 представлена структура адреси А ПЗП табличної, часткової згортки, де A(sign)- часткова послідовність ΔΝ знакових відліків, А( ) - номер допплерівської згортки, А(k) - ознака згортки: k=0 - синфазна, k=1 квадратурна згортка; на Фіг. 5 представлена часова діаграма табличного формування відліку знакової згортки арифметичним блоком згортки, де Тд - період дискретизації, Fi - синхроімпульс у момент часу Δΐΐ періоду дискретизації Тд; на Фіг.6 представлені: безперервною товстою лінією u(1, ν) - часовий відрізок реалізації ЛЧМ сигналу з девіацієй частоти Df=800 Гц, безперервною тонкою лінією ζ(1, ν) - часовий відрізок реалізації суміші ЛЧМ сигналу на вході й некорельованої нормальної завади смутою DF=1кГц при вхідному відношенні сигнал / завада - q = авх /σ =1, тонкою лінією "меандр" s(1, ν) -часовий відрізок реалізації жорстко обмеженої (кліпованої) суміші ЛЧМ сигналу і некорельованої нормальної завади ζ(1, ν); на фіг. 7 представлені: безперервною тонкою лінією ζ(1, ν) - часовий відрізок реалізації суміші ЛЧМ сигналу і некорельованої нормальної завади смугою DF=1кГц при вхідному відношенні сигнал/завада - q = авх/σ =1, пунктирною лінією -b(1, ν) - часовий відрізок реалізації модуля суміші ЛЧМ сигналу і некорельованої нормальної завади; на Фіг. 8-9 представлені: безперервною тонкою лінією Z(q, j) - часовий відрізок реалізації вихідного сигналу цифрового пристрою обробки прототипу, безперервною товстою лінією E(q, j) - часовий відрізок реалізації вихідного сигналу цифрового пристрою з роздільною частотно-часовою обробкою при вхідному відношенні сигнал/завада - q = авх (q) / σ = 1; 0.5 суміші ЛЧМ сигналу і некорельованої нормальної завади – ζ(q, ν). Тривалість оброблюваного ЛЧМ сигналу -. τ = 0.5 с. Пристрій цифрової обробки часових сигналів містить: АЦП 1, арифметичний блок згортки 2, блок керування 3. В пристрій цифрової обробки часових сигналів уведені оперативний запам'ятовуючий пристрій (ОЗП) знакових розрядів 4, виконаний у вигляді m зсувних послідовно-паралельних одно розрядних регістрів ΔΝ відліків 5, причому вхід D першого зсувного послідовно-паралельного одно розрядного регістру ΔΝ відліків 5 з'єднаний з виходом знакового розряду АЦП 1, входи D інших m-1 зсувних послідовно-паралельних одно розрядних регістрів ΔΝ відліків 5 з'єднані своїм входом D з першим, послідовним виходом D попереднього зсувного послідовно-паралельного одно розрядного регістру ΔΝ відліків 5, синхровходи С регістрів 5 об'єднані і підключені магістраллю керування до відповідного виходу Команди блока керування 3, введений рекурентний вимірник середнього значення модулів відліків 6, виконаний у вигляді ОЗП модулів відліків 7, підключеного входами адреси - А, запис-зчитування -W/R, вибір кристала -Cs магістраллю керування до відповідних виходів Команди блока керування 3, тривходового паралельного суматора 8, з'єднаного 1-м входом D(+) із входом D ОЗП модулів відліків 7 і підключеного до виходу модуля даних -|у| АЦП 1, 2-м входом D(-), з'єднаного з виходом D ОЗП модулів відліків 7, регістру суми відліків S(n) 9, з'єднаного входом D з виходом D три входового паралельного суматора 8, синхровходом С підключеного до відповідного виходу Команди блока керування 3, нормуючого помножувача 10, 1-й вхід D якого з'єднаний з виходом D регістру суми відліків S(n) 9 і підключений до 3-го входу D (-) тривходового паралельного суматора модулів відліків 8, а синхровходи С1, С2 магістраллю керування підключені до відповідних виходів Команди блока керування 3, а вихід D є виходом рекурентного вимірника середнього значення модулів відліків 6, постійного запам'ятовуючого пристрою (ПЗП) нормуючих коефіцієнтів 11, з'єднаного виходом D з 2-м входом нормуючого помножувача 10, входами адреси - А, вибір кристала - Cs магістраллю керування підключеного до відповідних виходів Команди блока керування 3, а арифметичний блок згортки 2 виконаний у вигляді m ПЗП табличних, часткових, синфазних/ квадратурних згорток 12, входи адреси A(sign) кожного μ-го ПЗП табличної, часткової, синфазної/квадратурної згортки 12 підключені до другого, паралельного виходу D μ-го зсувного послідовно-паралельного одно розрядного регістру ΔΝ відліків 5, входи адреси А( ), A(j), Вибір кристала Cs кожного μ-го ПЗП табличної, часткової, синфазної/квадратурної, згортки 12 з'єднані з відповідними входами інших m-1 ПЗП табличних, часткових, синфазних/квадратурних згорток 12 і підключені магістраллю даних до відповідних виходів Команди блока керування 3, m - входового паралельного суматора 13, з'єднаного своїми m входами D з m виходами D відповідних ПЗП табличних, часткових, синфазних/квадратурних згорток 12, а синхровходом С магістраллю керування підключеного до відповідного виходу Команди блока керування 3, помножувача 14 вихідних відліків рекурентного вимірника середнього значення модуля відліків 6 та m - входового паралельного суматора 13, вихід D якого підключений до 1-го входу D помножувача 14, а до 2-го входу D підключений вихід 5 UA 104922 C2 5 10 D рекурентного вимірника середнього значення модуля відліків 6, синхровходи С1, С2 магістраллю керування підключені до відповідних виходів Команди блоку керування 3, квадратора - суматора 15, 1-й і 2-й входи D якого об'єднані і підключені до виходу D помножувача 14 вихідних відліків рекурентного вимірника середнього значення модуля відліків 6 та m - входового паралельного суматора 13, а синхровходи С1, С2. Установка 0 магістраллю керування підключені до відповідних виходів Команди блоку керування 3, ПЗП табличного обчислення квадратного кореня 16, з'єднаного адресним входом А с виходом D квадратора суматора 15, входом вибір кристала - Cs підключеного до відповідного виходу Команди блока керування 3, а вихід D є виходом цифрового пристрою обробки часових сигналів. Функціонування пристрою розглянемо на прикладі обробки симетрично лінійно частотномодульованих (СЛЧМ) сигналів, що мають розрізнення за часом і частотою і потребують багатоканальної допплерівської обробки [6] yt cos D t 15 20 25 30 35 40 45 50 55 D t / 22; 2 / 2 (20) Пристрій функціонує під керуванням команд і синхросигналів блока керування 3. У момент часу t1 блок керування 3 формує: - синхроімпульс F1 на вході С АЦП 1; - для арифметичного блока згортки 2 код допплерівського каналу на входах А( ); - код синфазної згортки k=0 на входах A(k) m ПЗП табличної, часткової, синфазної згортки 6; - команду очищення регістру на вході Установка в 0 квадратора - суматора 15; - для рекурентного вимірника середнього значення модуля відліків 6 команду Вибір кристала (рівень логічного 0) на вході Cs, адресу mod[(n-1+ Ν,Ν) на вході А ОЗП модулів відліків 7; - адресу нормуючого множника на вході А, команду Вибір кристала (рівень логічного 0) на вході Cs ПЗП нормуючих множників 11. На цьому етапі виконуються такі дії: АЦП 1 дискретизує вхідний сигнал і формує на своєму виході sign[y(n)] знаковий розряд відліку у(n), на своєму виході |у(n)| - підсумовуючому вході D1 три входового паралельного суматора 8 багато розрядний цифровий код модуля відліку у(n), обнуляє внутрішній регістр квадратора - суматора 15, ОЗП модулів відліків 7 підготовлений до приймання даних. При цьому нормуючий множник 1/N установлений на виході D ПЗП нормуючих множників 11 другому вході D нормуючого помножувача 10. У момент часу t2 блок керування 3 формує: - для арифметичного блоку згортки 2 синхроімпульс F 2 на входах С зсувнихпослідовно паралельних регістрів 5; - для рекурентного вимірника середнього значення модуля відліків 6 команду Читання (рівень логічного 0), на вході W/R ОЗУ модулів відліків 7. На цьому етапі виконуються такі дії: - відлік знакового розряду n-ϊ вибірки sign[y(n)], який записується в перший зсувний послідовно - паралельний регістр 5 з одночасним зсувом даних у послідовно з'єднаних m зсувних послідовно - паралельних регістрах 5; - на 2- й віднімаючий вхід D тривходового паралельного суматора 8 зчитується самий старий відлік, записаний в ОЗП модулів відліків 7 за адресою mod[(n-1+ Ν,Ν). У момент часу t3 блок керування 3 формує: - для арифметичного блока згортки 2 команду вибір кристала на входах Cs m ПЗУ табличної, часткової, синфазної/квадратурної згортки 6; - для рекурентного вимірника середнього значення модуля відліків 6 синхроімпульс F З на вході С тривходового паралельного суматора відліків 8, синхроімпульс F 3 на вході С регістра суми модулів відліків 9. На цьому етапі виконуються наступні дії: - по ΔΝ відлікам знакових розрядів із других, паралельних виходів m зсувно-паралельних регістрів 5 на адресних входах A[signy(n)] m ПЗП табличної, часткової, синфазної/квадратурної згортки 12 на їхніх виходах формуються m відліків часткової, синфазної згортки кліпованого сигналу sign[y(n)] із синфазною допплерівською багато розрядною копією сигналу Re(yo( ,(μ1)·ΔΝ+Δn) 6 UA 104922 C2 u , ,n Re zo, ,n 1 Re yo, 1 n signyn n 1; (21) n0 - у регістр суми модулів відліків 9 записується відлік Υ(n) з виходу D тривходового суматора 8 і, таким чином, рекурентно обчислюється сума N модулів відліків у ковзному часовому вікні. Υ(n) = Υ(n-1) + |у (n)| - |у (n -Ν+1)|; у (n -Ν+1) = у [mod(n-N+1, Ν)]; (22) (24) 5 10 15 mod(n-N+1, Ν) - адреса, за якою відлік у (n -Ν+1) записаний в ОЗП модулів відліків 7. У момент часу t4 блок керування 3 формує: - для арифметичного блока згортки 2 синхроімпульс F 4 на вході С m - входового паралельного суматора часткових знакових згорток 13; - для рекурентного вимірника середнього значення модуля відліків 6 синхроімпульс F 4 на нормуючому вході С 1 помножувача 10. На цьому етапі виконуються наступні дії: - m-входовий паралельний суматор 13 формує на своєму виході D - вході D1 помножувача середнього значення модуля відліків і відліків знакової згортки суматора 14 згортку послідовності N знакових відліків з допплерівською синфазною копією сигналу як суму m часткових синфазних згорток з паралельних виходів m ПЗП табличної часткової синфазної / квадратурної згортки 12. U,n Re zo,n u, ,n ; 1,...m; (25) 20 25 30 - відлік суми Ν модулів відліків Υ(n) с виходу D регістра суми модулів відліків 9 і нормуючий множник, 1/N з виходу D ПЗП нормуючих множників 11 записуються у внутрішні регістри, нормуючого помножувача 10. У момент часу t5 блок керування 3 формує: - для арифметичного блока згортки 2 код квадратурної згортки j=1 на входах A(j), команду вибір кристала на входах Cs m ПЗП табличної, часткової, синфазної/квадратурної згортки 7; - для вимірника середнього значення модуля відліків 6 команду Запис (рівень логічної 1), на вході W/R ОЗУ модулів відліків 7 синхроімпульс F 5 на вході С 2 нормуючого помножувача 14. На цьому етапі виконуються такі дії: - по ΔΝ відлікам знакових розрядів із других, паралельних виходів D m зсувних послідовно - паралельних регістрів 5 на адресних входах A(sign) m ПЗП табличної, часткової, синфазної/квадратурної згортки 7 на їхніх виходах формуються m відліків ,,n часткової, квадратурної згортки кліпованого сигналу sign[y(n)] із квадратурною допплерівською багаторозрядною копією сигналу myo, 1 n , ,n mzo, ,n 35 40 1 myo, n signyn n 1 ; - -й допплерівський відлік синфазної знакової згортки U( ,n) з виходу D m - входового паралельного суматора 13 встановлюється на вході D1 помножувача середнього значення модуля відліків і відліків знакової згортки 14. Нормуючий помножувач 10 відлік Y(n) помножує на нормуючий множник 1/ N і встановлює на своєму виході D - вході D2 помножувача середнього значення модуля відліків і відліків знакової згортки 14 середнє значення модуля відліків an Yn 1/ ; (27) 45 (26) n0 Обчислене середнє значення модуля відліків a n зберігається на вході D2 помножувача середнього значення модуля відліків і відліків знакової згортки 14 до нового n+1 -го періоду дискретизації. У момент часу t6 блок керування 3 формує: - для арифметичного блока згортки 2 синхроімпульс F 6 на вході C m- входового паралельного суматора 9; 7 UA 104922 C2 5 - синхроімпульс F 6 на вході С 2 помножувача середнього значення модуля відліків і відліків знакової згортки 14. На цьому етапі виконуються такі дії: - -й допплерівський відлік синфазної знакової згортки U( ,n) і відлік середнього значення модуля s(n) перемножуються й установлюються на виході помножувача середнього значення модуля відліків і відліків знакової згортки 14 - входах D1, D2 квадратора-суматора 15 ,n an U,n ; 10 (28) - m - входовий паралельний суматор 8 формує на своєму виході D - вході D1 помножувача середнього значення модуля відліків і відліків знакової згортки 14 квадратурну згортку послідовності N знакових відліків з допплерівською копією сигналу як суму m часткових синфазних згорток з паралельних виходів m ПЗП табличної часткової синфазної/квадратурної згортки 6. V ,n mzo, ,n v , ,n ; 1,...m; (29) 15 20 У момент часу t7 блок керування 3 формує для арифметичного блока згортки 2 синхроімпульс F 7 на вході С 1 квадратора-суматора 15. На цьому етапі виконуються такі дії: - -й допплерівський відлік синфазної згортки ξ( ,n) з виходу D помножувача середнього значення модуля відліків і відліків знакової згортки 14 квадрується і підсумовується із змістом акумулятора квадратора-суматора 15 2 2 Ζ ( ,n) = 0 + ξ ( ,n); 25 30 (30) У момент часу t8 блок керування 3 формує для арифметичного блока згортки 2 синхроімпульс F 8 на вході С 2 помножувача середнього значення модуля відліків і відліків знакової згортки 14. На цьому етапі -й допплерівський відлік квадратурної знакової згортки V( ,n) і відлік середнього значення модуля s(n) перемножуються і встановлюються на виході D помножувача середнього значення модуля відліків і відліків знакової згортки 14 - входах D1, D2 квадратора суматора 15 η( ,n) = a n •V( ,n); 35 (31) У момент часу t8 блок керування 3 формує для арифметичного блока згортки 2 синхроімпульс F 8 на вході С 2 квадратора-суматора 15, при цьому виконуються такі дії: - -й допплерівський відлік квадратурної згортки η( ,n) з виходу D помножувача середнього значення модуля відліків і відліків знакової згортки 14 квадрується і підсумовується з вмістом акумулятора квадратора- суматора 15 і на виході D квадратора накопичувача 16 - вході А ПЗП 2 табличного обчислення квадратного кореня 16 установлюється код квадрата згортки Z ( ,n). 2 2 2 Ζ ( ,n) = ξ ( ,n) + η ( ,n) (32) 40 45 У момент часу t 9 блок керування 3 формує для арифметичного блоку згортки 2 команду вибір кристалу на вході Cs ПЗП табличного обчислення квадратного кореня 16, при цьому виконуються такі дії: - на виході D ПЗП табличного обчислення квадратного кореня 16 установлюється код z( ,n) 2 таблично обчисленого квадратного кореня з Ζ ( ,n) 2 2 1 Е( ,n) = [ξ ( ,n) + η ( ,n) /2; 50 (33) На цьому формування -го допплерівського вихідного відліку z( ,n) завершене. В n-му періоді дискретизації виконується формування L допплерівських відліків методом роздільної амплітудно-фазової обробки t1-t8. 8 UA 104922 C2 5 10 Після завершення допплерівської обробки в n-му періоді дискретизації блок керування 3 послідовно формує для вимірника середнього значення модуля відліків 6 команду адреси mod(n, Ν) на вході адреси А ОЗП модулів відліків 7, команду Запис (рівень логічної 1), на вході W/R ОЗП модулів відліків 7, при цьому модуль відліку |у (n)| з виходу АЦП 1 записується в ОЗУ модулів відліків 7 за адресою mod (n, N). Пряме обчислення одного відліку модуля згортки реалізації сигналу у(n) довжиною N відліків χ з копією в пристрої прототипі згідно з (1) потребує 2Ν операцій множення, 2 Ν операцій додавання при обчисленні синфазної й квадратурної згорток, 2 операції зведення у квадрат, 2 операції додавання при обчисленні квадрата модуля, 1 операцію табличного обчислення квадратного кореня - усього Q.prot операцій формування Q.prot=4•N+4+1=4•N+5; 15 20 Згідно з (26), (29). (31) у пропонованому пристрої обчислення m часткових синфазної й квадратурної знакових згорток кліпованого сигналу із багаторозрядною комплексною копією, що потребує 2Δn операцій множення і 2 Δn операцій додавання багато розрядних чисел, виконується таблично за 2 такти, 2m операцій додавання комплексних часткових згорток виконуються m - входовим паралельним суматором за 2 такти, множення вихідних комплексних відліків знакової згортки й рекурентного вимірника середнього значення модуля відліків виконується за 2 такти, обчислення квадрата модуля включає 2 операції зведення у квадрат, 2 операції додавання, табличне обчислення квадратного кореня виконується за 1 такт - усього Q sign.inov операцій. Q sign.inov=2+2+2+2+2+1=11; 25 (34) (35) Рекурентне вимірювання середнього значення модуля відліків, згідно з (22), (27), вимагає одну операцію множення та одну операцію додавання за L циклів Qampl.inov = (1+1)/L=2/L; (36) Повна кількість арифметичних операцій пристрою, що заявляється, при обчисленні одного вихідного відліку дорівнює 30 Q.inov=Q sign.inov+Q ampl.inov=11+2/L. (37) Відносно прототипу виграш - W у швидкодії за рахунок скорочення кількості операцій становить Q sign.prot 4·Ν + 5 35 W Qsign.prot Qinov 4 N 5 ; 11 2 / L (38) Для N >> 5; 4•N+5 4•N; L N/2 >> 2; 11+2/L 11; W 40 45 4 ; 11 (39) В Таблиці наведені дані виграшу за числом операцій відносно прототипу при допплерівській фільтрації сигналу в ковзному вікні як функція числа відліків сигналу N в реалізації - W(N). Технічний результат - підвищення швидкодії відносно прототипу досягається: - розділенням амплітудної й фазової обробки; - реалізацією фазової (когерентної) обробки знаковою згорткою, яка виконується таблично; - амплітудною (некогерентною) обробкою, яка виконується рекурентно. Втрати у вихідному відношенні сигнал/завада не більш ніж 3.5 дБ. Ємність Q одного постійного ЗП, необхідна для табличного обчислення часткової згортки, дорівнює ΔΝ Q=2 AN •2 k r •2 • 2; (39) де r - розрядність вихідних даних. Для ΔΝ = 8; ΔL=7; k=1; r=8; (40) 9 UA 104922 C2 Q=16 Мбіт 5 10 15 Табличне обчислення часткових знакових згорток з параметрами (40) може бути реалізоване, наприклад, на базі мікросхем постійної пам'яті фірми SST(Silicon Storage Technology)-SST 28ЕЕ016 ємністю 16 Мбіт (2М 8), SST 28ЕЕ032 ємністю 32 Мбіт (4М 8) 8 [7]. Сучасні мікросхеми постійної Флеш пам'яті мають ємність Q 100 Гбіт. Джерела інформації: 1. Свистов В. И. Радиолокационные сигналы и их обработка. - Μ.: Советское радио. -1970.С. 193-195. 2. Рабинер Л., Гоулд Б. Теория и применение цифровой обработки сигналов. - М.: Мир.1978, С. 422, 423. 3. Финкелыптейн М. И. Основы радиолокации. - М.: Радио и связь. - 1983. - С. 249-252. 4. Ипатов В. П., Казаринов Ю. М. и др. Поиск, обнаружение и измерение параметров в радионавигационных системах. -М.: Советское радио. - 1975.-С. 127-151. 5. Пестряков В. Б. Фазовые радиотехнические системы. - М.: Советское радио". -1968.-С. 340-342. 6. Варакин Л. Е. Теория сложных сигналов. - М.: Советское радио. - 1970. - С. 139,140 7. Гук М. Аппаратные средства IBM PC. Энциклопедия. - СПб: Питер. - 2000. - С. 408, 409. Таблиця Ν 128 256 512 W W(N) 46 93 186 20 ФОРМУЛА ВИНАХОДУ 25 30 35 40 45 50 Пристрій цифрової обробки часових сигналів, що містить АЦП, арифметичний блок згортки, блок керування, який відрізняється тим, що введені оперативний запам'ятовуючий пристрій (ОЗП) знакових розрядів, виконаний у вигляді m зсувних послідовно-паралельних однорозрядних регістрів ΔΝ відліків кожний, причому вхід D першого зсувного послідовнопаралельного однорозрядного регістра ΔΝ відліків з'єднаний з виходом знакового розряду АЦП, входи D інших m-1 зсувних послідовно-паралельних однорозрядних регістрів ΔΝ відліків з'єднані своїм входом D з першим послідовним виходом D попереднього зсувного послідовнопаралельного однорозрядного регістра ΔΝ відліків, синхровходи С регістрів об'єднані і підключені магістраллю керування до відповідного виходу ″Команди″ блока керування, рекурентний вимірювач середнього значення модулів відліків, виконаний у вигляді ОЗП модулів відліків, підключеного входами адреси - А, запис-зчитування - W/R, вибір кристала - Cs магістраллю керування до відповідних виходів ″Команди″ блока керування, тривходового паралельного суматора, з'єднаного першим входом D(+) із входом D ОЗП модулів відліків і підключеного до виходу модуля даних АЦП - |у|, другим входом D(-), з'єднаного з виходом D ОЗП модулів відліків, регістра суми відліків S(n), з'єднаного входом D з виходом D тривходового паралельного суматора, синхровходом С підключеного до відповідного виходу ″Команди″ блока керування, нормуючого помножувача, один вхід D якого з'єднаний з виходом D регістра суми відліків S(n) і підключений до третього входу D(-) тривходового паралельного суматора модулів відліків, а синхровходи С1, С2 магістраллю керування підключені до відповідних виходів ″Команди″ блока керування, а вихід D є виходом рекурентного вимірювача середнього значення модулів відліків, постійного запам'ятовуючого пристрою (ПЗП) нормуючих коефіцієнтів, з'єднаного виходом D із другим нормуючим входом помножувача, входами адреси - А, вибір кристала - Cs магістраллю керування, підключеного до відповідних виходів ″Команди″ блока керування, арифметичний блок згортки, виконаний у вигляді μ ПЗП табличних, часткових, синфазних/квадратурних згорток, входи адреси A(sign) кожного μ-го ПЗП табличної, часткової, синфазної/квадратурної згортки підключені до другого, паралельного виходу D m-го зсувного послідовно-паралельного однорозрядного регістра ΔΝ відліків, входи адреси А( ), А(j), вибір кристала Cs кожного μ-го ПЗП табличної, часткової, синфазної/квадратурної згортки з'єднані з відповідними входами інших μ-1 постійних запам'ятовуючих пристроїв ПЗП табличних, часткових, синфазних/квадратурних згорток і підключені магістраллю даних до відповідних виходів ″Команди″ блока керування, m-входового паралельного суматора, з'єднаного своїми m 10 UA 104922 C2 5 10 входами D з m виходами D відповідних ПЗП табличних, часткових, синфазних/квадратурних згорток, а синхровходом С магістраллю керування підключеного до відповідного до виходу ″Команди″ блока керування, помножувача вихідних відліків рекурентного вимірювача середнього значення модуля відліків і m-входового паралельного суматора, вихід D якого підключений до першого входу D помножувача, а до другого входу D підключений вихід D рекурентного вимірювача середнього значення модуля відліків, синхровходи С1, С2 магістраллю керування підключені до відповідних виходів ″Команди″ блока керування, квадратора-суматора, перший і другий входи D якого об'єднані й підключені до виходу D помножувача вихідних відліків рекурентного вимірювача середнього значення модуля відліків і m-входового паралельного суматора, а синхровходи С1, С2, Встановлення 0 магістраллю керування, підключені до відповідних виходів ″Команди″ блока керування, ПЗП табличного обчислення квадратного кореня, з'єднаного входом адреси А з виходом D квадратора-суматора, входом вибір кристала - Cs підключеного до відповідного виходу ″Команди″ блока керування, а вихід D є виходом цифрового пристрою обробки часових сигналів. 11 UA 104922 C2 12 UA 104922 C2 13 UA 104922 C2 14 UA 104922 C2 15 UA 104922 C2 Комп’ютерна верстка А. Крижанівський Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 16

ДивитисяДодаткова інформація

Автори англійськоюZatserkovskyi Ruslan Oleksiiovych

Автори російськоюЗацерковский Руслан Алексеевич

МПК / Мітки

МПК: G01S 7/28

Мітки: сигналів, обробки, пристрій, часових, цифровий

Код посилання

<a href="https://ua.patents.su/18-104922-cifrovijj-pristrijj-obrobki-chasovikh-signaliv.html" target="_blank" rel="follow" title="База патентів України">Цифровий пристрій обробки часових сигналів</a>

Попередній патент: Вібраційний коток-модуль

Наступний патент: Спосіб і пристрій для оптимізованого кругооберту стрижнів при виробництві гарячекатаних безшовних сталевих труб безперервним способом

Випадковий патент: Спосіб одержання каталізатора для автономного генератора тепла на основі безполум'яного спалювання газоподібного вуглеводневого палива