Обчислювальна система

Номер патенту: 19875

Опубліковано: 25.12.1997

Автори: Дідик Петро Іванович, Любарський Валерій Федорович, Мушка Віра Михайлівна, Балабанов Олександр Степанович, Авербух Анатолій Базильович, Коваль Валерій Миколайович, Булавенко Олег Миколайович, Рабинович Зіновій Львович, Палагін Олександр Васильович

Формула / Реферат

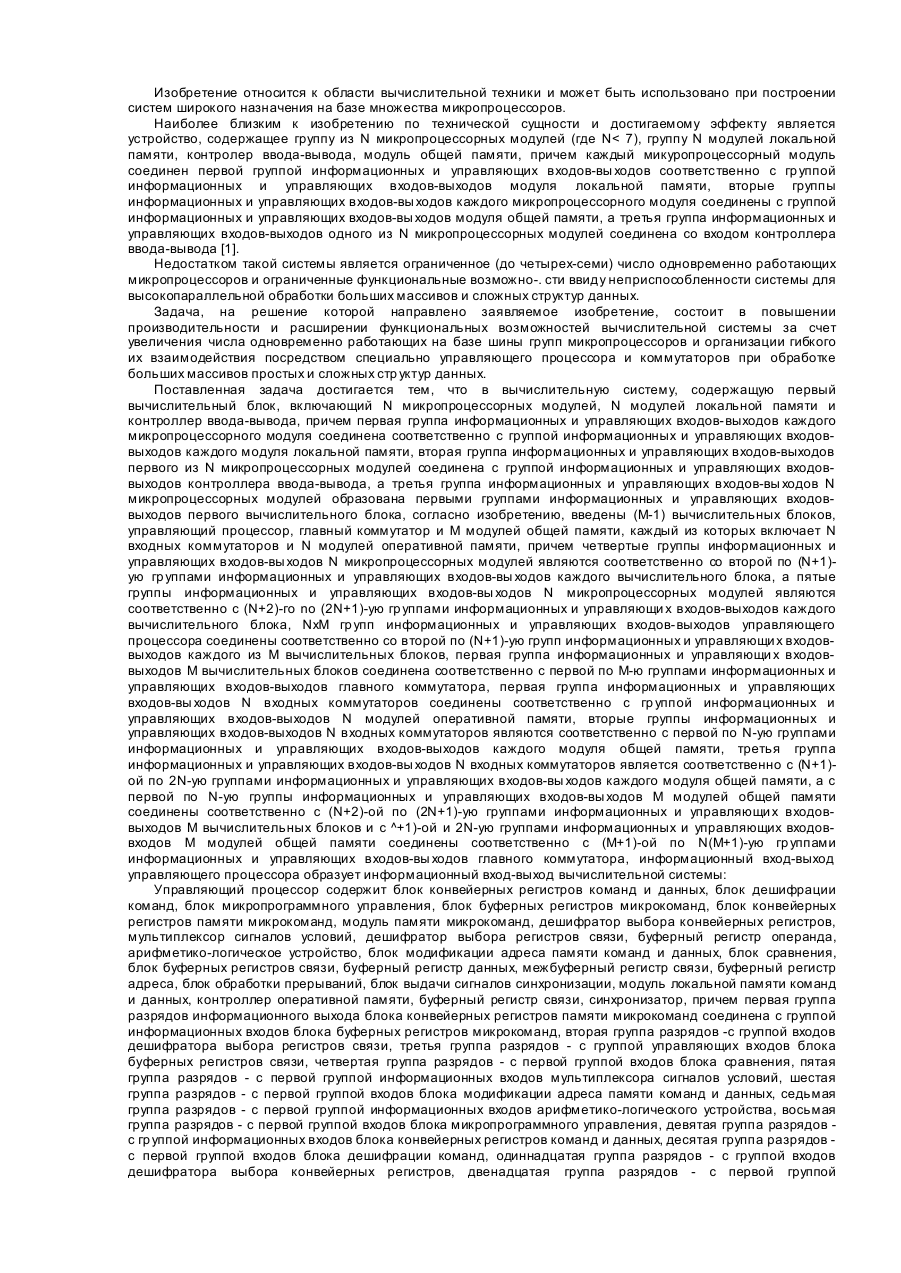

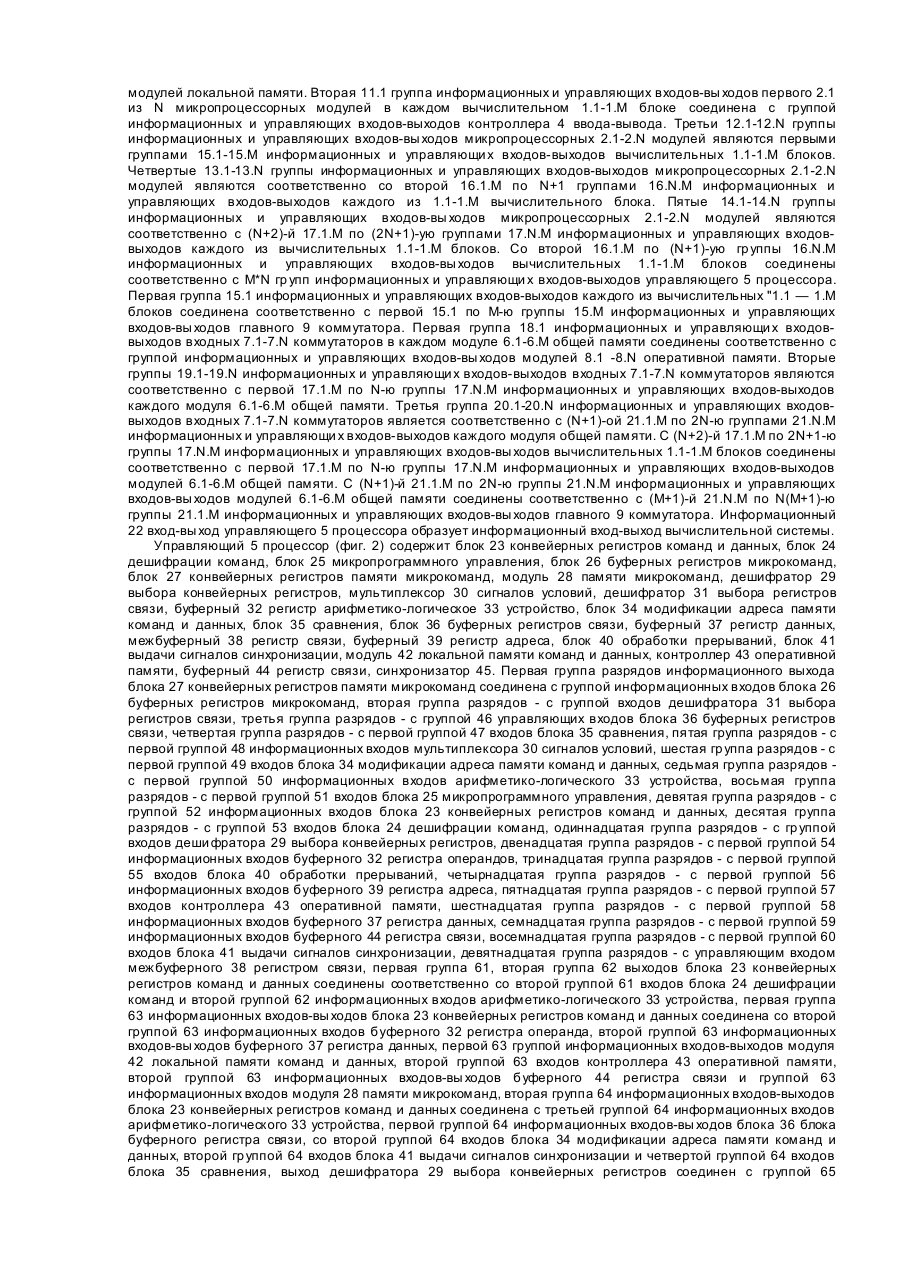

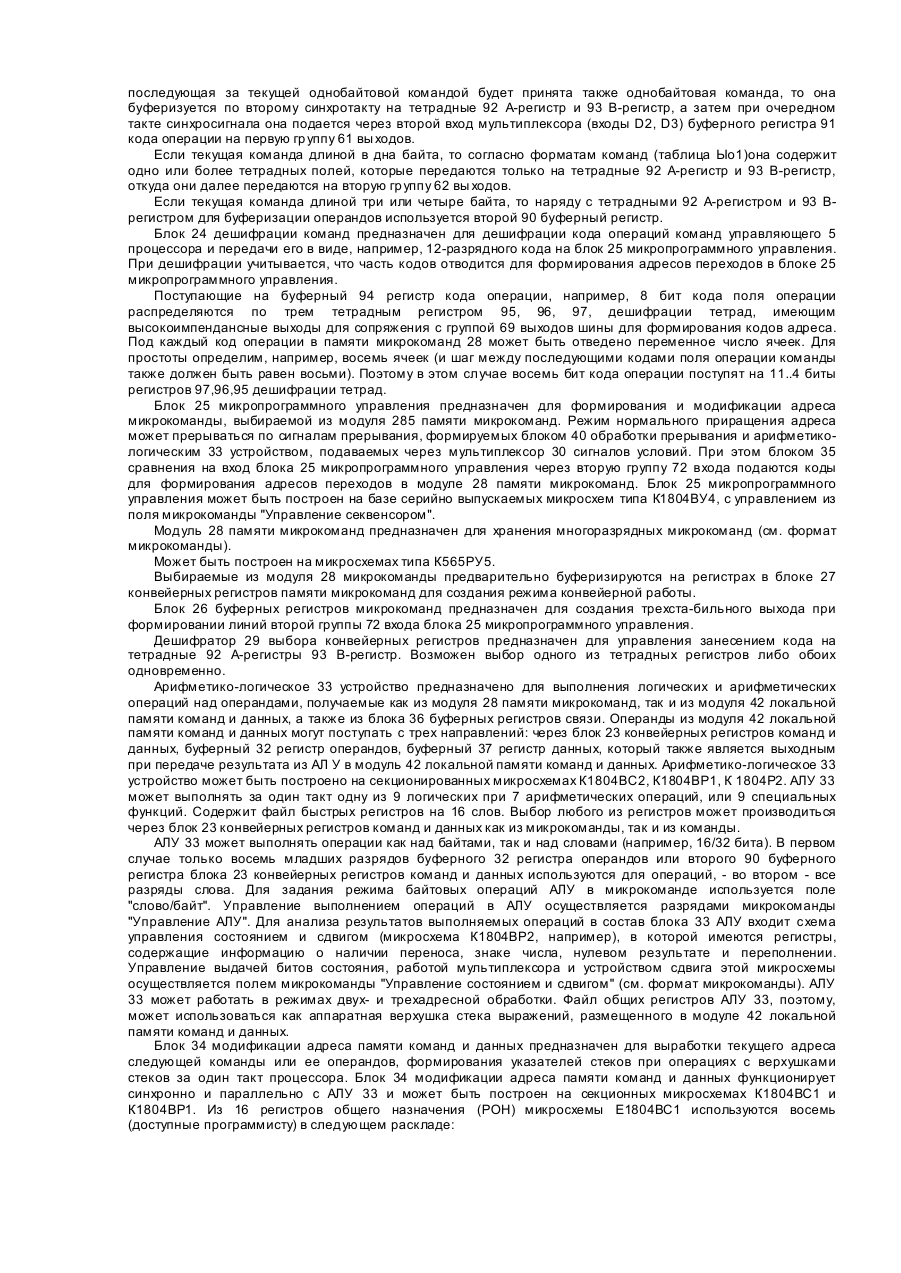

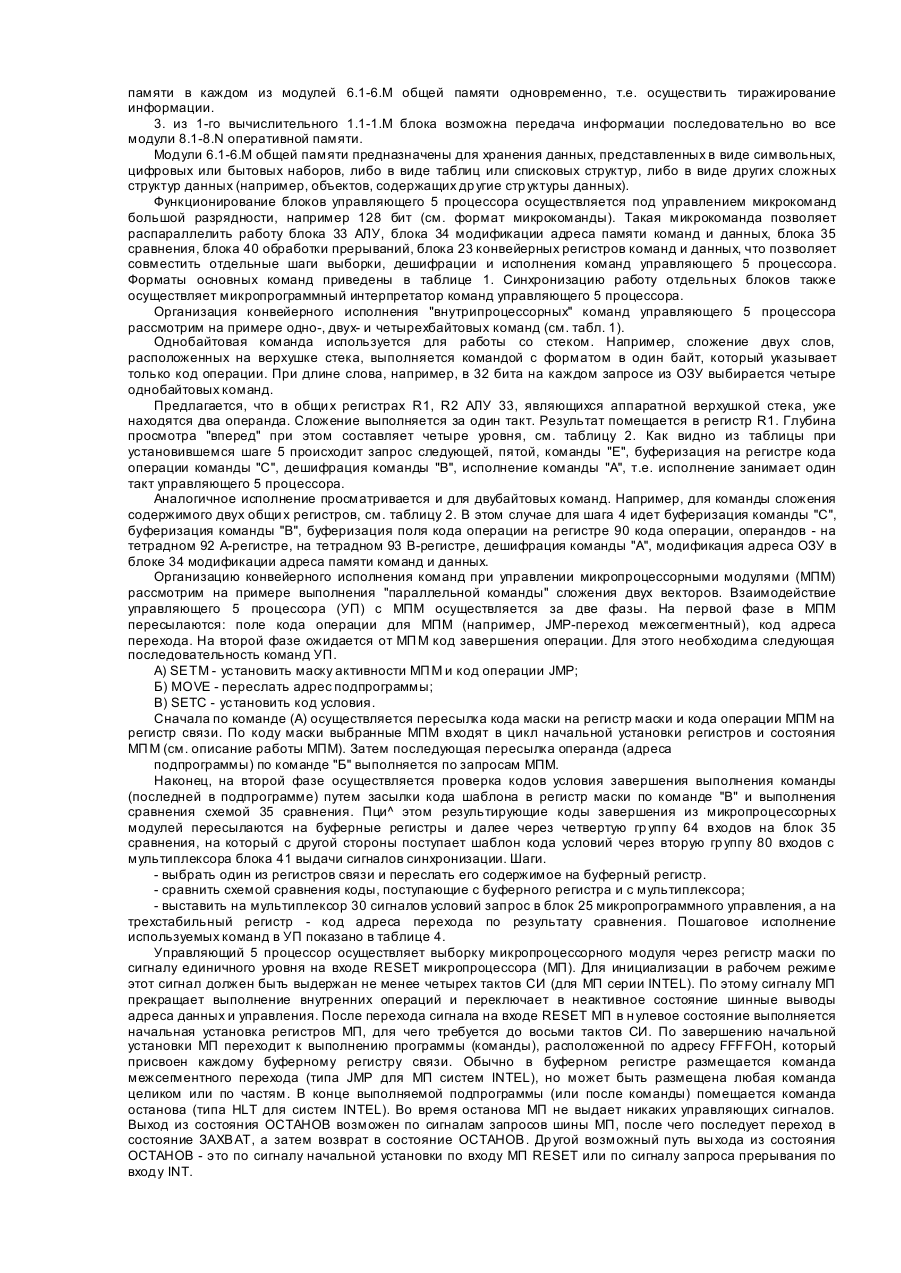

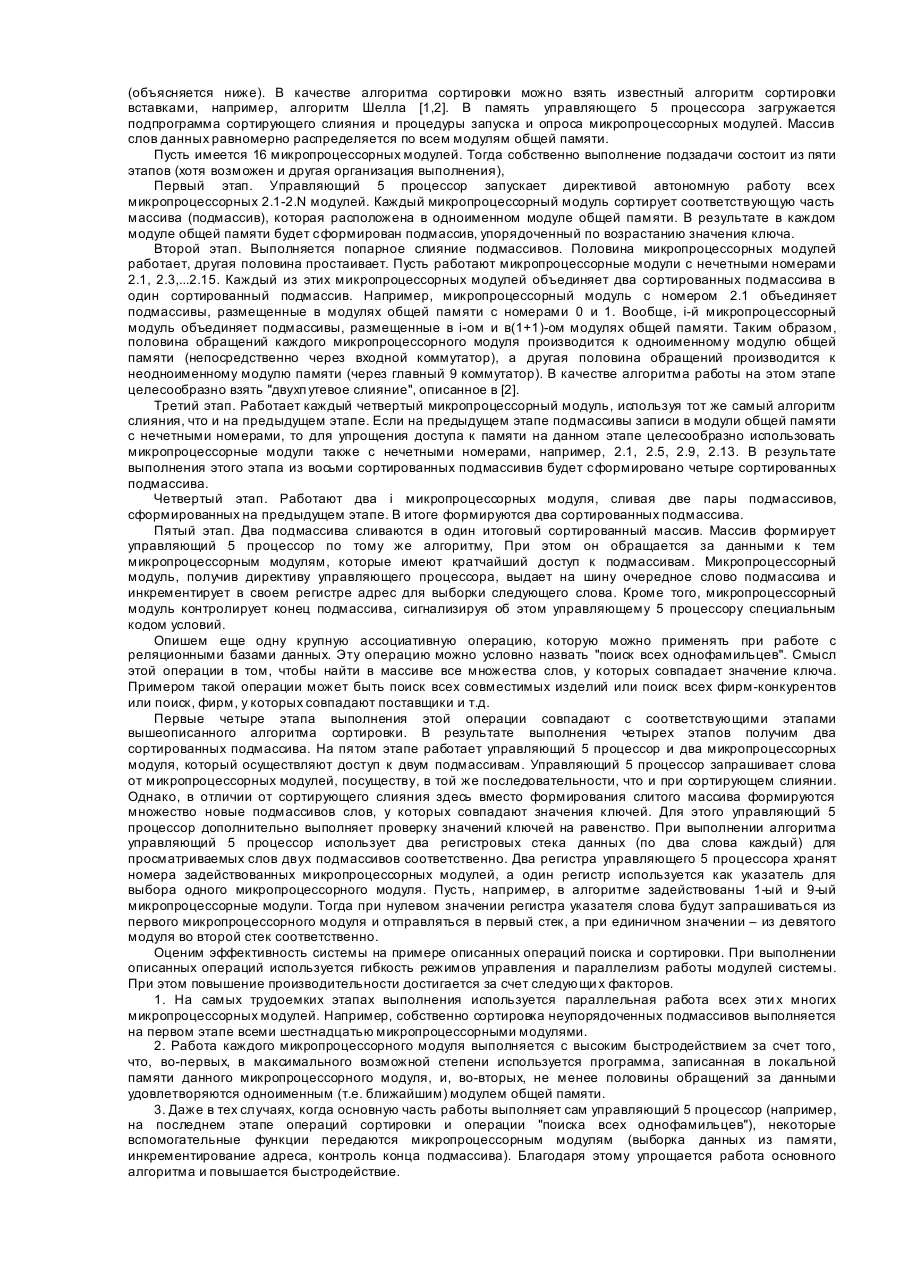

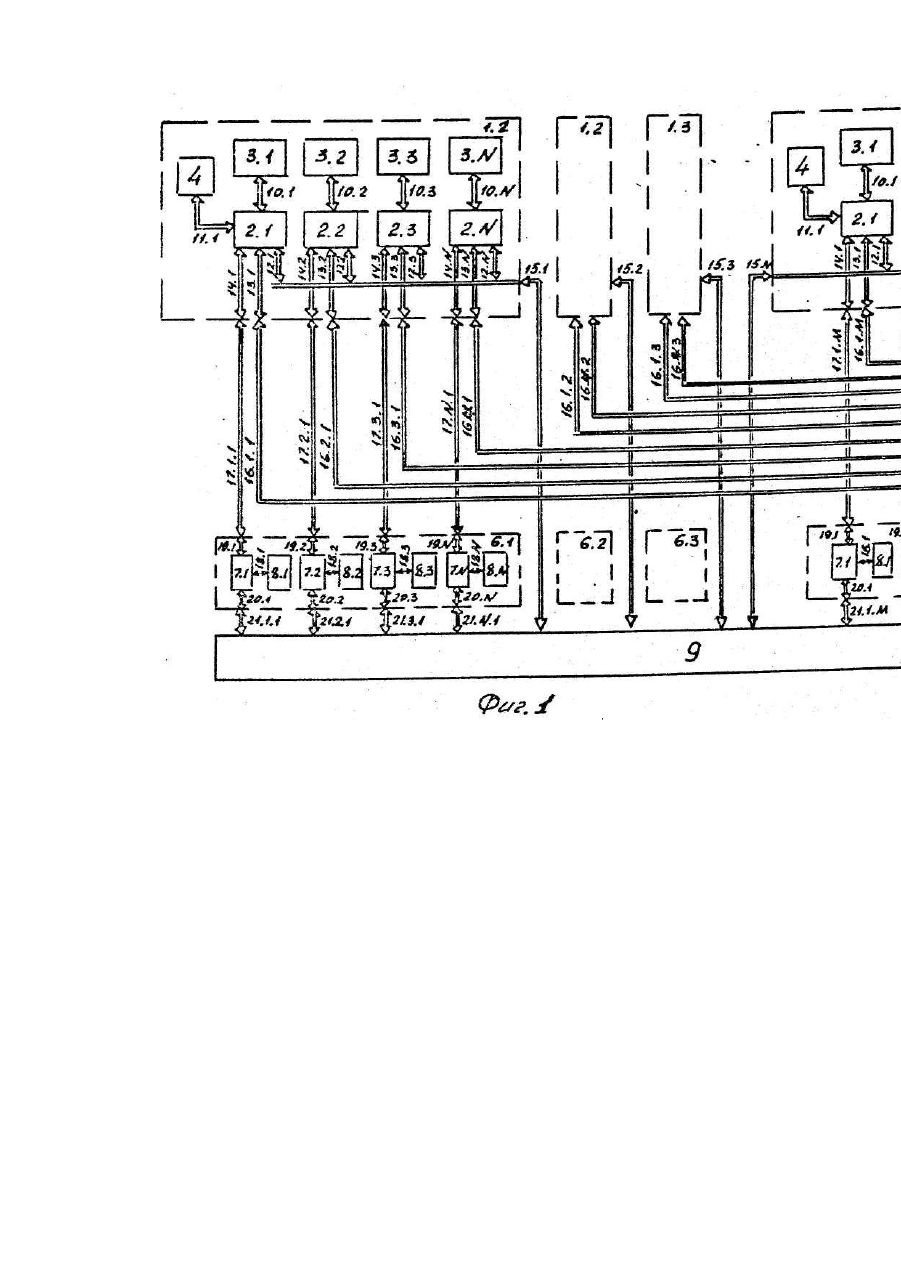

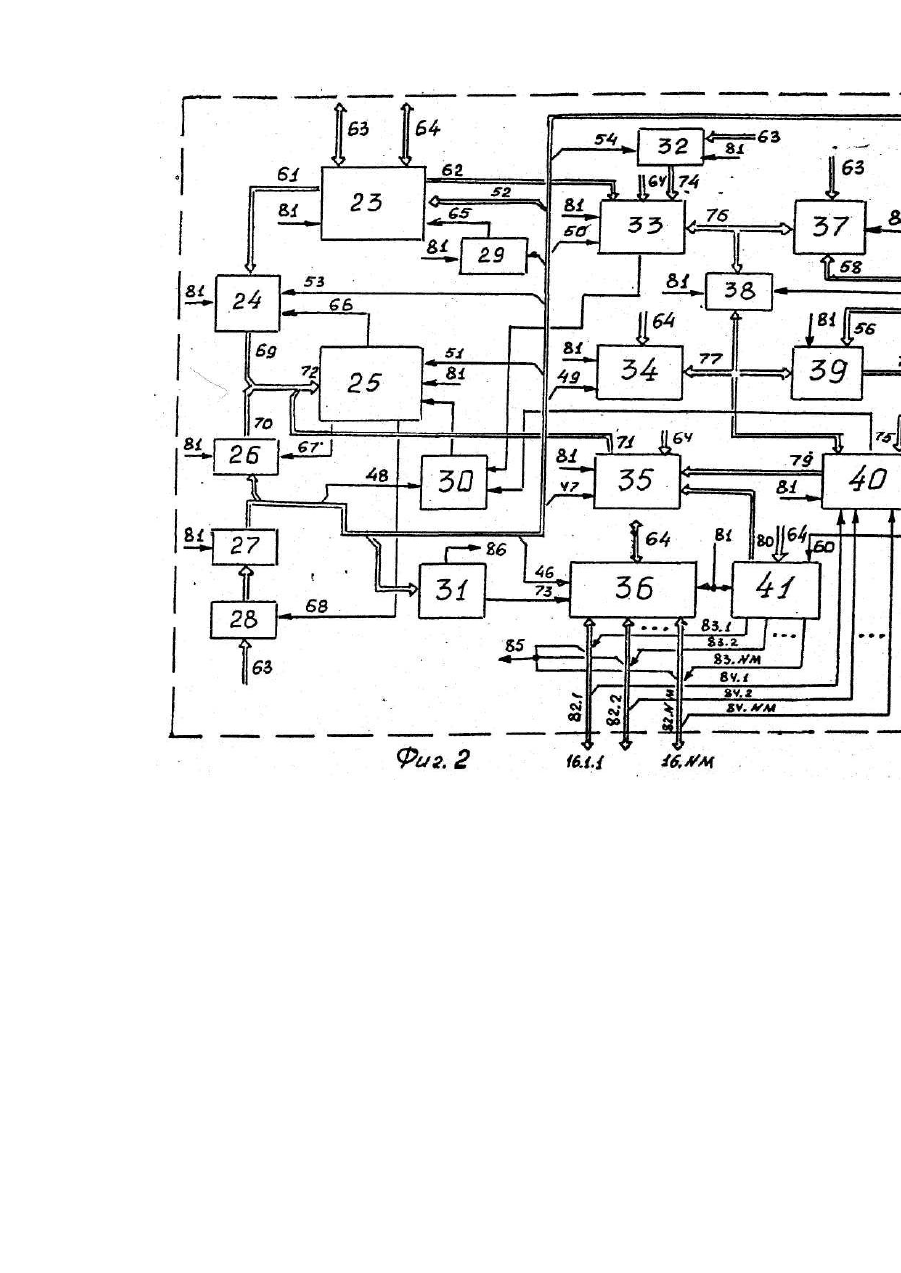

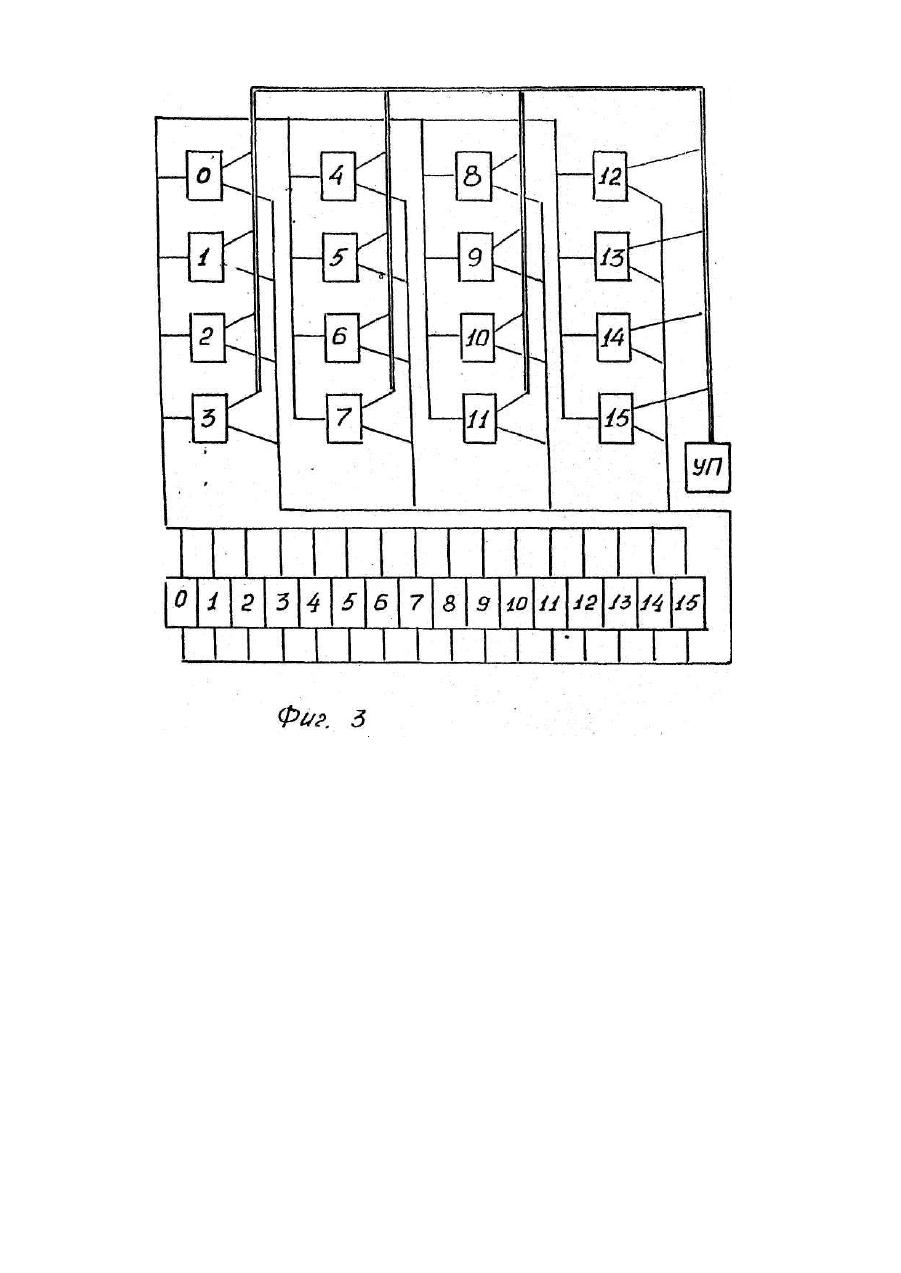

1. Вычислительная система, содержащая первый вычислительный блок, включающий N микропроцессорных модулей, N модулей локальной памяти и контроллер ввода-вывода, причем первая группа информационных и управляющих входов-выходов каждого микропроцессорного модуля соединена соответственно с группой информационных и управляющих входов-выходов каждого модуля локальной памяти, вторая группа информационных и управляющих входов-выходов первого из N микропроцессорных модулей соединена с группой информационных и управляющих входов-выходов контроллера ввода-вывода, а третья группа информационных и управляющих входов-выходов N микропроцессорных модулей образована первыми группами информационных и управляющих входов-выходов первого вычислительного блока, отличающаяся тем, что в нее введены (М-1) вычислительных блоков, управляющий процессор, главный коммутатор и М модулей общей памяти, каждый из которых включает N входных коммутаторов и N модулей оперативной памяти, причем четвертые группы информационных и управляющих входов-выходов N микропроцессорных модулей являются соответственно со второй по (N+1)-yю группами информационных и управляющих входов-выходов каждого вычислительного блока, а пятые группы информационных и управляющих входов-выходов N микропроцессорных модулей являются соответственно с (N+2)-ой по (2N+1)-yю группами информационных и управляющих входов-выходов каждого вычислительного блока, NxM групп информационных и управляющих входов-выходов управляющего процессора соединены соответственно со второй по (N+1)-yю групп информационных и управляющих входов-выходов каждого из М вычислительных блоков, первая группа информационных и управляющих входов-выходов М вычислительных блоков соединена соответственно с первой по М-ю группами информационных и управляющих входов-выходов главного коммутатора, первая группа информационных и управляющих входов-выходов N входных коммутаторов соединены соответственно с группой информационных и управляющих входов-выходов N модулей оперативной памяти, вторые группы информационных и управляющих входов-выходов N входных коммутаторов являются соответственно с первой по N-ую группами информационных и управляющих входов-выходов каждого модуля общей памяти, третья группа информационных и управляющих входов-выходов N входных коммутаторов является соответственно с (N+1)-ou по 2N-ую группами информационных и управляющих входов-выходов каждого модуля общей памяти, с первой по N-ую группы информационных и управляющих входов-выходов М модулей общей памяти соединены соответственно с (N+2)-oй no (2N+1)-yю группами информационных и управляющих входов-выходов М вычислительных блоков, а с (N+1)-oh по 2N-ую группы информационных и управляющих входов-входов М модулей общей памяти соединены соответственно с (М+1)-ой по N(M+1)-yю группами информационных и управляющих входов-выходов главного коммутатора,; информационный вход-выход управляющего процессора образует информационный вход-. выход вычислительной системы.

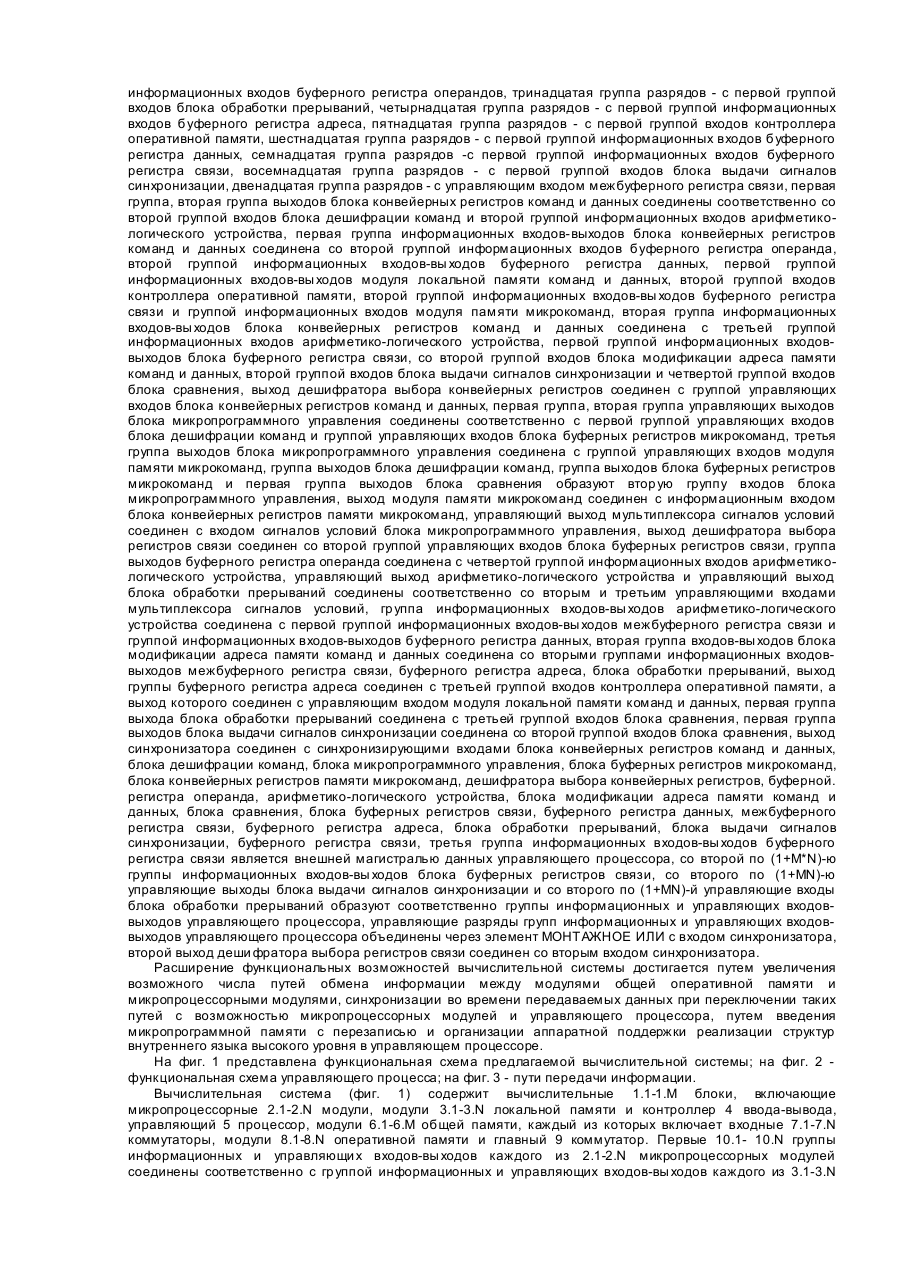

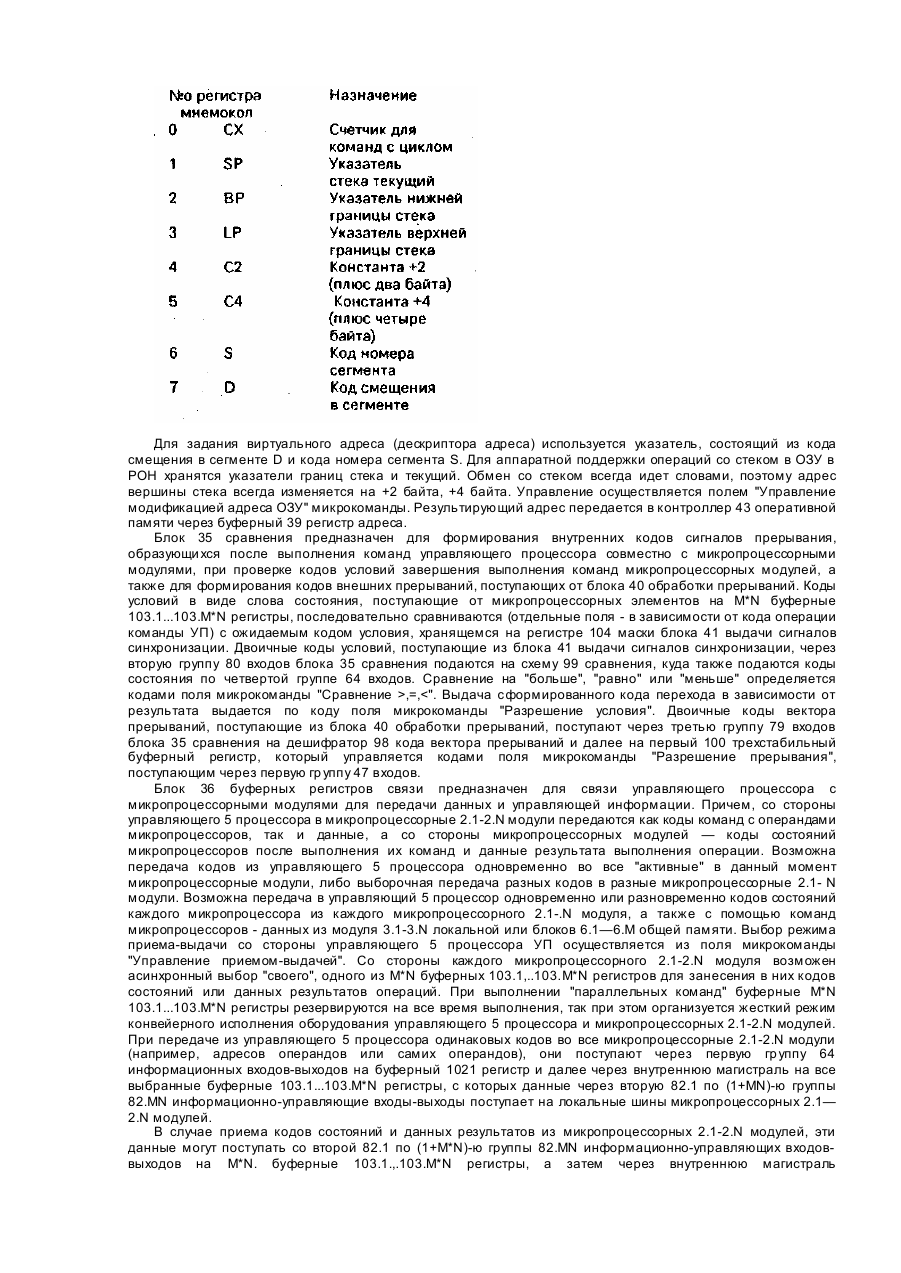

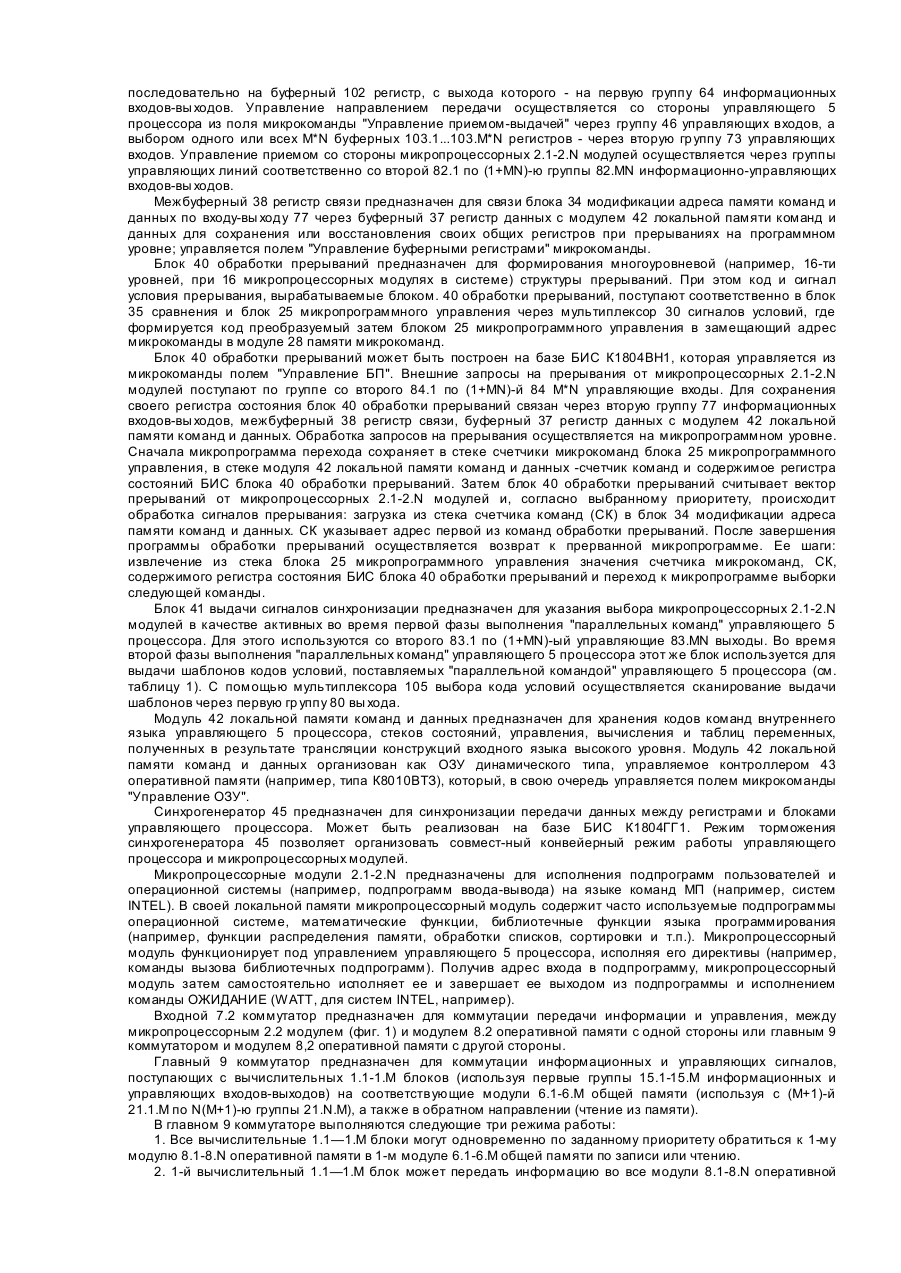

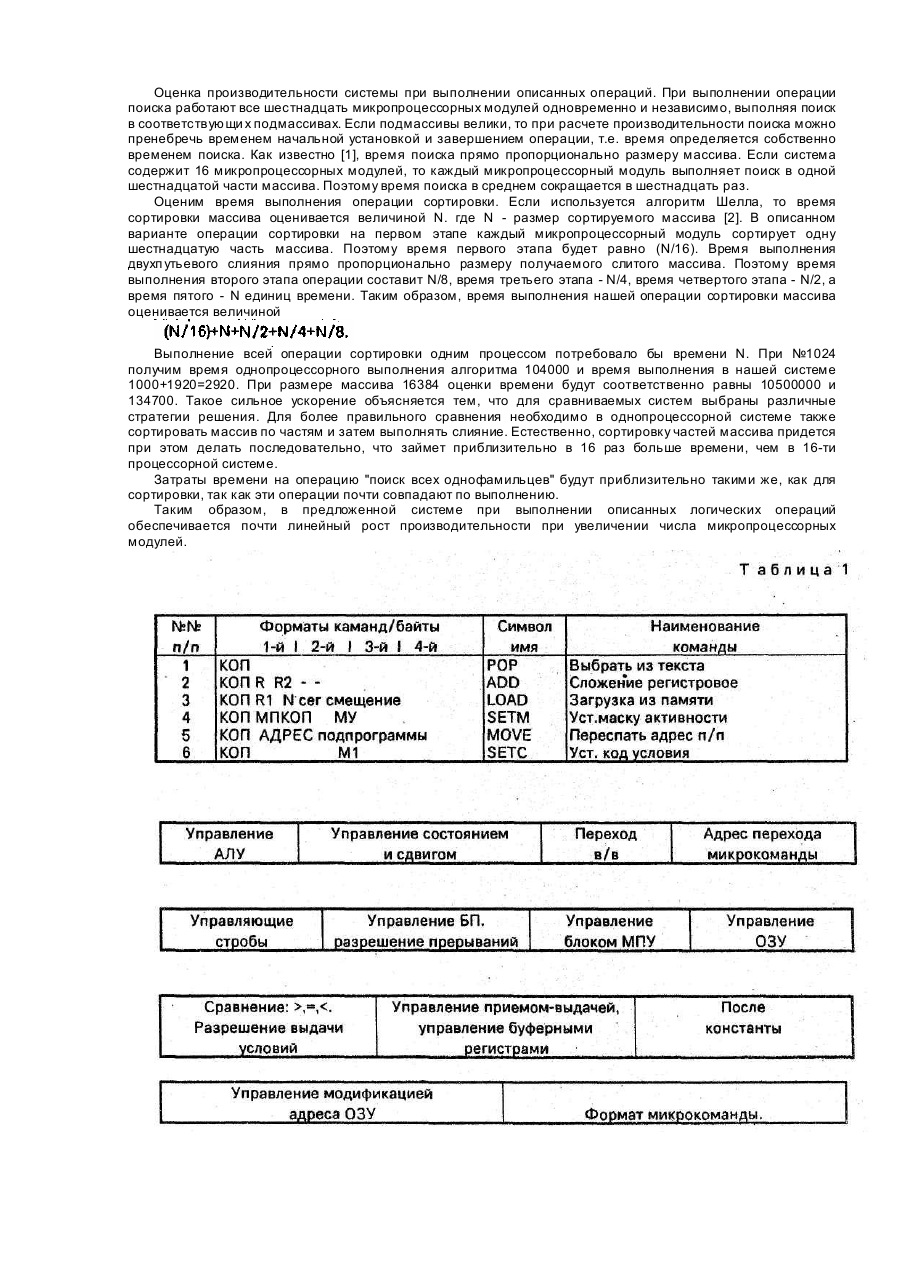

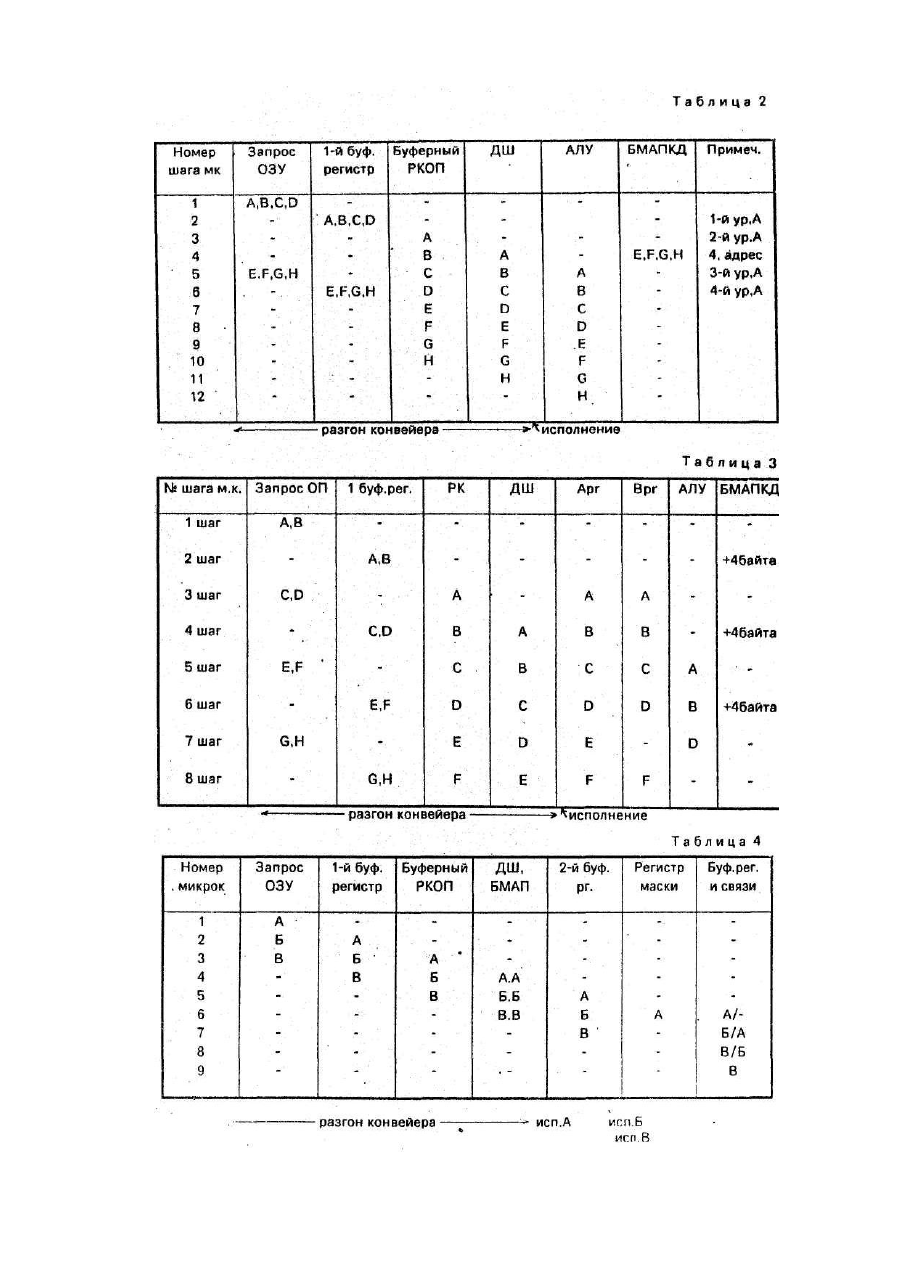

2. Вычислительная система по п. 1, отличающаяся тем, что управляющий процессор содержит блок конвейерных регистров команд и данных, блок дешифрации команд, блок микропрограммного управления, блок буферных регистров микрокоманд, блок конвейерных регистров памяти микрокоманд, модуль памяти микрокоманд, дешифратор выбора конвейерных регистров, мультиплексор сигналов условий, дешифратор выбора регистров связи, буферный регистр операнда, арифметико-логическое устройство, блок модификации адреса памяти команд и данных, блок сравнения, блок буферных регистров связи, буферный регистр данных, межбуферный регистр связи, буферный регистр адреса, блок обработки прерываний, блок выдачи сигналов синхронизации, модуль локальной памяти команд и данных, контроллер оперативной памяти, буферный регистр связи, синхронизатор, причем первая группа разрядов информационного выхода блока конвейерных регистров памяти микрокоманд соединена с группой информационных входов блока буферных регистров микрокоманд, вторая группа разрядов - с группой входов дешифратора выбора регистров связи, третья группа разрядов - с группой управляющих входов блока буферных регистров связи, четвертая группа разрядов - с первой группой входов блока сравнения, пятая группа разрядов - с первой группой информационных входов мультиплексора сигналов условий, шестая группа разрядов - с первой группой входов блока модификации адреса памяти команд и данных, седьмая группа разрядов - с первой группой информационных входов арифметико-логического устройства, восьмая группа разрядов - с первой группой входов блока микропрограммного управления, девятая группа разрядов- с группой информационных входов блока конвейерных регистров команд и данных, десятая группа разрядов - с первой группой входов блока дешифрации команд, одиннадцатая группа разрядов - с группой входов дешифратора выбора конвейерных регистров, двенадцатая группа разрядов - с первой группой информационных входов буферного регистра операндов, тринадцатая группа разрядов - с первой группой входов блока обработки прерываний, четырнадцатая группа разрядов - с первой группой информационных входов буферного регистра адреса, пятнадцатая группа разрядов - с первой группой входов контроллера оперативной памяти, шестнадцатая группа разрядов - с первой группой информационных входов буферного регистра данных, семнадцатая группа разрядов - с первой группой информационных входов буферного регистра связи, восемнадцатая группа разрядов - с первой группой входов блока выдачи сигналов синхронизации, девятнадцатая группа разрядов - с управляющим входом межбуферного регистра связи, первая группа, вторая группа выходов блока конвейерных регистров команд и данных соединены соответственно со второй группой входов блока дешифрации команд и второй группой информационных входов арифметико-логического устройства, первая группа информационных входов-выходов блока конвейерных регистров команд и данных соединена со второй группой информационных входов буферного регистра операнда, второй группой информационных входов буферного регистра данных, первой группой информационных входов-выходов модуля локальной памяти команд и данных, второй группой входов контроллера оперативной памяти, второй группой информационных входов-выходов буферного регистра связи и группой информационных входов модуля памяти микрокоманд, вторая группа информационных входов-выходов блока конвейерных регистров команд и данных соединена с третьей группой информационных входов арифметико-логического устройства, первой группой информационных входов-выходов блока буферного регистра связи, со второй группой входов блока модификации адреса памяти команд и данных, второй группой входов блока выдачи сигналов синхронизации и четвертой группой входов блока сравнения, выход дешифратора выбора конвейерных регистров соединен с группой управляющих входов блока конвейерных регистров команд и данных, первая группа, вторая группа управляющих выходов блока микропрограммного управления соединены соответственно с первой группой управляющих входов блока дешифрации команд и группой управляющих входов блока буферных регистров микрокоманд, третья группа выходов блока микропрограммного управления соединена с группой управляющих входов модуля памяти микрокоманд, группа выходов блока дешифрации команд, группа выходов блока буферных регистров микро-команд и первая группа выходов блока сравнения образуют вторую группу входов блока микропрограммного управления, выход модуля памяти микрокоманд соединен с информационным входом блока конвейерных регистров памяти микрокоманд, управляющий выход мультиплексора сигналов условий соединен с входом сигналов условий блока микропрограммного управления, выход дешифратора выбора регистров связи соединен со второй группой управляющих входов блока буферных регистров связи, группа выходов буферного регистра операнда соединена с четвертой группой информационных входов арифметико-логического устройства, управляющий выход арифметико-логического устройства и управляющий выход блока обработки прерываний соединены соответственно со вторым и третьим управляющим входами мультиплексора сигналов условий, группа информационных входов-выходов арифметико-логического устройства соединена с первой группой информационных входов-выходов межбуферного регистра связи и группой информационных входов-выходов буферного регистра данных, вторая группа входов-выходов блока модификации адреса памяти команд и данных соединена со вторыми группами информационных входов-выходов межбуферного регистра связи, буферного регистра адреса, блока обработки прерываний, выход группы буферного регистра адреса соединено третьей группой входов контроллера оперативной памяти, а выход которого соединен с управляющим входом модуля локальной памяти команд и данных, первая группа выхода блока обработки прерываний соединена с третьей группой входов блока сравнения, первая группа выходов блока выдачи сигналов синхронизации соединена со второй группой входов блока сравнения, выход синхронизатора соединен с синхронизирующими входами блока конвейерных регистров команд и данных, блока дешифрации команд, блока микропрограммного управления, блока буферных регистров микрокоманд, блока конвейерных регистров памяти микрокоманд, дешифратора выбора конвейерных регистров, буферного регистра операнда, арифметико-логического устройства, блока модификации адреса памяти команд и данных, блока сравнения, блока буферных регистров связи, буферного регистра данных, межбуферного регистра связи, буферного регистра адреса, блока обработки прерываний, блока выдачи сигналов синхронизации, буферного регистра связи, третья группа информационных входов-выходов буферного регистра связи является внешней магистралью данных управляющего процессора, со второй по (1+МN)-ю группы информационных входов-выходов блока буферных регистров связи, со второго по (1+МN)-ю управляющие выходы блока выдачи сигналов синхронизации и со второго по (1+МN)-ый управляющие входы блока обработки прерываний образуют соответственно группы информационных и управляющих входов-выходов управляющего процессора, управляющие разряды групп информационных и управляющих входов-выходов управляющего процессора объединены через МОНТАЖНОЕ ИЛИ с входом синхронизатора, второй выход дешифратора выбора регистров связи соединен со вторым входом синхронизатора.

Текст

Изобретение относится к области вычислительной техники и может быть использовано при построении систем широкого назначения на базе множества микропроцессоров. Наиболее близким к изобретению по технической сущности и достигаемому эффекту является устройство, содержащее группу из N микропроцессорных модулей (где N,=,

ДивитисяДодаткова інформація

Назва патенту англійськоюComputer system

Автори англійськоюBulavenko Oleh Mykolaiovych, Koval Valerii Mykolaiovych, Palahin Oleksandr Vasyliovych, Rabinovych Zinovii Lvovych, Averbukh Anatolii Baziliiovych, Balabanov Oleksandr Stepanovych, Didyk Petro Ivanovych, Liubarskyi Valerii Fedorovych, Mushka Vira Mykhailivna

Назва патенту російськоюВычислительная система

Автори російськоюБулавенко Олег Николаевич, Коваль Валерий Николаевич, Палагин Александр Васильевич, Рабинович Зиновий Львович, Авербух Анатолий Базильевич, балабанов Александр Степанович, Дидык Петр Иванович, Любарский Валерий Федорович, мушка Вера Михайловна

МПК / Мітки

МПК: G06F 15/16

Мітки: система, обчислювальна

Код посилання

<a href="https://ua.patents.su/18-19875-obchislyuvalna-sistema.html" target="_blank" rel="follow" title="База патентів України">Обчислювальна система</a>

Попередній патент: Лікер “берізка”

Наступний патент: Дробарка

Випадковий патент: Спосіб атипової резекції легені у хворих на обмежені форми хіміорезистентного туберкульозу