Пристрій керування дискретно-аналоговим індикатором

Номер патенту: 55344

Опубліковано: 17.03.2003

Автори: Олексенко Павло Феофанович, Грінберг Ісак Павлович, Сипко Микола Іванович, Бушма Олександр Володимирович, Беккер Вадим В'ячеславович, Бухнаєв Володимир Миколайович

Формула / Реферат

Устройство управления дискретно-аналоговым индикатором, содержащее блок управления младшими разрядами, выходы которого подключены к соответствующим первым входам дискретно-аналогового индикатора, тактовый генератор, выход которого подключен к управляющему входу блока управления младшими разрядами и управляющим входам n коммутаторов, преобразователь в единичный кол, выходы которого с первого по (n-1)-й подключены к первым информационным входам соответствующих коммутаторов, выходы которых соединены с соответствующими вторыми входами дискретно-аналогового индикатора, информационные входы блока управления младшими разрядами и входы преобразователя в единичный код являются соответственно первыми и вторыми входами устройства, отличающееся тем, что, с целью повышения надежности функционирования устройства, в него введены элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент НЕ, выход которого и выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены ко вторым информационным входам коммутаторов соответственно с первого по (n-1)-й, первый вход n-го коммутатора соединен с шиной логического нуля, первый выход преобразователя в единичный код соединен со входом элемента НЕ и первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, каждый выход преобразователя в единичный код со второго по (n-2)-й подключен к первому входу соответствующего и второму входу предыдущего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, (n-1)-й выход преобразователя в единичный код соединен со вторыми входами (n-2)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и n-го коммутатора.

Текст

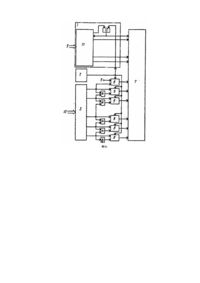

Изобретение относится к измерительной технике и может быть использовано при создании устройств отображения информации с дискретно-аналоговым индикатором (ДАИ). Цель изобретения - повышение надежности функционирования. На чертеже представлена функциональная схема устройства. Устройство управления ДАИ содержит блок 1 управления младшими разрядами, тактовый генератор 2, преобразователь 3 в единичный код, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 4, коммутаторы 5, элемент НЕ 6, ДАИ 7 и шину 8 логического нуля. На чертеже обозначены первые и вторые входы 9, 10 устройства. Блок 1 управления младшими разрядами может включать в себя блок 11 преобразования кода и элемент ИЛИ 12. Устройство работает следующим образом. На входы 9, 10 подается цифровой код величины, подлежащей отображению. На входы блока 1 поступает двоичный семисегментный код младшего десятичного разряда, а на входы преобразователя 3 двоичный семисегментный код старшего десятичного разряда. При логическом нуле на выходе тактового генератора 2 на выходах блока 1 формируется единичный код текущего числа младших разрядов, а при логической единице - единичный код максимального числа младших разрядов (в единичном коде числа а представлены количеством знаков "единица"). На выходах преобразователя 3 формируется единичный код текущего числа старших разрядов. Элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 4 анализируют логические потенциалы на выходах преобразователя 3, удельный вес которых отличается на единицу, и переключаются в единичное состояние при несовпадении этих сигналов. С помощью n-2 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 4 и элемента НЕ 6 происходит формирование единичного позиционного кода числа старших разрядов (в единичном позиционном коде число выражается порядковым номером знака "единица" в ряду знаков "нуль"). На первые сигнальные входы n коммутаторов 5 поступает единичный код числа старших разрядов, а на вторые - его единичный позиционный код. Управление коммутатором 5 производится с помощью тактового генератора 2. При логической единице, генерируемой последним, к ДАИ 7 с выходов коммутаторов 5 подводится единичный код числа старших разрядов, При логическом нуле на выходе тактового генератора 2 к ДАИ 7 подводится единичный позиционный код числа старших разрядов плюс единица. Таким образом, при логической единице на выходе тактового генератора 2 на ДАИ 7 возбуждаются элементы всех полных старших разрядов из числа участвующих в индикации, а при логическом нуле - остальные элементы одного неполного старшего разряда. Частота импульсов тактового генератора 2 выбрана выше критической частоты слияния мельканий, а их скважность равна двум, поэтому на ДАИ 7 наблюдается непрерывное свечение в виде линии, длина которой пропорциональна входной величине, заданной кодовым сигналом. Работу устройства рассмотрим на примере индикации числа "64" (на индикаторе 7 отображается 100 значений: от "00" до "99"). Число n коммутаторов 5 разно количеству шин старших разрядов в матрице ДАИ 7 (n = 10). На входы 9, 10 устройства поступает код "1011111, 0110011". При логическом нуле на втором входе элемента ИЛИ 12 входной код "0110011" трансформируется блоком 1 в код "0000011111", а при логической единице - в код "1111111111". На вход преобразователя 3 подводится код "1011111", что приводит к появлению на его выходных шинах кода "000111111". На выходе элемента НЕ 6 устанавливается логический нуль, поскольку его вход связан с выходом преобразователя 3 с наименьшим удельным весом. На выходах n2 = 8 элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 4 формируется код "00100000". В результате на первых входах коммутаторов 5 устанавливается код "0000111111", а на вторых входа х - код "0001000000". При логической единице на управляющих входа х коммутаторов 5 на их выходах будет действовать кодовая комбинация, установленная на первых входах, то есть "0000111111". При логическом нуле на их управляющих входа х на выходах коммутаторов 5 устанавливается кодовая комбинация, подведенная на вторые входы: "0001000000". Тактовый генератор 2 создает импульсную последовательность с частотой 100Гц при скважности два. Таким образом, во время действия импульса тактового генератора 2 (потенциала логической единицы) на шины ДАИ 9 подводятся: код "0000111111" по старшим разрядам и код "1111111111" по младшим разрядам, что приводит к возбуждению шести полных старши х разрядов (60 светодиодов) из числа участвующи х в индикации. При нулевом логическом уровне на выходе тактового генератора 2 (во время паузы) на шины ДАИ 7 поступают: код "0001000000" по старшим разрядам и код "0000011111" по младшим разрядам, что обеспечивает возбуждение пяти элементов седьмого старшего разряда (5 светодиодов). Поскольку частота смены тактов выбрана выше критической частоты слияния мельканий, а время возбуждения двух гр упп светодиодов одинаково, оператор наблюдает на ДАИ 7 равномерно светящуюся линию из 60 + 5 = 65 светодиодов, соответствующую входному коду числа "64". При числе "00" на ДАИ 7 горит один светодиод. Таким образом, обеспечивается уменьшение числа элементов устройства. Кроме того, последовательное формирование кодов, с помощью которых возбуждаются старшие разряды ДАИ, позволяет получить топологически плоский граф электрической схемы. Все это и обусловливает повышение надежности функционирования. Фіг.

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for controlling discrete-analogue indicator

Автори англійськоюBushma Oleksandr Volodymyrovych, Oleksenko Pavlo Feofanovych, Sypko Mykola Ivanovych

Назва патенту російськоюУстройство управления дискретно-аналоговым индикатором

Автори російськоюБушма Александр Владимирович, Олексенко Павел Феофанович, Сипко Николай Иванович

МПК / Мітки

МПК: G01R 13/00

Мітки: дискретно-аналоговим, пристрій, керування, індикатором

Код посилання

<a href="https://ua.patents.su/2-55344-pristrijj-keruvannya-diskretno-analogovim-indikatorom.html" target="_blank" rel="follow" title="База патентів України">Пристрій керування дискретно-аналоговим індикатором</a>

Попередній патент: Пристрій для відображення вимірювальної інформації

Наступний патент: Пристрій індикації вимірювального приладу

Випадковий патент: Спосіб виготовлення труби пластмасової, армованої