Аналого-цифровий обчислювальний пристрій

Номер патенту: 15467

Опубліковано: 30.06.1997

Автори: Драбич Петро Петрович, Джала Роман Михайлович, Яворський Ігор Миколайович

Формула / Реферат

Аналого-цифровий обчислювальний пристрій, який складається з регістра послідовного наближення, першого цифроаналогового перетворювача і компаратора, причому вхід дозволу регістра під'єднаний до шини нулевого потенціалу, вхід послідовного вводу вхідних даних регістра підключений до виходу компаратора, перший вхід котрого з'єднаний з виходом першого цифроаналогового перетворювача, цифровий вхід котрого під'єднаний до інформативного виходу регістра, що є виходом пристрою, а тактовий вхід регістра є тактовим входом пристрою, який відрізняється тим, що в нього додатково введені перший і другий елементи затримки, логічний елемент АБО, інвертор напруги, адресний лічильник, тригер, двоканальний комутатор, здвоєний мультиплексор і другий цифроаналоговий перетворювач, а також вхід установки в нуль, дві групи по n аналогових входів, при цьому перший вхід елемента АБО з'єднаний з входом установки в нуль адресного лічильника і є входом установки в нуль пристрою, другий вхід логічного елемента АБО під'єднаний до виходу сигналу переповнення адресного лічильника, до виходу логічного елемента АБО під'єднаний вхід установки в нуль тригера, D-вхід тригера підключений до шини потенціалу логічної одиниці, об'єднані тактові входи тригера і адресного лічильника, а також вхід синхронізації другого цифроаналогового перетворювача через інвертор напруги підключені до виходу сигнала закінчення перетворення регістра, куди також через перший елемент затримки під'єднаний його стартовий вхід, до інформативного виходу регістра під'єднаний також цифровий вхід другого цифроаналогового перетворювача, аналогові входи першого і другого цифроаналогових перетворювачів з'єднані відповідно з першим і другим виходами здвоєного мультиплексора, другий вхід компаратора об'єднаний з виходом двоканального комутатора, перший вхід котрого з'єднаний з виходом двоканального комутатора, перший вхід котрого з'єднаний з виходом другого цифроаналогового перетворювача, до виходу тригера підключений вхід управління двоканального комутатора, вхід синхронізації першого цифроаналогового перетворювача через другий елемент затримки з'єднаний з тактовим входом регістра, вхід управління здвоєного мультиплексора підключений до адресного виходу адресного лічильника, другий вхід двоканального комутатора і n - 1 входів першої групи входів здвоєного мультиплексора є першою групою п аналогових входів пристрою, перший вхід першої групи входів здвоєного мультиплексора під'єднаний до шини нулевого потенціалу, друга група n входів здвоєного мультиплексора є другою групою n аналогових входів пристрою.

Текст

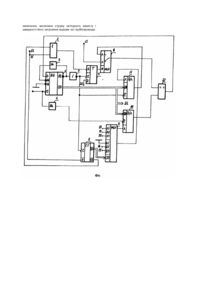

Винахід відноситься до вимірювальної і обчислювальної техніки, призначений для перемноження, піднесення до степені і ділення аналогових сигналів і може бути використаний в апаратурі для корозійних обстежень нафто-, газо- і продуктопроводів, а також в апаратурі для пошуку і розвідки родовищ корисних копалин з допомогою зондуючих електромагнітних полів. Найбільш близьким по технічній суті до заявлюваного технічного рішення є аналогоцифровий перетворювач, який складається з регістра послідовного наближення, цифроаналогового перетворювача і компаратора напруг, причому вхід дозволу регістра послідовного наближення приєднаний до шини нулевого потенціалу, тактовий вхід регістра є тактовим входом пристрою, стартовий вхід регістра об'єднаний з виходом сигналу закінчення перетворення, вхід послідовного вводу вхідних даних підключений до виходу компаратора, вихід регістра послідовного наближення з'єднаний із входом цифроаналогового перетворювача, аналоговий вихід якого з'єднаний з першим входом компаратора, а другий вхід останнього є аналоговим входом пристрою (Застосування інтегральних мікросхем в електронній обчислювальній техніці: Довідник / Р.В. Данілов і інші. - М.: Радіо і связь / Під ред. Б.Н. Файзулаєва, Б.В.Тарабрина, 1987. - С.113 - прототип). Прототип має теж обмежені функціональні можливості, тому що забезпечує лише перетворення постійної напруги в число і може бути використаний також для обчислення відношення двох напруг. Задачею заявленого пристрою е розширення функціональних можливостей. Для вирішення цієї задачі в аналого-цифровий обчислювальний пристрій, який складається з регістра послідовного наближення, першого цифроаналогового перетворювача і компаратора, причому вхід дозволу регістра під'єднаний до шини нулевого потенціалу, вхід послідовного вводу вхідних даних регістра підключений до виходу компаратора, перший вхід котрого з'єднаний з виходом першого цифроаналогового перетворювача, цифровий вхід котрого під'єднаний до інформативного виходу регістра, що є виходом пристрою, а тактовий вхід регістра є тактовим входом пристрою, додатково введені перший і другий елементи затримки, логічний елемент АБО, інвертор напруги, адресний лічильник, тригер, двоканальний комутатор, здвоєний мультиплексор і другий цифроаналоговий перетворювач, а також вхід установки в нуль, дві групи по п аналогових входів, при цьому перший вхід елемента АБО з'єднаний з входом установки в нуль адресного лічильника і є входом установки в нуль пристрою, другий вхід логічного елемента АБО підключений до виходу сигналу переповнення адресного лічильника, до виходу логічного елемента АБО під'єднаний вхід установки в нуль тригера, D-вхід тригера підключений до шини потенціалу логічної одиниці, об'єднані тактові входи тригера і адресного лічильника, а також вхід синхронізації другого цифроаналогового перетворювача через інвертор напруги підключені до виходу сигнала закінчення перетворення регістра, куди також через перший елемент затримки під'єднаний його стартовий вхід, до інформативного виходу регістра під'єднаний також цифровий вхід другого цифроаналогового перетворювача, аналогові входи першого і другого цифроаналогових перетворювачів з'єднані відповідно з першим і другим виходами здвоєного мультиплексора, другий вхід компаратора об'єднаний з виходом двоканального комутатора, перший вхід котрого з'єднаний з виходом другого цифроаналогового перетворювача, до виходу тригера підключений вхід управління двоканального комутатора, вхід синхронізації першого цифроаналогового перетворювача через другий елемент затримки з'єднаний з тактовим входом регістра, вхід управління здвоєного мультиплексора підключений до адресного виходу адресного лічильника, другий вхід двоканального комутатора і n - 1 входів першої групи входів здвоєного мультиплексора є першою групою п аналогових входів пристрою, перший вхід першої групи входів здвоєного мультиплексора під'єднаний до шини нулевого потенціалу, друга група n входів здвоєного мультиплексора є другою групою n аналогових входів пристрою. Додатково введені в аналого-цифровий обчислювальний пристрій елементи широко використовуються в різних інформаційновимірювальних та обчислювальних пристроях, але окремо вони не володіють властивостями, які забезпечили б вирішення поставленої задачі. Такими властивостями володіє лише їх запропонована сукупність, тобто, вступаючи у взаємодію, признаки сукупності надають заявленому пристрою нову якість, яка відповідає критерію "суттєві відмінності". На кресленні (фіг.) показана структурна схема заявленого аналого-цифрового обчислювального пристрою. Аналого-цифровий обчислювальний пристрій складається з регістра послідовного наближення 1, логічного елемента АБО 2, першого і другого елементів затримки 3, 4, інвертора напруги 5, адресного лічильника 6, тригера 7, двоканального комутатора 8, здвоєного мультиплексора 9, першого і другого цифроаналогових перетворювачів 10, 11 і компаратора 12, а також має вхід установки в нуль 13, тактовий вхід 14, першу групу із n аналогових входів 15, 16, 17, другу групу із n аналогових входів 18, 19, 20 та цифровий вихід 21 і шину потенціалу логічної одиниці 22. Вхід дозволу регістра 1 приєднаний до шини нулевого потенціалу, а тактовий вхід регістра 1 є тактовим входом пристрою 14. До тактового входу регістра 1 через елемент затримки 4 підключений також вхід синхронізації першого цифроаналогового перетворювача 10, цифровий вхід якого об'єднаний з аналогічним входом другого цифроаналогового перетворювача 11 і підключений до інформативного виходу регістра 1, який є виходом пристрою 21, стартовий вхід регістра 1 через перший елемент затримки 3 під'єднаний до свого виходу сигналу закінчення перетворення. До виходу сигналу закінчення перетворення регістра 1 через інвертор напруги 3 також під'єднані тактові входи тригера 7 і адресного лічильника 6, а також вхід синхронізації цифроаналогового перетворювача 11, D-вхід тригера 7 приєднаний до шини потенціалу логічної одиниці. Входи установки в нуль адресного лічильника 8 і перший вхід логічного елемента АБО 2 об'єднані і підключені до шини 13. Другий вхід логічного елемента АБО 2 з'єднаний з виходом сигналу переповнення адресного лічильника 6. Вихід логічного елемента АБО 2 з'єднаний з входом установки в нуль тригера 7. До виходу тригера 7 підключений вхід управління двоканального комутатора 8, перший аналоговий вхід котрого з'єднаний з виходом другого цифроаналогового перетворювача 11. Другий вхід двоканального комутатора 8 і n - 1 вхід першої групи входів здвоєного мультиплексора 9 є першою групою п аналогових входів пристрою 15, 16, 17. Аналогові входи першого і другого цифроаналогових перетворювачів 10 і 11 під'єднані відповідно до першого і другого виходів здвоєного мультиплексора 9. Вихід першого цифроаналогового перетворювача 10 і вихід двоканального комутатора 8 підключені до першого і другого входів компаратора 12, вихід котрого з'єднаний з входом послідовного вводу даних регістра 1. Вихід адресного лічильника 6 підключений до входу управління здвоєного мультиплексора 9. Вихід другого цифроаналогового перетворювача 11 з'єднаний з першим входом двоканального комутатора 8. Пристрій реалізує функцію типу де на кресленні - значення вхідних напруг, - результат обчислення в двійковому коді. Пристрій працює наступним чином. Нехай на входи 15, 16, 17 поступають напруги а на входи 18, 19, 20 - постійні напруги Перед запуском пристрою на його вхід 13 подається короткий додатній імпульс, під дією якого обнуляються адресний лічильник 6 і тригер 7. При цьому на виході лічильника 6 формується нулевий адрес, під дією якого відкриваються канали і здвоєного мультиплексора 9. Під дією сформованого на виході тригера потенціалу логічного нуля двоканальний комутатор 8 знаходиться в положенні, показаному на кресленні. При надходженні потенціалу логічного нуля на шину 14 запускається регістр 1 і розпочинається перший цикл перетворення аналогових сигналів і які подаються з допомогою двоканального комутатора 8 і мультиплексора 9 відповідно на перший вхід компаратора 12 і аналоговий вхід цифроаналогового перетворювача 10. Перетворення аналогових сигналів в двійковий код здійснюється по методу порозрядного зважування. Під дією кожного додатного фронту тактових імпульсів, що поступають на тактовий вхід 14 регістра 1, останній виробляє випробувальний цифровий код починаючи з кода який з допомогою тактових імпульсів записується у вхідний регістр цифроаналогового перетворювача 10, перемножується в ньому на напругу перетворюючись при цьому в аналоговий сигнал Далі порівнюється в компараторі 12 з аналоговим сигналом Якщо випробовувальний сигнал менший від компаратор 12 виробляє на своєму виході потенціал логічної одиниці, в протилежному випадку - логічного нуля. Сигнал з виходу компаратора 12 поступає на вхід регістра 1, встановлюючи старший розряд регістра 1 у стан, який відповідає аналоговому сигналу при додатнім імпульсі синхронізації. Одночасно наступний більш молодший розряд регістра 1 встановлюється в стан логічного нуля. Таким чином, після двох тактових імпульсів на виході регістра 1 встановлюється код де - значення в старшому розряді регістра 1, яке відповідає рівню аналогового сигналу Після трьох тактових імпульсів визначиться 10 й розряд регістра 1, а повний цикл перетворення здійсниться за 13 тактових імпульсів, Закінчення перетворення аналогових сигналів відображається від'ємним перепадом напруги на виході регістра 1, який через елемент затримки 3 подається на стартовий вхід регістра 1 і, через інвертор напруги 5, - на тактові входи адресного лічильника 6 і тригера 7. Тригер 7 переводиться в стан логічної одиниці, на виході адресного лічильника 6 формується наступний адрес для відкривання каналів і здвоєного мультиплексора 9, а результат перетворення записується у вхідний регістр цифроаналогового перетворювача 11. В другому циклі перетворення на перший і другий входи компаратора 12 подаються відповідно напруги і Після 13 тактових імпульсів на виході регістра 1 сформується число яке під дією сигналу закінчення перетворення регістра 1 записується в вхідний регістр другого цифроаналогового перетворювача 11. Сигналом закінчення перетворення формується наступний адрес для мультиплексора 9 і знову запускається регістр 1. В третьому циклі перетворення на перший і другий входи компаратора 12 подаються відповідно напруги і Під дією наступних 13 тактових імпульсів на виході регістра 1 сформується число Число записується у вхідний регістр цифроаналогового перетворювача 11, знову розпочинається наступний цикл, т.д. Після перебору всіх адресів на виході переповнення адресного лічильника 6 появляється короткий додатній імпульс, який обнуляє тригер 7, а на адресному виході лічильника 6 знову формується нулевий адрес. Комутатор 8 і мультиплексор 9 повертаються в початковий стан і серія з циклів знову повторюється. Таким чином за циклів на виході 21 пристрою послідовно сформуються двійкові числа При запропонований пристрій може успішно використовуватись в апаратурі для корозійних обстежень магістральних нафто-, газо- і продуктопроводів з метою вимірювання глибини їх залягання, величини струму катодного захисту і швидкості його затухання вздовж осі трубопровода.

ДивитисяДодаткова інформація

Назва патенту англійськоюAnalog-to-digital computing unit

Автори англійськоюDrabych Petro Petrovych, Dzhala Roman Mykhailovych, Yavorskyi Ihor Mykolaiovych

Назва патенту російськоюАналого-цифровое вычислительное устройство

Автори російськоюДрабич Петр Петрович, Джала Роман Михайлович, Яворский Игорь Николаевич

МПК / Мітки

МПК: H03M 1/00

Мітки: пристрій, аналого-цифровий, обчислювальній

Код посилання

<a href="https://ua.patents.su/3-15467-analogo-cifrovijj-obchislyuvalnijj-pristrijj.html" target="_blank" rel="follow" title="База патентів України">Аналого-цифровий обчислювальний пристрій</a>

Попередній патент: Спосіб наплавки металевої поверхні

Наступний патент: Цифровий синтезатор частоти

Випадковий патент: Спосіб об'єктивної рентгенограметричної оцінки товщини шару запальної інфільтрації при гнійно-деструктивних ускладненнях уражень легень у хворих на снід