Цифровий синтезатор частоти

Номер патенту: 15468

Опубліковано: 30.06.1997

Автори: Іоненко Володимир Єлісійович, Майборода Олег Володимирович

Формула / Реферат

Цифровой синтезатор частоты, содержащий накапливающий сумматор, устройство управляемой задержки, выход которого соединен с тактовым входом накапливающего сумматора и является выходом устройства, а управляющий вход соединен с первым выходом накапливающего сумматора, отличающийся тем, что введен двоичный счетчик с постоянной емкостью, равной где - разрядность двоичного счетчика, вход которого является тактовым входом устройства, схема сравнения, выход которой соединен с входом устройства управляемой задержки, первый вход схемы сравнения соединен с выходом двоичного счетчика, а второй вход ее соединен со вторым выходом накапливающего сумматора, вход которого является входом установки длительности периода синтезируемого сигнала устройства.

Текст

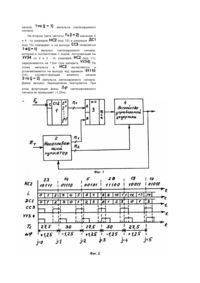

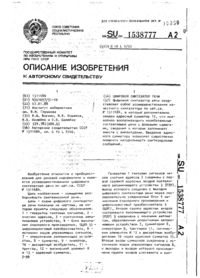

Изобретение относится к радиотехнике, в частности к преобразованию цифрового кода частоты в аналоговый двухуровневый сигнал соответствующей частоты. Известен цифровой синтезатор частоты на основе накапливающего сумматора [1]. Синтезатор содержит последовательно включенные накапливающий сумматор и счетчик-делитель. Достоинством устройства является его простота. Недостатком устройства является большая величина фазовых флуктуации на выходе накапливающего сумматора из-за ограниченного быстродействия последнего. Уменьшение фазовых флуктуации с помощью счетчика-делителя ограничивает величину и диапазон синтезуемых частот. Известен цифровой синтезатор частоты на основе накапливающего сумматора с коррекцией временного положения импульса переноса сумматора [2]. Синтезатор содержит накопитель кодов (накапливающий сумматор), блок управления, устройство управляющей задержки, делитель частоты (счетчик-делитель). Достоинством устройства является возможность уменьшения уровня фазовых флуктуации без уменьшения величины и диапазона синтезируемых частот. Недостатком устройства является его сложность, вызванная использованием в синтезаторе блока управления с достаточным быстродействием для установки величины задержки в устройстве управляемой задержки. Наиболее близким по технической сущности к предлагаемому изобретению является цифровой синтезатор частоты [3], содержащий опорный генератор, блок исключения импульсов, делитель с переменным коэффициентом деления, устройство управляемой задержки, накапливающий сумматор и делитель кода. Работа устройства основана на делении тактовой частоты на переменный коэффициент равный отношению тактовой и синтезируемой частот. Причем в коэффициенте выделяются целая и дробная части. Целая часть поступает на делитель с переменным коэффициентом деления и используется для установки коэффициента деления, равного целой части коэффициента Дробная часть поступает на накапливающий сумматор, в котором вычисляется требуемая задержка сигнала, поступающего с делителя с переменным коэффициентом деления. Достоинством устройства является снижение уровня фазовых флуктуации без уменьшения величины и диапазона синтезируемых частот за счет корректировки временного положения выходных импульсов. Недостатком устройства является его сложность, которая связана с использованием в синтезаторе блока исключения импульсов, делителя с переменным коэффициентом деления и устройства управляемой задержки с большим числом градаций (каскадов), Блок исключения импульсов используется для исключения импульсов из опорной тактовой последовательности. Делитель с переменным коэффициентом деления предназначен для деления "прореженной" тактовой частоты, поступающей с блока исключения импульсов, на число, определяемое делителем кодов. Устройство управляемой задержки должно иметь большое число каскадов при заданной разрешающей способности (величине фазовых флуктуации) из-за большого диапазона регулируемых задержек, который должен быть равен периоду тактовой частоты. Возможности по уменьшению периода тактовой частоты (увеличению тактовой частоты) ограничиваются быстродействием делителя с переменным коэффициентом деления. Низкие динамические характеристики последнего вызваны необходимостью установки требуемого коэффициента деления. В основу изобретения поставлена задача создать такой цифровой синтезатор частоты, в котором за счет использования вычислений по модулю числа большего, чем максимально возможный период синтезируемого сигнала выведены двоичный счетчик с постоянной емкостью, равной где - разрядность двоичного счетчика, и схема сравнения, а также изменено функциональное назначение накапливающего сумматора, что позволило максимально повысить тактовую частоту устройства (уменьшить период тактовой частоты до минимальной величины), а следовательно, уменьшить диапазон регулируемых задержек (уменьшить число градаций при заданной разрешающей способности) устройства управляемой задержки и за счет этого упростить устройство. Для этого в цифровой синтезатор частоты, содержащий накапливающий сумматор, устройство управляемой задержки, выход которого соединен с тактовым входом накапливающего сумматора и является выходом устройства, а управляющий вход соединен с первым выходом накапливающего сумматора, введены двоичный счетчик с постоянной емкостью, равной где - разрядность двоичного счетчика, вход которого является тактовым входом устройства, схема сравнения, выход которой соединен с входом устройства управляемой задержки, первый вход соединен с выходом двоичного счетчика, а второй вход соединен со вторым выходом накапливающего сумматора, вход которого является входом установки длительности периода синтезируемого сигнала устройства. Введение двоичного счетчика с постоянной емкостью, равной дало возможность вести отсчет текущего времени по модулю числа, равного где - период тактовой частоты с дискретностью, равной (подсчет числа периодов тактовой частоты по модулю Использование двоичного счетчика с постоянной емкостью дало возможность максимально повысить его динамические характеристики, а значит максимально повысить тактовую частоту устройства (уменьшить период тактовой частоты до минимального значения), что уменьшило диапазон регулируемых задержек, а следовательно, при заданной разрешающей способности позволило уменьшить число градаций устройства управляемой задержки. Использование входа накапливающего сумматора в качестве входа установки длительности периода синтезируемого сигнала устройства позволило применить накапливающий сумматор для вычисления времени, соответствующего моменту начала синтезируемого сигнала периода по модулю числа, равного где - разрядность накапливающего сумматора, шаг перестройки периода синтезируемого сигнала. Отметим, что в прототипе накапливающий сумматор используется для вычисления по дробной части коэффициента деления величины задержки выходного сигнала делителя с переменным коэффициентом деления. Введение схемы сравнения позволило путем непрерывного анализа кода текущего времени, вырабатываемого двоичным счетчиком, и кода времени начала периода синтезируемого сигнала, поступающего от накапливающего сумматора, выработать в момент их совпадения импульс, который через устройство управляемой задержки поступает на тактовый вход накапливающего сумматора и выход устройства. Авторам неизвестны технические решения, имеющие совокупность признаков, совпадающих с совокупностью отличительных признаков предлагаемого технического решения. На фиг.1 представлена схема электрическая структурная цифрового синтезатора частоты; на фиг.2 - временная диаграмма работы устройства. Цифровой синтезатор частоты содержит двоичный счетчик 1 с постоянной емкостью, равной где - разрядность двоичного счетчика, вход которого является тактовым входом устройства, схему сравнения 3, первый вход которой соединен с выходом двоичного счетчика 1, накапливающий сумматор 2, вход которого является входом установки длительности периода синтезируемого сигнала устройства, второй выход соединен с вторым входом схемы сравнения, и устройство управляемой задержки 4, вход которого соединен с выходом схемы сравнения 3, выход соединен с тактовым входом накапливающего сумматора и является выходом устройства, а управляющий вход соединен с первым выходом накапливающего сумматора 2. Двоичный счетчик 1, схема сравнения 3, накапливающий сумматор 2 легко могут быть реализованы на цифровых ИС серий 100, 1500, 530, 533 и др. Устройство управляемой задержки 4 может быть реализовано, например, на многоотводной линии задержки, отводы которой в соответствии с управляющим кодом коммутируются с помощью мультиплексора. Работа устройства основана на вычислении в двоичном счетчике сумматоре начала и накапливающем текущего времени и времени периода синтезируемого сигнала соответственно, их анализа в схеме сравнения формировании выходного импульса при их совпадении и его задержке в синтезируемого сигнала. В ведется отсчет текущего времени с дискретностью, равной периоду тактовой частоты (подсчет числа периодов тактовой частоты Причем счет ведется по модулю числа При этом емкость равна Удобно выбрать модуль где этом случае формируемый код в так, чтобы емкость - разрядность В текущего времени такте опорной частоты равен где - вычет числа (остаток от деления числа по модулю на В по каждому выходному импульсу происходит вычисление времени, соответствующего моменту начала периода (выходного импульса) синтезируемого сигнала. Причем вычисления также выполняются по модулю числа а емкость равна где - шаг перестройки периода синтезируемого сигнала. Удобно выбрать так, чтобы емкость где - разрядность В этом случае код периода синтезируемого сигнала загружаемый в равен где - период синтезируемого сигнала. Код времени начала формирования выходного импульса равен где - порядковый номер выходного импульса. При такой работе устройства выполнение условия (1) означает, что разность между текущим временем, формируемым и вычисленным в временем начала периода синтезируемой частоты не превышает величины модуля Поэтому ведение вычислений по модулю в и упрощает устройство и не приводит к искажению результатов вычислений и сравнения положение кодов выходного и импульса Временное определяется моментом времени, когда совпадут код и старших разрядов кода Эту функцию выполняет Временное положение импульса на выходе определяется с точностью, не устройстве управляемой задержки в соответствии с управляющим кодом, поступающим из Особенностью устройства является использование в и вычислений по модулю числа который выбирается из условия: превышающей Из-за ограниченных динамических характеристик (например, 4 - х разрядный двоичный счетчик 1500ИЕ136 имеет время установки разрядов около 2нс) эта точность не превышает ±1нс. Для более точной временной привязки выходных импульсов синтезируемого сигнала в пределах интервала после в где устройстве максимально возможный период используется управляемое разрядами - разрядность управляющей шины , где (число градаций рано В этом случае временная привязка выходного импульса устройства производится с погрешностью не более Величина периода равна синтезируемого сигнала импульса на выходе Отметим, что синтезируемого сигнала ограничивается быстродействием и равна времени выполнения операции сложения в нем. Например, при реализации 16-разрядного с использованием схемы ускоренного переноса на элементах серии 100 и 500 (максимальная частота синтезируемого сигнала на элементах серии 533 В соответствии с (6) диапазон синтезируемых частот лежит в пределах При больших значениях можно упростить периода можно флуктуации необходимо использовать Рассмотрим работу устройства на примере для следующих его параметров: Шаг перестройки в фазовых флуктуации синтезируемого сигнала, которая не превышает величины Таким образом, старших разрядов определяют временное положение выходного импульса синтезируемого сигнала во временном превышающей с погрешностью (временное не положение выходного импульса на выходе а средних разряда следующих после старших разрядов, определяют временное положение выходного импульса в пределах временного интервала с погрешностью не более (период - разрядность - разрядность - разрядность управляющей шины (разрешающая способность 2,5нс); - время выполнения операции сложения в При принятых параметрах соответствии с (1) и (2) модуль устройства равен в Диапазон синтезируемых частот в соответствии с (7) лежит в пределах Шаг перестройки соответствии с (9) равен периода в необходимо синтезировать в сигнал с периодом Из выражения (6) получаем значение кода равен Дискретность установки кода текущего времени и задержки в определяют величину интервале частота Величина фазовых флуктуации соответствии с (10) не превышает синтезируемого сигнала. периода тактовая неравенство (7) определяет точность установки (частоты фазовых исключить из устройства, а реализовать, например, на счетчике 1500ИН136, время установки разрядов которого не превышает 2нс. При более жестких требованиях к величине фазовых Пусть Емкость величине флуктуации Величина минимально возможного периода при (временное положение Для рассматриваемого примера временная диаграмма работы устройства приведена на фиг.2. На диаграмме показаны (соответственно сверху вниз) выходы в десятичном и двоичном кодах, порядковый номер периода тактовой частоты выход в десятичном коде, выход выход длительность синтезированного периода сигнала (нс), величина фазовых флуктуации сигнала (нс) и порядковый номер выходного импульса синтезированного сигнала. Работа устройства начинается с установки на входе кода и обнулении и Установка или в любое другое состояние приведет к соответствующему сдвигу начальной фазы синтезируемого сигнала. При обнулении и срабатывает и на выходе появляется импульс синтезируемого сигнала с нулевой задержкой в соответствии с кодом поступающим со 2 и 3 - го разрядов Этим импульсом код загружается в и на его выходе появляется код времени соответствующий моменту начала сигнала. импульса синтезируемого На втором такте частоты значения 5 и 4 - го разрядов (код 10) и разрядов (код 10) совпадают и на выходе появляется импульс синтезируемого сигнала, который в соответствии с кодом, поступающим на со 2 и 3 - го, разрядов (код 11), задерживается на 7,5нс (три дискрета По этому импульсу в вычисляется и устанавливается на выходе код времени (14), соответствующий моменту начала импульса синтезируемого сигнала. Далее процесс периодически повторяется. При этом флуктуация фазы сигнала не превышает ±1,25нс. синтезированного

ДивитисяДодаткова інформація

Назва патенту англійськоюDigital frequency synthesizer

Автори англійськоюIonenko Volodymyr Oleksiiovych, Maiboroda Oleh Volodymyrovych

Назва патенту російськоюЦифровой синтезатор частоты

Автори російськоюИоненко Владимир Алексеевич, Майборода Олег Владимирович

МПК / Мітки

МПК: H03B 19/00

Мітки: синтезатор, цифровий, частоти

Код посилання

<a href="https://ua.patents.su/4-15468-cifrovijj-sintezator-chastoti.html" target="_blank" rel="follow" title="База патентів України">Цифровий синтезатор частоти</a>

Попередній патент: Аналого-цифровий обчислювальний пристрій

Наступний патент: Спосіб визначення змочуваності порід-колекторів

Випадковий патент: Спосіб ранньої діагностики відторгнення розщеплених вільних аутодермотрансплантатів у постраждалих від глибоких опіків