Оптоелектронний дешифратор-комутатор

Номер патенту: 25117

Опубліковано: 30.10.1998

Автори: Одобецький Сергій Іванович, Тарновський Микола Геннадійович, Горбачук Ігор Павлович, Осадчук Володимир Степанович

Формула / Реферат

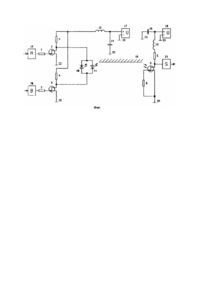

Оптоэлектронный дешифратор-коммутатор, содержащий первый источник питания, минус которого подключен к первой общей шине, первый и второй полевые транзисторы, истоки которых подключены к первой общей шине, отличающийся тем, что в него введены первый - шестой резисторы, первый и второй светодиоды, фототранзистор, отражающие поверхность, первая и вторая катушки индуктивности, первый и второй конденсаторы, переключающий элемент и второй источник питания, причем затвор первого транзистора подключен ко второму выводу первого резистора, сток соединен с катодом первого светодиода, с анодом второго светодиода и через третий резистор и первую катушку индуктивности подключен к плюсу первого источника питания, затвор второго транзистора подключен ко второму выводу второго резистора, сток соединен с анодом первого светодиода, с катодом второго светодиода и через четвертый резистор и первую катушку индуктивности подключен к плюсу первого источника питания, отражающая поверхность направляет излучение светодиода на затвор фототранзистора, исток которого соединен со второй общей шиной, затвор через шестой резистор подключен ко второй общей шине, а сток соединен с переключающим элементом и через пятый резистор и вторую катушку индуктивности подключен к плюсу второго источника питания, плюс первого источника питания через первый конденсатор подключен к первой общей шине, плюс второго источника питания через второй конденсатор подсоединен ко второй общей шине, с которой соединен минус второго источника питания.

Текст

Изобретение относится к электронной коммутационной технике и может быть использовано в устройства х коммутации каналов связи ЭВМ. Существует ряд устройств, предназначенных для коммутации сообщений, выполняемой с помощью управляющих кодов (слов). Известен коммутатор для многокаскадных коммутирующи х систем, который осуществляет поиск всех требуемых каналов связи с помощью многоразрядных кодов (Авт. св. СССР №1582345, кл. H03K17/00, 1988). Недостатками такого устройства является увеличение времени идентификации адреса получателя информации вследствие. применения значительных аппаратных ресурсов, предназначенных для распознавания адреса, а также невысокая помехоустойчивость. Также известен многоканальный коммутатор, применяемый в автоматических системах сбора информации и осуществляющий подключение источников информации к общей информационной шине (Авт. св. СССР №1541764, кл. H03K17/00, 1988). Недостаток этого устройства заключается в том, что выбор источников информации производится в жесткой последовательности, что исключает возможность в любой момент времени подключить к общей информационной шине любой необходимый информационный источник. Наиболее близким по технической сущности к предлагаемому изобретению является компаратор на КМОП-элементах для сравнения двух 1-разрядных слов (Патент Японии №2 41212, кл. H03K19/21, 1985), содержащий I трехтранзисторных логических схем ИСКЛЮЧАЮЩЕЕ ИЛИ, в которых исток первого транзистора соединен с выходом 1 - го разряда одного из двух сравниваемых слов и с затвором тарою транзистора, исток второго транзистора подключен к выходу I-го разряда другого слова и к затвору первого транзистора, стоки первого и второго транзисторов соединены между собой и подключены к стоку третьего транзистора, затвор которого соединен с истоком и образует выход такой трехтранзисторной логической схемы. Выходы всех логических схем объединены и подключены к истоку четвертого транзистора, затвор которого соединен с затвором пятого транзистора и подключен к источнику опорного напряжения, сток четвертого транзистора подключен к истоку пятого транзистора, к истоку шестого транзистора и ко входу инвертора, стоки пятого и шестого транзисторов соединены между собой и подключены к плюсу источника питания, выход инвертора соединен с затвором шестого транзистора и является выходом устройства. Четвертый и пятый транзисторы образуют схему управления, которая регистрирует совпадение/несовпадение в логических схемах. Фиксирует результат в схеме-защелке, которая образована инвертором и шестым транзистором, и определяет совпадение/несовпадение двух Iразрядных слов. Недостатком такого устройства является необходимость использования дополнительного источника опорного напряжения, ограниченное быстродействие в результате применения дополнительного коммутирующе го каскада и использования КМОП-транзисторов, низкая помехоустойчивость, поскольку вход и выход данного устройства электрически связаны между собой. В основу изобретения поставлена задача создания оптоэлектронного дешифраторакоммутатора, в котором за счет введения новых элементов и связей между ними обеспечивается взаимодействие оптического излучения с полупроводниковым коммутирующим элементом, что позволяет повысить достоверность распознавания совпадения двух сравниваемых кодов за счет использования светодиодов, как "индикаторов" совпадения/несовпадения, увеличить помехоустойчивость устройства, в результате применения оптической развязки между входными и выходным сигналами, а также повысить быстродействие устройства за счет использования оптоэлектронного коммутирующего элемента. Поставленная задача достигается тем, что в оптоэлектронный дешифратор-коммутатор, содержащий первый источник питания, минус которого подключен к первой общей шине, первый и второй полевые транзисторы, истоки которых подключены к первой общей шине, введены первый - шестой резисторы, первый и второй светодиоды, фототранзистор» отражающая поверхность, первая и вторая, катушки индуктивности, первый и второй конденсаторы, переключающий элемент и второй источник питания, причем затвор первого транзистора подключен ко второму выводу первого резистора, сток соединен с катодом первого светодиода, с анодом второго светодиода и через. третий резистор и первую катушку индуктивности подключены к плюсу первого источника питания, затвор второго транзистора подключен ко второму, выводу второго резистора, сток соединен с анодом первогосветодиода, с катодом второго светодиода и через четвертый резистор и первую катушку индуктивности подключены к плюсу первого источника питания, отражающая поверхность направляет излучение светодиодов на затвор фототранзистора, исток которого соединен со второй общей шиной, затвор через шестой резистор подключен ко второй общей шине, а сток соединен с переключающим элементом и через пятый резистор и вторую катушку индуктивности подключен к плюсу второго источника питания, плюс первого источника питания через первый конденсатор подключен к первой общей шине, плюс второго источника питания через второй конденсатор подсоединен ко второй общей шине, с которой соединен минус второго источника питания. Уменьшение времени распознавания адреса в предлагаемом изобретении достигается за «чет исключения дополнительного коммутирующего каскада, использования сверхвысокочастотных полевых транзисторов с барьером Шотки на основе GaAs и применения светодиодов, имеющих минимальные фронты нарастания и спада. Исключение дополнительного источника опорного напряжения в результате применения светодиодов, как "индикаторов" совпадения сравниваемого адреса получателя информации с установленным адресом, повышает достоверность определения совпадения/несовпадения, надежность и помехоустойчивость устройства, так как разброс параметров транзисторов и помехи с амплитудами, составляющими десятые доли вольта не оказывают существенного влияния на свечение или не свечение светодиодов. Оптическая развязка между входными и выходным сигналами также значительно повышает помехоустойчивость устройства, поскольку помехи, присутствующие на входе устройства, не проникают на его выход и не могут вызвать ложное срабатывание коммутирующего элемента. На чертеже (фиг.) представлена схема, поясняющая принцип действия оптоэлектронного дешифратора-коммутатора. Оптоэлектронный дешифратор-коммутатор содержит резисторы 1 - 6, первый и второй полевые транзисторы 7 и 8. Фототранзистор 9, первый и второй светодиоды 10 и 11, первую и вторую катушки индуктивности 12 и 13, первый и второй конденсаторы 14 и 15, отражающую поверхность 16, источники питания 17 и 18, два однобитовых регистра 19 и 20, коммутирующий элемент 21. Входом устройства является информационная шина, к которой подключены входы регистров 19 и 20, а выходом - выход коммутирующего элемента 21. Затвор полевого транзистора 7 через резистор 1 подключен к выходу регистра 19, исток подключен к общей шине 22, а сток соединен с катодом светодиода 10, с анодом светодиода 11 и через резистор 3 и катушку индуктивности 12 подключен к плюсу источника питания 17. Затвор полевого транзистора 8 через резистор 2 подключен к выходу регистра 20, исток подключен к общей шине 22, а сток соединен с анодом светодиода 10, с катодом светодиода 11 и через резистор 4 и катушку индуктивности 12 подключен к плюсу источника питания 17. Затвор фототранзистора 9 через резистор 6 соединен с его истоком, который подключен к общей шине 23, сток подключен к коммутирующему элементу 21 и через резистор 5 и катушку индуктивности 13 соединен с плюсом источника питания 18. Плюс источника питания 17 через конденсатор 14 подключен к общей шине 22; которая соединена с его минусом. Плюс источника питания 18 через конденсатор 15 соединен с общей шиной 23, к которой подключен его минус. Отражающая поверхность 1В оптически связывает светодиоды 10 и 11 с фототранзистором 9. Для практической реализации заявляемого устройства можно воспользоваться выпускаемыми серийно полевыми транзисторами с барьером Шотки на основе GaAs, работающих в режиме обеднения (например, типа ЗП320А-2) в качестве транзисторов 7 и 8, и бескорпусной их реализацией, в качестве фототранзисторе. В качестве светодиодов можно использовать светодиоды на основе GaP или SIC, которые имеют фронты нарастания и спада, составляющие единицы наносекунд. В качестве конденсаторов можно воспользоваться малоиндуктивными конденсаторами типа К 10 17. При включении источников питания 17 и 18 через транзисторы 7 и 8 и фототранзистор 9 начинают течь токи стоков, величины которых зависят от номиналов резисторов 3 - 5, значений напряжений на затворах транзисторов 7 и 8 и наличия светового потока на затворе фототранзистора 9. Величины напряжений на затворах транзисторов 7 и 8 определяются содержимым однобитовых регистров 19 и 20, в которые с информационной шины заносятся сравниваемые биты. Если значения битов не равны, то рабочая точка одного из транзисторов 7 и 8 находится вблизи области отсечки, а другого вблизи области насыщения. Поэтому между стоками этих транзисторов существует разность потенциалов, заставляющая светиться один из двух светодиодов. Если значение бита в регистре 19 равно логической единице, а значение бита в регистре 20 - логическому нулю, то возбуждается светодиод 10. Если бит в регистре 19 имеет значение логического нуля, а в регистре 20 логической единицы, то светится светодиод 11. Излучение светодиодов с помощью отражающей. поверхности 16 подается на затвор фоторезистора 9, который в результате находится в режиме насыщения. Если значения битов в регистрах 19 и 20 одинаковые, то оба транзистора находятся в одинаковом состоянии, и разность потенциалов между их стоками равна нулю, поэтому ни один из светодиодов не светится и фототранзистор 9 переходит в высокоомное состояние, потенциал его стока возрастает, что вызывает переключение коммутирующего элемента 21. Резисторы 1 и 2 обеспечивают нахождение рабочей точки транзисторов 7 и 8 вблизи области отсечки, когда на входе присутствует напряжение, соответствующее уровню логического нуля. Резисторы 3 и 4 определяют наклон нагрузочных прямых транзисторов 7 и 8 соответственно. Резистор 6 обеспечивает запирание фототранзистора 9 в случае отсутствия светового потока на его затворе. С резистора 5 снимается напряжение, подаваемое на вход переключающего элемента 21. Катушки индуктивности 12 и 13 вместе с конденсаторами 14 и 15 образуют фильтры высоких частот. Разрядность регистров 19 и 20 может, быть увеличена до любой необходимой величины, а изменения, вносимые в этом случае в схему предлагаемого изобретения, сводятся к подключению к дополнительным разрядам регистров новых каскадов аналогичных каскаду, построенному на транзисторах 7 и 8.

ДивитисяДодаткова інформація

Автори англійськоюOsadchuk Volodymyr Stepanovych, Tarnovskyi Mykola Genadiiovych, Tarnovskyi Mykola Hennadiiovych

Автори російськоюОсадчук Владимир Степанович, Тарновский Николай Геннадиевич, Тарновский Николай Геннадьевич

МПК / Мітки

МПК: H03K 17/00

Мітки: оптоелектронний, дешифратор-комутатор

Код посилання

<a href="https://ua.patents.su/3-25117-optoelektronnijj-deshifrator-komutator.html" target="_blank" rel="follow" title="База патентів України">Оптоелектронний дешифратор-комутатор</a>

Попередній патент: Спосіб одержання волокна з трести льону та коноплі

Наступний патент: Мастильно-охолоджувальна рідина для механічної обробки металів

Випадковий патент: Гнучкий бункер