Генератор рівномірно розподілених випадкових чисел

Номер патенту: 59670

Опубліковано: 15.09.2003

Автори: Торба Ганна Олександрівна, Бобух Всеволод Анатолійович, Горбенко Іван Дмитрович, Торба Олександр Олексійович, Степченко Олексій Зотович, Єлаков Сергій Генадійович

Формула / Реферат

Генератор рівномірно розподілених випадкових чисел, що містить багатоканальний вузол генерації випадкових логічних рівнів, які складаються з послідовно з`єднаних генератора шуму, підсилювача-обмежувача та лічильного тригера, і канал спряження з ПЕОМ, який включає в себе регістр зсуву, вхід даних якого з`єднаний з виходом елемента «ВИКЛЮЧНЕ АБО», входи якого підключені до виходів вузлів генерації випадкових логічних рівнів, виходи регістра зсуву увімкнуті до входів вихідного паралельного регістра, з`єднаного виходами з шиною ПЕОМ, тактовий генератор, вихід якого з`єднаний з синхровходом регістра зсуву і входом подільника імпульсів, вихід якого під`єднаний до синхровходу вихідного паралельного регістра та входу контролера шини, до складу якого входить програмований дешифратор адреси, входи якого під`єднані до шини ПЕОМ, а вихід контролера шини з`єднаний з входом дозволу вихідного паралельного регістра, який відрізняється тим, що додатково введені канали спряження з ПЕОМ, в яких дешифратори адреси запрограмовані на окремі адреси, при цьому кількість вузлів генерації випадкових логічних рівнів перевищує кількість каналів спряження з ПЕОМ, до кожного з яких під`єднано щонайменше один вузол генерації випадкових логічних рівнів, який не з`єднаний з іншими каналами спряження з ПЕОМ.

Текст

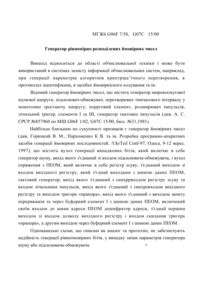

Генератор рівномірно розподілених випадкових чисел, що містить багатоканальний вузол генерації випадкових логічних рівнів, які складаються з послідовно з'єднаних генератора шуму, підсилювача-обмежувача та лічильного тригера, і канал спряження з ПЕОМ, який включає в себе регістр зсуву, вхід даних якого з'єднаний з виходом елемента «ВИКЛЮЧНЕ АБО», входи якого підключені до виходів вузлів генерації випадкових логічних рівнів, виходи регістра зсуву увімкнуті до входів вихідного паралельного регістра, з'єднаного виходами з шиною ПЕОМ, тактовий генератор, вихід якого з'єднаний з синхровходом регістра зсуву і входом подільника імпульсів, вихід якого під'єднаний до синхровходу вихідного паралельного регістра та входу контролера шини, до складу якого входить програмований дешифратор адреси, входи якого під'єднані до шини ПЕОМ, а вихід контролера шини з'єднаний з входом дозволу вихідного паралельного регістра, який відрізняється тим, що додатково введені канали спряження з ПЕОМ, в яких дешифратори адреси запрограмовані на окремі адреси, при цьому КІЛЬКІСТЬ вузлів генерації випадкових логічних рівнів перевищує КІЛЬКІСТЬ каналів спряження з ПЕОМ, до кожного з яких під'єднано щонайменше один вузол генерації випадкових логічних рівнів, який не з'єднаний з іншими каналами спряження з ПЕОМ Винахід відноситься до області обчислювальної техніки і може бути використаний в системах захисту інформації обчислювальних систем, наприклад, при генерації параметрів алгоритмів криптографічного перетворення, в протоколах аутентифікацм, в засобах імовірнісного кодування та ін Відомий генератор випадкових чисел (див Горицкий В М , Пархоменко К В та ін Розробка програмно-апаратних засобів генерації ймовірних послідовностей /UkrTell Conf-97, Одеса, 9-12 верес 1997), що містить вузол генерації випадкових бітів, який включає в себе генератор шуму, вихід якого з'єднаний зі входом підсилювачаобмежувача, і вузол спряження з ПЕОМ, який включає в себе регістр зсуву, з'єднаний виходом зі входом вихідного регістру, який з'єднаний виходами з шиною даних ПЕОМ, тактовий генератор, вихід якого з'єднаний з синхровходом регістру зсуву та входом лічильника імпульсів, вихід якого з'єднаний з синхровходом вихідного регістру та виходом тригера «прапора», вихід якого з'єднаний з виходом запиту переривання та через буферний елемент І з шиною даних ПЕОМ, включений своїм входом до шини адреси ПЕОМ дешифратор адреси, з'єднаний першим виходом зі входом дозволу вихідного регістру і входом скидання тригера «прапора», а другим виходом через буферний елемент І з шиною даних ПЕОМ Недоліком цього генератора є невелика надійність генерування випадкових чисел (послідовностей) одноканальною схемою Найбільш близьким по сукупності ознак є генератор рівномірно розподілених ймовірних чисел (див Декларац пат Укр 33361 від 16 02 1999 по МПК G06F7/58, G07C15/00, Бюл №1 від 15 02 2001), що містить багатоканальний вузол генерації випадкових бітів, кожен канал в якому включає в себе послідовно з'єднані генератор шуму, підсилювач-обмежувач і лічильний тригер, виходи усіх вузлів об'єднані схемою "ВИКЛЮЧНЕ АБО", і канал спряження з ПЕОМ, включаючий в собі регістр зсуву, виходи якого увімкнуті до входів вихідного регістру, з'єднаного виходами з шиною даних ПЕОМ, тактовий генератор, вихід якого (О ю 59670 з єднаний з синхровходом регістру зсуву та входом випадкових логічних рівнів, які складаються з полічильника імпульсів, вихід якого під'єднаний до слідовно з'єднаних генераторів 2-1 2-к шуму, підсинхровходу вихідного регістру та входу тригера силювачів-обмежувачів 3-1 3-к і лічильних триге«прапора», а його вихід з'єднаний з виходом запирів 4-1 4-к, і «т» каналів 5-1 5-т спряження з ту переривання та через буферний елемент І з ПЕОМ, кожен канал МІСТИТЬ регістр 6-1 6-п зсуву, шиною даних ПЕОМ, і дешифратор адреси, вклювхід даних якого з'єднаний з виходом елемента 7чений входами до шини адреси ПЕОМ, а першим 1 7-т «ВИКЛЮЧНЕ АБО», входи якого підключені виходом до входу дозволу вихідного регістру та до виходів вузлів 1-1 1-к генерації випадкових входу скидання тригера «прапора», а другим вилогічних рівнів Виходи регістра 6-1 6-т зсуву ходом до буферного елементу І увімкнуті до входів вихідного паралельного регістру 8-1 8-т, з'єднаного виходами з шиною 9 Надійність генерації випадкових ПЕОМ Тактовий генератор 10-1 1-10-т з'єднай з послідовностей підвищена за рахунок використансинхровходом регістру 6-1 6-т зсуву і входом ня багатоканального генератора випадкових бітів дільника 11-1 11-т імпульсів, вихід якого Але одноканальна схема спряження з ПЕОМ випід'єднаний до синхровходу вихідного паралельнозначає відносно невелику надійність усієї системи, го регістру 8-1 8-т та входу контролера 12-1 12як "найслабкіша ланка ланцюга" m шини, до складу якого входить програмований В основу винаходу поставлена задача стводешифратор адреси 13-1 13-т, входи якого рення такого генератора рівномірно розподілених під'єднані до шини 9 ПЕОМ, а вихід контролера випадкових чисел, у якого нове схемне рішення 12-1 12-т шини з'єднаний з входом дозволу вузла спряження з ПЕОМ дозволило б забезпечивихідного паралельного регістру 8-1 8-т ти високу надійність генерації випадкових рівноімовірних чисел КІЛЬКІСТЬ вузлів 1-1 1-к генерації випадкових логічних рівнів перевищує КІЛЬКІСТЬ каналів 5-1 5Такий технічний результат може бути досягнут спряження з ПЕОМ, і до кожного каналу 5-1 5тий, якщо в генераторі рівномірно розподілених т спряження під'єднаний що найменше один вувипадкових чисел, що містить багатоканальний зол генерації випадкових логічних рівнів, який не вузол генерації випадкових логічних рівнів, які з'єднаний з іншими каналами спряження з ПЕОМ складаються з послідовно з'єднаних генератора шуму, підсилювача-обмежувача та лічильного триГенератор рівномірно розподілених випадкогера, і канал спряження з ПЕОМ, який включає в вих чисел працює наступним чином На виходах себе регістр зсуву, вхід даних якого з'єднаний з генераторів 2-1 2-к шуму формуються імпульси виходом елемента «ВИКЛЮЧНЕ АБО», входи яковипадкової амплітуди, наступні через випадкові го підключені до виходів вузлів генерації випадкочасові інтервали Амплітуда цих імпульсів вих логічних рівнів, виходи регістра зсуву увімкнуті підсилювачами-обмежувачами 3-1 3-к перетводо входів вихідного паралельного регістру, з'єднарюється в ЛОГІЧНІ рівні ТТЛ або КМОН мікросхем ного виходами з шиною ПЕОМ, тактовий генераІмпульси з виходів підсилювачів-обмежувачів 3тор, вихід якого з'єднаний з синхровходом регістру 1 3-к подаються на входи лічильних тригерів 4зсуву і входом дільника імпульсів, вихід якого під'1 4-к, на виходах яких формуються ЛОГІЧНІ рівні, з єднаний до синхровходу вихідного паралельного рівною імовірністю приймаючі значення нуля або регістру та входу контролера шини, до складу якоодиниці в випадкові моменти часу го входить програмований дешифратор адреси, Випадкові ЛОГІЧНІ рівні об'єднуються елеменвходи якого під'єднані до шини ПЕОМ, а вихід контами 7-1 7-т «ВИКЛЮЧНОГО АБО» в кожному тролера шини з'єднаний з входом дозволу вихідканалі 5-1 5-т спряження з ПЕОМ і записуються ного паралельного регістру, згідно винаходу, допослідовно в регістр 6-1 6-т зсуву з частотою, що датково введені канали спряження з ПЕОМ, в яких виробляється тактовим генератором 10-1 10-т дешифратори адреси запрограмовані на окремі Обов'язковою умовою формування рівномірно адреси, при цьому КІЛЬКІСТЬ вузлів генерації випадрозподілених випадкових чисел є вибір періоду кових логічних рівнів перевищує КІЛЬКІСТЬ каналів тактових імпульсів генератора 10-1 10-т у 5 10 спряження з ПЕОМ, до кожного з яких під'єднано разів більшим, ніж середній період випадкових що найменше один вузол генерації випадкових імпульсів на виходах генераторів шуму 2-1 2-к логічних рівнів, який не з'єднаний з іншими канаДІЛЬНИК 11-1 11-т імпульсів через КОЖНІ «П» перілами спряження з ПЕОМ одів тактового генератора 10-1 10-т формує імпульс для запису коду з регістру 6-1 6-т зсуву в Таким чином, введення в генератор рівномірно вихідний паралельний регістр 8-1 8-т, а також розподілених випадкових чисел додаткових «т-1» для керування контролером 12-1 12-т шини Для каналів спряження з ПЕОМ, в яких дешифратори зчитування випадкових чисел на шину 9 ПЕОМ адреси запрограмовані на окремі адреси, а також виставляється адреса порта, що розпізнається введення додаткових зв'язків дозволяє підвищити дешифратором 13-1 13-т адреси, і вихідний сигнадійність генерування рівномірно розподілених нал контролера 12-1 12-т шини дозволяє зчитувипадкових чисел за рахунок гарячого резервування коду вихідного регістру 8-1 8-т через шину вання як вузлів генерації випадкових логічних рів9 ПЕОМ в комп'ютер нів так і каналів спряження з ПЕОМ На рисунку (див фіг) зображена структурна схема генератора рівномірно розподілених випадкових чисел Генератор містить «к» вузлів 1-1 1-к генерації В кожному каналі 5-1 5-т спряження з ПЕОМ дешифратори 13-1 13-т адреси запрограмовані на розпізнавання різних адрес портів 59670 Комп'ютерна верстка М Мацело Підписано до друку 06 10 2003 Тираж39 прим Міністерство освіти і науки України Державний департамент інтелектуальної власності, Львівська площа, 8, м Київ, МСП, 04655, Україна ТОВ "Міжнародний науковий комітет", вул Артема, 77, м Київ, 04050, Україна

ДивитисяДодаткова інформація

Назва патенту англійськоюGenerator of uniformly-distributed random numbers

Автори англійськоюTorba Oleksandr Oleksiiovych, Horbenko Ivan Dmytrovych, Stepchenko Oleksii Zotovych, Bobukh Vsevolod Anatoliiovych, Torba Hanna Oleksandrivna

Назва патенту російськоюГенератор равномерно распределенных случайных чисел

Автори російськоюТорба Александр Алексеевич, Горбенко Иван Дмитриевич, Степченко Алексей Зотович, Бобух Всеволод Анатольевич, Торба Анна Александровна

МПК / Мітки

МПК: G06F 7/58, G07C 15/00

Мітки: рівномірно, генератор, розподілених, чисел, випадкових

Код посилання

<a href="https://ua.patents.su/3-59670-generator-rivnomirno-rozpodilenikh-vipadkovikh-chisel.html" target="_blank" rel="follow" title="База патентів України">Генератор рівномірно розподілених випадкових чисел</a>

Попередній патент: Ківш скрепера

Наступний патент: Вітродвигун

Випадковий патент: Спосіб одержання кальцієвмісної сполуки