Процесор петрі

Номер патенту: 32183

Опубліковано: 15.12.2000

Автори: Матейченко Віктор Валентинович, Петришин Юрій Степанович, Лобода Віталій Гаврилович, Єльчанінов Дмитро Борисович

Текст

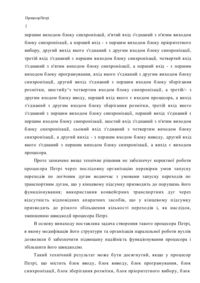

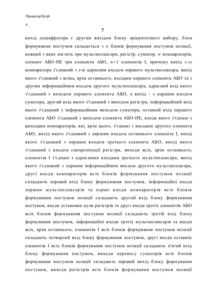

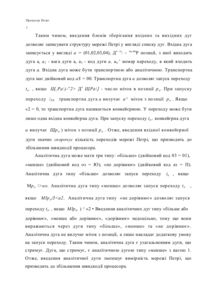

]VfflK5G06F15/20 ПРОЦЕСОР ПЄТРІ Винахід відноситься до обчислювальної техніки та систем управління, а власне, до швидкодіючих спеціалізованих процесорів, призначених для автоматизації технологічних процесів та обробки інформації. Відомий прилад для моделювання оцінних мереж Петрі (див. Мережі Петрі, паралельні алгоритми та моделі мультипроцесорних систем / Васільєв В. В., Кузьмук В. В. - Київ: Наук. Думка, 1990. - С. 190-194). Прилад містить блок вхідних розміточних векторів, блок вихідних розміточних векторів, блок поточної розмітки, блок перегляду вхідних векторів, блок перегляду вихідних векторів, блок обчислення поточної розмітки, блок обчислення додаткового коду, блок порівняння, блок моделей вершин, блок фіксації, елемент, що розв'язує, блок індикації та два генератора синхронізації. Проте зазначене вище технічне рішення не забезпечує управління реальними об'єктами та процесами через відсутність блоків вводу та виводу інформації; швидкодію, достатню для роботи приладу у реальному масштабі часу через неефективну організацію взаємодії блоків приладу; оперативного програмування роботи приладу шляхом зміни топології та розмітки мережі через в ідсутність блоку програмування; контролю над можливим переповненням розрядної сітки приладу та відповідної реакції на це, що не виключає випадків неправильного функціонування мережі Петрі, через відсутність засобів контролю та обробки випадків переповнення розрядної сітки. Найбільш близьким до приладу, що заявляється, за сукупністю гіри^наків є процесор Петрі (див. Пат. України на винахід №15213 А. / Бюл., 1997. - №3), що містить чотири блоки топології, блок арифметико-логічних приладів, блок перевірки логічних умов, блок формування постумов, блок зберігання поточної розмітки, блок вводу, блок виводу, блок програмування, блок ч пріоритетного вибору і блок синхронізації. Перший вхід блоку формування постумов з'єднаний з третім входом блоку синхронізації, другий вихід з'єднаний з п'ятим входом блоку зберігання розмітки, третій вхід з'єднаний з Процесор Петрі 2 першим виходом блоку синхронізації, п'ятий вхід з'єднаний з п'ятим виходом блоку синхронізації, а перший вхід - з першим виходом блоку пріоритетного вибору, другий вихід якого з'єднаний з другим входом блоку синхронізації, третій вхід з'єднаний з першим виходом блоку синхронізації, четвертий вхід з'єднаний з п'ятим виходом блоку синхронізації, а перший вхід - з першим виходом блоку програмування, вхід якого з'єднаний з другим виходом блоку синхронізації, другий вихід з'єднаний з першим входом блоку зберігання розмітки, шостийу^з четвертим входом блоку синхронізації , а третій/- з другим входом блоку вводу, перший вхід якого є входом процесора, а вихід з'єднаний з другим входом блоку зберігання розмітки, третій вхід якого з'єднаний з першим виходом блоку синхронізації, перший вихід з'єднаний з першим входом блоку синхронізації, шостий вхід з'єднаний з п'ятим виходом блоку синхронізації, сьомий вхід з'єднаний з четвертим виходом блоку синхронізації, а другий вихід - з першим входом блоку виводу, другий вхід якого з'єднаний з першим виходом блоку синхронізації, а вихід є виходом процесора. Проте зазначене вище технічне рішення не забезпечує коректної роботи процесора Петрі через послідовну організацію перевірки умов запуску переходів по логічним дугам водночас з умовами запуску переходів по транспортним дугам, що у кінцевому підсумку призводить до порушень його функціонування; використання конвейєрних транспортних дуг через відсутність в ідповідних апаратних засобів, що у кінцевому підсумку призводить до різкого збільшення кількості переходів і, як наслідок, зменшенню швидкодії процесора Петрі. В основу винаходу поставлена задача створення такого процесора Петрі, в якому модифікація його структури та організація паралельної роботи вузлів дозволили б забезпечити підвищену надійність функціонування процесора і збільшити його швидкодію. Такий технічний результат може бути досягнутий, якщо у процесор Петрі, що містить блок вводу, блок виводу, блок програмування, блок синхронізації, блок зберігання розмітки, блок пріоритетного вибору, блок Процесор Петрі З формування постумов, перший вихід якого з'єднаний з третім входом блоку синхронізації, другий вихід з'єднаний з п'ятим входом блоку зберігання розмітки, третій вхід з'єднаний з першим виходом блоку синхронізації, п'ятий вхід з'єднаний з п'ятим виходом блоку синхронізації, а перший вхід - з першим виходом блоку пріоритетного вибору, другий вихід якого з'єднаний з другим входом блоку синхронізації, третій вхід з'єднаний з першим виходом блоку синхронізації, четвертий вхід з'єднаний з п'ятим виходом блоку синхронізації, а перший вхід - з першим виходом блоку програмування, вхід якого з'єднаний з другим виходом блоку синхронізації , другий вихід з'єднаний з першим входом блоку зберігання розмітки, шостий г - з четвертим входом блоку синхронізації, а третшУ^з другим входом блоку вводу, перший вхід якого є входом процесора, а вихід з'єднаний з другим входом блоку зберігання розмітки, третій вхід якого з'єднаний з першим виходом блоку синхронізації, перший вихід з'єднаний з першим входом блоку синхронізації, шостий вхід з'єднаний з п'ятим виходом блоку синхронізації, сьомий вхід з'єднаний з четвертим виходом блоку синхронізації, а другий вихід - з першим входом блоку виводу, другий вхід якого з'єднаний з першим виходом блоку синхронізації, а вихід є виходом процесора, згідно винаходу, ввести блок зберігання вхідних дуг, аналізатор вхідних дуг, блок формування передумов, блок зберігання вихідних дуг, причому, з'єднаний входом з четвертим виходом блоку програмування, а виходом - з другим входом аналізатора вхідних дуг, блок зберігання вхідних дуг складається з к блоків зберігання вхідної дуги, кожний з яких містить чотири регістри, .аналізатор'вхідних дул, перший вхід(ЙБ^га з'єднаний з третім виходом блоку синхронізації, третій вхід з'єднаний з другим виходом блоку зберігання розмітки, перший вихід з'єднаний з другим входом блоку пріоритетного вибору, а другий вихід - з другим входом блоку формування передумов, складається з к блоків аналізу вхідн ої дуги, к о жний з яких мі стить мультипл ек сер, суматор, дв а демультиплексери, елемент 4І-АБО, елемент І, два елементи АБО-НЕ, s+3 елементи НЕ, блок формування передумов, що складається з п блоків формування передумов позиції, кожний з яких містить мультиплексер та к Процесор Петрі 4 компараторів, з'єднаний першим в ходом з першим виходом блоку пріоритетного вибору, а виходом - з четвертим входом блоку зберігання розмітки та четвертим входом блоку формування постумов, блок зберігання вихідних дуг, що складається з w блоків зберігання вихідної дуги, кожний з яких містить три регістри та демультиплексер, з'єднаний входом з п'ятим виходом блоку програмування, а виходом - з другим входом блоку формування постумов, при цьому блок зберігання розмітки складається з п б локів зб ер іг ання розм ітки позиції , ко жний з я ких м іс тить два мультиплексери, регістр, суматор, два елементи АБО, п'ять елементів І, елемент НЕ, причому вихід першого мультиплексера з'єднаний з другим входом суматора, перший вхід якого з'єднаний з виходом регістра, а інформаційний вихід - з пер шим інформаційним входом другого мультиплексера, перший адресний вхід якого з'єднаний з виходом першого елемента АБО, другий адресний вхід з'єднаний з виходом другого елемента І, а вихід - з інформаційним входом регістра, вхід синхронізації якого з'єднаний з виходом другого елемента АБО, а вхід установки нуля - з виходом п'ятого елемента І, другий вхід першого елемента АБО з'єднаний з виходом першого елемента І, другий вхід якого з'єднаний з виходом елемента НЕ, другий вхід другого елемента АБО з'єднаний з виходом третього елемента І, а третій вхід - з виходом четвертого елемента І, четверті інформаційні та четверті адресні входи других мультиплексерів та четверті входи других елементів АБО всіх блоків зберігання розмітки позиції складають перший вхід блоку зберігання розмітки, другі інформаційні входи мультиплексерів, входи елементів НЕ, другі входи других елементів І та другі входи третіх елементів І всіх блоків зберігання розмітки позиції складають другий вхід блоку зберігання розмітки, адресні входи перших мультиплексерів та перші входи перших, других та третіх елементів І всіх блоків зберігання розмітки позиції складають третій вхід блоку зберіг ання розмітки, треті інформаційні входи других мультиплексерів та другі входи четвертих та п'ятих елементів І всіх блоків зберігання розмітки позиції складають четвертий вхід блоку зберігання розмітки, перші інформаційні входи перших мультиплексерів всіх блоків Процесор Петрі 5 зберігання розмітки позиції складають п'ятий вхід блоку зберігання розмітки, треті адресні входи других мультиплексерів та перші входи четвертих та п'ятих елементів І всіх блоків зберігання розмітки позиції складають шостий вхід блоку зберігання розмітки, перші входи елементів АБО всіх блоків зберігання розмітки позиції складають сьомий вхід блоку зберіг ання розмітки, виходи сигналів переносів суматорів всіх блоків зберігання розмітки позиції складають перший вихід блоку зберігання розмітки, виходи регістрів всіх блоків зберігання розмітки позиції складають другий вихід блоку зберігання розмітки, блок пріоритетного вибору містить регістр, дешифратор, т-1 елементів АБО та т блоків аналізу переходів, кожний з яких містить RS-тригер, мультиплексер, елемент НЕ, елемент АБО та елемент АБОНЕ, причому г-й вихід регістра з'єднаний з другим інформаційним входом мультиплексора г-го блоку аналізу переходу, і-й вхід дешифратора з'єднаний з виходом елемента АБО-НЕ z-го блоку аналізу переходу, перший вихід дешифратора з'єднаний з першим інформаційним входом мультиплексера першого блоку аналізу переходу, виходи дешифратора з 2 і по 21+ - 1 з'єднані з входами г-го елемента АБО, вихід якого з'єднаний з першим інформаційним входом мультиплексера і-h 1-го блоку аналізу переходу, при цьому у кожному блоці аналізу переходу вихід мультиплексера з'єднаний з входом установки одиниці і^-тригера та з входом елемента НЕ, вихід якого з'єднаний з входом установки нуля .US'-тригера, вхід синхронізації якого з'єднаний з виходом елемента АБО, а прямий вихід - з останнім входом елемента АБО-НЕ, інформаційний вхід та вхід синхронізації регістра складають перший вхід блоку пріоритетного вибору, всі входи, крім останнього, елементів АБО-НЕ всіх блоків аналізу переходів складають другий вхід блоку пріоритетного вибору, адресні входи мультиплексерів та перші входи елементів АБО всіх блоків аналізу переходів складають третій вхід блоку пріоритетного вибору, другі входи елементів АБО всіх блоків аналізу переходів складають четвертий вхід блоку пріоритетного вибору, виходи елементів АБО та перший вихід дешифратора складають перший вихід блоку пріоритетного вибору, нульовий Процесор ПетрІ 6 ? вихід дешифратора є другим вихідом блоку пріоритетного вибору, блок формування постумов складається з п блоків формування постумов позиції, кожний з яких містить три мультиплексери, регістр, суматор, w компараторів, елемент АБО-НЕ три елементи АБО, п+1 елементів І, причому вихід і-го компаратора з'єднаний з z-м адресним входом першого мультиплексера, вихід якого з'єднаний з всіма, крім останнього, входами першого елемента АБО та з другим інформаційним входом другого мультиплексера, адресний вхід якого з'єднаний з виходом першого елемента АБО, а вихід - з першим входом суматора, другий вхід якого з'єднаний з виходом регістра, інформаційний вхід якого з'єднаний з інформаційним виходом суматора, останній вхід першого елемента АБО з'єднаний з виходом елемента АБО-НЕ, входи якого з'єднані з виходами компараторів, які, крім цього, з'єднані з входами другого елемента АБО, вихід якого з'єднаний з першим входом останнього елемента І, вихід якого з'єднаний з першим входом третього елемента АБО, вихід якого з'єднаний з входом синхронізації регістра, виходи всіх, крім останнього, елементів І з'єднані з адресними входами третього мультиплексера, вихід якого з'єднаний з першим інформаційним входом другого мультиплексера, другі входи компараторів вс іх блоків формування постумов позиції складають перший вхід блоку формування постумов, інформаційні входи перших м уль типлексер ів та перші в ходи компаратор ів вс іх блоків формування постумов позиції складають другий вхід блоку формування постумов, входи установки нуля регістрів та другі входи третіх елементів АБО всіх блоків формування постумов позиції складають третій вхід блоку формування постумов, інформаційні входи третіх мультиплексерів та входи всіх, крім останнього, елементів І всіх блоків формування постумов позиції складають четвертий вхід блоку формування постумов, другі входи останніх елементів І всіх блоків формування постумов позиції складають п'ятий вхід блоку формування постумов, виходи переносу суматорів всіх блоків формування постумов позиції складають перший вихід блоку формування постумов, виходи регістрів всіх блоків формування постумов позиції складають другий вихід блоку формування постумов. Процесор Петр і 7 Таким чином, введення блоків зберігання вхідних та вихідних дуг дозволяє записувати структуру мережі Петрі у вигляді списку дуг. Вхідна дуга записується у вигляді а = (01,02,03,04), Д е а\ ~ н° меР позиції, з якої виходить дуга а, а2 - вага дуги а, а3 - код дуги а, а4 ' номер переходу, в який входить дуга а. Вхідна дуга може бути транспортною або аналітичною. Транспортна дуга має двійковий код а$ = 00. Транспортна дуга а дозволяє запуск переходу t a . , якщо Щ,Ра\)- а 2> Д е ЩРа\] - число міток в позиції р а . При запуску переходу / fl4 транспортна дуга а вилучає а^ міток з позиції р а . Якщо «2 = 0, то транспортна дуга називається конвейєрною. У переходу може бути лише одна вхідна конвейєрна дуга. При запуску переходу ta/. конвейєрна дуга а вилучає Щр а .) міток з позиції р а . Отже, введення вхідної конвейєрної дуги значно скорочує кількість переходів мережі Петрі, що призводить до збільшення швидкодії процесора. Аналітична дуга може мати три типу: «більше» (двійковий код 03 = 01), «менше» (двійковий код оз = Ю), «не дорівнює» (двійковий код аз = П). Аналітична дуга типу «більше» дозволяє запуск переходу іа , якщо Мр а \>ао. Аналітична дуга типу «менше» дозволяє запуск переходу t a , якщо МІр а Л Д е h ~ номер переходу, з якого виходить дуга b, bi ~ вага дуги Ь, Ь ъ - номер позиції, в яку входить дуга Ь. При запуску переходу /^ дуга b додає Ь 2 міток в позицію р ь Якщо Z?2~05 то вхідна дуга називається конвейєрною. При запуску переходу t^. конвейєрна дуга Ъ додає в позицію р^ стільки м іток, скільки вилучила з відповідної позиції вхідна конвейєрна дуга переходу і^. . Отже, введення вихідної конвейєрної дуги значно скорочує кількість переходів мережі Петрі, що призводить до збільшення швидкодії процесора. В блоку аналізу вхідних дуг визначається, дозволяє або забороняє вхідна дуга а запуск переходу t a. . Аналіз всіх вхідних дуг робиться водночас, що призводить до збільшення швидкодії процесора. В б локу пр іор итетного вибору в изначається, дозволений або заборонений запуск переходу. Якщо всі вхідні дуги переходу дозволяють його запуск, то запуск переходу дозволений, інакше - заборонений. Всі переходи аналізуються водночас, а вирішення конфліктів та вибір переходів, що запускаються, робиться дешифратором з врахуванням пріоритетів переходів, що призводить до збільшення швидкодії процесора. Крім того, в блоку пріоритетного вибору запам'ятовується результат аналізу переходу по аналітичним дугам. Тому зміна розмітки мережі Петрі при запуску переходу з більш високим пріоритетом не вплине на результат аналізу переходів з більш низьким пріоритетом. Таким чином, виключаються випадки неправильного запуску переходів, що призводить до підвищення надійності функціонування процесора. В блоках формування перед- та постумов на основі аналізу вхідних дуг визначаються перед- та постумови водночас для всіх переходів мережі Петрі. Таким чином, на момент вибору переходу, що запускається його перед- та постумови будуть вже сформовані. В блоках зберігання розмітки та формування постумов водночас змінюється розмітка лише вхідних та Процесор Пєтрі 9 вихідних позицій переходу, що запускається. Це призводить до збільшення швидкодії процесора. На фіг. 1 представлена структурна схема процесора Петрі, на фіг.2 - блок зберігання вхідної дуги, на фіг.З - блок аналізу вхідної дуги, на фіг.4 - блок формування передумов позиції , на фіг.5 - блок зберігання вихідної дуги, на фіг.6 - блок формування постумов позиції, на фіг.7 - блок зберігання розмітки позиції, на фіг. 8 - блок пріоритетного вибору, на фіг. 9 - блок аналізу переходу. Процесор Петрі (фіг. 1) містить блок 1 вводу, блок 2 виводу, блок З програмування, блок 4 синхронізації, блок 5 зберігання розмітки, блок 6 пріоритетного вибору, блок 7 формування постумов, блок 8 зберігання вхідних дуг, аналізатор 9 вхідних дуг, блок 10 формування передумов, блок 11 зберігання вихідних дуг. Перший вхід блоку 1 вводу є входом процесора, другий вхід з'єднаний з третім виходом блоку 3 програмування, а вихід з'єднаний з другим входом блоку 5 зберігання розмітки, другий вихід якого з'єднаний з третім входом аналізатора 9 вхідних дуг та першим входом блоку 2 виводу, а перший вихід з'єднаний з першим входом блоку 4 синхронізації, третій вихід якого провідником 12 з'єднаний з першим входом аналізатора 9 вхідних дуг, другий вихід - з входом блоку 3 програмування, а четвертий вихід провідником 1 3 - з сьомим входом блоку 5 зберігання розмітки, перший вхід якого з'єднаний з другим виходом блоку 3 програмування, перший вихід якого з'єднаний з першим входом блоку 6 пріоритетного вибору, четвертий вихід з'єднаний з входом блоку 8 зберігання вхідних дуг, шостий вихід з'єднаний з четвертим входом блоку 4 синхронізації, а п'ятий вихід - з входом блоку 11 зберігання вихідних дуг, вихід якого з'єднаний з другим входом блоку 7 формування постумов, другий вихід якого з'єднаний з п'ятим входом блоку 5 зберігання розмітки. Вихід блоку 8 зберігання вхідних дуг з'єднаний з другим входом аналізатора 9 вхідних дуг, перший вихід якого з'єднаний з другим входом блоку 6 пріоритетного вибору, перший вихід якого з'єднаний з першим входом блоку 7 формування постумов та з першим входом блоку 10 формування передумов, другий вхід якого з'єднаний з другим виходом Процесор Петр і 10 аналізатора 9 вхідних дуг, а вихід - з четвертим входом блоку 5 зберігання розмітки та четвертим входом блоку 7 формування постумов, перший вихід якого з'єднаний з третім входом блоку 4 синхронізації, п'ятий вихід якого провідником 14 з'єднаний з п'ятим входом блоку 7 формування постумов, з шостим входом блоку 5 зберігання розмітки та четвертим входом блоку 6 пріоритетного вибору, другий вихід якого з'єднаний з другим входом блоку 4 синхронізації, перший вихід якого провідником 15 з'єднаний з третім входом блоку 6 пріоритетного вибору, з третім входом блоку 7 формування постумов, з третім входом блоку 5 зберігання розмітки та з другим входом блоку 2 виводу, вихід якого є виходом процесора. Блок зберігання вхідної дуги (фіг.2) містить чотири регістри 16-19, входи яких шиною 20 з'єднані з четвертим виходом блоку 3 програмування. Виходи 21-25 регістрів 16-19 з'єднані з другим входом аналізатора 9 вхідних дуг. Блок аналізу вхідної дуги (фіг.З) містить мультиплексер 26, суматор 27, два демультиплексери 28 та 29, елемент ЗО 4І-АБО, елемент 31 І, два елементи 32 та 33 АБО-НЕ, s+З елементи 34.1-34.s+3 HE. Інформаційні входи мультиплексера 26 шинами 35.1-35.п з'єднані з другим виходом блоку 5 розмітки, адресний вхід мультиплексера 26 шиною 21 з'єднаний з виходом блоку 8 зберігання вхідних дуг, вихід мультиплексера 26 з'єднаний з входом А суматора 27, вхід В суматора 27 з'єднаний з виходами елементів 34.1-34.s HE, на вхід С переносу суматора 27 подається сигнал «1», інформаційні виходи D суматора 27 з'єднані з інформаційними входами демультиплексера 28 та з входами елемента 33 АБО-НЕ, вихід V переносу суматора 27 з'єднаний з входом елемента 34.s+3 HE та з третьою та четвертою групою входів елемента ЗО 4І-АБО, інформаційні входи демультиплексера 28 з'єднані з виходом елемента 31 І, з виходом елемента 32 АБО-НЕ та шиною 25 з виходом блоку 8 зберігання вхідних дуг, адресний вхід демультиплексера 28 шиною 21 з'єднаний з виходом блоку 8 зберігання вхідних дуг, виходи демультиплексера 29 провідниками 36.l.i-Зб.т.і з'єднані з другим входом блоку 6 пріоритетного вибору, виходи демультиплексера 28 шинами 37.1 .і Процесор Петрі 11 З7.п.і, провідниками 38.1.і-38.п.і та 39.1.і-39.п.і, шинами 40.1.і-40.п.і з'єднані з другим входом блоку 10 формування передумов, входи елементів 34.1-34.S НЕ шиною 22 з'єднані з виходом блоку 8 зберігання вхідних дуг, виходи елементів 34.1-34.s НЕ з'єднані з входами елемента 31 І, вхід елемента 34.S+1 НЕ провідником 23'з'єднаний з виходом блоку 8 зберігання вхідних дуг, вихід елемента 34.S+1 НЕ з'єднаний з першою та другою групою входів елемента ЗО 4І-АБО, вхід елемента 34.S+2 НЕ провідником 24 з'єднаний з виходом блоку 8 зберігання вхідних дуг, вихід елемента 34.S+2 НЕ з'єднаний з першою та третьою групою входів елемента ЗО 4І-АБО, входи елемента 32 АБО-НЕ провідниками 23 та 24 з'єднані з виходом блоку 8 зберігання вхідних дуг, вихід елемента 34.S+3 НЕ з'єднаний з першою та другою групою входів елемента ЗО 4І-АБО, вихід елемента 33 АБО-НЕ з'єднаний з четвертою групою входів елемента ЗО 4І-АБО, третя та четверта група входів елемента ЗО 4І-АБО провідниками 23 та 24 в ідповідно з'єднані з виходом блоку 8 зберігання вхідних дуг, друга, третя та четверта група входів елемента ЗО 41АБО провідником 12 з'єднані з третім виходом блоку 4 синхронізації, вихід елемента ЗО 4І-АБО з'єднаний з інформаційним входом демультиплексера 29, адресний вхід якого шиною 25 з'єднаний з виходом блоку 8 зберігання вхідних дуг. ' -' Блок формування передумов позиції (фіг.4) містить к компараторів 41.141 .к та мультиплексер 42. Інформаційні входи мультиплексера 42 провідниками 38.і. 1-38.і.к, 39.і.1-39.і.к та шинами 40.і.1-40.і.к з'єднані з другим виходом аналізатора 9 вхідних дуг, адресні входи мультиплексера 42 з'єднані з виходами компараторів 41.1-41.к, входи А компараторів 41.1-41.k шинами 37.і.1-37.і.k з'єднані з другим виходом аналізатора 9 вхідних дуг, входи В компараторів 41.1-41 .к шиною 43 з'єднані з першим виходом блоку 6 пріоритетного вибору, виходи мультиплексера 42 провідниками 44.І, 45 .і та шиною 46.і з'єднані з четвертим входом блоку 7 формування постумов та з четвертим входом блоку 5 зберігання розмітки. Проц есор Пе тр і Ґ „ „ * ) 12 Блок зберігання вихідної дуги (фіг. 5) містить три регістри 47-49 та демультиплексер 50. Входи регістрів 47-49 шиною 51 з'єднані з п'ятим виходом блоку 3 програмування, виходи регістрів 47 та 48 з'єднані з інформаційними входами демультиплексера 50, виходи регістра 49 з'єднані з адресним входом демультиплексер а 50, виходи демультиплексера 50 шинами 52.1.і-52.п.і та 53.1.1-53.П і з'єднані з другим входом блоку 7 формування постумов. Блок формування постумов позиції (фіг.6) містить три мультиплексери 54-56, суматор 57, регістр 58, w компараторів 59.1-59.w, елемент 60 АБО-НЕ три елементи 61-63 АБО, п+1 елементів 64.1-64.П+1 І, причому вихід компаратора 59л з'єднаний з і-и адресним входом мультиплексера 54, вихід якого з'єднаний з всіма, крім останнього, входами елемента 61 АБО та з другим інформаційним входом мультиплексера 55, адресний вхід якого з'єднаний з виходом елемента 61 АБО, а вихід - з входом А суматора 57, вхід В якого з'єднаний з виходом регістра 58, інформаційний вхід якого з'єднаний з інформаційним виходом D суматора 57, останній вхід елемента 61 АБО з'єднаний з виходом елемента 60 АБО-НЕ, входи якого з'єднані з виходами компараторів 59.1-59.w, які, крім цього, з'єднані з входами елемента 62 АБО, вихід якого з'єднаний з першим входом елемента 64.П+1 І, вихід якого з'єднаний з першим входом елемента 63 АБО, вихід якого з'єднаний з входом С синхронізації регістра 58, виходи елементів 64.1-64.П І з'єднані з адресними входами мультиплексера 56, вихід якого з'єднаний з першим інформаційним входом мультиплексера 55, входи В компараторів 59.1-59.w шиною 43 з'єднані з першим виходом блоку 6 пріоритетного вибору, інформаційні входи мультиплексера 54 шинами 53 і 1-53.і.w з'єднані з виходом блоку 11 зберігання вихідних дуг, входи А компараторів 59.1-59.w шинами 52.1.1-52.і w з'єднані з виходом блоку 11 зберігання вихідних дуг, вхід R установки нуля регістра 58 та другий вхід елемента 63 АБО провідником 15 з'єднані з першим виходом блоку 4 синхронізації, інформаційні входи мультиплексера 56 шинами 46.146.п з'єднані з вводом блоку 10 формування передумов, входи елементів 64.164.п І провідниками 44.1-44.П та 45.1-45.П з'єднані з вводом блоку 10 Процесор Петрі 13 формування передумов, другий вхід елемента 64.П+1 І провідником 14 з'єднаний з п'ятим виходом блоку 4 синхронізації, вихід V переносу суматора 51 провідником 65 з'єднаний з третім входом блоку 4 синхронізації, вихід регістра 58 шиною 66 з'єднаний з п'ятим входом блоку 5 зберігання розмітки. Блок зберігання розмітки позиції (фіг.7) містить два мультиплексери 67 та 68, регістр 69, суматор 70, два елементи 71 та 72 АБО, п'ять елементів 73-77 І, елемент 78 НЕ, причому вихід мультиплексера 67 з'єднаний з входом В суматора 70, вхід А якого з'єднаний з виходом регістра 69, а інформаційний вихід D - з першим інформаційним входом мультиплексера 68, перший адресний вхід якого з'єднаний з виходом елемента 71 АБО, другий адресний вхід з'єднаний з виходом елемента 74 І, а вихід - з інформаційним входом регістра 69, вхід С синхронізації якого з'єднаний з виходом елемента 72 АБО, а вхід R установки нуля - з виходом елемента 77 І, другий вхід елемента 1) АБО з'єднаний з виходом елемента 73 І, другий вхід якого з'єднаний з виходом елемента 78 НЕ, другий вхід елемента 72 АБО з'єднаний з виходом елем ента 75 І, а третій вхід - з виходом елемент а 76 І, четвер тий інформаційний вхід мультиплексера 68 шиною 79 з'єднаний з другим виходом блоку 3 програмування, четвертий адресний вхід мультиплексера 68 та четвертий вхід елементіа 72 АБО провідником 80 з'єднані з другим виходом блоку 3 програмування, другі інформаційні входи мультиплексерів 67 та 68 шиною 81 з'єднані з виходом блоку 1 вводу, вхід елемента 78 НЕ та другий вхід елемента 74 І провідником 82 з'єднані з виходом блоку 1 вводу, другий вхід елемента 75 І провідником 83 з'єднаний з виходом блоку 1 вводу, адресний вхід мультиплексера 67 та перші в ходи елем ент ів 73-75 І провідником 15 з'єднані з першим виходом блоку 4 синхронізації, третій інформаційний вхід мультиплексера 68 шиною 46.і з'єднаний з виходом блоку 10 формування передумов, другий вхід елемента 76 І провідником 44.і з'єднаний з виходом блоку 10 формування передумов, другий вхід елемента 77 І провідником 45.і з'єднаний з виходом блоку 10 формування передумов, перший інформаційний вхід мультиплексера 67 шиною 66 з'єднаний з другим Процесор Петрі 14 виходом блоку 7 формування постумов, третій адресний вхід мультиплексера 68 та перші входи елементів 76 та 77 І провідником 14 з'єднані з п'ятим виходом блоку 4 синхронізації, перші входи елементів 71 та 72 АБО провідником 13 з'єднані з четвертим виходом блоку 4 синхронізації, вихід V переносу суматора 70 провідником 84 з'єднаний з першим входом блоку 4 синхронізації, вихід регістра 69 шиною 35.і з'єднаний з першим входом блоку 2 виводу та з третім входом аналізатора 9 вхідних дуг. Блок пріоритетного вибору (фіг.8) містить регістр 85, дешифратор 86, т-1 елементів 87.1-87.т-1 АБО та т блоків 88.1-88.m аналізу переходів, кожний з яких містить (фіг.9) Я^-тригер 89, мультиплексер 90, елемент 91 НЕ, елемент 92 АБО та елемент 93 АБО-НЕ, причому z-й вихід регістра 85 провідником 94.і з'єднаний з другим інформаційним входом мультиплексера 90 блоку 88.і аналізу переходу, і-й вхід дешифратора 86 провідником 95.і з'єднаний з виходом елемента 93 АБО-НЕ блоку 88.і аналізу переходу, перший вихід дешифратора 86 провідником 96.1 з'єднаний з першим інформаційним входом мультиплексера 90 блоку 88.1 аналізу переходу, виходи дешифратора 86 з 2і по 21+ -1 з'єднані з входами елемента 87.і АБО, вихід якого провідником 96.і з'єднаний з першим інформаційним входом мультиплексера 90 блоку 88.і аналізу переходу, при цьому у кожному блоці 88.і аналізу переходу (фіг.9) вихід мультиплексера 90 з'єднаний з входом S установки одиниці Я£-тригера 89 та з входом елемента 91 НЕ, вихід якого з'єднаний з входом R установки нуля /^-тригера 89, вхід синхронізації якого з'єднаний з виходом елемента 92 АБО, а пря мий вихід - з останнім в ходом елемента 93 АБО -НЕ, інформаційний вхід та вхід С синхронізації регістра шиною 97 з'єднані з першим виходом блоку 3 програмування, всі входи, крім останнього, елемента 93 АБО-НЕ провідниками 36.і.1-36.і.k з'єднані з другим виходом аналізатора 9 вхідних дуг, адресний вхід мультиплексера 90 та перший вхід елемента 92 АБО провідником 15 з'єднані з першим виходом блоку 4 синхронізації, другий вхід елемента 92 АБО провідником 14 з'єднаний з п'ятим виходом блоку 4 синхронізації, виходи елементів 87.1-87.т-1 АБО та Процесор Петрі 15 перший вихід дешифратора 86 шиною 43 з'єднані з першими входами блоків 7 та 10 формування пост- та передумов, нульовий вихід дешифратора 86 провідником 98 з'єднаний з другим входом блоку 4 синхронізації. Процесор працює^слТдуючим чином. Функціонування процесора починається з виконання операцій програмування. Для цього з блоку 4 синхронізації (фіг. 1) в блок З програмування доступає один імпульс сигналу про початок виконання операцій програмування. Після цього з блоку 3 програмування в блок 8 зберігання вхідних дуг та в блок 11 зберігання вихідних дуг записується алгоритм обробки даних у в игляді структури м ережі Петрі, в блок 5 зберігання розмітки записується початкова розмітка мережі Петрі, в блок 1 вводу записуються дані про позиції мережі Петрі, в які буде надходити інформація з датчиків об'єкту управління, та про спосіб вводу цієї інформації, в блок 6 пріоритетного вибору записуються дані про переходи, що використовуються. Дані про вхідну дугу та сигнал синхронізації запису цих даних надходять в блок зберігання вхідної дуги (фіг.2) по шині 20. В регістр 16 записується номер позиції, з якої виходить дуга, в регістр 17 - вага дуги, в регістр 18 - тип дуги, в регістр 19 - номер переходу, в який входить дуга. Дані про вихідну дугу та сигнал синхронізації запису цих даних надходять в блок зберігання вихідної дуги (фіг,5) по шині 51. В регістр 47 записується номер переходу, з якого виходить дуга, в регістр 48 - вага дуги, в регістр 49 - номер позиції, в яку в ходить д уга. Д ані про початкову розм ітку позиції та сигнал синхронізації запису цих даних надходять в блок зберігання розмітки позиції (фіг.7) відповідно по шині 79 та провіднику 80 і записуються в регістр 69. Дані про позиції мережі Петрі, в які буде надходити інформація з датчиків об'єкту управління, та про спосіб вводу цієї інформації записуються в регістр блоку І вводу (фіг. 1). Якщо у відповідному розряді регістра записана «З», то в позицію дозволені ввод інформації з датчиків, інакше - заборонені. Якщо у відповідному розряді регістра записана «1», то ввод нових даних в позицію робиться з втратою старих даних (кількіс ть м іток в позиції до Процесор Петрі 16 операції вводу замінюється на кількість міток, що відповідає новим даним), інакше, якщо у відповідному розряді регістра записану «О», то ввод нових даних в позицію робиться із збереженням старих даних (кількість міток в позиції до операції вводу додається до кількості міток, що відповідає новим даним). Дані про переходи, що використовуються, та сигнал синхронізації запису цих даних надходять в блок 6 пріоритетного вибору (фіг. 8) по шині 97 і записуються в регістр 85. Якщо перехід не використовується процесором (число переходів в структурі мережі Петрі менше, ніж може запускати процесор), то у відповідному розряді регістра 85 записується «1», інакше «0». Коли всі блоки процесора запрограмовані, з блоку З програмування (фіг. 1) в блок 4 синхронізації,поступає один імпульс сигналу про закінчення операцій програмування. Після цього водночас виконуються операції вводу даних, що надійшли з датчиків об'єкту управління, та операції виводу даних для виконавчих механізм ів об'єкту управління. Для цього з блоку 4 синхронізації по провіднику 15 в блок 5 зберігання розмітки та в блок 2 виводу поступає один імпульс сигналу синхронізації операцій вводу-виводу. Інформація, отримана з датчиків об'єкту управління, дані про дозвіл та спосіб вводу цієї інформації надходять з блоку 1 вводу в блок зберігання розмітки позиції (фіг.7) відповідно по шині 81 і провідникам 83 та 82. Якщо запис інформації в позицію дозволений (по провіднику 83 ,гю£тугшє сигнал «1»), то по задньому фронту імпульсу сигналу синхронізації по провіднику 15 в регістр 69 буде записана нова розмітка позиції. В противному випадку (по провіднику 83 і^тЬстунає сигнал «0») запис в регістр 69 зроблений не буде. Якщо ввод нових даних в позицію робиться з збереженням старих даних (по провіднику 82

ДивитисяДодаткова інформація

Назва патенту англійськоюPetri processor

Автори англійськоюYelchaninov Dmytro Borysovych, Mateichenko Viktor Valentynovych, Loboda Vitalii Havrylovych, Petryshyn Yurii Stepanovych

Назва патенту російськоюПроцессор петри

Автори російськоюЕльчанинов Дмитрий Борисович, Матейченко Виктор Валентинович, Лобода Виталий Гаврилович, Петришин Юрий Степанович

МПК / Мітки

МПК: G06F 15/16, G06F 19/00, G06F 13/00

Код посилання

<a href="https://ua.patents.su/33-32183-procesor-petri.html" target="_blank" rel="follow" title="База патентів України">Процесор петрі</a>

Попередній патент: Пристрій для експериментального визначення концентраційних меж розповсюдження полум’я генераторних газів

Наступний патент: Спосіб підвищення рухливості сперміїв людини

Випадковий патент: Солі s-похідних 1,2,4-триазолів, що стимулюють ріст насіння соняшнику