Частотно-фазовий дискримінатор

Номер патенту: 5206

Опубліковано: 28.12.1994

Автори: Соколов Михайло Михайлович, Нейлюк Володимир Макарович, Дейсман-Косіянчук Степан Петрович, Таран Володимир Михайлович

Формула / Реферат

(57) Частотно-фазовый дискриминатор, содержащий первый и второй D-триггеры, D-входы которых соединены с нулевой шиной, а С-входы являются соответственно первыми вторым входами частотно-фазового дискриминатора, JK-триггер и первый и второй элементы И-НЕ, при этом первый вход первого элемента И-НЕ соединен с инверсным выходом первого D-триггера и J-bxoдом JK-триггера, второй вход соединен с прямым выходом JK-триггера и является вы ходом частотно-фазового дискриминатора, а выход соединен с S-входом первого D-триггера, первый вход второго элемента И-НЕ соединен с инверсным выходом второго D-триггера и К-входом JK-триггера, второй вход соединен с инверсным выходом JK-триггера, а выход соединен с S-входом второго D-триггера, отличающий-с я тем, что в него введены первый, второй и третий элементы НЕ, а также элемент 2И-ИЛИ-НЕ, первый и второй входы которого соединены с первым входом, а через первый элемент НЕ - со вторым входом частотно-фазового дискриминатора соответственно, третий и четвертый входы соединены со вторым входом, а через второй элемент НЕ - с первым входом частотно-фазового дискриминатора, а выход через третий элемент НЕ соединен с С входом JK-триггера.

Текст

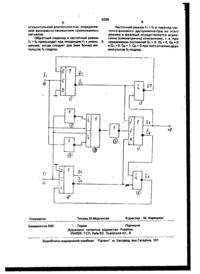

Частотно-фазовый дискриминатор, содержащий первый и второй D-триггеры, Dвходы которых соединены с нулевой шиной, а С-входы являются соответственно первым и вторым входами частотно-фазового дискриминатора, JK-триггер и первый и второй элементы И-НЕ, при этом первый вход первого элемента И-НЕ соединен с инверсным выходом первого D-триггера и J-BXO дом JK-триггера, второй вход соединен с прямым выходом JK-триггера и является выходом частотно-фазового дискриминатора, а выход соединен с S-входом первого D-триггера, первый вход второго элемента И-НЕ соединен с инверсным выходом второго D-триггера и'К-входом JK-триггера, второй вход соединен с инверсным выходом JK-триггера, а выход соединен с S-входом второго D-триггера, о т л и ч а ю щ и й с я тем, что в него введены первый, второй и третий элементы НЕ, а также элемент 2И-ИЛИ-НЕ, первый и второй входы которого соединены с первым входом, а через первый элемент НЕ - со вторым входом частотно-фазового дискриминатора соответственно, третий и четвертый входы соединены со вторым входом, а через второй элемент НЕ - с первым входом частотно-фазового дискриминатора, а выход через третий элемент НЕ соединен с С входом JK-триггера. С > сл ю 8 Изобретение относится к радиотехнике и может быть использовано для частотно-фазовой дискриминации двух потоков импульсов. Наиболее близким по технической сущности к заявляемому является частотно-фазовый дискриминатор (ЧФД), содержащий два D-триггера, входы синхронизации которых соединены со входными шинами, выход первого D-триггера соединен с первым входом первого элемента И-НЕ, а выход второго D-триггера соединен с первым входом второго элементе которого соедине ! с выхоДами упрмянутых Ы D-триггеров. а вы одьщміш^ени со вторьд інформаціГ ми входами логических элементов И-НЕ, выходы которых соединены с установочными входами соответствующих D-триггеров. Недостатком этого устройства является ограниченная область его использования, обусловленная использованием в нем только ассинхронного jk-триггера. Наличие такого ограничения не позволяет широко применять указанный ЧФД при его различных микросхемных реализациях с сохранением высокой точности дискриминации. В основу изобретения поставлена задача усовершенствования частотно-фазового О 5206 дискриминатора, в котором путем стабиливходы первого элемента НЕ 3 и элемента 2 зации дискриминационной характеристики И-ИЛИ-НЕ 9 формирует синхроимпульс, повышается точность. поступающий на С-вход jk-триггера 6, и подПоставленная задача решается тем, что тверждает исходное состояние Qi = 1, Qe в 1 в частотно-фазовый дискриминатор, содер- 5 и, следовательно, состояние jk-триггера 6 не жащий первый и второй D-триггеры, D-BXOпоменяется. ды которых соединены с нулевой миной, а В исходном состоянии Qi = 0, Q? = 0i, С-входы являются соответственно первым и Об = 1 поступление импульса частоты f, и вторым входами частотно-фазового дискрисоответствующего ему синхроимпульса на минатора, jk-триггер и первый и второй эле- 10 С-вход jk-триггера 6 обуславливает состояменты И-НЕ, при этом первый вход первого ние Qi = 0, а затем следует подтверждение элемента И-НЕ соединен с инверсным выОб = 1. Следовательно, состояние меняется ходом первого D-триггера и J-входом jk-тригпри поступлении синхроимпульса на С-вход гера, второй вход соединен с прямым jk-триггера 6. выходом jk-триггера и является выходом ча- 15 стотно-фазового дискриминатора, а выход Таким образом, поступление каждого соединен с S-входом первого D-триггера, импульса частоты изменяет состояние JKпервый вход второго элемента И-НЕ соедитриггера, за исключением состояния Qi - 1, нен с инверсным выходом второго D-триггеQ2 = 0, Об = 1, которое лишь подтверждаетра и К-входом JK-триггера, второй вход 20 ся. соединен с инверсным выходом jk-триггера, По соображениям симметрии работы а выход соединен с S-входом второго Dможно сделать вывод, что поступление имтриггера, согласно изобретению, введены пульса частоты h на второй вход 11 изменяпервый, второй и третий элементы НЕ, а ет состояние JK-триггера в обратном также элемент 2И-ИЛИ-НЕ, первый и вто- 25 направлении, за исключением состояния рой входы которого соединены с первым Qi m 0, Ог = 1, Об = 0, которое лишь подтвервходом, а через первый элемент НЕ - со ждается. вторым входом частотно-фазового дискриРассмотрим работу в частотных и фазоминатора соответственно, третий и четвервых режимах. тый входы соединены со вторым входом, а 30 При частоте следования импульсов h > f 1 через второй элемент НЕ - с первым входом неизбежно оказывается состояние Qi = 1, Ог частотно-фазового дискриминатора, а выход * 0, Об = 1. Затем при поступлении импульса через третий элемент НЕ соединен с С-вхоТ следует переход в состояние Qi = 0, Ог ' 0, 2 дом jk-триггера. Об = 1, а при наличии импульса f і происходит 35 возврат в то же состояние или подтверждеНа чертеже представлена электричение состояния. ская структурная схема частотно-фазового Чередование этих состояний характеридискриминатора. зует частотный режим при частотах следоваЧастотно-фазовый дискриминатор сония импульсов f2 > f i , в котором выходной держит первый 1 и второй 2 D-триггеры. 40 сигнал Об = 1. первый 3 и второй 4 и третий 5 элементы НЕ, Если в ходе процесса под воздействиjk-триггер б, первый 7 и второй 8 элементы ем обратной связи частота f i увеличиваетИ-НЕ, элемент 2 И-ИЛИ-НЕ 9, первый 10 и ся и достигает частоты f2, то при тенденции второй 11 входы и выход 12 частотно-фазок дальнейшему ее увеличению создается вого дискриминатора. 45 ситуация, когда поступают два подряд импульса частоты f i . При этом происходит переход в состояние Qi = 0, Q2 = 0, Об - 0 и Частотно-фазовый дискриминатор равыходной сигнал через воздействие обратботает следующим образом. ной связи создает тенденцию к уменьшеИмпульсы сравниваемых частот f i и тг поступают на С-входы первого 1 и второго 2 50 нию частоты f i . Если далее поступает D-триггеров соответственно. Синхроимимпульс частоты f 1, то происходит переход пульсы, поступающие на С-вход jk-триггера в состояние Qt = 1, Ог = 0, Об = 1. что 6, образуются из импульсов сравниваемых создает тенденцию к увеличению частоты f 1 частот одновременно из любого пришедшеи т. д. го импульса f і или І2. 55 Таким образом, в фазовом режиме Рассмотрим процессы изменения состоЧФД происходит чередование состояний яний jk-триггера 6 при поступлении импульQi - 0, Ог - 0. Qe = 1 и Qi = 0, Ог - 0, Qe = 0, сов частоты fi на первый вход 10. частоты f і и f2 уравниваются соответственВ исходном состоянии Qi = 1, О г в 0 , но изменениям сигнала Об = 1 и Qe - 0 с Об * 1 поступление импульса частоты fi на = 5206 относительной длительностью, определяемой фазорассогласованием сравниваемых сигналов. Обратный переход в частотный режим f і > f2 происходит при тенденции f і к уменьшению, когда следует два (или более) импульсов h подряд. Упорядник Замовлення 599 Частотный режим f 1 > f2 и переход частотно-фазового дискриминатора из этого режима в фазовый осуществляется аналогично (симметрично) описанному, т. е. при чередовании состояний Qi « 0, Q2 - 0, Qe в О и Qі • 0, Ог ' 1, Qe в 0 при поступлении двух • импульсов h подряд. Техред М Моргентал Коректор М. Керецман * Тираж Підписне Державне патентне відомство України, 254655. ГСП, КиТв-53, Львівська пл., 8 Виробничо-видавничий комбінат "Патент", м. Ужгород, вул.Гагаріна, 101

ДивитисяДодаткова інформація

Назва патенту англійськоюFrequency-phase discriminator

Автори англійськоюDeisman-Kosiianchuk Stepan Petrovych, Sokolov Mykhailo Mykhailovych, Taran Volodymyr Mykhailovych

Назва патенту російськоюЧастотно-фазовый дискриминатор

Автори російськоюДейсман-Косиянчук Степан Петрович, Соколов Михаил Михайлович, Таран Владимир Михайлович

МПК / Мітки

МПК: H03D 13/00

Мітки: дискримінатор, частотно-фазовий

Код посилання

<a href="https://ua.patents.su/4-5206-chastotno-fazovijj-diskriminator.html" target="_blank" rel="follow" title="База патентів України">Частотно-фазовий дискримінатор</a>

Попередній патент: Генератор серії імпульсів

Наступний патент: Цифровий вимірювач інтервалів часу

Випадковий патент: Спосіб отримання фармацевтичної композиції ранозагоюючої та регенеруючої дії на основі пептидів дермального шару свиней