Фазометр

Номер патенту: 65165

Опубліковано: 15.03.2004

Формула / Реферат

1. Фазометр, що містить перший пристрій вибору і зберігання дійсної частини амплітуди сигналу х, другий пристрій вибору і зберігання уявної частини амплітуди сигналу у, перший і другий блоки перемножування, перший блок обчислення арктангенса сигналу х і блок обчислення різниці фаз двох гармонічних сигналів, який відрізняється тим, що в нього введені перший і другий аналізатори, входи яких є входами досліджуваних сигналів х і у, перший і другий блоки корекції, підключені виходами до входів першого і другого блоків перемножування, а входами - до виходів першого і другого аналізаторів відповідно, перший пристрій вибору і зберігання уявної частини амплітуди сигналу х, другий пристрій вибору і зберігання дійсної частини амплітуди сигналу у, перший і другий блоки обчислення відношення уявної і дійсної частин амплітуди сигналів і другий блок обчислення арктангенса сигналу у, причому виходи першого і другого аналізаторів підключені також до входів пристроїв вибору і зберігання уявної і дійсної частин амплітуди сигналу х і до входів пристроїв вибору і зберігання уявної і дійсної частин амплітуди сигналу у відповідно; виходи пристроїв вибору і зберігання уявної і дійсної частин амплітуди сигналу х підключені до входу блока обчислення відношення уявної і дійсної частин амплітуди сигналу х, підключеного виходом до входу першого блока перемножування, а виходи пристроїв вибору і зберігання уявної і дійсної частин амплітуди сигналу у підключені до входу блока обчислення відношення уявної і дійсної частин амплітуди сигналу у, підключеного виходом до входу другого блока перемножування; виходи першого і другого блоків перемножування підключені до входів першого і другого блоків обчислення арктангенсів сигналів х і у відповідно, виходи яких підключені до входів блока обчислення різниці фаз двох гармонічних сигналів.

2. Фазометр за п. 1, який відрізняється тим, що блок корекції містить зсувні регістри, перший і другий блоки порівняння кодів, перший і другий суматори, перший і другий помножувачі, перший, другий, третій, четвертий елементи І, перший, другий, третій елементи АБО, перший блок пам'яті, подільник, а також додаткові елементи для обчислення коригувального множника: другий, третій і четвертий подільники, третій і четвертий помножувачі, п'ятий елемент І, третій, четвертий, п'ятий, шостий, сьомий суматори, обчислювач кількості періодів сигналу на відрізку аналізу і другий блок пам'яті, причому перший і другий входи другого подільника підключені до виходів третього і четвертого суматорів, перші входи яких підключені до виходу першого елемента АБО, а другі входи - до другого виходу першого зсувного регістра, вихід другого подільника підключений до входу шостого суматора, другий вхід якого з'єднаний через третій помножувач і п'ятий суматор з обчислювачем кількості періодів сигналу на відрізку аналізу; вихід шостого суматора підключений до першого входу третього подільника, другий вхід якого з'єднаний з виходом третього помножувача; вхід обчислювача кількості періодів сигналу на відрізку аналізу підключений до виходу аналізатора, а його вихід - до входу п'ятого елемента І, другий вхід якого з'єднаний з першим блоком порівняння кодів, а вихід підключений до входу сьомого суматора, вихід якого з'єднаний з першим входом четвертого помножувача, а його вихід з'єднаний із другим входом четвертого подільника; перший вхід четвертого подільника підключений до виходу п'ятого суматора, а його вихід з'єднаний із входом другого блока пам'яті, що також з'єднаний з виходом третього подільника.

Текст

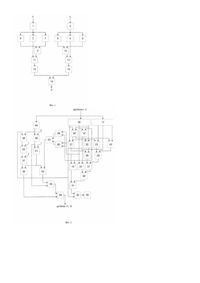

Винахід відноситься до області вимірювальної техніки і призначений для вимірювання різниці фаз двох гармонічних сигналів у широкому динамічному діапазоні. Відомий пристрій для вимірювання фазового зсуву між двома напругами [1], що містить два ключових детектори і загальний допоміжний гетеродин-генератор синуса з частотою, близькою до частоти в кратне число раз більшої від частоти вимірюваних коливань, а також перетворювачі синуса в гострі імпульси, і фільтри низьких частот, що виділяють обвідну, а вимірюють фазометром різницю фаз між обвідними, котра дорівнює шуканій різниці фаз, помноженій на коефіцієнт кратності між частотою генератора і частотою досліджуваного сигналу. Такий пристрій вимірює замість шуканого значення різниці фаз інші значення різниці фаз, при цьому вимірюють також і відношення частот, тому точність такого пристрою зовсім невисока. Найбільш близьким по технічній сутності до пропонованого винаходу є вимірювач зсуву фаз [2], узятий як прототип, що містить синхронізатор і формувач, по входах з'єднані з входом опорного сигналу, стробоскопічний перетворювач, першим входом підключений до входу досліджуваного сигналу, подільник частоти, першим входом з'єднаний з формувачем, а другим - з виходом синхронізатора, аналого-цифровий перетворювач, входом з'єднаний з виходом стробоскопічного перетворювача, запам'ятовуючий елемент, перший і другий суматори, перший регістр дійсної частини x (перший пристрій вибору і зберігання дійсної частини амплітуди сигналу x ) і другий регістр уявної частини y (другий пристрій вибору і зберігання уявної частини амплітуди сигналу y ), з'єднаний по входу з виходом другого суматора, перший перемножувач (перший блок перемножування), першим входом з'єднаний з першим виходом запам'ятовуючого елемента, а виходом - з першим входом першого суматора, другий перемножувач, першим входом підключений до другого виходу запам'ятовуючого елемента, а виходом - до першого входу другого суматора, обчислювач (перший блок обчислення арктангенса сигналу x ), входами з'єднаний з виходами першого і другого регістрів, блок віднімання (блок обчислення різниці фаз двох гармонічних сигналів), першим входом з'єднаний з виходом першого суматора, а виходом - із входом першого регістра, третій перемножувач (другий блок перемножування), перший вхід якого з'єднаний з виходом другого регістра, другий вхід - із другим виходом запам'ятовуючого елемента, а вихід - із другим входом блоку віднімання, четвертий перемножувач, перший вхід якого з'єднаний з виходом другого регістра, другий вхід - з першим виходом запам'ятовуючого елемента, а вихід - із другим входом другого суматора, другі входи першого і другого перемножувачів підключені паралельно до виходу першого регістра, вихід аналого-цифрового перетворювача з'єднаний із другим входом першого суматора, другий вхід стробоскопічного перетворювача, керуючі входи аналого-цифрового перетворювача, першого і другого регістрів і запам'ятовуючого елемента паралельно з'єднані з виходом синхронізатора, вихід подільника частоти з'єднаний з керуючим входом обчислювача. Вимірювання фазового зсуву забезпечується за допомогою пристрою, в основі якого закладено використання в зворотному зв'язку ланки виду exp jwt , тобто комплексного резонатора, а цей підхід зменшує смугу пропускання і таким чином обмежує діапазон вимірювання. Використання зворотного зв'язку обмежує також точність вимірювання. В основу винаходу поставлена задача удосконалити фазометр шляхом виключення стробоскопічного перетворювача, аналого-цифрового перетворювача, каналу опорного сигналу, поділу на два ідентичні канали сигналів x і y і введення двох блоків корекції, які здійснюють вибір двох пар найбільших сусідніх вибірок гармонічних сигналів, а також формування коригувальних множників, що забезпечує підвищення точності вимірювання і розширення діапазону вимірювання. Поставлена задача вирішується тим, що у фазометрі, який містить перший пристрій вибору і зберігання дійсної частини амплітуди сигналу x , другий пристрій вибору і зберігання уявної частини амплітуди сигналу y , перший і другий блоки перемножування, перший блок обчислення арктангенса сигналу x і блок обчислення різниці фаз двох гармонічних сигналів, новим є те, що в нього додатково введені перший і другий аналізатори, входи яких є входами досліджуваних сигналів x і y , перший і другий блоки корекції, підключені виходами до входів першого і другого блоків перемножування, а входами - до виходів першого і другого аналізаторів відповідно, перший пристрій вибору і зберігання уявної частини амплітуди сигналу x , другий пристрій вибору і зберігання дійсної частини амплітуди сигналу y , перший і другий блоки обчислення відношення уявної і дійсної частин амплітуди сигналів і другий блок обчислення арктангенса сигналу y , причому виходи першого і другого аналізаторів підключені також до входів пристроїв вибору і зберігання уявної і дійсної частин амплітуди сигналу x і до входів пристроїв вибору і зберігання уявної і дійсної частин амплітуди сигналу y відповідно; виходи пристроїв вибору і зберігання уявної і дійсної частин амплітуди сигналу x підключені до входу блоку обчислення відношення уявної і дійсної частин амплітуди сигналу x , підключеного виходом до входу першого блоку перемножування, а виходи пристроїв вибору і зберігання уявної і дійсної частин амплітуди сигналу y підключені до входу блоку обчислення відношення уявної і дійсної частин амплітуди сигналу y , підключеного виходом до входу другого блоку перемножування; виходи першого і другого блоків перемножування підключені до входів першого і другого блоків обчислення арктангенсів сигналів x і y відповідно, виходи яких підключені до входів блоку обчислення різниці фаз двох гармонічних сигналів. Крім того кожен блок корекції містить зсувні регістри, перший і другий блоки порівняння кодів, перший і другий суматори, перший і другий помножувачі, перший, другий, третій, четвертий елементи І, перший, другий, третій елементи АБО, перший блок пам'яті, подільник, а також додаткові елементи для обчислення коригувального множника: другий, третій і четвертий подільники, третій і четвертий помножувачі, п'ятий елемент І, третій, четвертий, п'ятий, шостий, сьомий суматори, підраховувач кількості періодів сигналу на відрізку аналізу і другий блок пам'яті, причому перший і другий входи другого подільника підключені до виходів третього і четвертого суматорів, перші входи яких підключені до виходу першого елемента АБО, а другі входи - до другого виходу першого зсувного регістра, вихід другого подільника підключений до входу шостого суматора, другий вхід якого з'єднаний через третій помножувач і п'ятий суматор з підраховувачем кількості періодів сигналу на відрізку аналізу; вихід шостого суматора підключений до першого входу третього подільника, другий вхід якого з'єднаний з виходом третього помножувача; вхід підраховувача кількості періодів сигналу на відрізку аналізу підключений до виходу аналізатора, а його вихід - до входу п'ятого елемента І, другий вхід якого з'єднаний з першим блоком порівняння кодів, а вихід підключений до входу сьомого суматора, вихід якого з'єднаний з першим входом четвертого помножувача, а його вихід з'єднаний із другим входом четвертого подільника; перший вхід четвертого подільника підключений до виходу п'ятого суматора, а його вихід з'єднаний із входом другого блоку пам'яті, що також з'єднаний з виходом третього подільника. Збільшення точності вимірювання різниці фаз досягається шляхом помноження відношення уявної і дійсної ö æ 2n ÷ ç ç 2n + 1- Z ÷ 1 ø при gn > gn+1 , і на коригувальний частин амплітуди сигналів x і y на коригувальний множник è æ 2(n + 1) ö ÷ ç ç 2n + 1- Z ÷ 1 ø 1 при gn gn +1 F ï ê Re{ x,n } è 1 øú û ë ˆ j=í é Im Fy,n+1 æ 2(n + 1) ö ù ï ÷ú ç ïarctg ê ÷ ç ê Re Fy,n+1 è 2n + 1 - Z1 ø ú ï û ë ï é Im{ x,n +1} æ 2(n + 1) öù F ï ÷ú, gn > gn+1. ç ï- arctg ê Re{ Fx,n +1} ç 2n + 1- Z1 ÷ú ê øû è ë î На фіг.1 представлена структурна схема фазометра, на фіг.2 - приклад побудови блоку корекції. Пристрій містить перший і другий аналізатори 1, 2, перший і другий блоки корекції 3, 4, перший і другий пристрої 5, 6 вибору і зберігання уявної частини амплітуди сигналів, перший і другий пристрої 7, 8 вибору і зберігання дійсної частини амплітуди сигналів, перший і другий блоки обчислення відношення уявної і дійсної частин амплітуди сигналів 9, 10, перший і другий блоки перемножування 11, 12, перший і другий блоки обчислення арктангенсів сигналів 13, 14 і блок обчислення різниці фаз двох гармонічних сигналів 15. Причому виходи аналізаторів 1, 2 підключені до входів пристроїв 5, 6 вибору і зберігання уявної частини амплітуди сигналів, до входів пристроїв 7, 8 вибору і зберігання дійсної частини амплітуди сигналів відповідно і до входів блоків корекції 3, 4, причому пристрої 5, 7 вибору і зберігання уявної і дійсної частин амплітуди сигналу x підключені до блоку обчислення відношення уявної і дійсної частин амплітуди сигналу x - 9, підключеного до входу блоку перемножування 11, другий вхід якого з'єднаний з виходом блоку корекції 3, а пристрої 6, 8 вибору і зберігання уявної і дійсної частин амплітуди сигналу y підключені до блоку обчислення відношення уявної і дійсної частин амплітуди сигналу y - 10, підключеного до входу блоку перемножування 12, другий вхід якого з'єднаний з виходом блоку корекції 4; виходи блоків перемножування 11, 12 підключені до входів блоків обчислення арктангенсів сигналів x і y 13,14 відповідно, виходи яких підключені до входів блоку обчислення різниці фаз двох гармонічних сигналів 15. Блок корекції 3 (фіг.2) містить зсувні регістри 16, 17, перший блок 18 порівняння кодів, перший суматор 19, перший помножувач 20, перший, другий, третій, четвертий елементи І 21-24, другий блок 25 порівняння кодів, перший елемент АБО 26, другий помножувач 27, другий елемент АБО 28, другий суматор 29, перший блок 30 пам'яті, подільник 31, третій елемент АБО 32, а також додаткові елементи для обчислення коригувального множника: другий, третій і четвертий подільники 33-35, третій і четвертий помножувачі 36 і 37, п'ятий елемент І 38, третій, четвертий, п'ятий, шостий, сьомий суматори 39, 40, 41, 42, 43, підраховувач кількості періодів сигналу на відрізку аналізу 44 і другий блок 45 пам'яті. Входами блоку корекції є входи блоків 16, 17, 44, а його виходом вихід блоку 45. Причому перший і другий входи другого подільника 33 підключені до виходів третього і четвертого суматорів 39, 40, перші входи яких підключені до виходу першого елемента АБО 26, а другі входи - до другого виходу першого зсувного регістра 16. Вихід другого подільника 33 підключений до входу шостого суматора 42, на другий вхід якого надходить інформація від підраховувача кількості періодів сигналу на відрізку аналізу 44 через третій помножувач 36, на другому вході якого встановлений код числа двійка, і через п'ятий суматор 41, на другому вході якого встановлений код числа одиниця. Вихід шостого суматора 42 підключений до першого входу третього подільника 34, другий вхід якого з'єднаний з виходом третього помножувача 36. Вхід підраховувача кількості періодів сигналу на відрізку аналізу 44 підключений до виходу аналізатора 1, а його вихід - до входу п'ятого елемента І 38, другий вхід якого з'єднаний з першим блоком 18 порівняння кодів, а вихід підключений до входу сьомого суматора 43, на другому вході якого встановлений код числа одиниця. Вихід сьомого суматора 43 з'єднаний з першим входом четвертого помножувача 37, на другому вході якого встановлений код числа двійка, а його вихід з'єднаний із другим входом четвертого подільника 35. Перший вхід четвертого подільника 35 підключений до виходу п'ятого суматора 41, а його вихід з'єднаний із входом другого блоку 45 пам'яті, що також з'єднаний з виходом третього подільника 34. Аналогічним образом виконаний блок корекції 4. Фазометр працює в такий спосіб. Сигнали, зсув фаз між якими необхідно виміряти, надходять на входи аналізаторів 1, 2, що виконують F перетворення Фур'є (ПФ). З виходів аналізаторів 1, 2 коди вибірок спектрів Fx і y послідовно передаються на входи двох пар пристроїв 5, 6, 7, 8 вибору і зберігання уявної і дійсної частин амплітуди сигналів і на входи двох блоків корекції 3, 4, що здійснюють вибір двох пар найбільших сусідніх вибірок гармонічних сигналів, а також формування коригувальних множників, коди яких надходять на перші входи блоків перемножування 11, 12. З { } { } { { } } виходів двох пар пристроїв 5, 6, 7, 8 вибору і зберігання уявної і дійсної частин амплітуди сигналів коди уявної і дійсної частин амплітуди сигналів надходять на входи двох блоків обчислення відношення уявної і дійсної частин амплітуди сигналів 9, 10, а результати обчислення передаються на другі входи блоків перемножування 11, 12. Результати перемножування з виходу блоків перемножування 11, 12 надходять на входи двох блоків обчислення арктангенсів сигналів 13, 14, на виходах яких формуються коди від виконання операції знаходження арктангенса, що далі надходять на входи блоку обчислення різниці фаз двох гармонічних сигналів 15, на виході якого формується код, що представляє вимірюване значення різниці фаз двох гармонічних сигналів. Обчислення в блоці корекції проводяться в такий спосіб. F З виходу аналізатора 1 коди вибірок спектрів Fx чи y послідовно передаються в зсувний регістр 16. Регістр одночасно вміщує 3 числа і має відповідно 3 виходи. З першого і третього виходів регістра коди вибірок g1 і g3 , надходять на входи блоку 25 порівняння кодів і через елементи 121 чи 22 можуть бути передані на один із входів елемента АБО 26. На виходах блоку 25 порівняння формуються сигнали дозволу для елементів І 21 і 22 таким чином, що на вихід елемента АБО 26 передається код більшої з вибірок g1 і g3 . Код вибірки gn на виході елемента АБО 26 порівнюється в блоці 18 порівняння з кодом вибірки g2 на другому виході регістра 16. Якщо g2 > gn , то на виході блоку 18 порівняння формується сигнал дозволу, що підтверджує, що три числа на виходах регістра 16 відповідають локальному максимуму спектра сигналу, причому вибірки g2 і gn є найбільшими сусідніми в цьому максимумі, а вибірка g2 - максимальна. Аналогічним образом сигнал формується блоками 23, 24, 27, 28, 29, 30, 31, 32 при g2 < gn . Коди вибірок g2 і gn надходять на входи суматорів 39, 40, у яких відбуваються операції їхнього віднімання і додавання. Результат віднімання як ділене і результат додавання як дільник надходять у подільник 33, а код частки від ділення с виходу подільника 33 надходить у якості віднімаючого в суматор 42, куди також надходить сформований елементами 44, 36, 41 код суми 2n + 1 . Код на виході суматора 42 надходить у подільник 34, куди також передається в якості діленого 2n код з виходу помножувача 36. На виході подільника 34 формується код ö æ 2n ÷ ç ç 2n + 1- Z ÷ 1 ø . У випадку, якщо gn < gn +1 елемент І 38, одержавши сигнал дозволу від коригувального множника è першого блоку 18 порівняння кодів, підключає елементи 43, 37, 35, для формування коригувального множника æ 2(n + 1) ö ç ÷ ç 2n + 1- Z ÷ 1 ø . Коди коригувальних множників надходять у блок 45 пам'яті, у якому зберігаються і передаються в è блоки перемножування 11, 12 результати вимірювань. Таким чином, для компенсації похибки вимірювання різниці фаз гармонічних сигналів з дискретними значеннями частот, для яких формуються вибірки спектрів сигналів методом ПФ, у пристрої автоматично виробляються правки для корекції результатів вимірювань. Джерела інформації: 1. Авторське свідоцтво СРСР №458777, МКП G01R25/00, 1975. 2. Авторське свідоцтво СРСР №1366966, МКП G01R25/00, 1988.

ДивитисяДодаткова інформація

Назва патенту англійськоюPhase-angle meter

Назва патенту російськоюФазометр

МПК / Мітки

МПК: H03K 5/22, G01R 25/00

Мітки: фазометр

Код посилання

<a href="https://ua.patents.su/4-65165-fazometr.html" target="_blank" rel="follow" title="База патентів України">Фазометр</a>

Попередній патент: Спосіб боротьби з пилоутворенням

Наступний патент: Контейнер транспортно-захисний для твердих екологічно небезпечних та радіоактивних відходів

Випадковий патент: Давач для вимірювання атмосферної корозії металевих конструкцій