Пристрій статистичного кодування та декодування факсимільних сигналів

Номер патенту: 8392

Опубліковано: 29.03.1996

Автори: Балькін Геннадій Федорович, Голосний Валентин Іванович, Сапунков Михайло Наумович, Зайченко Олександр Григорович

Формула / Реферат

Устройство статистического кодирования и декодирования факсимильных сигналов, содержащее на передающей стороне входной делитель, выход которого соединен с входом кодера видеосигнала и через формирователь разделительных бит и формирователь бит описания с двумя первыми входами сумматора, выход которого подключен ко входу первого буферного блока, а на приемной стороне последовательно соединенные второй буферный блок, дешифратор разделительных бит, распределитель и декодер видеосигнала, первый выход которого является выходом устройства, а второй выход соединен с управляющим входом второго буферного блока, отличающееся тем, что, с целью увеличения помехоустойчивости, в него введены на передающей стороне последовательно соединенные счетчик-накопитель и формирователь данных о числе кодовых бит, включенные между выходом входного делителя и первым дополнительным входом сумматора, и последовательно соединенные блок управления и запоминающий блок, включенные между выходом кодера видеосигнала и вторым дополнительным входом сумматора, причем выход кодера видеосигнала соединен с вторым входом счетчика-накопителя, а дополнительный выход кодера видеосигнала - с вторым входом запоминающего блока, а на приемной стороне последовательно соединенные приемник данных о числе кодовых бит и элемент сравнения, включенные между дополнительным выходом распределителя и вторым входом декодера видеосигнала, второй выход которого соединен с вторым входом элемента сравнения.

Текст

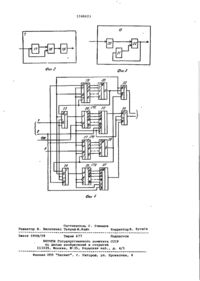

УСТРОЙСТВО СТАТИСТИЧЕСКОГО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ФАКСИМИЛЬНЫХ СИГНАЛОВ, содержащее на передающей стороне входной делитель, выход которого соединен с входом кодера видеосигнала и через формирователь разделительных Сит и формирователь бит описания с двумя первыми входами сумматора, выход которого подключен ко входу первого буферного бл'ока, а на приемной стороне последовательно соединенные второй буферный блок, дешифратор разделительных бит, распределитель и декодер видеосигнала, первый, выход которого является выходом устройства, а второй выход соединен с управ ;ляющим входом второго буферного блока, о т л и ч а ю щ е е с я тем, что, с целью увеличения помехоустойчивости, в него введены на передающей стороне последовательно соединенные счетчик-накопитель и формирователь данных о числе кодовых бит, включенные между выходом входного делителя н первым дополнительным входом сумматора, и последовательно соединенные блок управления и запоми нающий блок, включенные между выходом кодера видеосигнала и вторым дополнительным входом сумматора,* причем выход кодера видеосигнала соединен с вторым входом счетчиканакбпителя, а дополнительный выход кодера видеосигнала -' с вторым входом запоминающего блока, а на приемной стороне последовательно соединенные приемник данных о числе кодовых бит и элемент сравнения, включенные между дополнительным выходом распределителя и вторым входом декодера видеосигнала, второй выход которого соединен с вторым входом элемента сравнения. 1 1040623 Изобретение относится к факсимильра оидеосигнала - с вторым входом ной технике, в частности к устройстзапоминающего блока, а на приемной вам сжатия объема передаваемых сигстороне последовательно соединенные налов путем статистического кодироприемник данных о числе кодовых бит вания, и может быть использовано для и элемент сравнения, включенные между передачи информации, закодированной 5 дополнительным выходом распределителя как равномерным, так и неравномери вторым входом декодера видеосигнала, ным кодом. 'второй выход которого соединен с вторым входом элемента сравнения. Известно устройство статистичесНа фиг. 1 представлена структуркого кодирования и декодирования факсимильных сигнапоз, которое на 10 ная электрическая схема устройства статистического кодирования и декопередающей стороне '-одержит входной дирования факсимильных сигналов; делитель видеосигнала. Ьыход делителя на фиг. 2 - структурная электричесподан на кодер видеосигнала, формикая схема формирователя данных о рователь разделительных бит, формирователь бит описания, формирователь \ 5 числе кодовых бит; на фиг. 3 - структурная электрическая схема приемника сигнала адреса, выходы которы;: чеданных о числе кодовых бит; на рез последовательно соединенные фиг. 4 - структурная электрическая сумматор и первый буферный блок подасхема блока управления и запоминаюны в канал связи. Кроме того, дополнительный выход кодера видеосигнала 20 щего блока для случая применения неравномерного кода (модифицироподключен к дополнительному входу ванного кода Хаффмена (МКХ). * формирователя сигнала адрес. На приемной стороне известное устройство Устройство статистического кодисодержит последовательно соединенрования и декодирований факсимильных ные второй буферный блок, дешифратор тЦ сигналов (фиг. 1) содержит на переразделительных бит, распределитель, дающей стороне входной делитель 1, дешифратор сигнала адреса и дековыход которого соединен с первым дер [ 1 ] . входом счетчика-накопителя 2 и со входами кодера 3 видеосигнала, Недостаток известного устройства формирователя 4 разделительных бит, заключается в сравнительно низкой формирователя 5 бит описания. Второй помехоустойчивости, что обуславливход счетчика-накопителя 2 вместе со в ается наличием в сигнале бит адреса. входом 6 управления подключен к доЦель изобретения - повышение полнительному яыходу кодера 3, выход помехоустойчивости при передаче счетчика-накопителя 2 подан на вход факсимильных сигналов. I Указанная цель достигается тем, 35 формирователя 7 данных о числе кодовых бит, а выход блока 6 управлечто в устройство статистического ния - на вход запоминающего блока 8. кодирования и декодирования факси- ' Выходы формирователя 7 данных, засильных сигналов,содержащее на перепоминающего блока 8, формирователя 4 дающей стороне входной делитель, выход которого соединен с входом 40 разделительных бит и формирователя 5 бит описания подсоединены к соответкодера видеосигнала и через формиствующимвходам сумматора 9, выход рователь разделительных бит и форкоторого через первый буферный блок МИРОЬ-ІІЄЛЬ бит описания с двумя 10 подай в канал связи. На приемной входами сумматора, выход которого - . подключен к входу первого буферного 45 стороне устройство содержит последовательно соединенные второй буферный блока, а на приемной стороне после„блок 11, дешифратор 12 раз делитель * довательно соединенные второй буферных бит, распределитель 13 и деконий блок, дешифратор разделительных дер 14 видеосигн ала. Между вторым бит, распределитель и декодер видеосигнала^ первый выход которого сп выходом распределиттеля 13 и вторым входом декодера 14 введены послеявляется выходом устройства, а второй довательно соединенные приемник 15 выход соединен J управляющим входом данных о числе кодовых бит и злемєні второго буферного блока, введены на 16 сравнения, второй вход которого передающей стороне последовательно подключен ко второму выходу декосоединенные счетчик-нокопитель и Формирователь данных о числе кодовых 55 дера 14 и к управляющему входу второго буферного блока 11. Сит, включенные между выходом входного делителя и первым дополнительУстройство работает следующим ном рходом сумматора, и по'аледОваобразом. телььс соединенные блок управления Входной сигнал во входном делии запоминающий блок, включенные 60 теле 1 делится на строки и на интермежду выходом кодера видеосигнала валы кодирования. В~начале строки а вгорым дополнительным входом сумразвертки после разделительных бит, матора, причем выход кодера соедисформированных формирователем 4, нен с вторым входом счетчика-накопередаются биты описания строки по пителя, а дополнительный выхед кеде- '5 интервалам кодирования. Эти биты , зо 1040623 образуются в формирователе 5. В интервалах, содержащих информацию, эта информация кодируется кодером 3 и записывается Б запоминающий блок 8 с помощью блока 6 управления. Одновременно подсчитывается счетчикомнакопителем 2 число кодовых бит на данном интервале. Полученные числа кодируются в формирователе 7. Далее все полученные биты объединяются сумматором 9, уплотняются во времени первым буферным блоком 1Q и передаются по каналу связи на приемную сторону. На приемной стороне во втором буферном блоке 11 под действием поступающих запросов от декодера 14 происходит разуплотнение кодовых бит. Дешифратор 12 выделяет разделительные биты, после которых распределитель 13 подает в приемник данных 15 закодированные числа кодовых бит по интервалам кодирования. После получения этих данных распределитель 13 переключает поток бит на декодер 14, который начинает декодирование. По мере декодирования декодер 14 запрашивает новые биты из второго буферного блока 11. Число запрошенных бит сравнивается элементом 16 сравнения с числом, полученным от приемника данных 15. Когда сравниваемые числа совпадут, элемент 16 сравнений, независимо от результата декодирования, дает команду декодеру 14 перейти к декодированию следующего содержащего информацию интервала. На фиг. 2 изображен формирователь данных о числе кодовых бит интервалов. Формирователь данных содержит регистр 17 числа, вычитатель 18 и кодер 19 числа; на фиг. 3 приемник данных 15 о числе кодовых бит, который содержит декодер 20 числа, регистр 21 числа, и блок 22 сложения. Формирователь. 7 данных работает следующим образом. В конце интервала кодирования счетчик-накопитель 2 выдает число кодовых бит в прошедшем интервале. Это чиспо подается на вход вычитателя 18 и регистра 17, в котором хранится предыдущее число. Затем вновь поступившеє число и число, поступившеє из регистра 17, вычитаются одно из другого, а полученная і а выходе вычитагеля 18 разность с Г учетом знака кодируется кодером 19 и подается на сумматор 9 для включения в общий поток бит. На приемной стороне (фи г. 3 ) по-лученная разность декодируется декодером 20 и поступает на вход блока 10 22 сложения, на втором входе которого находится предыдущий результат сложения. Блок 22 сложения производит суммирование двух чисел с учетом знака и выдает результат на элемент 16 сравнения. Одновременно І5 полученный результат запоминается регистром 21 для последующего суммирования . На фиг. 4 представлен пример реализации блока 6 управления запоми20 нающего блока 8 для случая применения неравномерного кода МКХ. В качестве запоминающих элементов могут быть применены адресные регистры с организацией 102 4 х 1 слов. Блок 6 25 управления содержит входные коммутаторы 23 и 24 управляющих сигналов, двоичные счетчики 25 и 26 адресов, реверсивные двоичные счетчики 27 и 28, дешифраторы 29- и 30, запоминаю30 щие элементы 31, 32 и коммутаторы 33 и 34 выходных сигналов. Подтверждением достижения; положительного эффекта служат данные машинного моделирования. Моделирование проводилось с использованием электронных 35 тест-таблиц МККТТ, которые содержат восемь различных стандартных изображений. При моделировании использовались ошибки канала связи, полученные при Цифровой передаче со скоростью 4800 бит/с при помощи модема, удовлетворяющего рекомендации V 27 МККТТ путем записи этих ошибок на реальном канале. 45 50 Таким образом, предлагаемое устройство позволяет значительно повысить помехоустойчивость для широкого класса устройств статистического кодирования, применяющих как равномерные, так и неравномерные коды, и использующие различные методы Формирования факсимильного сигнала. 1040623 7 • * T7 > Г — ^ /у - > ч. 0W.J Фог Составитель Г. Ромашов Редактор В. Вилипенко Техред М.Надь КорректорВ. Бутяга Заказ 6949/59 Тираж 677 Подписное ВНИЧПИ Государственного комитета СССР по делам изобретений и открытий 1І3035, Москва, Ж-35, Раушская наб., д. 4/5 Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

ДивитисяДодаткова інформація

Назва патенту англійськоюStatistical coding and fasimile signal decoding unit

Автори англійськоюBalkin Hennadii Fedorovych, Ноlоsnуш Valentyn Ivanovych, Zaichenko Oleksandr Hryhorovcyh

Назва патенту російськоюУстройство статистического кодирования и декодирования факсимильных сигналов

Автори російськоюБалькин Геннадий Федорович, Голосной Валентин Иванович, Зайченко Александр Григорьевич

МПК / Мітки

МПК: H04N 1/40

Мітки: декодування, пристрій, статистичного, сигналів, кодування, факсимільних

Код посилання

<a href="https://ua.patents.su/4-8392-pristrijj-statistichnogo-koduvannya-ta-dekoduvannya-faksimilnikh-signaliv.html" target="_blank" rel="follow" title="База патентів України">Пристрій статистичного кодування та декодування факсимільних сигналів</a>

Попередній патент: Стабілізований перетворювач постійної напруги

Наступний патент: Спосіб виготовлення суспензій і установка для його здійснення

Випадковий патент: Спосіб отримування консорціуму мікроорганізмів, консорціум мікроорганізмів та спосіб ліквідації нафтових забруднень