Відбивач струму

Номер патенту: 89892

Опубліковано: 12.05.2014

Автори: Діденко Михайло Володимирович, Азаров Олексій Дмитрович, Богомолов Сергій Віталійович

Формула / Реферат

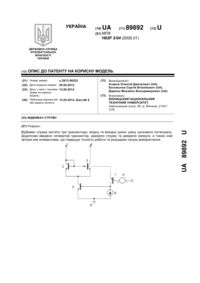

Відбивач струму, що містить три транзистори, вхідну та вихідну шини, шину нульового потенціалу, причому вхідну шину з'єднано з колектором першого транзистора, а також з базою третього транзистора, емітери першого та другого транзисторів об'єднано, бази першого та другого транзисторів об'єднано та з'єднано з колектором другого транзистора, а також з емітером третього транзистора, колектор третього транзистора з'єднано з вихідною шиною, який відрізняється тим, що у нього введено четвертий транзистор, джерело струму та джерело напруги, причому бази першого та другого транзисторів, емітер четвертого транзистора з'єднано з колектором першого транзистора та з вхідною шиною, колектор другого транзистора з'єднано з вихідною шиною, емітери першого та другого транзисторів з'єднано з колектором третього транзистора, база четвертого транзистора з'єднано з другим виводом джерела напруги, перший вивід джерела напруги з'єднано з шиною нульового потенціалу, базу третього транзистора з'єднано з колектором четвертого транзистора, а також з першим виводом джерела струму, другий вивід джерела струму з'єднано з емітером третього транзистора, а також з шиною нульового потенціалу.

Текст

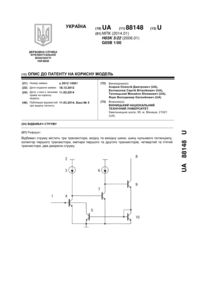

Реферат: UA 89892 U UA 89892 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до аналогової техніки і може бути використана в двотактних підсилювальних схемах. Відомо відбивач струму (U.S. Patent Devis; Patent Number 4,673,867; Appl. No.: 879,879; Data of Patent Jun. 16, 1987), який містить шину нульового потенціалу, вхідну та вихідну шини, два транзистори, два резистора та джерело струму, причому вхідну шину з'єднано з першим виводом джерела струму, другий вивід джерела струму з'єднано з колектором та базою першого транзистора, а також з базою другого транзистора, емітери першого та другого транзисторів з'єднано з першим виводом першого та другого резисторів відповідно, другі виводи першого та другого резисторів з'єднано з шиною нульового потенціалу, колектор другого транзистора з'єднано з вихідною шиною. Таким чином схема забезпечує засіб отримання опорного струму, проте недоліком є велика похибка передачі сигналу. За найближчий аналог (прототип) вибрано відбивач струму Уілсона (Wilson, G. R. (December 1968), "A Monolithic Junction FET-n-p-n Operational Amplifier", IEEE J. Solid State Circuits SC-3 (4): 341-348, doi:10.1109/JSSC.1968.1049922), який містить три транзистори, вхідну та вихідну шини, шину нульового потенціалу, причому вхідну шину з'єднано з колектором першого транзистора, а також з базою третього транзистора, емітери першого та другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, бази першого та другого транзисторів об'єднано та з'єднано з колектором другого транзистора, а також з емітером третього транзистора, колектор третього транзистора з'єднано з вихідною шиною. Недоліком найближчого аналога є низька точність роботи пристрою. В основу корисної моделі поставлено задачу створення такого відбивача струму, в якому за рахунок введення нових елементів та зв'язків між ними, за умови, що генератор вхідного сигналу має обмежений опір, підвищується точність роботи, це розширює галузь використання корисної моделі у різноманітних пристроях імпульсної та обчислювальної техніки, автоматики тощо. Поставлена задача вирішується тим, що у відбивач струму, який містить три транзистори, вхідну та вихідну шини, шину нульового потенціалу, причому вхідну шину з'єднано з колектором першого транзистора, а також з базою третього транзистора, емітери першого та другого транзисторів об'єднано, бази першого та другого транзисторів об'єднано та з'єднано з колектором другого транзистора, а також з емітером третього транзистора, колектор третього транзистора з'єднано з вихідною шиною, згідно з корисною моделлю, введено четвертий транзистор, джерело струму та джерело напруги, причому бази першого, другого транзисторів та емітер четвертого транзистора з'єднано з колектором першого транзистора та з вхідною шиною, колектор другого транзистора з'єднано з вихідною шиною, емітери першого та другого транзисторів з'єднано з колектором третього транзистора, база четвертого транзистора з'єднано з другим виводом джерела напруги, перший вивід джерела напруги з'єднано з шиною нульового потенціалу, базу третього транзистора з'єднано з колектором четвертого транзистора, а також з першим виводом джерела струму, другий вивід джерела струму з'єднано з емітером третього транзистора, а також з шиною нульового потенціалу. На кресленні представлено схему відбивача струму. Пристрій містить вхідну шину 1, яку з'єднано з базами першого 2, другого 5 транзисторів, емітером четвертого 7 транзистора та колектором першого 2 транзистора, колектор другого 5 транзистора з'єднано з вихідною шиною, емітери першого 2 та другого 5 транзисторів з'єднано з колектором третього 3 транзистора, база четвертого 7 транзистора з'єднано з другим виводом джерела напруги 9, перший вивід джерела напруги 9 з'єднано з шиною нульового потенціалу 6, базу третього 3 транзистора з'єднано з колектором четвертого 7 транзистора, а також з першим виводом джерела струму 8, другий вивід джерела струму 8 з'єднано з емітером третього 3 транзистора, а також з шиною нульового потенціалу 6. Пристрій працює таким чином. Вхідний сигнал у вигляді струму надходить на вхідну шину 1. Якщо вхідний струм втікає у схему, то збільшується емітерний струм на першому 2, четвертому 7 транзисторах і базовий струм другого 5 транзистора. При цьому другий 5 транзистор привідкривається і струм вихідної шини 4 збільшується. Збільшення емітерного струму четвертого 7 транзистора веде до збільшення колекторного струму четвертого 7 транзистора, що, у свою чергу, веде до збільшення базового струму третього 3 транзистора, при цьому він привідкривається, що призводить до врівноваження падіння напруги на першому 2 транзисторі у діодному вмиканні. Якщо вхідний струм витікає зі схеми, то зменшується емітерний струм на першому 2, четвертому 7 транзисторах і базовий струм другого 5 транзистора. При цьому другий 5 транзистор призакривається і струм вихідної шини 4 зменшується. Зменшення емітерного струму четвертого 7 транзистора веде до зменшення колекторного струму четвертого 7 1 UA 89892 U 5 10 15 транзистора, що, у свою чергу, веде до зменшення базового струму третього 3 транзистора, при цьому він призакривається, що призводить до врівноваження падіння напруги на першому 2 транзисторі у діодному вмиканні. Вихідна шина 4 відслідковує зміну струму на колекторі другого 5 транзистора. Джерело напруги 9 служить для задання базової напруги четвертого 7 транзистора. Джерело струму 8 задає робочий струм для роботи четвертого 7 та третього 3 транзисторів. Точка об'єднання третього 3 транзистора, другого вивода джерела струму 8 та першого вивода джерела напруги 9 утворюють шину нульового потенціалу 6. Джерело струму 8, четвертий 7 та третій 3 транзистори утворюють коло від'ємного зворотного зв'язку між базою другого 5 та емітером першого 2 транзисторів. Введення цього від'ємного зворотного зв'язку зменшує вхідний опір схеми, значення якого буде відповідати: 2 re , де rв х rв х - вхідний опір відбивача струму; - коефіцієнт передачі в p-n-р транзисторі; re - опір емітера першого 2 транзистора. Це призведе до збільшення точності роботи схеми. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 20 25 30 Відбивач струму, що містить три транзистори, вхідну та вихідну шини, шину нульового потенціалу, причому вхідну шину з'єднано з колектором першого транзистора, а також з базою третього транзистора, емітери першого та другого транзисторів об'єднано, бази першого та другого транзисторів об'єднано та з'єднано з колектором другого транзистора, а також з емітером третього транзистора, колектор третього транзистора з'єднано з вихідною шиною, який відрізняється тим, що у нього введено четвертий транзистор, джерело струму та джерело напруги, причому бази першого та другого транзисторів, емітер четвертого транзистора з'єднано з колектором першого транзистора та з вхідною шиною, колектор другого транзистора з'єднано з вихідною шиною, емітери першого та другого транзисторів з'єднано з колектором третього транзистора, база четвертого транзистора з'єднано з другим виводом джерела напруги, перший вивід джерела напруги з'єднано з шиною нульового потенціалу, базу третього транзистора з'єднано з колектором четвертого транзистора, а також з першим виводом джерела струму, другий вивід джерела струму з'єднано з емітером третього транзистора, а також з шиною нульового потенціалу. Комп’ютерна верстка С. Чулій Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 2

ДивитисяДодаткова інформація

Автори англійськоюAzarov Oleksii Dmytrovych

Автори російськоюАзаров Алексей Дмитриевич

МПК / Мітки

МПК: H03F 3/04

Код посилання

<a href="https://ua.patents.su/4-89892-vidbivach-strumu.html" target="_blank" rel="follow" title="База патентів України">Відбивач струму</a>

Попередній патент: Установка для стерилізації рідких середовищ

Наступний патент: Епоксидне зв’язуюче з підвищеними фізико-механічними характеристиками, модифіковане 3,3′-(1,4-фенілен)біс(2-хлоропропанонітрилом)

Випадковий патент: Бурильнозакладна машина