Матричний пристрій для піднесення в квадрат

Номер патенту: 115416

Опубліковано: 25.10.2017

Автори: Дрозд Олександр Валентинович, Антощук Світлана Григорівна, Дрозд Мирослав Олександрович, Грень Валентин Ігорович, Соколов Олександр Олександрович

Формула / Реферат

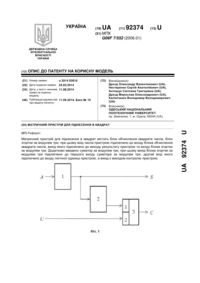

Матричний пристрій для піднесення в квадрат, що містить блок обчислення квадрата числа, при цьому n розрядів 1,…, n входу числа пристрою, де n=2X - розрядність числа, X - ціле додатне число, 2n + 1 - просте число, підключено відповідно до n розрядів 1,…, n входу блока обчислення квадрата числа, 2n розрядів 1,…, 2n виходу якого підключено відповідно до 2n розрядів 1,…, 2n виходу результату пристрою, який відрізняється тим, що введено елемент АБО та блок порівняння, при цьому n розрядів 1,…, n входу числа пристрою підключено відповідно до n входів елемента АБО, вихід якого підключено до першого виходу контролю пристрою, n молодших 1,…, n та n старших n + 1,…, 2n розрядів виходу блока обчислення квадрата числа підключено відповідно до n розрядів 1,…, n першого та n розрядів 1,…, n другого входів блока порівняння, вихід якого підключено до другого виходу контролю пристрою.

Текст

Реферат: Винахід належить до обчислювальної техніки, а саме до арифметичних цифрових пристроїв, і може бути використаний в машинобудівних технологіях. Матричний пристрій для піднесення в квадрат містить блок обчислення квадрата числа, при цьому n розрядів 1,…, n входу числа X n пристрою, де n=2 - розрядність числа, X - ціле додатне число, 2 +1 - просте число, підключено відповідно до n розрядів 1,…, n входу блока обчислення квадрата числа, 2n розрядів 1,…, 2n виходу якого підключено відповідно до 2n розрядів 1,…, 2n виходу результату пристрою згідно з винаходом введено: елемент АБО та блок порівняння, при цьому n розрядів 1,…, n входу числа пристрою підключено відповідно до n входів елемента АБО, вихід якого підключено до першого виходу контролю пристрою, n молодших 1,…,n та n старших n+1,…, 2n розрядів виходу блока обчислення квадрата числа підключено відповідно до n розрядів 1,…, n першого та n розрядів 1,…, n другого входів блока порівняння, вихід якого підключено до другого виходу контролю пристрою. Технічний результат полягає в забезпеченні виявлення відмов з переважним ігноруванням збоїв, що у збоєнечутливих пристроях підтримує високу продуктивність, а також спрощення пристрою. UA 115416 C2 (12) UA 115416 C2 UA 115416 C2 5 10 15 20 25 30 35 40 45 50 55 60 Винахід, що пропонується, належить до обчислювальної техніки, а саме до арифметичних цифрових пристроїв, і може бути використаний в машинобудівних технологіях. Відомий матричний пристрій для піднесення в квадрат, що містить блок елементів І та блок суматорів, при цьому входи розрядів числа підключено до входів блока елементів І, виходи яких підключено до входів блока суматорів, вихід якого є виходом результату пристрою [1]. Недоліки аналогу: низька достовірність результату - пристрій не виконує контроль обчислюваного результату. Найбільш близьким до запропонованого винаходу по технічній суті та результату, що досягається, є матричний пристрій для піднесення в квадрат, який містить блок обчислення квадрата числа, блок згортки за модулем три та суматор за модулем три, при цьому вхід числа пристрою підключено до входу блока обчислення квадрата числа, вихід якого підключено до виходу результату пристрою та входу блока згортки за модулем три, вихід якого підключено до першого входу суматора за модулем три, другий вхід якого підключено до входу логічної одиниці пристрою, а вихід є виходом контролю пристрою [2]. Недоліки прототипу: пристрій виявляє збої з високою ймовірністю, що заважає його роботі у складі збоєнечутливих систем, які відволікаються на обробку несуттєвих порушень із втратою продуктивності. Крім того, пристрій має великі витрати обладнання. Задача винаходу - створення матричного пристрою для піднесення в квадрат, в якому шляхом введення елемента АБО та блока порівняння забезпечено виявлення відмов з переважним ігноруванням збоїв, що у збоєнечутливих пристроях підтримує високу продуктивність, а також спрощення пристрою. Поставлена задача вирішується тим, що у матричний пристрій для піднесення в квадрат, що містить блок обчислення квадрата числа, при цьому n розрядів 1,…, n входу числа пристрою, де х n n=2 - розрядність числа, X- ціле додатне число, 2 +1 - просте число, підключено відповідно до n розрядів 1,…, n входу блока обчислення квадрата числа, 2n розрядів 1,…, 2n виходу якого підключено відповідно до 2n розрядів 1,…, 2n виходу результату пристрою, згідно з винаходом введено: елемент АБО та блок порівняння, при цьому n розрядів 1,…, n входу числа пристрою підключено відповідно до n входів елемента АБО, вихід якого підключено до першого виходу контролю пристрою, n молодших 1,…, n та n старших n+1,…,2n розрядів виходу блока обчислення квадрата числа підключено відповідно до n розрядів 1,…, n першого та n розрядів 1,…, n другого входів блока порівняння, вихід якого підключено до другого виходу контролю пристрою. Технічний ефект від запропонованого рішення полягає в тому, що шляхом введення елемента АБО та блока порівняння забезпечено виявлення відмов з переважним ігноруванням збоїв, що у збоєнечутливих пристроях підтримує високу продуктивність, а також спрощення пристрою. Переважне виявлення відмов та спрощення пристрою можна оцінити наступним чином. Розрядність n визначається у відповідності до формули Ферма з обчислення простого числа С = n х 2 +1, де n=2 , X - ціле додатне число, яка справедлива для Х= 1, 2, 3, 4, включаючи випадки n-8 і n=16, що є найбільш поширеними значеннями розрядності мікропроцесорної техніки для обслуговування широкого кола галузей з достатньою точністю. При обробці великих масивів вимірів, викривлення окремих чисел збоями не є суттєвим для остаточного результату, тобто системи обробки стають збоєнечутливими, однак чутливими до зменшення продуктивності внаслідок виявлення та обробки збоїв. Тому контроль повинен виявляти відмови та переважно ігнорувати збої. Запропоноване рішення виконує контроль за забороненими значеннями . результату, до яких належить просте (n+1)-розрядне число С і кратні йому числа: С k, де k=1,…, n n 2 -1, та за нульовим значенням результату при ненульовому операнді. Всього таких чисел 2 2n при загальній кількості 2 значень 2n-розрядного коду результату, що дозволяє оцінити ймовірність виявлення збою (як ймовірності виявлення помилки результату при виконанні -n операції за один такт) як Р3=2 . Відмова буде виявлятися з такою ймовірністю кожний такт, що Z за Z операцій, тобто Z тактів, складе ймовірність РB=1 - (1 – Р3) . Для малих значень Р3 час виявлення відмови визначається як T B=In 2 / Р3. Спрощення пристрою визначається зменшенням витрат на контроль, які у прототипі містять блок згортки за модулем три 2nрозрядного результату, що є значно складнішим у порівнянні iз введеними елементом АБО та блоком порівняння n-розрядних кодів. Суть винаходу пояснюється кресленням на фіг. 1, де зображено матричний пристрій для піднесення в квадрат, що містить блок 1 обчислення квадрата числа, елемент 2 АБО, блок 3 порівняння, n розрядів 1,…, n входу А числа пристрою, 2n розрядів 1,…,2n виходу S результату пристрою та перший Е1 і другий Е2 виходи контролю пристрою, при цьому n розрядів 1,…, n входу А пристрою підключено відповідно до n розрядів 1,…, n входу блока 1 та відповідно до n 1 UA 115416 C2 5 10 15 20 25 30 35 40 45 50 входів елемента 2, вихід якого підключено до виходу Е1 пристрою, 2n розрядів 1,…, 2n виходу блока 1 підключено відповідно до 2n розрядів 1,…, 2n виходу S пристрою, n молодших 1,…, n та n старших n+1,…, 2n розрядів виходу блока 1 підключено відповідно до n розрядів 1,…, n першого та n розрядів 1,…, n другого входів блока 3, вихід якого підключено до виходу Е2 пристрою. Пристрій працює у такий спосіб. На вхід А пристрою та відповідно на вхід блока 1 та на входи елемента 2 подається nрозрядне число а{1,…, n). Блок 1 обчислює 2n-розрядний результат - квадрат числа s{1,…, 2n} = 2 а{1,…, n} , який видається на вихід S пристрою та молодшими s{1,…,n} й старшими s{n+1,…,2n} розрядами на n розрядів 1,…, n першого та n розрядів 1,…, n другого входів блока 3, відповідно. Елемент 2 обчислює диз'юнкцію розрядів числа а {1,…, n}, яка видається на вихід Е1 пристрою у якості першого розряду коду контролю та приймає нульове й одиничне значення відповідно при а {1,…,n} =0 та a{1,…, n) 0. Блок 3 порівнює між собою коди s{1,…, n) i s{n+1,…,2n) та видає результат порівняння на вихід Е2 пристрою як другий розряд коду контролю, який приймає нульове й одиничне значення при s{1,…,n}s{n+1,…, 2n) та s{1,…, n) = s{n+1,…, 2n), відповідно. n х Розрядність n приймає значення за умови, що число С = 2 +1 є простим, де n=2 , X - ціле додатне число. Наприклад, для значень 2, 3 та 4 числа X розрядність n приймає відповідно значення 4, 8 та 16, а число С - значення 17, 257 та 65537, що є простими числами. При цьому . n числа С k, де k=1…2 -1, є забороненими, тобто не можуть бути добутками n-розрядних чисел, оскільки при розкладанні на співмножники містять просте (n+1)-розрядне число С. Двійкові коди . чисел С k, утворюють код з повторенням, тобто n молодших розрядів дорівнюють n старшим . розрядам. Тому блок 3 ідентифікує числа С k, формуючи на виході Е2 пристрою одиничне значення. Це значення формується також для нульового значення добутку. Код контролю на виходах Е1 та Е2 пристрою приймає значення 002 при нульовому значенні числа а{1,…, n} та не збіганні молодших і старших розрядів результату, тобто не нульовому, а помилковому його значенні. Код контролю приймає значення 012 при нульовому значенні числа а{1,…, n} та збіганні молодших і старших розрядів результату, що має місце при його правильному нульовому значенні. Код контролю приймає значення 102 при ненульовому значенні числа а{1,…, n} та не збіганні молодших і старших розрядів результату, тобто у відсутності його забороненого значення. Код контролю приймає значення 112 при ненульовому значенні числа а{1,…, n} та збіганні молодших і старших розрядів результату, що свідчить про його помилкове заборонене значення. Типові несправності матричного пристрою викривляють результат на вагу будь-якого одного R-1 розряду, тобто помилка має вигляд ±2 , де R - номер розряду, R=12n. Контроль виявляє 2± R-1 . помилку на заборонених значеннях результату, якщо виконується умова a{1,…, n} 2 = С k. Наприклад, для n=4 число С=17, і додатна помилка врозряді R=6 виявляється при а{1,…, . n}=6 та k=4, оскільки виконується умова, тобто 36+32=17 4 або при а{1,…, n} = 11 та k=9, оскільки 121+32=17-9, а від'ємна помилка в тому ж розряді - при а{1,…, n} = 7 та k=1, оскільки . . 49-32=17 1 або при а{1,…,n} = 10 та k=4, оскільки 100-32=17 4. Таким чином, розряди коду контролю приймають взаємно інверсні значення при обчисленні правильного результату та однакові значення при виявленні помилки, включаючи помилку на одному з виходів Е1 або Е2 пристрою при несправному контролі. Пристрій може бути використаний для побудови комп'ютерних систем зі схемами контролю, що самоперевіряються у множині константних несправностей. Джерела інформації: 1. Матричное устройство для возведения в квадрат. 1439583 СССР, МКИ G06F 7/552 / А. В. Дрозд, Е. Л. Полин, В. Н. Лацин, В. А. Соколов, В. Л. Панченко (СССР). - № 3992917/24-24; Заявлено 14.11.85; Опубл. 23.11.88, Бюл. № 43. 2. Патент на корисну модель № 92374 Україна, МПК G06F 7/552 (2006.01). Матричний пристрій піднесення в квадрат / О.В. Дрозд, С.А. Нестеренко, С.Г. Антощук, М.О. Дрозд, В.В. Калініченко. - № u 2014 03010; Заявлено 24.03.2014; Опубл. 11.08.2014, Бюл. № 15. 55 ФОРМУЛА ВИНАХОДУ 60 Матричний пристрій для піднесення в квадрат, що містить блок обчислення квадрата числа, при X цьому n розрядів 1,…, n входу числа пристрою, де n=2 - розрядність числа, X - ціле додатне n число, 2 +1 - просте число, підключено відповідно до n розрядів 1,…, n входу блока обчислення 2 UA 115416 C2 5 квадрата числа, 2n розрядів 1,…, 2n виходу якого підключено відповідно до 2n розрядів 1,…, 2n виходу результату пристрою, який відрізняється тим, що введено елемент АБО та блок порівняння, при цьому n розрядів 1,…, n входу числа пристрою підключено відповідно до n входів елемента АБО, вихід якого підключено до першого виходу контролю пристрою, n молодших 1,…, n та n старших n+1,…, 2n розрядів виходу блока обчислення квадрата числа підключено відповідно до n розрядів 1,…, n першого та n розрядів 1,…, n другого входів блока порівняння, вихід якого підключено до другого виходу контролю пристрою. Комп’ютерна верстка В. Мацело Міністерство економічного розвитку і торгівлі України, вул. М. Грушевського, 12/2, м. Київ, 01008, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 3

ДивитисяДодаткова інформація

МПК / Мітки

МПК: G06F 7/552

Мітки: піднесення, квадрат, матричний, пристрій

Код посилання

<a href="https://ua.patents.su/5-115416-matrichnijj-pristrijj-dlya-pidnesennya-v-kvadrat.html" target="_blank" rel="follow" title="База патентів України">Матричний пристрій для піднесення в квадрат</a>