Цифро-аналоговий перетворювач

Номер патенту: 115415

Опубліковано: 25.10.2017

Автори: Уткіна Тетяна Юріївна, Лукашенко Дмитро Андрійович, Лукашенко Валентина Максимівна, Лукашенко Андрій Германович, Лукашенко Володимир Андрійович

Формула / Реферат

Цифро-аналоговий перетворювач, що містить операційний підсилювач, резисторну матрицю типу R-2R, резистор оберненого зв'язку, дві шини живлення, шину загального потенціалу, шину опорної напруги, n-розрядні комірки, причому кожна n-розрядна комірка містить вхідну розрядну шину, перший захисний діод, перший та другий МДП-ключі, перший транзистор скидання, перший транзистор управління, другий захисний діод, вихід якого підключений до шини загального потенціалу, другий транзистор скидання, кожний з виходів резисторної матриці через відкритий другий МДП-ключ підключені до інвертованого входу операційного підсилювача та виходу резистора оберненого зв'язку, вхід якого підключений до виходу операційного підсилювача, вихід якого є виходом пристрою, затвор другого МДП-ключа з'єднано з відповідним стоком першого транзистора управління, а витік другого МДП-ключа з'єднано з витоком першого МДП-ключа та з відповідним виходом резисторної матриці, стік першого МДП-ключа підключений до неінвертованого входу операційного підсилювача та шини загального потенціалу, а його затвор з'єднано зі стоком другого транзистора скидання, шина опорної напруги з'єднана з входомрезисторної матриці, n-розрядні входи пристрою є цифровими входами перетворювача, генератор тактових імпульсів, фазовий селектор, чотири перетворювача рівнів напруги, шина синхронізації, дозволяючий транзистор, два МДП-варактори, другий транзистор управління, транзистор підзарядки, причому витік дозволяючого транзистора підключений до відповідного входу пристрою, затвор дозволяючого транзистора з'єднано з входом першого захисного діода та підключено до виходу відповідного перетворювача рівня напруги, стік дозволяючого транзистора підключений до затворів першого МДП-варактора, першого транзистора управління та стоку першого транзистора скидання, утворюючи вузол С1, витоки першого транзистора скидання та першого транзистора управління, а також стік та витік першого МДП-варактора підключені до виходу відповідного перетворювача рівня напруги, затвор першого транзистора скидання з'єднано з витоком другого транзистора скидання, з входом другого захисного діода та підключені до виходу відповідного перетворювача рівня напруги, стік та витік другого МДП-варактора підключені до затвора першого МДП-ключа та стоку другого транзистора управління, витік другого транзистора управління з'єднано з витоком та затвором транзистора підзарядки та підключений до вихідної шини відповідного перетворювача рівня напруги, затвори другого МДП-варактора, другого транзистора управління підключені до стоку транзистора підзарядки, вихід генератора тактових імпульсів підключений до шини синхронізації та до входу фазового селектора, виходи якого з'єднано з відповідними входами перетворювачів рівня напруги, шина загального потенціалу пристрою з'єднана з виходом другого захисного діода та підключена до відповідної шини генератора тактових імпульсів, фазового селектора, чотирьох перетворювачів рівня напруги, друга шина живлення підключена до відповідних шин живлення генератора тактових імпульсів, фазового селектора, перша шина живлення підключена до відповідних шин живлення чотирьох перетворювачів рівня напруги, загальна шина резисторної матриці з'єднана з шиною загального потенціалу, який відрізняється тим, що в кожну n-розрядну комірку додатково введені третій та четвертий транзистори скидання та шина зовнішнього управління Uупр, причому витік третього транзистора скидання підключений до вузла С2, а витік четвертого транзистора скидання підключений до вузла С1, стоки третього і четвертого транзисторів скидання підключені до шини загального потенціалу, а затвори третього і четвертого транзисторів скидання об'єднані та підключені до шини зовнішнього управління Uупр.

Текст

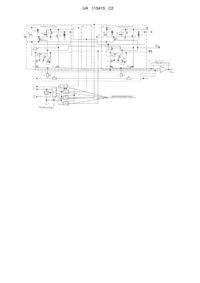

Реферат: Винахід належить до галузі обчислювальної техніки. Цифро-аналоговий перетворювач додатково додатково містить третій та четвертий транзистори скидання 30, 31 та шину зовнішнього управління Uупр, причому витік третього транзистора скидання 30 підключений до вузла С2, а витік четвертого транзистора скидання 31 підключений до вузла С 1, стоки третього і четвертого транзисторів скидання 30, 31 підключені до шини загального потенціалу 6, а затвори третього і четвертого транзисторів скидання 30, 31 об'єднані та підключені до шини зовнішнього управління Uупр. Технічним результатом, що досягається даним винаходом, є підвищення швидкодії цифро-аналогового перетворювача. UA 115415 C2 (12) UA 115415 C2 UA 115415 C2 5 10 15 20 25 30 35 40 45 50 55 60 Винахід належить до обчислювальної техніки та може бути використаний в системах управління при обробці інформації для перетворення цифрової кодової послідовності в аналоговий сигнал. Відомим є цифро-аналоговий перетворювач серії 572ПА [1], що містить операційний підсилювач, резисторну матрицю типу R-2R, резистор оберненого зв'язку, шину живлення, шину загального потенціалу, шину опорної напруги, n-розрядні комірки, причому кожна n-розрядна комірка містить вхідну розрядну шину, захисний діод, перший та другий МДП-ключі, транзистор скидання, управляючий транзистор, причому вихід захисного діода підключений до шини загального потенціалу, кожний з виходів резисторної матриці через відповідний перший МДПключ підключений до інвертованого входу операційного підсилювача та виходу резистора оберненого зв'язку, вхід якого підключений до виходу операційного підсилювача, вихід якого є виходом пристрою, затвори перших МДП-ключів з'єднано з відповідними стоками управляючих транзисторів, а кожний витік першого МДП-ключа з'єднано з витоком другого МДП-ключа та з відповідним виходом резисторної матриці, стоки других МДП-ключів підключені до неінвертованого входу операційного підсилювача, а їх затвори з'єднано з відповідним стоком транзистора скидання, витік якого підключений до шини загального потенціалу, до якої підключений неінвертований вхід операційного підсилювача, шина опорної напруги з'єднана з входом резисторної матриці; n-розрядні входи перетворювача є входами перетворювача, загальна шина резисторної матриці з'єднана з шиною загального потенціалу. Однак вказаний цифро-аналоговий перетворювач має малу швидкодію. Найбільш близьким до пропонованого по технічній суті є цифро-аналоговий перетворювач [2], який містить операційний підсилювач, резисторну матрицю типу R-2R, резистор оберненого зв'язку, дві шини живлення, шину загального потенціалу, шину опорної напруги, n-розрядні комірки, причому кожна n-розрядна комірка містить вхідну розрядну шину, перший захисний діод, перший та другий МДП-ключі, перший транзистор скидання, перший транзистор управління, другий захисний діод, вихід якого підключений до шини загального потенціалу, другий транзистор скидання, кожний з виходів резисторної матриці через відкритий другий МДПключ підключені до інвертованого входу операційного підсилювача та виходу резистора оберненого зв'язку, вхід якого підключений до виходу операційного підсилювача, вихід якого є виходом пристрою, затвор другого МДП-ключа з'єднано з відповідним стоком першого транзистора управління, а витік другого МДП-ключа з'єднано з витоком першого МДП-ключа та з відповідним виходом резисторної матриці, стік першого МДП-ключа підключений до неінвертованого входу операційного підсилювача та шини загального потенціалу, а його затвор з'єднано зі стоком другого транзистора скидання, шина опорної напруги з'єднана з входом резисторної матриці, n-розрядні входи пристрою є цифровими входами перетворювача, генератор тактових імпульсів, фазовий селектор, чотири перетворювача рівнів напруги, шина синхронізації, дозволяючий транзистор, два МДП-варактори, другий транзистор управління, транзистор підзарядки, причому витік дозволяючого транзистора підключений до відповідного входу пристрою, затвор дозволяючого транзистора з'єднано з входом першого захисного діода та підключено до виходу відповідного перетворювача рівня напруги, стік дозволяючого транзистора підключений до затворів першого МДП-варактора, першого транзистора управління та стоку першого транзистора скидання, утворюючи вузол С1, витоки першого транзистора скидання та першого транзистора управління, а також стік та витік першого МДПварактора підключені до виходу відповідного перетворювача рівня напруги, затвор першого транзистора скидання з'єднано з витоком другого транзистора скидання, з входом другого захисного діода та підключені до виходу відповідного перетворювача рівня напруги, стік та витік другого МДП-варактора підключені до затвора першого МДП-ключа та стоку другого транзистора управління, витік другого транзистора управління з'єднано з витоком та затвором транзистора підзарядки та підключений до вихідної шини відповідного перетворювача рівня напруги, затвори другого МДП-варактора, другого транзистора управління підключені до стоку транзистора підзарядки, вихід генератора тактових імпульсів підключений до шини синхронізації та до входу фазового селектора, виходи якого з'єднано з відповідними входами перетворювачів рівня напруги, шина загального потенціалу пристрою з'єднана з виходом другого захисного діода та підключена до відповідної шини генератора тактових імпульсів, фазового селектора, чотирьох перетворювачів рівня напруги, друга шина живлення підключена до відповідних шин живлення генератора тактових імпульсів, фазового селектора, перша шина живлення підключена до відповідних шин живлення чотирьох перетворювачів рівня напруги, загальна шина резисторної матриці з'єднана з шиною загального потенціалу. Недоліком цього перетворювача є низька швидкодія. Задача винаходу - підвищення швидкодії. 1 UA 115415 C2 5 10 15 20 25 30 35 40 45 50 55 Зазначена задача вирішується тим, що в основу винаходу цифро-аналогового перетворювача поставлено задачу зменшення часу на перерозподіл зарядів в перемикальних матрицях шляхом схемотехнічного рішення. Поставлена задача вирішується тим, що в кожну n-розрядну комірку додатково введені третій та четвертий транзистори скидання 30, 31 та шина зовнішнього управління U упр , причому витік третього транзистора скидання 30 підключений до вузла С 2 , а витік четвертого транзистора скидання 31 підключений до вузла С1 , стоки третього і четвертого транзисторів скидання 30, 31 підключені до шини загального потенціалу 6, а затвори третього і четвертого транзисторів скидання 30, 31 об'єднані та підключені до шини зовнішнього управління U упр . В основу винаходу поставлена задача підвищення швидкодії шляхом використання запропонованого вирішення, ознаки якого вказані в частині формули, яка відрізняється від аналога і виявляє в процесі взаємодії характерні особливості, які дають кожна окремо відомий позитивний ефект. При цьому забезпечується надпідсумковий технічний ефект, обумовлений сукупністю вказаних ознак, які полягають у тому, що паралельне з'єднання додаткового третього транзистора скидання 31 з першим транзистором скидання 13 і додаткового четвертого транзистора скидання 30 з закритим транзистором підзарядки 29 зменшує опір розряду ємностей вузлів С1 та С 2 майже до величини менше меншого. Таким чином, запропоноване рішення задовольняє критерію "суттєвої відмінності". На фіг. 1 представлений цифро-аналоговий перетворювач, що містить операційний підсилювач 1, резисторну матрицю 2 типу R-2R, резистор оберненого зв'язку 3, дві шини живлення 4, 5, шину загального потенціалу 6, шину опорної напруги 7, n-розрядні комірки 8, причому кожна n-розрядна комірка містить вхідну розрядну шину 9, перший захисний діод 10, перший та другий МДП-ключі 11, 12, перший транзистор скидання 13, перший транзистор управління 14, другий захисний діод 15, вихід якого підключений до шини загального потенціалу 6, другий транзистор скидання 16, кожний з виходів резисторної матриці 2 через відкритий другий МДП-ключ 12 підключені до інвертованого входу операційного підсилювача 1 та виходу резистора оберненого зв'язку 3, вхід якого підключений до виходу операційного підсилювача 1, вихід якого є виходом пристрою, затвор другого МДП-ключа 12 з'єднано з відповідним стоком першого транзистора управління 14, а витік другого МДП-ключа 12 з'єднано з витоком першого МДП-ключа 11 та з відповідним виходом резисторної матриці 2, стік першого МДП-ключа 11 підключений до неінвертованого входу операційного підсилювача 1 та шини загального потенціалу 6, а його затвор з'єднано зі стоком другого транзистора скидання 16, шина опорної напруги 7 з'єднана з входом резисторної матриці 2, n-розрядні входи пристрою 17 є цифровими входами перетворювача, генератор тактових імпульсів 18, фазовий селектор 19, чотири перетворювачі рівнів напруги 20, 21, 22, 23, шина синхронізації 24, дозволяючий транзистор 25, два МДП-варактори 26, 27, другий транзистор управління 28, транзистор підзарядки 29, причому витік дозволяючого транзистора 25 підключений до відповідного входу пристрою 17, затвор дозволяючого транзистора 25 з'єднано з входом першого захисного діода 10 та підключено до виходу відповідного перетворювача рівня напруги 22, стік дозволяючого транзистора 25 підключений до затворів першого МДП-варактора 26, першого транзистора управління 14 та стоку першого транзистора скидання 13, утворюючи вузол С1 , витоки першого транзистора скидання 13 та першого транзистора управління 14, а також стік та витік першого МДП-варактора 26 підключені до виходу відповідного перетворювача рівня напруги 20, затвор першого транзистора скидання 13 з'єднано з витоком другого транзистора скидання 16, з входом другого захисного діода 15 та підключені до виходу відповідного перетворювача рівня напруги 21, стік та витік другого МДП-варактора 27 підключені до затвора першого МДП-ключа 11 та стоку другого транзистора управління 28, витік другого транзистора управління 28 з'єднано з витоком та затвором транзистора підзарядки 29 та підключений до вихідної шини відповідного перетворювача рівня напруги 23, затвори другого МДП-варактора 27, другого транзистора управління 28 підключені до стоку транзистора підзарядки 29, вихід генератора тактових імпульсів 18 підключений до шини синхронізації 24 та до входу фазового селектору 19, виходи якого з'єднано з відповідними входами перетворювачів рівня напруги 20, 21, 22, 23, шина загального потенціалу 6 пристрою з'єднана з виходом другого захисного діода 15 та підключена до відповідної шини генератора тактових імпульсів 18, фазового селектора 19, чотирьох перетворювачів рівня напруги 20, 21, 22, 23, друга шина живлення 5 підключена до відповідних шин живлення генератора тактових імпульсів 18, фазового селектора 19, перша шина живлення 4 підключена до відповідних шин живлення чотирьох перетворювачів рівня 2 UA 115415 C2 напруги 20, 21, 22, 23, загальна шина резисторної матриці 2 з'єднана з шиною загального потенціалу 6, який відрізняється тим, що в кожну n-розрядну комірку додатково введені третій та четвертий транзистори скидання 30, 31 та шина зовнішнього управління U упр , причому витік третього транзистора скидання 30 підключений до вузла С 2 , а витік четвертого транзистора 5 10 15 20 25 30 35 40 45 50 скидання 31 підключений до вузла С1 , стоки третього і четвертого транзисторів скидання 30, 31 підключені до шини загального потенціалу 6, а затвори третього і четвертого транзисторів скидання 30, 31 об'єднані та підключені до шини зовнішнього управління U упр . Підвищення швидкодії цифро-аналогового перетворювача забезпечується шляхом зменшення часу розрядки ємностей С1 , С 2 . Відомо, що час розрядки ємності визначається формулою R C , (1) де C - величина ємності вузла, R - опір ланцюга розряду вузла. Швидкий розряд ємностей вузлів С1 та С 2 забезпечується високим рівнем напруги на зовнішній шині U упр . Крім того, як видно з формули (1), зменшення часу розрядки ємностей С1 та С 2 забезпечується за рахунок паралельного з'єднання опорів ланцюга розрядки. Тому що при паралельному з'єднанні опорів загальний опір має величину менше меншого R j Ri R ij . (2) R j Ri Працює пристрій наступним чином. Перед початком перетворення здійснюють обнуління ємнісних вузлів С1 та С 2 завдяки імпульсу, що надходить з шини зовнішнього управління U упр з амплітудою напруги високого рівня. При цьому перший транзистор скидання 13 також сприяє розряду вузла С1 при надходженні імпульсу амплітуди високого рівня з виходу перетворювача рівня напруги 21. Синхронізація роботи в часі здійснюється аналогічно прототипу за допомогою імпульсів, які формуються генератором тактових імпульсів 18 та фазовим селектором 19, а високий рівень амплітуди забезпечується перетворювачами рівня напруги 20, 21, 22, 23. Розряд ємності вузлів витоків першого і другого МДП-ключів 11, 12 забезпечується наступним чином, через транзистор підзарядки 29 імпульс високого рівня з виходу перетворювача рівня напруги 23, підзаряджає ємність С 2 , яка сформована затворами ємності другого МДП-варактора 27 та другого транзистора управління 28. При надходженні імпульсу напруги високого рівня через другий транзистор управління 28 відбувається стрибок напруги на затворі першого МДП-ключа 11, відкриває його і через відкритий перший МДП-ключ 11 ємність витоків розряджається до потенціалу загальної шини 6. При надходженні з виходу перетворювача високого рівня 22 напруги на затвор дозволяючого транзистора 25, відкриває його і цифрова інформація з входів пристрою 17 проходить через дозволяючий транзистор 25 та підзаряджає ємність С1 . З надходженням імпульсу з виходу перетворювача високого рівня напруги 20 на відповідні входи першого МДПварактора 26 у вузлі С1 відбувається стрибок, який відкриває перший транзистор управління 14, при цьому імпульс високої напруги з виходу перетворювача рівня напруги 20 надходить на затвор другого МДП-ключа 12, відкриває його і підключає відповідний опір 2R на виході якого з'являється відповідне значення опорної напруги 7, яке надходить до інвертованого входу операційного підсилювача 1. Аналогові величини інформації, що надходять з виходів резисторної матриці 2 типу R 2R під дією цифрових одиниць 17, які знаходяться на відповідних входах перетворювача, за допомогою n-розрядних комірок 8 проходять через другі МДП-ключі 12 і надходять на інвертований вхід операційного підсилювача 1, на виході якого з'являється результат перетворення цифрового коду у відповідне значення аналогової величини. Порівняльний аналіз роботи цифро-аналогового перетворювача [2] (прототип, варіант 2) показав, що в процесі роботи перемикальних матриць багато часу витрачається на розряд ємностей у вузлах С1 та С 2 . Це пояснюється великим значенням опору ланцюга розрядки ємностей. Припустимо C1прот С1запр С , а C2прот С2запр С , тоді для зменшення опору ланцюга розрядки, в запропонованому цифро-аналоговому перетворювачі при паралельному з'єднанні опорів, загальний опір ланцюга розрядки в вузлі С1 має вигляд 3 UA 115415 C2 5 R13 R 31 R13 , (3) R13 R 31 де R13 - опір відкритого ключа транзистора 13 для розрядки ємності вузла С1 в прототипі; R31 - додатковий опір відкритого ключа транзистора скидання 31 для розрядки ємності вузла С1 . З формули (3) видно, що загальний опір менше опору відкритого ключа, тому час розрядки ємності вузла С1 зменшується. Нехай R13 R31 5 10 2 , тоді загальний опір ланцюга розрядки ємності С1 дорівнює R 13 , 2 тобто загальний опір зменшується в 2 рази. Отже, час розряду вузла С1 зменшується в 2 рази. прот 2 рази . запр У прототипі розряд ємності C 2прот здійснюється завдяки струму витоку. Нехай RС - опір R ij 10 2 розрядки ємності вузла С 2 (опір розрядки визначається в прототипі як R 5 1010 Ом); 15 R 30 5 10 2 - додатковий опір відкритого ключа транзистора скидання 30 для розрядки ємності вузла С2 . Використовуючи формулу (2), загальний опір вузла С2 матиме вигляд R 30 R С2 20 R С2 , (4) R 30 R С2 тому що R30 значно менше ніж RС , і, як наслідок, швидкодія при перерозподілі зарядів 2 збільшується. Дійсно, опір струму витоку вузла С 2 дорівнює R ij 5 10 10 Ом, а опір відкритого ключа транзистора скидання 30 дорівнює R 30 5 10 2 , тоді результат співвідношення (4) дорівнює прот 25 30 5 1010 C 1 10 8 рази . запр 5 10 2 C Отже, час розряду прот ємності С зменшується, що приводить до збільшення швидкодії розряду вузла С 2 запропонованої перемикальної матриці майже на 8 порядків. Крім того, високий рівень напруги, що надходить на затвори додатково введених транзисторів скидання 30, 31, зменшує опір відкритого ключа, що сприяє прискоренню процесу перезарядки ємностей. Отже, швидкий розряд ємностей вузлів С1 та С 2 забезпечується високим рівнем напруги на зовнішній шині U упр та зменшенням опору ланцюгів розрядки відповідних ємностей в кожній n розрядній комірці управління МДП-ключами. Завдяки сукупності зазначених ознак підвищується швидкодія пристрою, що дозволяє досягти позитивного ефекту при його експлуатації. Таким чином, задача винаходу підвищення швидкодії цифро-аналогового перетворювача вирішена за рахунок схемотехнічного рішення. 35 40 Джерела інформації: 1. Алексеенко А.Г. Применение прецизионных аналоговых микросхем / А.Г. Алексеенко и др. - М.: Радио и связь, 1985. 2. Пат. 24660 А Україна, МПК Н03М 1/12, G06G 7/26, G06J 3/00. Цифро-аналоговий перетворювач / В.М. Лукашенко, В.I. Биков, А.Г. Лукашенко; заявник та власник В.М. Лукашенко. - № а97062949; заявл. 20.06.1997; опубл. 04.08.1998, Бюл. № 5. 4 UA 115415 C2 ФОРМУЛА ВИНАХОДУ 5 10 15 20 25 30 35 40 45 Цифро-аналоговий перетворювач, що містить операційний підсилювач, резисторну матрицю типу R-2R, резистор оберненого зв'язку, дві шини живлення, шину загального потенціалу, шину опорної напруги, n-розрядні комірки, причому кожна n-розрядна комірка містить вхідну розрядну шину, перший захисний діод, перший та другий МДП-ключі, перший транзистор скидання, перший транзистор управління, другий захисний діод, вихід якого підключений до шини загального потенціалу, другий транзистор скидання, кожний з виходів резисторної матриці через відкритий другий МДП-ключ підключені до інвертованого входу операційного підсилювача та виходу резистора оберненого зв'язку, вхід якого підключений до виходу операційного підсилювача, вихід якого є виходом пристрою, затвор другого МДП-ключа з'єднано з відповідним стоком першого транзистора управління, а витік другого МДП-ключа з'єднано з витоком першого МДП-ключа та з відповідним виходом резисторної матриці, стік першого МДПключа підключений до неінвертованого входу операційного підсилювача та шини загального потенціалу, а його затвор з'єднано зі стоком другого транзистора скидання, шина опорної напруги з'єднана з входом резисторної матриці, n-розрядні входи пристрою є цифровими входами перетворювача, генератор тактових імпульсів, фазовий селектор, чотири перетворювача рівнів напруги, шина синхронізації, дозволяючий транзистор, два МДПварактори, другий транзистор управління, транзистор підзарядки, причому витік дозволяючого транзистора підключений до відповідного входу пристрою, затвор дозволяючого транзистора з'єднано з входом першого захисного діода та підключено до виходу відповідного перетворювача рівня напруги, стік дозволяючого транзистора підключений до затворів першого МДП-варактора, першого транзистора управління та стоку першого транзистора скидання, утворюючи вузол С1, витоки першого транзистора скидання та першого транзистора управління, а також стік та витік першого МДП-варактора підключені до виходу відповідного перетворювача рівня напруги, затвор першого транзистора скидання з'єднано з витоком другого транзистора скидання, з входом другого захисного діода та підключені до виходу відповідного перетворювача рівня напруги, стік та витік другого МДП-варактора підключені до затвора першого МДП-ключа та стоку другого транзистора управління, витік другого транзистора управління з'єднано з витоком та затвором транзистора підзарядки та підключений до вихідної шини відповідного перетворювача рівня напруги, затвори другого МДП-варактора, другого транзистора управління підключені до стоку транзистора підзарядки, вихід генератора тактових імпульсів підключений до шини синхронізації та до входу фазового селектора, виходи якого з'єднано з відповідними входами перетворювачів рівня напруги, шина загального потенціалу пристрою з'єднана з виходом другого захисного діода та підключена до відповідної шини генератора тактових імпульсів, фазового селектора, чотирьох перетворювачів рівня напруги, друга шина живлення підключена до відповідних шин живлення генератора тактових імпульсів, фазового селектора, перша шина живлення підключена до відповідних шин живлення чотирьох перетворювачів рівня напруги, загальна шина резисторної матриці з'єднана з шиною загального потенціалу, який відрізняється тим, що в кожну n-розрядну комірку додатково введені третій та четвертий транзистори скидання та шина зовнішнього управління Uупр, причому витік третього транзистора скидання підключений до вузла С2, а витік четвертого транзистора скидання підключений до вузла С1, стоки третього і четвертого транзисторів скидання підключені до шини загального потенціалу, а затвори третього і четвертого транзисторів скидання об'єднані та підключені до шини зовнішнього управління Uупр. 5 UA 115415 C2 Комп’ютерна верстка А. Крулевський Міністерство економічного розвитку і торгівлі України, вул. М. Грушевського, 12/2, м. Київ, 01008, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 6

ДивитисяДодаткова інформація

МПК / Мітки

Мітки: перетворювач, цифро-аналоговий

Код посилання

<a href="https://ua.patents.su/8-115415-cifro-analogovijj-peretvoryuvach.html" target="_blank" rel="follow" title="База патентів України">Цифро-аналоговий перетворювач</a>

Попередній патент: Регульований механізм приводу ноги крокуючих машин

Наступний патент: Матричний пристрій для піднесення в квадрат

Випадковий патент: Спосіб прокатки заготівки