Пристрій сполучення еом

Формула / Реферат

Устройство сопряжения электронной вычислительной машины, содержащее элементы приема и передачи информации, регистры адреса, тактовый гeнератор, отличающееся тем, что введены четыре регистра, два узла укорочения длительности импульса, три делителя числа импульсов, один RS- и два Dt-триггера, элементы И-НЕ, два элемента НЕ, элемент И, узел начального сброса, выход тактового генератора соединен с первым входом элемента И, выход которого соединен с тактовым входом первого делителя числа импульсов, выход первого делителя числа импульсов соединен с тактовым входом второго делителя числа импульсов, выход которого соединен с тактовым входом третьего делителя числа импульсов, выход третьего делителя числа импульсов соединен с первым входом элемента ИЛИ-НЕ, выходом соединенного с входами установки в ноль первого, второго регистров адреса, с первого по четвертый регистров и первого, второго Dt - триггеров, выход второго делителя числа импульсов соединен с тактовым входом четвертого регистра и с С-входом второго Dt-триггера, выход распределителя импульсов соединен с первыми входами со второго по пятый элементов И-НЕ, выход элемента приема соединен со входом первого узла укорочения длительности импульсов, с D-входом первого Dt-триггера, выход которого соединен с DR-входом первого регистра, выходы которого соединены с внутренней шиной устройства, которая соединена со входами данных всех разрядов первого и второго регистров адреса и второго и третьего регистров, выходы первого и второго регистров адреса и четыре младших разрядов третьего регистра адреса соединены с внешней шиной адреса устройства, выходы второго и входы данных четвертого регистров соединены с внешней шиной данных устройства, выходы старшие разрядов третьего регистра соединены со вторыми входами элементов И-НЕ, со второго по пятый, выходы которых соединены с шиной управляющих сигналов устройства, выход первого узла укорочения длительности импульса подсоединен к входу S RS-триггера, к входу установки в первоначальное состояние распределителя импульсов, тактовый вход распределителя импульсов соединен с выходом второго делителя числа импульсов, выходы распределителя импульсов соединены с тактовыми входами первого, второго регистров адреса и второго, третьего регистров, единичный выход RS-триггера соединен с входом второго узла укорочения длительности импульса и входом элемента задержки, выход которого соединен со вторым входом элемента И, выход второго узла укорочения длительности импульса соединен с первым входом первого элемента Й-НЕ, выходом соединенного с входами установки в ноль с первого по третий делителей числа импульсов и вторым входом элемента ИЛИ-НЕ, выход узла начального сброса соединен со вторым входом первого элемента И-НЕ, выход старшего разряда четвертого регистра соединен со входом D второго Dt-триггера, выход которого соединен с входом элемента передачи информации, выход которого соединен с последовательным выходом устройства, вход элемента приема соединен с последовательным входом устройства, выход третьего элемента И-НЕ соединен с входом установки в "1" второго Dt-триггера и через первый элемент НЕ - со входом разрешения приема параллельного кода четвертого регистра, выход седьмого разряда третьего регистра соединен через второй элемент НЕ с входом разрешения выдачи кода второго регистра.

Текст

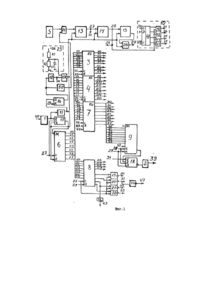

Изобретение относится к области вычислительной техники и может быть использовано для подключения периферийных устройств с возможностью приема и передачи параллельного кода к электронным цифровым машинам, имеющим последовательный выход и последовательный вход как выходной интерфейс стык С2 (PS-232). Причем оба устройства периферийное устройство и ЭВМ могут быть расположены на больших расстояниях друг от др уга. Наиболее близким к изобретению является устройство сопряжения, представляющее собой систему передачи данных [2]. Устройство содержит: ЭВМ, устройство управления, терминальные устройства, причем устройство управления содержит регистр команд, блок управления с использованием команд записи после считывания, блок записи, блок считывания, регистр адресации памяти, счетчик байтов. Блок управления инициирует блок записи команды, коды поступают в регистр команды и блок, когда блок выдает сигналы о завершении пересылки записываемых данных. Блок записи обеспечивает считывание отдельных массивов данных, хранящихся в памяти ЭВМ по содержимому регистра адреса и пересылки этих массивов в терминальные устройства, причем каждой операции соответствует увеличение на единицу содержимого регистра и уменьшение на единицу счетчика байтов. Недостатком данного устройства является большая сложность, для реализации его работы необходима обязательно ЭВМ, недостаточное быстродействие, отсутствие автоматизации процесса передачи информации. В основу изобретения поставлена задача создать устройство сопряжения ЭВМ, имеющих последовательный выходи последовательный вход как интерфейс стык С2, с ЭВМ или устройствами, имеющими параллельный вход и выход как интерфейс типа И41, причем количество этих устройств может быть более одного. Поставленная задача решена тем, что в устройство сопряжения электронной вычислительной машины, содержащее элементы приема и передачи информации, регистры адреса, тактовый генератор, согласно изобретению введены четыре регистра, распределитель импульсов, два узла укорочения длительности импульса, три делителя числа импульсов, один RS- и два Dt-триггера, элементы И-НЕ, два элемента НЕ, элемент И, узел начального сброса, выход тактового генератора соединен с первым входом элемента И, выход которого соединен с тактовым входом первого делителя числа импульсов, выход первого делителя числа импульсов соединен с тактовым входом второго делителя числа импульсов, вы ход которого соединен с тактовым входом третьего делителя числа импульсов, выход третьего делителя числа импульсов соединен с первым входом элемента ИЛИ-НЕ, выходом соединенного с входами установки в ноль первого, второго регистров адреса, с первого по четвертый регистров и первого, второго Dt-триггеров, выход второго делителя числа импульсов соединен с тактовым входом четвертого регистра с С-входом второго Dt-триггера, выход распределителя импульсов соединен с первыми входами со второго по пятый элементов И-НЕ, выход элемента приема соединен с входом первого узла укорочения длительности импульсов, с D-входом первого Dt-триггера, выход которого соединен с DR входом первого регистра, выходы которого соединены с внутренней шиной устройства, которая соединена с входами данных всех разрядов первого и второго регистров адреса и второго и третьего регистров, выходы первого и второго регистров адреса и четыре младших разрядов третьего регистра соединены с внешней шиной адреса устройства, выходы второго и входы данных четвертого регистров соединены с внешней шиной данных устройства, выходы старши х разрядов третьего регистра соединены со вторыми входами элементов И-НЕ, со второго по пятый, выходы которых соединены с шиной управляющих сигналов устройства, выход первого узла укорочения длительности импульса подсоединен к входу S PS-триггера, к входу установки в первоначальное состояние распределителя импульсов, тактовый вход распределителя импульсов соединен с выходом второго делителя числа импульсов, выходы распределителя импульсов соединены с тактовыми входами первого, второго регистров адреса и второго, третьего регистров, единичный выход RS-триггера соединен с входом второго узла укорочения длительности импульса и входом элемента задержки, выход которого соединен со вторым входом элемента И, выход второго узла укорочения длительности импульса соединен с первым входом первого элемента И-НЕ, выходом соединенного с входами установки в 0 с первого по третий делителей числа импульсов и вторым входом элемента ИЛИ-НЕ, выход узла начального сброса соединен со вторым входом первого элемента И-НЕ, выход старшего разряда четвертого регистра соединен со входом D второго D tтриггера, вы ход которого соединен с входом элемента передачи информации, выход которого соединен с последовательным выходом устройства, вход элемента приема соединен с последовательным входом устройства, вы ход третьего элемента Й-НЕ соединен с входом установки в "1" второго D триггера и через первый элемент НЕ с входом разрешения приема параллельного кода четвертого регистра, выход седьмого разряда третьего регистра соединен через второй элемент НЕ с входом разрешения выдачи кода второго регистра. С помощью узла укорочения длительности импульса по переднему фронту импульса, поступающего по последовательному входу устройства, устанавливается триггер, который разрешает счет импульсов делителями числа импульсов, один из выходов которых синхронизирует прием и выдачу последовательной информации, а другой поступает на распределитель импульсов, который разрешает прием и выдачу в различные регистры для формирования принимаемого и выдаваемого кода и управляющих сигналов. Таким образом, нововведенные признаки позволяют передавать информацию в периферийные устройства и принимать информацию в периферийные устройства только по последовательным входам и выходу хотя периферийные устройства содержат параллельные регистры. На фиг. 1 изображена блок-схема устройства; на фиг. 2 - временная диаграмма. Устройство сопряжения содержит элемент приема 1 и элемент передачи информации 2, регистры адреса 3, 4, тактовый генератор 5, регистры 6, 7, 8, 9, второй из которых 7 с возможностью перевода выходов разрядов в третье состояние, распределитель импульсов 10, два узла укорочения длительности импульса (СУДИ) 11, 12, делители числа импульсов 13, 14, 15, RS-триггер 16, Dt - триггеры 17, 19, элементы И-НЕ 19 23, элемент И 24, для выработки управляющих сигналов, узел начального сброса (УНС)25, элемент ИЛИ-НЕ 26, линии связей 27-40, регистр 41, элементы И 42-45, элементы НЕ 46, 48, линия 49 перевода в Z-coстояние регистра 7, элемент 50 задержки. Выход тактового генератора 5 соединен через элемент И 24 с входом первого делителя числа импульсов 13, выход 27 первого делителя 13 соединен с входом второго делителя числа импульсов 14, выход 28 которого соединен с входом третьего делителя числа импульсов 15, выход третьего делителя 15 соединен через элемент ИЛИ-НЕ 26 с входом 29 установки в ноль всех регистров и первого и второго Dt-триггеров, выход 28 второго делителя 14 соединен с тактовым входом четвертого регистра 9 с С-входом, второго Dt триггера 18, выход элемента приема 1 соединен с входом первого узла СУДИ 11, с входом D первого Dt триггера 17, выход которого соединен с ДР входом первого (сдвигового) регистра 6, выходы которого соединены с внутренней шиной устройства, которая соединена с входами всех разрядов регистров 3, 4, 7, 8, выходы регистров адреса 3, 4 и четыре младших разряда третьего регистра 8 поступают на шины адреса интерфейса И 41 периферийного устройства, выходы второго 7 и входы четвертого 9 регистров поступают на шины данных интерфейса И 41 периферийного устройства. Выходы старших разрядов третьего регистра 8 поступают через элементы И-НЕ 19-23 на шины 30-33 управляющих сигналов. Выход 34 первого СУДИ 11 подсоединен к S входу RS-триггера 16. Тактовый вход РИ 10 соединен с выходом 28 второго делителя 14. Выходы 35-38 распределителя импульсов 10 соединены с тактовыми входами регистров 3, 4, 7, 8. Единичный выход RS триггера 16 соединен с входом второй схемы СУДИ 12 и входом элемента задержки 50, выход которого соединен со вторым входом схемы И 24, выход второй схемы СУДИ 12 соединен с входом установки в О РИ 10 и через элемент И-НЕ 23 с входами установки в 0 делителей импульсов 13-15 и вторым входом элемента ИЛИ-НЕ 26, выход устройства начального сброса 25 соединен со входом первого элемента И-НЕ 23. Выход старшего разряда четвертого регистра 9 соединен со входом D второго Dt триггера 18, вход которого соединен со входом элемента передачи информации 2, вы : ход которого соединен с выходом 39 устройства .сопряжения. Вход 40 элемента приема 1 соединен с входом устройства сопряжения. Выход 31 третьего элемента И-НЕ 20 соединен с входом установки в 1, второго Dt-триггера 18 и через первый элемент НЕ 46 с входом 47 разрешения приема параллельного кода в четвертый регистр 9. Выход седьмого регистра 8 соединен через второй элемент НЕ 48 с входом 49 разрешения выдачи кода второго регистра 7. Рассмотрим возможную те хническую реализацию рассматриваемого устройства. В качестве элемента приема 1 применяется элемент 170 АП 2, цель которого принять сигнал с линии (может быть использован также оптрон и усилитель). В качестве элемента передачи 2 использован элемент 170 УП2, цель которого передать без искажения информацию (может также быть использован усилитель с оптроном). Регистры адреса 3-4 могут быть выполнены на элементах 133 ИР 13. Тактовый генератор может быть собран на элементе 133 Л Η 15 и дополнительном кварцевом резонаторе. Распределитель импульсов 10 может содержать регистры 133 ИР 13 и схемы И133ЛИ1. Узлы укорочения длительности импульсов 11, 12 могут быть выполнены на элементах 133ЛАЗ с использованием на каждую схему резистора порядка 300 Ом и конденсатора порядка 2200 пФ. В качестве RS триггера 16 и Dt триггеров 177 и 18 использованы элементы 133ТМ2. В качестве элемента задержки 50 использована Гобразная RS-цепь из резистора 300 Ом и конденсатора 3900 пФ. В качестве элемента ИЛИ-НЕ 26 использован элемент 133ЛЛ1. Устройство работает следующим образом. При включении питающего напряжения, см. фиг, 1 и фи г. 2, на вход элемента И-НЕ 23 поступает с УН С 25 низкий потенциал, который вызывает на выходе элемента И-НЕ 23 высокий потенциал, который придя на вход элемента ИЛ И-НЕ 26 вызывает на его выходе 29 низкий потенциал. Высокий потенциал на выходе элемента И-НЕ 23 и низкий потенциал на выходе ИЛ И-НЕ 26 устанавливают делители 13-15, триггер 16 и все регистры 3,4, 6-9 и первый D-триггер 17 в нулевое состояние. В момент ТО при приходе на вход 40 устройства первого стартового импульса срабатывает узел СУДИ 11 на выходе второго появляется узкий отрицательный импульс, который устанавливает триггер 16 в единичное состояние. Высокий потенциал с единичного плеча триггера 16 поступает на вход СУДИ 12 и вход элемента задержки 50. На выходе СУДИ 12 появляется узкий отрицательный импульс, который устанавливает РИ 10 в первоначальное состояние и вызывает на выходе элемента И-НЕ 23 узкий положительный импульс, длительностью 0,2-0,4 мкс. Последний еще раз устанавливает в 0 все регистры, триггеры и делители числа импульсов устройства. Высокий потенциал с выхода триггера 16 пройдя через элемент задержки 50 (время задержки около 1 мкс) разрешает прохождение импульсов через элемент И 24. Делитель 13 начинает считать импульсы. После появления на его выходе импульса в момент Т1 он поступает на входы триггера 17 и регистра 6 и по переднему фронту импульса в триггер 17 запоминается первый разряд принимаемого кода (прием стартового бита). Затем в момент Т2 появляется второй положительный импульс на выходе делителя 13. По переднему фронту этого импульса происходит прием следующего бита (первый информационный бит) в триггер 17 и переписи информации, которая до этого была в триггере 17 в младший разряд регистра 6. Таким образом при появлении каждого следующего импульса на выходе делителя 13 следующий бит информации запоминается в триггере 17, а предыдущая переписывается в регистр 6 и сдвигается в нем на 1 разряд от младших разрядов к старшим. При появлении 10-го импульса на выходе делителя 13 в регистр 6 будут находится 8 бит информации (предположим, что использован для передачи по интерфейсу стык С2 асинхронный режим работы с длиной слова 8 бит без контроля на четность-нечетность). Предположим, что необходимо записать код 89 Η (буква Η указывает, что код шестнадцатиричный) в ячейку памяти периферийного устройства по адресу 0105Н. В этом случае в момент ТЮ в регистре 6 будет находится код 05 Н. После окончания десятого импульса на выходе делителя 13 момент Τ 11 появляется первый положительный импульс на выходе 28 делителя 14, который поступает на вход распределителя импульсов 10 и на его выходе 35 появляется положительный импульс, который разрешает прием кода 05Н с выхода регистра 6 в регистр 3. Затем в следующие моменты времени с ТІ2 поТ21 включительно запоминается последовательный код 01 Η, приходящий на вход 40 в регистр 6, а после окончания двадцатого импульса на выходе делителя 13 момент Т22 появляется второй положительный импульс на выходе делителя 14, который поступает на вход распределителя 10 и на его выходе 36 появляется положительный импульс, который разрешает прием кода 01Η с выхода регистра 6 в регистр 4. Затем аналогично в момент времени с Т23 по Т32 напоминается последовательный код 89Н, приходящий на вход 40 в регистр 5, а после окончания тридцатого импульса на выходе делителя 13 момент ТЗЗ появляется третий положительный импульс на выходе делителя 14, который поступает на вход РИ 10 и на его выходе 37 появляется положительный импульс, который разрешает прием кода 89 Η с выхода регистра 6 в регистр 7. Затем аналогично в моменты времени с Т34 поТ43 запоминается последовательный код 40 Н, приходящий на вход 40 в регистр 6. В четвертом байте передаются старшие разряды адреса и сигналы управления. После окончания сорокового импульса на выходе делителя 13 момент Т44 появляется четвертый положительный импульс на выходе делителя 14, который поступает на вход РИ 10 и на его вы ходе 38 появляется положительный импульс, который разрешает прием кода 40Н с выхода регистра 6 в регистр 8, а также выдачи через элемент 21 управляющего сигнала записи. Таким образом, в момент Т44 на шину 32 будет выдан сигнал записи и данные 89Н будут записаны по адресу 0010 Н, периферийного устройства. В это время выходной сигнал поступающий с выхода элемента 48 на вход 49 элемента 7 переводит выходы регистра 7 с третьего состояния в активное. Если необходимо прочесть информацию, то в моменты времени с Т34 по Т43 на вход 40 подается код 20, который запоминается в регистре 6, После окончания сорокового импульса на выходе делителя 13 в момент Т4 на выходе 38 распределителя 10 появляется положительный импульс, который разрешает прием кода 2QH с регистра 6 в регистр 8 и на выходе 31.элемента 20 появляется сигнал чтения, который поступает на периферийное устройство и оно выставляет на шину данных данные. Кроме того, сигнал с выхода 31 элемента 20 поступает на вход S триггера 18 и устанавливая его в 1, а также через первый элемент НЕ 46 поступает на управляющий вход S1 (47) регистра 9, разрешая прием параллельного кода в регистр 9 по тактовому сигналу на шине С (28) этого регистра.

ДивитисяДодаткова інформація

Назва патенту англійськоюDevices for electronic computer connexion

Автори англійськоюFoida Albert Mykytovych

Назва патенту російськоюУстройство соединения эвм

Автори російськоюФойда Альберт Никитович

МПК / Мітки

МПК: G06F 13/12

Мітки: сполучення, пристрій, еом

Код посилання

<a href="https://ua.patents.su/5-18733-pristrijj-spoluchennya-eom.html" target="_blank" rel="follow" title="База патентів України">Пристрій сполучення еом</a>

Попередній патент: Пристрій для комутації електиричного кола

Наступний патент: Шихта для виготовлення термостійкого електропровідного керамічного матеріалу

Випадковий патент: Пристрій для формування оцінки мотивації учня, студента, слухача до навчання в комп'ютеризованій освітній системі