Пристрій відновлення синхронізації для синхронної цифрової ієрархічної системи передачі даних

Формула / Реферат

1. Пристрій відновлення синхронізації для синхронної цифрової ієрархічної (SDH) системи передачі даних, за допомогою якого треті сторони можуть використовувати SDH канал, що містить вхід для прийому мультиплексованого сигналу модуля синхронної передачі (STM), схему (20) відновлення синхронізації для відновлення синхронізуючого сигналу з STM сигналу, демультиплексор (21) для демультиплексування STM сигналу на множину сигналів підпорядкованих блоків (TU), процесор (25) показчика для зчитування даних показчика з TU сигналу, пристрій усунення вірівнювання бітів (28) для зчитування даних вирівнювання бітів з TU сигналу, буферний запам'ятовуючий пристрій (ЗО) з монітором (34), причому у запам'ятовуючому пристрої (ЗО) тимчасово зберігаються TU дані процесора, перш ніж вони будуть синхронізовані з відновленою частотою синхронізації, який відрізняється тим, що містить засіб фазового автопідстроювання частоти (32) для генерування сигналу відновленої синхронізації (31), причому засіб (32) включає в себе три входи підстроювання фази (ф1, ф2, ф3), які з'єднані з процесором показчика, пристроєм усунення вирівнювання бітів (28) та монітором (34) запам'ятовуючого пристрою відповідно, причому використовуються тільки зчитані дані усунення вирівнювання бітів, зформовані пристроєм усунення вирівнювання бітів (28) (на вході ф2 підстройки фази) для змінення відновлюваного синхронізуючого сигналу (23) і генерування сигналу відновленої синхронізації (31).

2. Пристрій відновлення синхронізації за п. 1, який відрізняється тим, що запам'ятовуючий пристрій (30) є "еластичним" запам'ятовуючим пристроєм, а вказані засоби (ф2, 32, 34) забезпечують перевірку умови недозаповнення чи переповнення запам'ятовуючого пристрою (30) для виконання підстроювання до сигналу відновленої синхронізації (31) так, щоб підтримати ємність запам'ятовуючого пристрою.

3. Пристрій відновлення синхронізації за будь-яким з попередніх пунктів, який відрізняється тим, що відновлений сигнал синхронізації (31) модифікується у другому режимі (ф1, ф2), використовуючи дані вирівнювання бітів (28).

4. Пристрій відновлення синхронізації за будь-яким з попередніх пунктів, який відрізняється тим, що засіб (34) використовується в іншому режимі роботи (ф3) засобу фазового автопідстроювання частоти (32) для перевірки того, що запам'ятовуючий пристрій (30) заповнено приблизно наполовину та для налагодження швидкості передачі відновленого сигналу синхронізації так, щоб підтримати умову половинного заповнення.

5. Пристрій відновлення синхронізації за будь-яким з попередніх пунктів, який відрізняється тим, що містить пристрій фазової автопідстройки частоти (32), який використовує як вхідний відновлюваний синхронізуючий сигнал (23), що видає сигнал відновленої синхронізації (31) на виході, та включає один чи більше додаткових входів (ф1, ф2, ф3) для налагодження частоти вихідного сигналу.

6. Пристрій відновлення синхронізації за будь-яким з попередніх пунктів, який відрізняється тим, що ефект використання даних покажчика обнульовується шляхом модифікації відновленого сигналу двічі з використанням даних покажчика, що мають однакову амплітуду, але протилежну полярність.

Текст

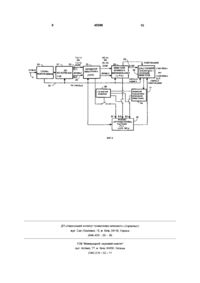

1 Пристрій відновлення синхронізації для синхронної цифрової ієрархічної (SDH) системи передачі даних, за допомогою якого треті сторони можуть використовувати SDH канал, що містить вхід для прийому мультиплексованого сигналу модуля синхронної передачі (STM), схему (20) відновлення синхронізації для відновлення синхронізуючого сигналу з STM сигналу, демультиплексор (21) для демультиплексування STM сигналу на множину сигналів підпорядкованих блоків (TU), процесор (25) показчика для зчитування даних показчика з TU сигналу, пристрій усунення вірівнювання бітів (28) для зчитування даних вирівнювання бітів з TU сигналу, буферний запам'ятовуючий пристрій (ЗО) з монітором (34), причому у запам'ятовуючому пристрої (ЗО) тимчасово зберігаються TU дані процесора, перш ніж вони будуть синхронізовані з відновленою частотою синхронізації, який відрізняється тим, що містить засіб фазового автопідстроювання частоти (32) для генерування сигналу відновленої синхронізації (31), причому засіб (32) включає в себе три входи підстроювання фази (ф1, ф2, фЗ), які з'єднані з процесором показчика, пристроєм усунення вирівнювання бітів (28) та монітором (34) запам'ятовуючого пристрою ВІДПОВІДНО, причому використовуються тільки зчитані дані усунення вирівнювання бітів, зформовані пристроєм усунення вирівнювання бітів (28) (на вході ф2 підстройки фази) для змінення відновлюваного синхронізуючого сигналу (23) і генерування сигналу відновленої синхронізації (31) 2 Пристрій відновлення синхронізації за п 1,який відрізняється тим, що запам'ятовуючий пристрій (ЗО) є "еластичним" запам'ятовуючим пристроєм, а вказані засоби (ф2, 32, 34) забезпечують перевірку умови недозаповнення чи переповнення запам'ятовуючого пристрою (ЗО) для виконання підстроювання до сигналу відновленої синхронізації (31) так, щоб підтримати ємність запам'ятовуючого пристрою 3 Пристрій відновлення синхронізації за будьяким з попередніх пунктів, який відрізняється тим, що відновлений сигнал синхронізації (31) модифікується у другому режимі (ф1, ф2), використовуючи дані вирівнювання бітів (28) 4 Пристрій відновлення синхронізації за будьяким з попередніх пунктів, який відрізняється тим, що засіб (34) використовується в іншому режимі роботи (фЗ) засобу фазового автопідстроювання частоти (32) для перевірки того, що запам'ятовуючий пристрій (ЗО) заповнено приблизно наполовину та для налагодження швидкості передачі відновленого сигналу синхронізації так, щоб підтримати умову половинного заповнення 5 Пристрій відновлення синхронізації за будьяким з попередніх пунктів, який відрізняється тим, що містить пристрій фазової автопідстройки частоти (32), який використовує як вхідний відновлюваний синхронізуючий сигнал (23), що видає сигнал відновленої синхронізації (31) на виході, та включає один чи більше додаткових входів (ф1, ф2, фЗ) для налагодження частоти вихідного сигналу 6 Пристрій відновлення синхронізації за будьяким з попередніх пунктів, який відрізняється тим, що ефект використання даних покажчика обнульовується шляхом модифікації відновленого сигналу ДВІЧІ з використанням даних покажчика, що мають однакову амплітуду, але протилежну полярність О 00 со ю 45398 Даний винахід відноситься до пристрою відновлення синхронізації для використання в синхронній цифровій ієрархічній (SDH) системі передачі даних Зокрема, винахід стосується створення пристрою, за допомогою якого треті сторони, що бажають використовувати SDH ЛІНІЮ зв'язку, яка знаходиться під керуванням іншого оператору, можуть передавати сигнали власної синхронізації та іншу інформацію в такій мережі Синхронізація третьої сторони встановлюється, коли сигнали синхронізації, які повинні бути передані в сигналі основної швидкості передачі, походять від джерела, яке несинхронізоване із джерелом, що використовується для синхронізації SDH мережі Тому синхронізація третьої сторони виявляється плезюхронною відносно до тактового сигналу широкополосного каналу передачі даних У SDH мережі сигнали основної частоти відображуються в модулі синхронної передачі (STM-N) з високою швидкістю передачі бітів в точці вводу мережі з використанням віртуальних накопичувачів (VC) та підпорядкованих блоків (TU), розмір і тип яких залежить від швидкості передачі даних підпорядкованих блоків об'єднуються разом в єдиний модуль синхронної передачі У точці виділення модуль синхронної передачі демультиплексується і відображується назад в сигнали основної швидкості передачі Однак, сигнали піддаються фазовим та частотним викривленням, що впливають наякість сигналу, який використовується для передачі синхронізуючої інформації Ключовим компонентом у SDH системах, що використовується для зменшення цих викривлень, є так званий десинхронізатор або пристрій відновлення синхронізації Даний винахід спрямований на удосконалення системи, розкритої в заявці на патент Великобританії 9114841 1, опублікованої під № GB 2257603A 13 січня 1993 Задача даного винаходу полягає в забезпеченні можливості третім сторонам, які використовують своє власне джерело синхронізації для основної швидкості передачі, передавати синхронізуючу інформацію по SDH мережі, яка використовується першою стороною В даний час це неможливо і, як показано на фіг 1В згаданого вище документу, потребує окремого каналу для передачі цієї синхронізуючої інформації В згаданому вище документі для відновлення синхронізації використовуються як дані показчика, так і дані вирівнювання бітів, або НІЯКІ З таких даних, причому синхронізація забезпечується на виході основної швидкості передачі в припущенні, що сигнал основної швидкості передачі синхронізований із широкополосним каналом передачі даних Заявник виявив, що коли дані вирівнювання бітів використовуються без даних покажчика, то SDH мережа може бути адаптована для передачі такої синхронізуючої інформації третьої сторони для надання окремого каналу Винахід пропонує пристрій відновлення синхронізації для синхронної цифрової ієрархічної (SDH) системи передачі даних, що забезпечує можливість третім сторонам використовувати SDH канал та містить вхід (5) для прийому мультиплек сованого сигналу модуля синхронної передачі, схеми (20) відновлення синхронізації для відновлення синхронізуючого сигналу із сигналу модуля синхронної передачі, демультиплексор (21) для демультиплексування сигналу модуля синхронної передачі на безліч сигналів підпорядкованих блоків, процесор показчика (25) для зчитування даних показчика із сигналу підпорядкованих блоків, пристрій усунення бітів вирівнювання (28) для зчитування даних вирівнювання бітів із сигналу підпорядкованих блоків, буферний запам'ятовуючий пристрій (ЗО) з монітором (34) запам'ятовуючого пристрою У вказаному запам'ятовуючому пристрої (ЗО) тимчасово зберігаються дані процесора підпорядкованих блоків, до того, як вони будуть синхронізовані з відновленою частотою синхронізації, при чому вказаний пристрій відновлення синхронізації відрізняється тим, що має засіб (32) для генерування сигналу відновленої синхронізації (31), який містить в собі три входи підстроики фази (ф1, ф2, фЗ), які з'єднані з процесором (25) показчика, пристроєм усунення бітів вирівнювання (28) та монітором запам'ятовуючого пристрою (34) ВІДПОВІДНО, при цьому використовуються тільки зчитані дані усування бітів вирівнювання, сформовані пристроєм усування бітів вирівнювання (28) (на вході ф2 підстроики фази) для модифікації відновленого синхронізуючого сигналу (23) і генерування відновленого сигналу синхронізації (31) Варіант здійснення винаходу буде описаний за допомогою приклада з посиланням на креслення, на яких показано наступне Фіг 1 - схематично показана SDN-мережа, яка може бути використана користувачем як третя сторона, фіг 2 - блок-схема, що ілюструє пристрій відновлення синхронізації, який виконаний у ВІДПОВІДНОСТІ до винаходу SDN-мережа (фіг 1) має джерело синхронізації 1 мережі, яке подає сигнал, наприклад, частотою 2 МГц, в пристрій обміну АТС-2 Пристрій обміну 2 подає сигнал із швидкістю 2Мбіт/сек на N сигнальних виходів 3 (зображено два), зв'язаних із SDHмультиплексором 4 Мультиплексований STM-N сигнал потім передають по широкополосному SDH-каналу 5 в SDH-демультиплексор б Пристрій обміну 2 також приєднаний до SDH- мультиплексору 4 за допомогою лінії управління 7, яка синхронізує широкополосний SDH- канал 5 із частотою синхронізації 2Мгц У демультиплексорі 6 сигнал перетворюється назад у формат основної швидкості передачі 2Мбіт/сек та подається по лінії 8 до пристрою обміну 9 ЛІНІЯ 10, відповідна до лінії 7, призначена для отримання синхронізуючої інформації із широкополосного каналу Додатково до цього, використовуючи пристрій відновлення синхронізації, який буде описаний, користувач третьої сторони може використовувати SDH-мережу для передачі синхронізуючої інформації та інших даних від приватної мережі 11 Джерело синхронізації 10 приватної мережі, яке не синхронізовано з джерелом синхронізації 1 мережі, передає синхронізуючі сигнали, тобто сигнали основної швидкості передачі 1 544Мбіт/сек чи 2 048Мбіт/сек по каналу 12 до SDH 45398 мультиплексора 4 Після демультиплексування ЗО, в якому поглинаються тимчасові фазові пересинхронізуючі сигнали передаються по каналу 13 хідні процеси, зумовлені проміжками, викликаними до приватної мережі 14 Можна бачити, порівнюювиділенням службових (додаткових) байтів та байчи фіг 1 з фіг 1 b у вищезгаданий заявці на патент тів вирівнювання Сигнал основної швидкості 29 з Великобританії, що синхронізуюча інформація від відновленою синхронізацією за допомогою засобу, третьої сторони у пристрої, який передував даноякий буде описаний, а потім зчитується з "еластиму винаходу, повинна була передаватися по окречного" запам'ятовуючого пристрою по ЛІНІЯМ 8 чи мому каналу 13 (фіг 1) На фіг 2 більш докладно зображено демульСхема фазової автопідстройки частоти тишіексор 6 разом з пристроєм десинхронізації чи (ФАПЧ) 32 отримує як вхідний опорний сигнал пристроєм відновлення синхронізації Мультиплесинхронізації ТО широкополосного каналу, відновксований STM-N сигнал спочатку подається на лений пристроєм 20 та видає модифікований сигсхему відновлення синхронізації 20, в якому так нал синхронізації зчитування для використання у званий синхронізуючий сигнал "TU" подається на даних відновленої синхронізації з "еластичного" ЛІНІЮ 23 Після ЦЬОГО об'єднаний сигнал надходить запам'ятовуючого пристрою ЗО Сигнал синхроніна демультиплексор 21, де він поділяється на N зації зчитування 31 може бути отриманий будьсигналів низького порядку, позначених як дані TUяким з множини способів Схема фазової автопідс11 чи TU-12 в залежності від частоти проходження тройки частоти 32 має три входи підстройки фази бітів сигналів основної швидкості (1 544Мбіт/сек чи ф1, ф2 та фЗ Вони з'єднані з процесором 25 пока2 048Мбіт/сек ВІДПОВІДНО) КОЖНИЙ З N сигналів зчика, пристроєм усунення вирівнювання бітів 28 основної швидкості 22 потім надходить на пристрій та монітором 34 запам'ятовуючого пристрою, ВІДвідновлення синхронізаціхі Хоча зображено тільки ПОВІДНО Вибір конкретної комбінації для викорисодин такий пристрій для одного демультиплексотання регулюється через селектор режиму 36, ра, на практиці має існувати окремий пристрій для який керує ВІДПОВІДНИМИ перемикачами для кожнокожного з N каналів 22 Дані TU підпорядкованих го з входів підстройки фази блоків спочатку надходять на процесор 25 показРобота схеми спочатку буде описана у нормачика Процесор показчика є частиною засобів адальному режимі роботи, тобто без участі третьої птації канапу високого порядку, і його функція посторони У першому режимі вибирається вхід ф1, і лягає в інтерпретації різниць фаз та частот між монитор запам'ятовуючого пристрою 34 регулюсигналами синхронізації в точці входу та точці виється так, щоб гарантувати, що "еластичний" заходу SDH-мережі, які закодовані показчиком попам'ятовуючий пристрій залишиться напівзаповдпорядкованих блоків "Показчики" більш детально неним, так що швидкість даних, що видаються із описані у зазначеній вище заявці на патент Велизапам'ятовуючого пристрою, дорівнювала швидкокобританії По суті, кожний віртуальний накопичусті, з якою вони поступають до запам'ятовуючого вач або VC сигнал має можливість знаходитися у пристрою Таким чином, синхронізуючий сигнал об'єднаному потоці байтів, так що початкова точка для основної швидкості передачі може бути відвіртуального накопичувача у спільному SDH- сигтворений точно налі може змінюватися для кадрів, що йдуть один У другому режимі обираються входи ф1 та ф2, за одним Значення показчика встановлює почата вхід фЗ блокується У цьому режимі сигнал відкову точку конкретного віртуального накопичувача новленої синхронізації широкополосного каналу на Процесор 25 показчика, крім того, приймає сигнал лінії 23 використовується безпосередньо з фазодозволу по лінії 26, який функціонує як динамічний вим регулюванням, що здійснена процесором 25 флаг для вказування, чи є дані у будь-якому конкпоказчика та пристроєм усунення бітового вирівретному SDH- сигналі істинними чи дійсними данювання 28 ними, чи відносяться до службових (непродуктивКоли зазначена вище схема повинна бути виних) даних користана для відновлення синхронізації основної швидкості для користувача третьої сторони, жоден Після процесору показчика отримані дані вірз наведених вище режимів не може бути використуального накопичувача передаються на пристрій таний Робота вищезгаданого пристрою десинхроусунення бітів вирівнювання 28, який утворює часнізації виконує регулювання показчика підпорядтину службових даних каналу низького порядку кованих блоків, призводячи до фазового Бітове вирівнювання визначено стандартами перехідного процесу, що приблизно дорівнює МККТТ По суті, дані вирівнювання бітів забезпе3,5мксек на один показчик, на виході SDH мережі чують засіб, який вказує, де у віртуальному накоПри належній конструкції десинхронізатора буде пичувачі знаходиться сигнал зі швидкістю передачі мати місце обмеження швидкості "відходу" цієї 2Мбіт/сек Наприклад, у точці входу до системи фази за рахунок обмеження ВІДПОВІДНОГО зсуву може бути більше даних графіка, ніж це може бути частоти пристрою ФАПЧ десинхронізатора Це розміщено у байтовому просторі, призначеному обмеження звичайно набуває фазової форми звудля цієї мети Будь-які дані переповнення можуть ження смуги пропускання ФАПЧ, призводячи до бути розміщені у додаткових байтах вирівнювання близько розташованих настройок показчика проВирівнювання бітів використовується для отритилежної полярності, що взаємно компенсуються мання засобу вказування, що дані графіка розміта не виявляють результативної дії на кінцевий щені у додаткових байтах вирівнювання, і що їх вихідний сигнал Однак, настройки показчика пронеобхідно віднайти перш, ніж сигнал може бути тилежної полярності, не розділені великим проміжнадісланий на подальшу обробку Після усунення ком (більше, ніж постійна часу RC схеми ФАПЧ) не бітів вирівнювання дані, що залишилися, подаютьбудуть взаємно скомпенсовані ся до "еластичного" запам'ятовуючого пристрою У синхронізованих SDH-мережах зміни показчика TU-1 будуть мати місце в результаті факторів, що повільно змінюються, наприклад, температурних ефектів у оптичних волокнах та мультиплексорі Хоча обладнання в основному допускає такі стрибки фази, що вводиться до сигналів основної швидкості, існують деякі системи, призначені для плезюсинхронної цифрової ієрархічної (PDH) передачі, що використовує тільки способи вирівнювання бітів, що мають припустиме відхилення менш, ніж Імксек Винахід пропонує засіб, за допомогою якого вплив змін показчика TU-1 може бути виключений, що призводить до вихідного фазового відгуку десинхронізатору, що можна порівняти із фазовим відгуком пристрою усунення вирівнювання бітів У третьому режимі роботи для використання при відновленні синхронізації для основної швидкості для третіх сторін, селектор 36 режиму працює так, що при нормальному режимі роботи третьої сторони вводиться в дію тільки вхід ф2, так що використовуються тільки дані усунення бітів вирівнювання для настройки частоти синхронізації ТО Хоча на кресленні вхід ф1 зображений як вимкнений, в альтернативному варіанті схема ФАПЧ може працювати у ВІДПОВІДЬ на сигнали настройки ф1, але компенсуючи кожну появу сигналом настройки рівної величини та протилежної полярності Таким чином, робота аналогічна роботі PDHдемультиплексора Вхід фЗ також може бути вве 45398 8 дений в дію як запобіжний захід, але монітор 34 запам'ятовуючого пристрою та "еластичне" запам'ятовуючого пристрою працюють по-різному, як буде описано нижче До тих пір, поки SDH-мережа залишається синхронізованою, ігнорування показчиків не матиме тривалого впливу на синхронізацію, що виконується для сигналу основної швидкості Фактично, будь-які тимчасові втрати синхронізації чи великі значення дрейфа у мережі SDH будуть врегульовані у "еластичному" запам'ятовуючому пристрої ЗО Це допускається у відносно великих межах, звичайно більше 40мксек для врегулювання максимально допустимого дрейфу у SDH-каналі Якщо синхронізація SDH-мережі втрачена та протязі тривалого часу, то в результаті, можливо, буде мати місце незаповнення чи переповнення "еластичного" запам'ятовуючого пристрою ЗО Монітор 34 запам'ятовуючого пристрою буде потім ініціювати "ВІДХІД" фази для відновлення ємності "еластичнго" запам'ятовуючого пристрою 32 Таким чином, монітор 34 запам'ятовуючого пристрою працює ВІДМІННИМ способом у порівнянні із способом, описаним для нормального режиму, чи без використання третьої сторони Як альтернатива, ємність може бути відновлена шляхом тимчасової заміни операції десинхронізації на один з перших двох режимів, тобто використання тільки монітору запам'ятовуючого пристрою на вході фЗ чи настройка з використанням ф1 та ф2 на протязі обмеженого періоду часу СИНХРОНІЗУЮЧИЙ КАНАЛ СИНХРОНІЗАЦІЯ ВЩ КАНАЛА Ґ 10 ИРНСТРШ ОБШНУ В ДЖЕРЕЛО СИНХРОШЗАЩ МЕРЕЖІ 1,1, SDH №• ИУЛЬТЕШІЕКСОР 2 МБіт/с 14 ЩІА.СНЕ ДЖЕРЕЛО і 1 "(ІСННХРОНІЗАіф " -13 Фіг. І ВЛАСНА МЕРЕЖА і І —~> > 45398 10 ЗЧИТУВАННЯ 20 ї 544 МБіт'с ФАЗОВА АВТОЩЦСТРОЙКА ЧІСТОТИ PLt (1.5/2 ЧГи) ФІГ.2 ДП «Український інститут промислової власності» (Укрпатент) вул Сім'ї Хохлових, 15, м Київ, 04119, Україна (044)456-20- 90 ТОВ "Міжнародний науковий комітет" вул Артема, 77, м Київ, 04050, Україна (044)216-32-71

ДивитисяДодаткова інформація

МПК / Мітки

Мітки: синхронізації, передачі, цифрової, даних, системі, ієрархічної, відновлення, пристрій, синхронної

Код посилання

<a href="https://ua.patents.su/5-45398-pristrijj-vidnovlennya-sinkhronizaci-dlya-sinkhronno-cifrovo-iehrarkhichno-sistemi-peredachi-danikh.html" target="_blank" rel="follow" title="База патентів України">Пристрій відновлення синхронізації для синхронної цифрової ієрархічної системи передачі даних</a>

Попередній патент: Спосіб одержання каталізатора для полімеризації олефіну

Наступний патент: Спосіб визначення заліза в мінеральних кислотах

Випадковий патент: Резервуар