Асинхронний інерційний лічильник

Номер патенту: 52731

Опубліковано: 15.01.2003

Автори: Осадчий Володимир Євгенович, Осадчий Олександр Євгенович

Формула / Реферат

1. Асинхронний інерційний лічильник, що містить дешифратор та блок лічильника, який відрізняється тим, що додатково містить пріоритетний шифратор, а блок лічильника виконаний у вигляді ланцюжка повторювачів з елементами І-НЕ і RS-тригерами, входи і виходи яких підключені до відповідних однойменних входів і виходів блока лічильника, інверсні R-входи RS-тригерів сполучені між собою і підключені до інверсного входу "Обнулення" блока лічильника, інші входи елементів І-НЕ також сполучені між собою і підключені до інверсного входу "Стоп" блока лічильника, дешифратор і пріоритетний шифратор мають входи дозволу роботи, при цьому виходи дешифратора підключені до відповідних однойменних входів блока лічильника, виходи блока лічильника сполучені з відповідними однойменними входами пріоритетного шифратора, а вихід останнього повторювача ланцюжка повторювачів блока лічильника сполучений також з шиною "Кінець відліку" асинхронного інерційного лічильника, вхід "Обнуления" асинхронного інерційного лічильника сполучений з однойменним входом блока лічильника, вхід "Стоп" блока лічильника підключений до шини "Стоп" асинхронного інерційного лічильника, шина керуючого сигналу "Запис" якого підключена до входу дозволу роботи дешифратора, а шина керуючого сигналу "Читання" підключена до входу дозволу роботи пріоритетного шифратора, шина вхідних даних асинхронного інерційного лічильника сполучена з відповідними входами дешифратора, шина вихідних даних асинхронного інерційного лічильника сполучена з відповідними виходами пріоритетного шифратора, вихід кожного попереднього (починаючи з першого і закінчуючи передостаннім) повторювача ланцюжка повторювачів блока лічильника сполучений також з входом наступного повторювача.

2. Лічильник за п. 1, який відрізняється тим, що при і-ому значенні вхідного слова, де і = 0,1,..., (2n-1) (n кількість входів дешифратора, за винятком входу дозволу роботи), одиниця з'являється на виході дешифратора, підключеному до (і+1) -го повторювача зсувального ланцюжка блока лічильника, а пріоритетний шифратор перетворює одиницю, зняту з виходу (і+1) -го RS-тригера блока лічильника, в і-е значення на виходах.

3. Лічильник за п. 1, який відрізняється тим, що при реверсивному відліку послідовності виходів дешифратора і входів пріоритетного шифратора, за винятком входу дозволу роботи пріоритетного шифратора, змінюються на зворотні.

Текст

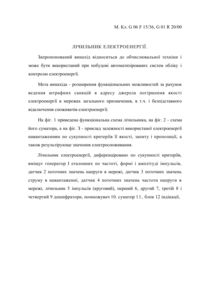

1 Асинхронний інерційний лічильник, що містить дешифратор та блок лічильника, який відрізняється тим, що додатково містить пріоритетний шифратор, а блок лічильника виконаний у вигляді ланцюжка повторювачів з елементами IНЕ і RS-тригерами, входи і виходи яких підключені до ВІДПОВІДНИХ однойменних входів і виходів блока лічильника, інверсні R-входи RS-тригерів сполучені між собою і підключені до інверсного входу "Обнуления" блока лічильника, ІНШІ ВХОДИ еле ментів І-НЕ також сполучені між собою і підключені до інверсного входу "Стоп" блока лічильника, дешифратор і пріоритетний шифратор мають входи дозволу роботи, при цьому виходи дешифратора підключені до ВІДПОВІДНИХ однойменних входів блока лічильника, виходи блока лічильника сполучені з ВІДПОВІДНИМИ однойменними входами пріоритетного шифратора, а вихід останнього повторювача ланцюжка повторювачів блока лічильника сполучений також з шиною "Кінець відліку" асинхронного інерційного лічильника, вхід Винахід відноситься до галузі обчислювальної техніки і може бути використаний як швидкодіючий ДВІЙКОВИЙ ЛІЧИЛЬНИК Відомий регістр зсуву /А С СССР N1624531 М кл G 11 3 19/00 від 1991 р /, що містить в кожному розряді четирьохстабшльний триггер побудований по схемі М - S з різно-полярним управлінням з входами і виходами/ кодові перетворювачі що складаються з елементів І-НЕ, І, прямі і інверсні "Обнуления" асинхронного інерційного лічильника сполучений з однойменним входом блока лічильника, вхід "Стоп" блока лічильника підключений до шини "Стоп" асинхронного інерційного лічильника, шина керуючого сигналу "Запис" якого підключена до входу дозволу роботи дешифратора, а шина керуючого сигналу "Читання" підключена до входу дозволу роботи пріоритетного шифратора, шина вхідних даних асинхронного інерційного лічильника сполучена з ВІДПОВІДНИМИ входами дешифратора, шина вихідних даних асинхронного інерційного лічильника сполучена з ВІДПОВІДНИМИ виходами пріоритетного шифратора, вихід кожного попереднього (починаючи з першого і закінчуючи передостаннім) повторювача ланцюжка повторювачів блока лічильника сполучений також з входом наступного повторювача 2 Лічильник за П 1, який відрізняється тим, що при 1-ому значенні вхідного слова, де і = 0,1, , (2П1) (п КІЛЬКІСТЬ входів дешифратора, за винятком входу дозволу роботи), одиниця з'являється на виході дешифратора, підключеному до (і+1) -го повторювача зсувального ланцюжка блока лічильника, а пріоритетний шифратор перетворює одиницю, зняту з виходу (і+1) -го RS-тригера блока лічильника, в і-е значення на виходах 3 Лічильник за П 1, який відрізняється тим, що при реверсивному відліку ПОСЛІДОВНОСТІ виходів дешифратора і входів пріоритетного шифратора, за винятком входу дозволу роботи пріоритетного шифратора, змінюються на зворотні виходи регістра Співпадаючими з пристроєм, що пропонується ознаками є зсуваючий ланцюжок що складається з повторювачів і триггерів Даний пристрій використовується в пристроях послідовного прийому-передачі інформації і забезпечує зсув двійкового коду Однак пристрій має обмежене застосування і не призначений для виконання відліку О Ю 52731 Відомий, також лічильник /А С СССР N1267612 М кл Н 03 К 23/00 від 1986р/ що складається з блоку лічильника, з ланцюжка що складається з Т- і Dt - триггерів, прямий вхід Т - триггеру сполучений з D - входом Dt триггеру ВІДПОВІДНОГО розряду, а тактові входи Dt - триггерів і Т - триггерів першого розряду сполучені з шиною тактових імпульсів, додатково введений елемент АБО, осередок дешифратора і блок управління, вхід якого сполучений з входом управління, а вихід сполучений з V - входом Т - триггеру першого розряду, перший вхід елемента АБО сполучений з виходом осередку дешифратора, а другий вхід - з шиною обнуления, вихід елемента АБО сполучений з ВІДПОВІДНИМИ входами всіх триггерів, входи дешифратора сполучені з прямими виходами Dt - триггерів, інверсний вихід кожного Dt - триггеру сполучений з тактовим входом Т триггеру останнього розряду Загальними з технічним рішенням, що пропонується ознаками є використання ланцюжка елементів для організації відліку, а також дешифратора Пристрій підвищує швидкодію двійкового відліку, але він зайве ускладнений і час відліку значний, оскільки існує нерівномірність довжини тимчасових інтервалів між різними станами лічильника, яка вирішується розтягненням тактуючих сигналів, в зв'язку з існуванням ступєневої залежності часу порозрядного двійкового відліку від КІЛЬКОСТІ його розрядів Найбільш близьким по технічній суті до технічного рішення, що пропонується є N-розрядний лічильник /Патент Російської федерації № 2128878 Н 03 К 23/00 від 1997р// що містить дешифратор, блок лічильника з ланцюжка D - триггерів, при цьому N - розрядний лічильник додатково містить шифратор, а блок лічильника, виконаний у вигляді зсуваючого ланцюжка D-триггерів з R-входами, інформаційні D-входи яких, а також виходи, підключені до ВІДПОВІДНИХ однойменних входів і виходів блоку лічильника, R-входи сполучені між собою і підключені до входу обнуления блоку лічильника, входи синхронізації D-триггерів також сполучені між собою і підключені до входу синхронізації блоку лічильника, дешифратор і шифратор мають входи дозволу роботи, при цьому виходи дешифратора підключені до ВІДПОВІДНИХ однойменних входів блоку лічильника, виходи блоку лічильника сполучені з ВІДПОВІДНИМИ однойменними входами шифратора, а вихід останнього D-триггеру зсуваючого ланцюжка блоку лічильника сполучений також з шиною "Кінець відліку" N розрядного лічильника, вхід "Обнуления" N - розрядного лічильника сполучений з однойменним входом блоку лічильника, вхід синхронізації блоку лічильника підключений до шини синхронізації N розрядного лічильника, шина керуючого сигналу "Запис" якого підключена до входу дозволу роботи дешифратора, а шина керуючого сигналу "Читання" підключена до входу дозволу роботи шифратора, шина вхідних даних N - разрядного лічильника сполучена з ВІДПОВІДНИМИ входами дешифратора, шина вихідних даних N - розрядного лічильника сполучена з ВІДПОВІДНИМИ виходами шифратора, вихід кожного попереднього (почина ючи з першого і закінчуючи передостаннім) Dтриггеру зсувючого ланцюжка блока лічильника сполучений також з D-входом наступного Dтриггеру Пристрій підвищує швидкодію двійкового відліку, але він зайве ускладнений і час відліку значний, оскільки як функціональні елементи відліку у лічильнику використовуються триггери, що в порівнянні з використанням повторювачів істотно обмежує Й Г ШВИДКОДІЮ ОО В основу винаходу поставлена задача створити такий пристрій, в якому реалізоване нове конструктивне виконання блоку лічильника з використанням ланцюжка елементів, (повторювачів) що забезпечують незначні тимчасові затримки на перемикання з одного логічного стану, в інший Заповнення ланцюжка здійснюється дешифратором, на вхід якого подається двійковий код, а результат перемикання елементів ланцюжка повторювачів перетворюється пріоритетним шифратором в загальноприйнятий ДВІЙКОВИЙ КОД, Щ ДОЗВОЛЯЄ О отримати пристрій з розширеними функціональними можливостями і областю застосування Поставлена задача вирішується асинхронним інерційним лічильником, що містить дешифратор, блок лічильника з ланцюжка повторювачів, елементів І-НЕ І RS триггерів, при цьому асинхронний інерційний лічильник додатково містить пріоритетний шифратор Блок лічильника, виконаний у f вигляді ланцюжка повторювачів, до кожного з яких підключені ВІДПОВІДНИМИ входами елементи І-НЕ і наступні за ними RS - триггери До виходів дешифратора підключені входи повторювачів, а виходи повторювачів підключені до ВІДПОВІДНИХ ВХОДІВ елементів І-НЕ Інверсні виходи елементів І-НЕ підключені до інверсних S-входів RS - триггерів Виходи RS - триггерів підключені до ВІДПОВІДНИХ виходів блоку лічильника і до входів пріоритетного шифратора Інверсні R-входи сполучені між собою і підключені до інверсного входу обнуления блоку лічильника, ІНШІ входи елементів І-НЕ також сполучені між собою і підключені до інверсного входу стопа блоку лічильника, дешифратор і шифратор мають входи дозволу роботи, при цьому виходи дешифратора підключені до ВІДПОВІДНИХ ВХОДІВ блоку лічильника, виходи блоку лічильника сполучені з ВІДПОВІДНИМИ однойменними входами пріоритетного шифратора, а вихід останнього повторювача ланцюжка повторювачів блоку лічильника сполучений також з шиною "Кінець відліку", вхід "Обнуления" асинхронного інерційного лічильника сполучений з однойменним входом блоку лічильника, вхід стопа блоку лічильника підключений до шини "Стоп" асинхронного інерційного лічильника, шина керуючого сигналу "Запис" якого підключена до входу дозволу роботи дешифратора, а шина керуючого сигналу "Читання" підключена до входу дозволу роботи пріоритетного шифратора, шина вхідних даних асинхронного інерційного лічильника сполучена з ВІДПОВІДНИМИ входами дешифратора, шина вихідних даних асинхронного інерційного лічильника сполучена з ВІДПОВІДНИМИ виходами пріоритетного шифратора, вихід кожного попереднього (починаючи з першого і закінчуючи передостаннім) повторювача ланцюжка повторювачів блоку лічильника сполучений також з входом на 52731 ступного повторювача Прямий ВІДЛІК забезпечупідвищення швидкодії двійкового відліку і досягється тим, що при 1-ому значенні вхідного слова, нення рівномірності довжини тимчасових інтерваП де і = 0,1, , (2 -1) (п КІЛЬКІСТЬ входів дешифратолів між різними станами лічильника не залежно від ра, за винятком входу дозволу роботи), одиниця КІЛЬКОСТІ його розрядів за рахунок реалізації стуз'являється на виході дешифратора підключеного пеневої залежності більш низького порядку часу до (і+1) - ого повторювача зсуваючого ланцюжка порозрядного двійкового відліку від КІЛЬКОСТІ розблоку лічильника/ а пріоритетним шифратором рядів і функціональних можливостей, за рахунок перетворює одиницю зняту з виходу (і+1) -го RSможливості реалізації прямого і реверсивного триггеру блоку лічильника в і-е значення на виховідліку, а також за рахунок використання як ВІДЛІдах Реверсивний ВІДЛІК забезпечується зміною, на кових елементів повторювачів, що мають найзворотні, послідовностей виходів дешифратора і менший час зпрацювання Триггери використовувходів пріоритетного шифратора, за винятком ються лише для фіксації результату відліку входу дозволу роботи пріоритетного шифратора На фіг 1 представлена схема пристрою, що пропонується ВІДМІТНИМИ ознаками пристрою, що пропонується є те, що асинхронний інерційний лічильник Пристрій, що пропонується містить (див фіг 1) додатково містить пріоритетний шифратор, а блок блок 1 лічильника, що складається з ланцюжка п лічильника, виконаний у вигляді ланцюжка повтоповторювачів 1 і, і=1, , к, (к=2 ) елементів І-НЕ 2 і, рювачів з елементами І-НЕ і RS-триггерами, входи і=1, , к і RS - триггерів 3 і, і=1, , к, при цьому асиі виходи яких підключені до ВІДПОВІДНИХ однойменнхронний інерційний ЛІЧИЛЬНИК додатково містить них входів і виходів блоку лічильника Інверсні Rпріоритетний шифратор 5 і дешифратор 4 Блок входи RS-триггерів сполучені між собою і підклюлічильника 1 виконаний у вигляді ланцюжка почені до інверсного входу обнуления блоку лічильвторювачів 1 і, і=1, , к, до кожного з яких підклюника, ІНШІ входи елементів І-НЕ також сполучені чені ВІДПОВІДНИМИ входами елементи І-НЕ 21, між собою і підключені до інверсного входу стопа і=1, , k і наступні за ними RS-триггери 3 і, і=1, , к блоку лічильника, дешифратор і пріоритетний До виходів дешифратора 4 підключені входи пошифратор мають входи дозволу роботи, при цьовторювачів 1 і, і=1, , к, а виходи повторювачів 1 і, му виходи дешифратора підключені до ВІДПОВІДНИХ і=1, , к, підключені до ВІДПОВІДНИХ входів елеменоднойменних входів блоку лічильника, виходи тів І-НЕ 2 і, і=1, , k Інверсні виходи елементів І-НЕ блоку лічильника сполучені з ВІДПОВІДНИМИ одно2 і, і=1, , k підключені до інверсних S-входів RS йменними входами пріоритетного шифратора, а триггерів З і , І = 1 , , k Виходи RS - тригерів З і , вихід останнього повторювача ланцюжка повтоі=1, , к, підключені до ВІДПОВІДНИХ виходів блоку рювачів блоку лічильника сполучений також з шилічильника 1 і до входів пріоритетного шифратора ною "Кінець відліку" асинхронного інерційного лі5 Інверсні R-входи RS - триггерів 3 і, і=1, , k спочильника, вхід "Обнуления" асинхронного інерційлучені між собою і підключені до інверсного входу ного лічильника сполучений з однойменним вхообнуления блоку лічильника, ІНШІ ВХОДИ елементів дом блоку лічильника, вхід стопа блоку лічильника І-НЕ 2 і, 1=1, , к, також сполучені між собою і підпідключений до шини "Стоп" асинхронного інерключені до інверсного входу стопа блоку лічильниційного лічильника, шина керуючого сигналу "Зака 1, дешифратор 4 і пріоритетний шифратор 5 пис" якого підключена до входу дозволу роботи мають входи дозволу роботи, при цьому виходи дешифратора, а шина керуючого сигналу "Читандешифратора 4 підключені до ВІДПОВІДНИХ ВХОДІВ ня" підключена до входу дозволу роботи пріоритеблоку лічильника 1, виходи блоку лічильника 1 тного шифратора, шина вхідних даних асинхронсполучені з ВІДПОВІДНИМИ однойменними входами ного інерційного лічильника сполучена з ВІДПОВІДпріоритетного шифратора 5, а вихід останнього НИМИ входами дешифратора, шина вихідних даних повторювача ланцюжка повторювачів 1 і, і=1, к, асинхронного інерційного лічильника сполучена з блоку лічильника 1 сполучений також з шиною ВІДПОВІДНИМИ виходами пріоритетного шифратора, "Кінець відліку", вхід "Обнуления" асинхронного вихід кожного попереднього (починаючи з першого інерційного лічильника сполучений з однойменним і закінчуючи передостаннім) повторювача ланцюжвходом блоку лічильника 1, вхід стопа блоку лічика повторювачів блоку лічильника сполучений тальника 1 підключений до шини "Стоп" асинхроннокож з входом наступного повторювача Прямий го інерційного лічильника, шина керуючого сигналу ВІДЛІК забезпечується тим, що при і-ому значенні "Запис" якого підключена до входу дозволу роботи вхідного слова, де і = 0,1, , (2п-1) (п КІЛЬКІСТЬ ВХОдешифратора 4, а шина керуючого сигналу "ЧиДІВ дешифратора, за винятком входу дозволу ротання" підключена до входу дозволу роботи пріоботи), одиниця з'являється на виході дешифраторитетного шифратора 5, шина вхідних даних асинра підключеному до (і+1) -ого повторювача зсувахронного інерційного лічильника сполучена з ВІДючого ланцюжка блоку лічильника, а пріоритетний ПОВІДНИМИ входами дешифратора 4, шина вихідшифратор перетворює одиницю зняту з виходу них даних асинхронного інерційного лічильника (і+1) -го RS-триггеру блоку лічильника в і-е знасполучена з ВІДПОВІДНИМИ виходами пріоритетного чення на виходах Реверсивний ВІДЛІК забезпечушифратора 5, вихід кожного попереднього (почиється зміною, на зворотні, послідовностей виходів наючи з першого і закінчуючи передостаннім) подешифратора і входів пріоритетного шифратора, вторювача 1 і, і=1, , к-1, ланцюжки повторювачів за винятком входу дозволу роботи пріоритетного блоку лічильника сполучений також з входом нашифратора ступного повторювача Реверсивний ВІДЛІК забезпечується зміною, на зворотні, послідовностей виходів дешифратора 4 і входів пріоритетного Сукупність вищеперелічених ознак пристрою, шифратора 5, за винятком входу дозволу роботи що пропонується дозволяє отримати технічний результат, що полягає в тому, що забезпечується 52731 пріоритетного шифратора 5 Технічна реалізація кожного з блоків і вузлів пристрою (, що пропонується фіг1) не складає будь-яких ускладнень, оскільки вони реалізовані на основі елементарних логічних елементів, RSтриггерів і найпростіших дешифраторі і пріоритетному шифраторі Робота лічильника заснована на тому, що кожному вхідному слову, в двійковому уявленні, ставиться у ВІДПОВІДНІСТЬ його код у вигляді сукупності нулів і однієї одиниці, який заноситься в ланцюжок повторювачів 1 і, (і=1, , к) блоку 1 лічильника, і після чого може бути перетворений в слово в двійковому уявленні, ВІДПОВІДНО стану RS-триггерів У залежності від функціонального призначення (додавання або віднімання одиниці) 'лічильник може бути реалізований з прямим і реверсним вдліком Функціонування обох варіантів ЛІЧИЛЬНИКІВ відрізняється роботою дешифратора 4 і пріоритетного шифратора 5 Робота пристрою відбувається таким чином У початковому стані значення на виходах RS - триггерів З і , і=1, , k і повторювачів 1 і, і=1, , k невизначені Виходи дешифратора 4 знаходяться у високоомному стані (сигнал "Запис" знаходиться в стані логічного нуля) По шині обнуления подають сигнал обнуления, який, поступаючи в блок 1 лічильника і далі на ВІДПОВІДНІ входи RS-триггерів З і, (і=1, , к) встановлює їх в стан "нуля" Після ДІЇ сигналу обнуления на шині "Запис" встановлюють керуючий сигнал "Запис", представлений у вигляді логічної "одиниці" ВІН ДОЗВОЛЯЄ роботу дешифратора 4 При цьому на шині вхідних 8 даних встановлюють код слова, яке повинне бути перетворене в "одиницю" на одному з виходів дешифратора 4 "Одиниця", поступаючи на ВІДПОВІДНИЙ ВХІД одного з повторювачів 1 і, (і=1, , к), "перемикає" його в стан "одиниця" Сигнал "Запис" не знімається до закінчення відліку Таким чином почергово в стан логічної одиниці перемикаються наступні в ланцюжку повторювачів 1 і, (і=1, , к) повторювачі, при умові встановлення логічної одиниці на шині "Стоп", відбувається перемикання ВІДПОВІДНИХ елементів І-НЕ 2 і, (і=1, , к), ЯКІ В СВОЮ чергу встановлюють в стан логічної одиниці ВІДПОВІДІ RS-триггери 3,і, (і=1, , к) ЯКЩО на шині "Читання" встановлюють керуючий сигнал "Читання", представлений у вигляді логічної "одиниці", ЯКИЙ дозволяє роботу пріоритетного шифратора 5 (в певні моменти часу на частині входів пріоритетного шифратора 5 знаходиться ПОСЛІДОВНІСТЬ З певного числа логічних "одиниць"), то на шині вихідних даних отримують проміжне значення лічильника По досягненні "одиницею" повторювача 1 к, на виході "Кінець відліку" з'являється "одиниця" Надалі робота пристрою не відрізняється від приведеної Пристрій, що Пропонується на відміну від базового, має високу швидкодію і забезпечує виконання прямого і реверсивного двійкового відліку Таким чином, забезпечується розширення функціональних можливості і галузей застосування пристрою Фіг. 52731 ТОВ "Міжнародний науковий комітет" вул Артема, 77, м Київ, 04050, Україна (044)236-47-24 10

ДивитисяДодаткова інформація

Назва патенту англійськоюAsynchronous binary counter

Автори англійськоюOsadchyi Oleksandr Yevhenovych, Osadchyi Volodymyr Yevhenovych

Назва патенту російськоюАсинхронный двоичный счетчик

Автори російськоюОсадчий Александр Евгеньевич, Осадчий Владимир Евгеньевич

МПК / Мітки

МПК: H03K 23/00

Мітки: лічильник, інерційний, асинхронний

Код посилання

<a href="https://ua.patents.su/5-52731-asinkhronnijj-inercijjnijj-lichilnik.html" target="_blank" rel="follow" title="База патентів України">Асинхронний інерційний лічильник</a>

Попередній патент: Спосіб лазерної обробки виробів з інструментальних та теплостійких сталей та сплавів

Наступний патент: Спосіб вимірювання температури

Випадковий патент: Спосіб розспорядження боєприпасів