Пристрій для нормалізації векторів у системах комп’ютерної графіки

Номер патенту: 63343

Опубліковано: 10.10.2011

Автори: Романюк Олександр Никифорович, Романюк Оксана Володимирівна, Павлик Тетяна Миколаївна

Формула / Реферат

Пристрій для нормалізації векторів у системах комп'ютерної графіки, який містить сім блоків множення, три суматори, вихід першого блока множення підключено до першого входу першого суматора, вихід другого блока множення підключено до другого входу першого суматора, вихід третього блока множення підключено до третього входу першого суматора, вихід четвертого блока множення підключено до входу третього суматора, вихід п'ятого блока множення підключено до першого інформаційного виходу пристрою, вихід шостого блока множення підключено до другого інформаційного виходу пристрою, вихід сьомого блока множення підключено до третього інформаційного виходу пристрою, який відрізняється тим, що в нього введено восьмий блок множення, блок постійної пам'яті, перший, другий, третій регістри, причому перший регістр інформаційним входом підключений до першого інформаційного входу пристрою, керуючим входом з'єднаний з першим керуючим входом пристрою, а виходом підключений до першого та другого входів першого блока множення та другого входу п'ятого блока множення, другий регістр інформаційним входом підключений до другого інформаційного входу пристрою, керуючим входом з'єднаний з другим керуючим входом пристрою, а виходом підключений до першого та другого входів другого блока множення та другого входу шостого блока множення, третій регістр інформаційним входом підключений до третього інформаційного входу пристрою, керуючим входом з'єднаний з третім керуючим входом пристрою, а виходом підключений до першого та другого входів третього блока множення та другого входу сьомого блока множення, перший вхід восьмого блока множення підключено до виходу першого суматора, а другий вхід - до другого виходу блока постійної пам'яті, другий вхід четвертого блока множення підключено до виходу другого суматора, а перший вхід - до виходу першого суматора, другий вхід третього суматора підключено до третього виходу блока постійної пам'яті, а вихід підключено до перших входів п'ятого, шостого, сьомого блоків множення відповідно.

Текст

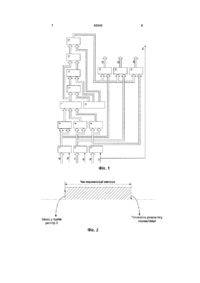

Пристрій для нормалізації векторів у системах комп'ютерної графіки, який містить сім блоків множення, три суматори, вихід першого блока множення підключено до першого входу першого суматора, вихід другого блока множення підключено до другого входу першого суматора, вихід третього блока множення підключено до третього входу першого суматора, вихід четвертого блока множення підключено до входу третього суматора, вихід п'ятого блока множення підключено до першого інформаційного виходу пристрою, вихід шостого блока множення підключено до другого інформаційного виходу пристрою, вихід сьомого блока множення підключено до третього інформаційного виходу пристрою, який відрізняється тим, що в нього введено восьмий блок множення, блок постійної пам'яті, перший, другий, третій регістри, причому перший регістр інформаційним входом U 2 (19) 1 3 ження підключено до першого входу першого суматора, а перший та другий входи підключено до першого інформаційного входу пристрою, вихід другого блока множення підключено до другого входу першого суматора, а перший та другий входи підключено до другого інформаційного входу пристрою, вихід третього блока множення підключено до третього входу першого суматора, а перший та другий входи підключено до третього інформаційного входу пристрою, вхід другого суматора підключено до виходу першого суматора, перший та другий входи четвертого блока множення підключено до виходу другого суматора, а вихід підключено до першого входу третього суматора, другий вхід третього суматора підключено до виходу другого суматора, а вихід підключено до входу блока ділення, вхід четвертого суматора підключено до виходу блока ділення, а вихід підключено до других входів п'ятого, шостого, сьомого блоків множення, перші входи яких підключено до першого, другого та третього входів пристрою відповідно, виходи п'ятого, шостого, сьомого блоків множення підключено до першого, другого та третього виходів пристрою відповідно [Phong Shading Reformulation for Hardware Renderer implification Apple Technical Report #43, Advanced Technology Group Apple Computer, Inc. August 2, 1993]. Недоліком пристрою є недостатня точність розрахунків при нормалізації векторів. В основу корисної моделі поставлено задачу створення пристрою для визначення нормалізації векторів у системах комп'ютерної графіки, у якому за рахунок введення нових блоків і зв'язків досягається підвищення точності обчислень. Поставлена задача вирішується тим, що пристрій для нормалізації векторів у системах комп'ютерної графіки, який містить перший÷сьомий блоки множення, перший÷третій суматори, вихід першого блока множення підключено до першого входу першого суматора, вихід другого блока множення підключено до другого входу першого суматора вихід третього блока множення підключено до третього входу першого суматора, вихід четвертого блока множення підключено до входу третього суматора, вихід п'ятого блока множення підключено до першого виходу пристрою, вихід шостого блока множення підключено до другого виходу пристрою, вихід сьомого блока множення підключено до третього виходу пристрою, введено восьмий блок множення, блок постійної пам'яті, перший÷третій регістри, інформаційний вхід першого регістра підключено до першого інформаційного входу пристрою, керуючий вхід підключено до першого керуючого входу пристрою, а вихід підключено до першого та другого входів першого блока множення та до другого входу п'ятого блока множення, інформаційний вхід другого регістра підключено до другого інформаційного входу пристрою, керуючий вхід підключено до другого керуючого входу пристрою, а вихід підключено до першого та другого входів другого блока множення та до другого входу шостого блока множення, інформаційний вхід третього регістра підключено до третього інформаційного входу пристрою, а вихід до першого та другого входів третього блока мно 63343 4 ження та до другого входу сьомого блока множення, перший вхід восьмого блока множення підключено до виходу першого суматора, а другий вхід до другого виходу блока постійної пам'яті, другий вхід четвертого блока множення підключено до виходу другого суматора, а перший вхід - до виходу першого суматора, другий вхід третього суматора підключено до третього виходу блока постійної пам'яті, а вихід підключено до перших входів п'ятого, шостого, сьомого блоків множення відповідно. На фіг. 1 зображено структурну схему пристрою; на фіг. 2 зображено активні рівні сигналів, які визначають початок та кінець процедури нормалізації вектора; на фіг. 3 зображено графіки максимальних відносних похибок нормалізації векторів для функцій прототипу (f(K)) та пристрою, що пропонується (h(K)). Пристрій для нормалізації вектора у системах комп'ютерної графіки (фіг. 1) включає перший÷третій регістри 1÷3 відповідно, перший÷третій 4÷6, четвертий 10, п'ятий÷сьомий 13÷15, восьмий 8 блоки множення відповідно, перший суматор 7, другий суматор 9, третій суматор 11, блок 12 постійної пам'яті, перший÷третій інформаційні входи 16÷18 пристрою відповідно, перший÷третій керуючі входи 19÷21 пристрою відповідно, перший÷третій інформаційні виходи 22÷24 пристрою відповідно, керуючий вихід 25 пристрою. Керуючий вхід першого регістра 1 підключено до першого керуючого входу 19 пристрою, а інформаційний вхід підключено до першого інформаційного входу 16. Керуючий вхід другого регістра 2 підключено до другого керуючого входу 20 пристрою, а інформаційний вхід підключено до другого інформаційного входу 17. Керуючий вхід третього регістра 3 підключено до третього керуючого входу 21 пристрою, а інформаційний вхід підключено до третього інформаційного входу 18. Перший, другий входи першого блока 4 множення підключено до виходу першого регістра 1 пристрою. Перший, другий входи другого блока 5 множення підключено до виходу другого регістра 2 пристрою. Перший, другий входи третього блока 6 множення підключено до виходу третього регістра 3 пристрою. Перший÷третій входи першого 7 суматора підключено до виходів блоків 4÷6 множення пристрою відповідно. Перший вхід восьмого блока 8 множення підключено до першого виходу блока 12 постійної пам'яті, а другий вхід - до виходу першого 7 суматора. Перший вхід другого 9 суматора підключено до виходу восьмого блока 8 множення, а другий вхід - до другого виходу блока 12 постійної пам'яті. Перший вхід четвертого блока 10 множення підключено до виходу першого 7 суматора. Перший вхід третього 11 суматора підключено до виходу четвертого блока 10 множення, а другий вхід - до третього виходу блока 12 постійної пам'яті. Перший вхід п'ятого блока 13 множення підключено до виходу першого 1 регістра, другий вхід підключено до виходу третього 11 суматора, а вихід є першим інформаційним виходом пристрою. Перший вхід шостого блока 14 множення підклю 5 63343 чено до виходу другого 2 регістра, а другий вхід до виходу третього 11 суматора, а вихід є другим інформаційним виходом пристрою. Перший вхід сьомого блока 15 множення підключено до виходу третього 3 регістра, а другий вхід - до виходу третього 11 суматора, а вихід є третім інформаційним виходом пристрою. Керуючий вихід 25 підключено до другого керуючого входу третього 3 регістра пристрою. Для використання векторів при формуванні реалістичних зображень необхідно виконати їх нормалізацію. Нормалізація вектора виконується за формулою: N0 x 2 y 2 z2 y x x 2 y 2 z2 i j z x 2 y 2 z2 , (1) k де x, y, z - ортогональні складові вектора. Для знаходження підкореневого виразу потрібно виконати три операції множення та дві операції додавання. Введемо позначення K 0 x 2 y2 z2 . У формулі (1) найбільш складними з точки зору апаратної реалізації є операції ділення та визначення квадратного кореня. Шляхом апроксима1 ції виразу поліномом Чебишова, отримуємо: K 1 K A K2 B K C , (2) де А = 0,822, В = -2,046, С = 2,227. Максимальна абсолютна похибка апроксимації Δмах поліномом Чебишова другого степеня не перевищує 0,0051, а максимальна відносна похибка δмах - 0,36 %. Використання апроксимаційної формули дозволяє при незначній похибці усунути трудомісткі операції ділення та визначення квадратного кореня з процедури нормалізації вектора, що суттєво зменшує обчислювальні витрати та складність апаратної реалізації. Запишемо формулу (2) у вигляді: 1 K ( A K B) K C (3). Пристрій працює наступним чином. Координата вектора х поступає на перший інформаційний вхід 16 пристрою та записується в перший регістр 1 активним рівнем сигналу на першому керуючому вході 19. На другий інформаційний вхід 17 пристрою поступає координата у та 6 записується в другий регістр 2 активним рівнем сигналу на другому керуючому вході 20. Значення координати z поступає на третій інформаційний вхід 18 пристрою і записується в третій регістр 3 активним рівнем сигналу на першому керуючому вході 21. Поява сигналу в регістрі 3 сигналізує про запис ортогональних складових вектора в перший÷третій відповідно 1÷3 регістри. Значення координати х подається на перший вхід першого 4 блока множення для піднесення відповідної координати до квадрату. Значення координати у подається на перший вхід другого блока 5 множенняпристрою, на виході якого формується значення 2 у . На перший вхід третього блока 6 множення подається значення координати z із формуванням 2 на його виході значення z . Для отримання зна2 2 2 чення x +y +z операнди із виходів першого÷третього 4÷6 блоків множення відповідно передаються на перший, другий, третій входи першого 7 суматора відповідно. Із виходу першого 7 сума2 2 2 тора значення підкореневого виразу х +у +z поступає на перший вхід восьмого блока 8 множення, на другий вхід якого передається значення коефіцієнта А із першого виходу блока 12 постійної пам'яті. Одержаний результат подається на перший вхід другого 9 суматора, на другий вхід якого поступає значення коефіцієнта В із другого виходу блока 12 постійної пам'яті. Одержане значення (А·K+В) передається на перший вхід четвертого блока 10 множення, на другий вхід якого поступає 2 2 2 значення x +y +z із виходу першого 7 суматора. Значення (А·K+В)·K передається на перший вхід третього 11 суматора, на другий вхід якого поступає значення коефіцієнта С із третього виходу блока 12 постійної пам'яті. Отриманий результат (А·K+В)·K+С передається на перші входи п'ятого+сьомого блоків 13÷15 множення відповідно і перемножуються із значеннями координат вектора x, y,z, що передаються із виходу першого÷третього 1÷3 регістрів відповідно. На першому÷третьому інформаційному виходах пристрою 22÷23 відповідно отримуємо значення x y z , , . 2 2 2 2 2 2 2 x y z x y z x y 2 z2 Задній фронт активного сигналу на керуючому виході 25 пристрою сигналізує про те, що на інформаційних виходах пристрою отримано достовірні дані, пристрій визначив нормалізований вектор та готовий до прийому нових операндів. У пристрої-прототипі при нормалізації векторів максимальна відносна похибка не перевищує 3 % (фіг. 3), а у запропонованому пристрої - не перевищує 0,36 % (фіг. 3). Таким чином, точність отриманих значень у порівнянні із пристроєм-прототипом у 8 разів більша, що свідчить про суттєве підвищення точності нормалізації векторів. 7 63343 8 9 Комп’ютерна верстка Л.Литвиненко 63343 Підписне 10 Тираж 23 прим. Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюVector normalization device in computer graphics systems

Автори англійськоюRomaniuk Oleksandr Nykyforovych, Romaniuk Oksana Volodymyrivna, Pavlyk Tetiana Mykolaivna

Назва патенту російськоюУстройство для нормализации векторов в системах компьютерной графики

Автори російськоюРоманюк Александр Никифорович, Романюк Оксна Владимировна, Павлик Татьяна Николаевна

МПК / Мітки

МПК: G06T 15/00

Мітки: векторів, комп'ютерної, графіки, нормалізації, пристрій, системах

Код посилання

<a href="https://ua.patents.su/5-63343-pristrijj-dlya-normalizaci-vektoriv-u-sistemakh-kompyuterno-grafiki.html" target="_blank" rel="follow" title="База патентів України">Пристрій для нормалізації векторів у системах комп’ютерної графіки</a>

Попередній патент: Двонаправлений відбивач струму

Наступний патент: Спосіб сегментації медичних ультразвукових зображень

Випадковий патент: Лотовий рівнемір