Комп’ютерна система безперервної діагностики ходових частин швидкісного рухомого складу залізниць

Номер патенту: 67530

Опубліковано: 15.06.2004

Автори: Стасюк Ілона Олександрівна, Кельріх Михайло Борисович, Семенова Наталія Володимирівна, Ковзель Микола Олегович, Зубко Арлікін Петрович, Сергієнко Микола Іванович, Остапюк Борис Ярославович, Шпеко Микола Іванович

Формула / Реферат

1. Комп'ютерна система безперервної діагностики ходових частин швидкісного рухомого складу залізниць, що включає блок гальванічної розв'язки, регістри, дешифратор, яка відрізняється тим, що її доповнено модемами, персональним комп'ютером та мікропроцесорними системами первинної обробки діагностичної інформації, кожний із яких включає мікропроцесор, два дешифратори, оперативний запам'ятовуючий пристрій, чотирипортовий модуль, мікропроцесорний модуль читання діагностичної інформації, причому вихід шини старших і молодших розрядів першого порту мікропроцесора підключений відповідно до входу першого і другого дешифраторів, вихід шини даних другого порту мікропроцесора з'єднаний із входами регістра, оперативного запам'ятовуючого пристрою та чотирипортового модуля, управляючі входи яких підключені до відповідних виходів третього дешифратора, підключеного своїм входом до виходу шини адреси третього порту мікропроцесора, шини запису і читання якого з'єднані із входами запису і читання оперативного запам'ятовуючого пристрою і чотирипортового модуля, мікропроцесорні модулі читання діагностичної інформації виконані в вигляді матриці (nxm), управляючі входи кожного jго стовпця (j=1,2,...m) яких об'єднані і підключені до jго виxoдy першого дешифратора, входи послідовного порту кожного іго рядка матриці мікропроцесорних модулів читання діагностичної інформації підключені через ій блок гальванічної розв'язки до іго виходу другого дешифратора, стробуючий вхід якого з'єднаний з виходом послідовного порту мікропроцесора, виходи мікропроцесорних модулів читання діагностичної інформації кожного jго стовпця підключені через jй блок гальванічної розв'язки до входу послідовного порту мікропроцесора, вхід персонального комп'ютера підключений через модеми до першого виходу чотирипортового модуля центральної мікропроцесорної системи первинної обробки діагностичної інформації, а попередні і наступні мікропроцесорні системи первинної обробки діагностичної інформації з'єднані послідовно через відповідні виходи чотирипортових модулів і підключені до відповідних виходів чотирипортового модуля центральної мікропроцесорної системи первинної обробки діагностичної інформації.

2. Комп'ютерна система безперервної діагностики ходових частин швидкісного рухомого складу залізниць за п. 1, яка відрізняється тим, що мікропроцесорний модуль читання діагностичної інформації містить три дешифратори, мікропроцесор, аналого-цифровий перетворювач, оперативний запам'ятовуючий пристрій, регістр, ключ, комутатори аналогових сигналів і перетворювачі аналогових сигналів, причому вихід шини старших і молодших розрядів першого порту мікропроцесора підключений відповідно до входів першого і другого дешифраторів, стробуючі входи яких об'єднані і підключені до стробуючого виходу мікропроцесора, вхід послідовного порту якого підключений до виходу ключа, перший та другий входи якого підключені відповідно до шини входу послідовного порту і управляючого входу мікропроцесорного модуля читання діагностичної інформації, вихід послідовного порту якого підключений до виходу послідовного порту мікропроцесора, комутатори аналогових сигналів виконані у вигляді матриці (PXF), перші управляючі входи кожного sго (s=1,2,...p) стовпця якої підключені до (PXF) sго виходу першого дешифратора, другі управляючі входи комутаторів аналогових сигналів кожного его рядка матриці підключені до его (е=1,2,...F) виходу другого дешифратора, інформаційний вхід кожного комутатора аналогового сигналу підключений до відповідного входу мікропроцесорного модуля читання діагностичної інформації, вихід комутатора аналогового сигналу кожного его рядка матриці підключений через ей перетворювач аналогових сигналів до его входу аналого-цифрового перетворювача, шини запису і читання якого підключені відповідно до шин запису і читання регістра, оперативного запам'ятовуючого пристрою і мікропроцесора, а вихід шини адреси другого порту мікропроцесора підключений до входу адреси оперативного запам'ятовуючого пристрою і третього дешифратора, виходи якого з'єднані з відповідними управляючими входами аналого-цифрового перетворювача, регістра і оперативного запам'ятовуючого пристрою, входи шин даних яких об'єднані і підключені до виходу шини даних третього порту мікропроцесора.

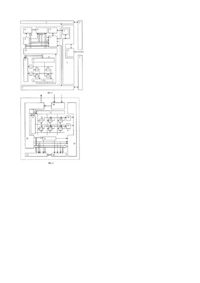

Текст

Винахід належить до обчислювальної та вимірювальної техніки і може бути використаний для безперервної діагностики і прогнозу технічного стану ходових частин швидкісних потягів. Відомий пристрій [1] який виконує функції збору, перетворення та передачі інформації параметрів фізичною середовищу, що включає датчики, формувачі інформації, аналого-цифрові перетворювачі, блоки дешифрації, запам'ятовуючій пристрій, електронну обчислювальну машину і блок регістрів управляючі входи яких підключені до відповідних входів формувачів інформації, а вихід аналого-цифрового перетворювача підключений до входу запам'ятовуючого пристрою. Недоліками відомого пристрою є обмежені функціональні можливості в зв'язку з тим, що у відомому пристрої проводиться тільки реєстрація параметрів фізичного середовища, а не виконуються функції діагностики контролюємого фізичного середовища і як недолік не проводиться прогноз його технічного стану. Відомий пристрій [2] виконуючий функції автономного запису та читання інформації, що включає центральний процесор, комутаційний модуль, датчики: і автономний запам'ятовуючий пристрій підключений до виходу відповідного датчика, а центральний процесор з'єднаний через комутаційний модуль з виходом автономного запам'ятовуючого пристрою. Недоліком відомого пристрою є обмежені функціональні можливості в зв'язку з тим, що в ньому виконується тільки інформаційно-вимірювальні функції шляхом перетворення вимірюваної величини в послідовність імпульсів, кількість яких пропорційна вимірювальній величині, які накопичуються в запам'ятовуючому пристрої і дані поступають в центральний процесор і зовсім: не виконуються функції діагностики об'єкта вимірювання. Найбільш близьким за своєю технічною суттєвістю є інформаційно-вимірювальна система [3], яка включає аналого-цифровий перетворювач, регістри, блок гальванічної розв'язки і електронному обчислювальну машину, причому вихід аналогово-цифрового перетворювача з'єднаний з інформаційними входами першого та другого регістрів, а інформаційний вихід електронної обчислювальної машини підключений до інформаційного входу дешифратора. Недоліком даного пристрою є обмежені функціональні можливості в зв'язку з тим, що відомим пристроєм не можливо виконувати безперервну діагностику ходових частин включаючи і колісні пари в процесі руху швидкісних потягів, а також не можливо реалізувати прогноз технічного стану. В основу винаходу поставлена задача розширення функціональних можливостей завдяки спроможності виконання з єдиних інформаційних позицій безперервної діагностики і прогнозу те хнічного стану ходових частин включаючи і колесні пари в процесі руху швидкісних потягів, реєстрації аварійних режимів і як наслідок підвищення безпеки руху потягів завдяки можливості виключення аварійних ситуацій. Поставлена мета досягається шляхом включення до комп'ютерної системи безперервної діагностики ходових частин швидкісного рухомого складу залізниць модемів, персонального комп'ютера, та мікропроцесорної системи первинної обробки діагностичної інформації кожна із яких включає оперативний запам'ятовуючий пристрій, чотирьох портовий модуль, мікропроцесорний модуль читання діагностичної інформації причому вихід шини старших і молодших розрядів першого порту мікропроцесора підключений відповідно до входу першого і другого дешифраторів, ви хід шини даних другого порту мікропроцесора з'єднаний зі входами регістра, оперативного запам'ятовуючого пристрою та чотирьохпортового модуля управляючі входи яких підключені до відповідних виходів третього дешифратора підключеного своїм входом до виходу шини адреси третього порту мікропроцесора шини запису і читання якого з'єднані зі - входами запису і читання оперативного запам'ятовуючого пристрою і чотирьохпортового модуля, мікропроцесорні модулі читання діагностичної інформації виконані в вигляді матриці (nxm) управляючі входи кожного jго стовпця (j=1, 2, ... m) якої об'єднані і підключені до jго виходy першого дешифратора, входи послідовного порту кожної jї строчки матриці мікропроцесорних модулів читання діагностичної інформації підключені через і й блок (і=1, 2, ..., n) гальванічної розв'язки до і го виходу другого дешифратора стробуючий вхід якого з'єднаний з виходом послідовного порта мікропроцесора, виходи мікропроцесорних модулів читання діагностичної інформації кожного jго стовбця підключені через jй блок гальванічної розв'язки до входу послідовного порту мікропроцесора, вхід персонального комп'ютера підключений через модеми до першого виходу чотирьохпортового модуля центральної мікропроцесорної системи первинної обробки діагностичної інформації, а попередні і наступні мікропроцесорні системи первинної обробки діагностичної інформації з'єднані послідовно через відповідні виходи чотирьохпортових модулів і підключені до відповідних входів чотирьохпортового модуля центральної мікропроцесорної системи первинної обробки діагностичної інформації, причому мікропроцесорний модуль читання діагностичної інформації містить три дешифратори, мікропроцесор, аналогово-цифровий перетворювач, оперативний запам'ятовуючий пристрій, регістр, ключ, комутатори аналогових сигналів і перетворювачі аналогових сигналів, причому вихід шини старших і молодших розрядів першого порту мікропропроцесора підключений відповідно до входу першого і другого дешифраторів стробуючі входи: яких об'єднані і підключені до стробуючого виходу мікропроцесора, вхід послідовного порту якого підключений до виходу ключа, перший та др угий входи якого підключені відповідно до шини входу послідовного порту і управляючого входу мікропроцесорного модуля читання діагностичної інформації вихід послідовного порту якого підключений до виходу послідовного порту мікропроцесора, комутатори аналогових сигналів виконані у вигляді матриці (FXP) перші управляючі входи кожного s го (s=1, 2,…p) стовпця якої підключені до s го виходу першого дешифратора, другі управляючі входи комутатора аналогових сигналів кожної еї строчки матриці підключені до eго (e=1, 2, … F) другого дешифратора, інформаційний вхід кожного комутатора аналогового сигналу підключений до відповідного входу мікропроцесорного модуля читання діагностичної інформації, вихід комутатора аналогового сигналу кожної єї строчки матриці підключений через е й перетворювач аналогових сигналів до е го входу аналого-цифрового перетворювача шини запису і читання якого підключені відповідно до шин запису і читання регістра, оперативного запам'ятовуючого пристрою і мікропроцесора, а вихід шини адреси другого порту мікропроцесора підключений до входу адреси оперативного запам'ятовуючого пристрою і третього дешифратора виходи якого з'єднані з відповідними управляючими входами аналого-цифрового перетворювача, регістра і оперативного запам'ятовуючого пристрою входи шин даних яких об'єднані і підключені до виходу шини даних третього порту мікропроцесора. Завдяки введенню персонального комп'ютера, модемів і мікропроцесорних систем первинної обробки діагностичної інформації їх матричних організацій архітектури і введенню нових зв'язків між ними, комп'ютерна система безперервної діагностики ходових частин швидкісного рухомого складу залізниць забезпечує значне розширення функціональних можливостей завдяки новій можливості виконання з єдиних інформаційних позицій безперервної діагностики і прогнозу технічного стану ходових частин включаючи і колісні пари в процесі руху швидкісного потяга, реєстрації аварійних режимів з прив'язкою до часу і можливості передачі інформації на всі рівні управління залізницею. Крім того значно покращується безпека руху потягів завдяки можливості передбачення і виключення можливої аварійної ситуації. Значно поліпшились також експлуатаційні показники комп'ютерної системи завдяки однорідній матричній організації і можливості її тестування в процесі роботи. На фіг.1 наведено структурну схему комп'ютерної схеми безперервної - діагностики ходових частин швидкісного рухомого складу залізниць, на фіг.2 наведено структурну схему мікропроцесорної системи первинної обробки діагностичної інформації, на фіг.3 наведено блок-схему алгоритму роботи комп'ютерної системи безперервної діагностики ходових частин швидкісного рухомого складу залізниць, на фіг.4 наведено блок-схему алгоритму роботи мікропроцесорної системи первинної обробки діагностичної інформації. Комп'ютерна схема безперервної діагностики ходових частин швидкісного рухомого складу залізниць (фіг.1) включає: персональний комп'ютер 1, мікропроцесорні системи первинної обробки діагностичної інформації 2, дешифратори 3, блоки гальванічної розв'язки 4, модеми 5, регістр 6, чотирьохпортовий модуль 7, оперативний запам'ятовуючий пристрій 8, мікропроцесорні модулі читання діагностичної інформації 9, мікропроцесор 10. Вихід шини старших і молодших розрядів першого мікропроцесора 10 підключений відповідно до входу першого і другого де шифраторів 3.Ви хід шини даних друго го порту мікропроцесора 10 з'єднаний зі входами регістра 6, оперативного запам'ятовуючого пристрою 8 та чотирьохпортового модуля 7, управляючі входи яких підключені до відповідних виходів третього дешифратора 3 підключеного своїм входом до виходу шини адреси третього порту мікропроцесора 10 шини запису і читання якого з'єднані зі входами запису і читання оперативного запам'ятовуючого пристрою 8 і чотирьохпортового модуля 7. Мікропроцесорні модулі читання діагностичної інформації 9 виконані у вигляді матриці (nxm) (для випадку n=2, m=2). Управляючі входи кожного j-того (j=1, 2, ... m) стовпця матриці мікропроцесорних модулів читання діагностичної інформації 9 об'єднані і підключені до j-того виходу першого деши фратора 3. Входи послідовного порту кожної і-тої строчки матриці мікропроцесорних модулів читання діагностичної інформації 9 підключені через і-тий блок гальванічної розв'язки 4 до і-того виходу другого деши фратора 3 стробуючий вхід якого з'єднаний з виходами послідовного порту мікропроцесора 10. Виходи мікропроцесорних модулів читання діагностичної інформації 9 кожного j-того стовпця матриці .підключені через j-тий блок гальванічної розв'язки 4 до виходу послідовного порту мікропроцесора 10. Вхід персонального комп'ютера 1 підключений через модем 5 до першого виходу чотирьохпортового модуля 7 центральної мікропроцесорної системи первинної обробки діагностичної інформації 2. Попередні і наступні мікропроцесорні системи первинної обробки діагностичної інформації 2 з'єднані послідовно через відповідні виходи чотирьохпортових модулів 7 і підключені до відповідних входів чотирьохпортового модуля 7 центральної мікропроцесорної системи первинної обробки діагностичної інформації 2. Кожний мікропроцесорний модуль читання діагностичної інформації 9 (фіг.2) включає три дешифратори 11, мікропроцесор 12, аналого-цифровий перетворювач 13, оперативний запам'ятовуючий пристрій 14, регістр 15, ключ: 16, комутатори аналогових сигналів 17 і перетворювачі аналогових сигналів 18. Вихід шини старши х і молодших розрядів першого порту мікропроцесора 12 підключені відповідно до входів першого і другого дешифраторів 11 стробуючі входи яких об'єднані і підключені до стробуючого виходу мікропроцесора 12. Вихід послідовного порту мікропроцесора 12 підключений до входу ключа 16 перший та другий входи якого підключені відповідно до шини входу послідовного порту і управляючого входу мікропроцесорного модуля читання діагностичної інформації 9 вихід послідовного порту якого підключений до виходу послідовного порту мікропроцесора 12. Комутатори аналогових сигналів 17 виконані у вигляді матриці (FXP) перші управляючі входи кожного Sого (S=1, 2,…,P) стовпця якої підключені до Sого виходу першого дешифратора 11. Другі управляючі входи комутаторів аналогових сигналів 17 кожної 1ї строчки матриці підключені до 1ого виходу (1=1,2,..., F) другого дешифратора 11. Інформаційний вхід кожного комутатора аналогових сигналів 17 підключений до відповідного входу мікропроцесорного модуля читання діагностичної інформації 9. Вихід комутатора аналогового сигналу 17 кожної 1ї строчки матриці підключений через 1й перетворювач аналогових сигналів 18 до 1ого входу аналогово-цифрового перетворювача 13 тини запису і читання якого підключені відповідно до шини запису і читання регістра 15, оперативного запам'ятовуючого пристрою 14 і мікропроцесора 12. Вихід шини адреси другого порту мікропроцесора підключений до входу адреси оперативного запам'ятовуючого пристрою 14 і третього дешифратора 11 виходу якого з'єднані з відповідними управляючими входами аналогово-цифрового перетворювача 13, регістра 15 і оперативного запам'ятовуючого пристрою 14 входи шин даних яких об'єднані і підключені до виходу шини даних третього порту мікропроцесора 12. Мікропроцесор 10 (фіг.1) і мікропроцесор 12 (фіг.2) виконані, наприклад, у вигляді однокристального мікропроцесора типу KM 1816 ВЕ51. Чотирьох портовий модуль 7 (фіг.1) виконаний, наприклад, у вигляді інтегральної схеми типу ST16C554DCF. Блоки гальванічної розв'язки 4 (фіг.1) виконані, наприклад, у вигляді оптронів типу АОТ1285. Робота комп'ютерної системи безперервної діагностики ходових частин швидкісного рухомого складу залізниць (фіг.1) проводиться у послідовності з блок-схемою алгоритму роботи (фіг.3). Мікропроцесорна система первинної обробки діагностичної інформації 2 (фіг.2) проводиться у послідовності з блок-схемою алгоритму роботи (фіг.4). Після запуску комп'ютерної системи вона працює постійно в реальному часі. При цьому згідноалгоритмів (фіг.2, фіг.3) запускається в роботу мікропроцесорні системи первинної обробки діагностичної інформації 2 і мікропроцесорні модулі читання діагностичної інформації 9. Згідно алгоритму (фіг.3) мікропроцесором 12 визначається режим робіт чи інсталяції мікропроцесорного модуля читання діагностичної інформації 9. Якщо робота, то мікропроцесором 12 видається серія управляючих сигналів завдяки яким дешифраторами 11 послідовно підключаються датчики первинної інформації, яка через комутатори аналогових сигналів 11 поступає через відповідний перетворювач аналогових сигналів 18 на вхід аналогового-цифрового перетворювача 13, де вона перетворюється в цифровий еквівалент і далі записується в оперативний запам'ятовуючий пристрій. Після читання діагностичної інформації відповідно алгоритму (фіг.4) мікропроцесором 12 обчислюються такі параметри як прискорення кузова вагона, частоти коливань ресорної підвіски, рівень вібрації, прискорення колісних пар, та інші. Після обчислення ряду параметрів визначається можливість аварійного режиму. Якщо аварійного режиму немає, то мікропроцесором; 12 формується запит в мікропроцесорну систему первинної обробки інформації 2 і дальше транзитом в персональний комп'ютер 1 на предмет обміну даними. В тому випадку коли з верхнього рівня управління був запит на обмін даними, то мікропроцесор 12 згідно алгоритму (фіг.4) формує і передає блок необхідних даних. Після чого, а також в тому випадку, коли запиту на облік даними не було мікропроцесор 12 на основі прочитаної діагностичної інформації визначає рівень технічного стану ходових частин швидкісного рухомого складу. Якщо технічний стан задовільний, то процес повторюється, тобто проводиться чергове читання із датчиків діагностичних даних та їх обробка. У випадку коли технічний стан не задовільний то мікропроцесор 12 формує і передає файл технічного стану ходових частин на верхній рівень управління і аналізується ситуація на предмет зупинки чи можливості продовження функціонування. Якщо необхідно зупинити потяг, то проводиться процедура виключення і робота комп'ютерної системи закінчується. У випадку, коли після читання первинних даних з'ясовується, що деякі парад/гетри виходять за норму, тобто аварійний режим, то мікропроцесор 12 перериває свою роботу, формує і передає відомості і файл аварійної інформації на верхні рівні управління. Після чого аналогічно вище описаному проводиться аналіз на предмет зупинки чи продовження роботи. Якщо після запуску комп'ютерної системи, необхідно її інсталювати, то із персонального комп'ютера 1 передається файл інсталяції завдяки якому мікропроцесорна система первинної обробки діагностичної інформації 2 і мікропроцесорний модуль читання діагностичної інформації програмується на необхідний режим роботи і вона запускається в роботу. В тім випадку коли після запуску комп'ютерної системи необхідно провести її тестування, то з верхнього рівня управління, тобто із персонального комп'ютера 1 передається файл тестової програми завдяки якому проводиться тестування мікропроцесорної системи первинної обробки діагностичної інформації 2 і мікропроцесорного модуля читання діагностичної інформації 9. Якщо тест виконується, то проводиться процедура після тестового контролю і система, запускається в роботу. В тім випадку коли тест не виконується, то формується і передається інформація про несправність системи на верхній рівень управління і комп'ютерна система в роботу не запускається. Робота мікропроцесорної системи первинної обробки діагностичної інформації 2 (фіг.1) проводиться згідно алгоритму (фіг.3). Після запуску комп'ютерної системи мікропроцесор 10 приймає від комп'ютера 1 файл запуску й запускає систему в роботу. Після цього мікропроцесором 10 формується запит на обмін діагностичною інформацією з мікропроцесорними модулями читання діагностичної інформації 9. Після цього мікропроцесором 10 приймається блок діагностичних даних, на базі яких вичислюються такі показники як визначення рівня плавності ходу вагона, рівня комфортності, величину надійності ходових частин, реалізується визначення прогнозу технічного стану та інші. Коли всі параметри визначені, то мікропроцесором 10 реалізується вивід про технічний стан вагона. Якщо технічний стан не задовільний, то проводиться більш детальна обробка аварійного режиму, і видається файл аварійних даних на верхній рівень управління. Після цього мікропроцесором 10 проводиться аналіз на предмет зупинки, чи можливості проведення руху. В тім випадку коли технічний стан задовільний, то мікропроцесором 10 проводиться аналіз на предмет чи був аварійний запит від мікропроцесорного модуля читання діагностичної інформації 9. Якщо був то реалізується прийом файлу аварійних даних, його обробка і передача на верхній рівень управління і аналізується необхідність зупинки. У випадку, коли в зупинці, не має потреби, то комп'ютерна система аналогічна вищеописаному автоматично записується на новий цикл роботи. Завдяки введенню нових елементів та зв'язків між ними запропонована комп'ютерна система безперервної діагностики ходових частин швидкісного рухомого складу залізниць вигідно відрізняється від прототипу. На відміну від прототипу, в якому звужені функціональні можливості, тому що ним неможливо виконувати безперервну діагностику ходови х часта швидкісного руху потягів включаючи колісні пари, а також неможливо визначити прогноз технічного стану у запропонованій комп'ютерній системі завдяки введенню таких елементів як мікропроцесорні системи первинної обробки діагностичної інформації і мікропроцесорних модулів читання діагностичної інформації, а також нових зв'язків між ними, з'я вилась можливість виконувати з єдиних інформаційних позицій безперервну діагностику і прогноз технічного стану ходових частин в процесі руху швидкісних потягів, реєстрації нормативних і аварійних режимів і як наслідок підвищити рівень безпеки руху потягів. Крім того, в запропонованій системі завдяки збільшенню ступеня однорідності з'явилась можливість вести в процесі роботи настройку системи і тестовий контроль, покращити такі експлуатаційні характеристики як живучість, надійність, пошук та ремонт пошкоджень і т.п. ЛІТЕРАТУРА 1. Устройство сбора, преобразования и передачи результатов измерения параметров физической среды. G06F17/40/ Патент РО №2079882, БИ №14, 20.05.97г. 2. United States Patent 5270704 "Autonomus Pulse Reading and Recording System" Dec. 14, 1993, G01D4/00. 3. Інформаційно-вимірювальна система. G06F15/20, патент України №16876. Промислова власність, Офіційний бюлетень №4, 1997р. (прототип).

ДивитисяДодаткова інформація

Назва патенту англійськоюComputerized system for continuously monitoring the running equipment of a high-speed train

Автори англійськоюSerhiienko Mykola Ivanovych, Zubko Arlikin Petrovych

Назва патенту російськоюКомпьютерная система для непрерывного контроля ходовой части скоростного поезда

Автори російськоюСергиенко Николай Иванович, Зубко Арликин Петрович

МПК / Мітки

МПК: G06F 17/40, G06F 17/20

Мітки: діагностики, ходових, система, частин, складу, безперервної, комп'ютерна, швидкісного, рухомого, залізниць

Код посилання

<a href="https://ua.patents.su/5-67530-kompyuterna-sistema-bezperervno-diagnostiki-khodovikh-chastin-shvidkisnogo-rukhomogo-skladu-zaliznic.html" target="_blank" rel="follow" title="База патентів України">Комп’ютерна система безперервної діагностики ходових частин швидкісного рухомого складу залізниць</a>

Попередній патент: Спосіб хірургічного лікування вузлового зоба

Наступний патент: Механізм для очистки внутрішньої поверхні котла цистерни

Випадковий патент: Пристрій для руйнування шкаралупи горіхів