Завадостійкий цифровий фазовий детектор

Номер патенту: 68130

Опубліковано: 12.03.2012

Автори: Бойко Денис Олександрович, Альошин Геннадій Васильович, Приходько Сергій Іванович

Формула / Реферат

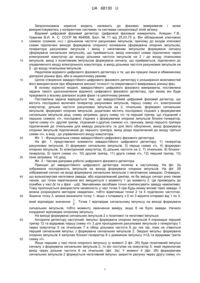

Завадостійкий цифровий фазовий детектор, що містить генератор рахункових імпульсів, першу схему "І", електронний комутатор, дільник частоти рахункових імпульсів на 2, лічильник імпульсів, формувач сигнальних імпульсів, формувач опорних імпульсів, який відрізняється тим, що він додатково містить послідовно з'єднані з формувачем сигнальних імпульсів діод, схему затримки, другу схему "І" та перший тригер, що з'єднаний з першою схемою "І", послідовно з'єднані з формувачем опорних імпульсів блокінг-генератор, третю схему "І", другий тригер, з'єднаний з другою схемою "І", причому вихід першого тригера підключений до лічильника для виводу результату та для його обнулення, вихід формувача опорних імпульсів підключений до першого тригера, вихід діода підключений до входу третьої схеми "І", а вхід - до управляючого входу комутатора.

Текст

Реферат: UA 68130 U UA 68130 U 5 10 15 20 25 30 35 40 45 Запропонована корисна модель належить до фазових вимірювачів і може використовуватись у когерентних системах та системах синхронізації ліній зв'язку. Відомий цифровий фазовий детектор: Цифровой фазовый измеритель. Алешин Г.В., Урвачев В.И. А. С. СССР № 464858, Бюл. № 11 від 25.03.75 р. Він обладнаний ключовою схемою (схемою «І») і дільником частоти рахункових імпульсів, причому до входів ключової схеми підключені виходи формувача опорного коливання (формувача опорних імпульсів), генератора рахункових імпульсів і вихід з негативним імпульсом формувача сигналу (формувача сигнальних імпульсів), що приймається, вихід ключової схеми підключено через електронний комутатор до входу дільника частоти імпульсів на 2 і до входу лічильника імпульсів, вихід з позитивним імпульсом формувача сигналу, що приймається, підключено до управляючого входу електронного комутатора, а вихід дільника частоти рахункових імпульсів на 2 - до входу лічильника імпульсів. Недоліком відомого цифрового фазового детектору є те, що він працює лише в обмеженому діапазоні різниці фаз, або в нециклічному режимі. Ціллю створення завадостійкого цифрового фазового детектору є розширення можливостей його використання при збереженні високої точності та оперативності вимірювань різниці фаз. В основу корисної моделі, завадостійкого цифрового фазового вимірювача, поставлена задача такого удосконалення відомого цифрового фазового детектору, при якому він буде працювати у всьому діапазоні зсувів фази і в циклічному режимі. Поставлена задача вирішується тим, що завадостійкий цифровий фазовий детектор, що містить послідовно включені генератор рахункових імпульсів, першу схему «І», електронний комутатор, дільник частоти рахункових імпульсів на 2, лічильник, формувач сигнальних імпульсів, формувач опорних імпульсів, додатково містить послідовно з'єднані з формувачем сигнальних імпульсів діод, схему затримки, другу схему «І» та перший тригер, що з'єднаний з першою схемою «І», послідовно з'єднані з формувачем опорних імпульсів блокінг-генератор, третю схему «І», другий тригер, з'єднаний з другою схемою «І», причому, вихід першого тригера підключений до лічильника для виводу результату та для його обнулення, вихід формувача опорних імпульсів підключений до першого тригера, вихід діода підключений до входу третьої схеми «І», а вхід - до управляючого входу комутатора. Фіг. 1 - Функціональна схема завадостійкого цифрового фазового детектора. На фіг. 1 представлені елементи завадостійкого цифрового детектору: 1) генератор рахункових імпульсів, 2) формувач сигнальних імпульсів, 3) перша схема «І», 4) формувач опорних імпульсів, 5) електронний комутатор, 6) дільник частоти на 2, 7) лічильник, 8) блокінггенератор, 9) третя схема «І», 10) другий тригер, 11) друга схема «І», 12) перший тригер, 13) лінія затримки, 14) діод. Фіг. 2 - Часова діаграма роботи цифрового фазового детектора. Принцип дії завадостійкого цифрового детектора полягає в наступному. На фіг. 2а зображена послідовність імпульсів на виході формувача опорних імпульсів. На фіг. 2б зображений сигнал на вході формувача сигнальних імпульсів з негативною завадою. Очевидно, що вузькосмугова негативна завада, або кодозалежний джитер, як би зміщує сигнал униз таким чином, що точки перетинання вісі зміщуються з моменту 1 до моменту 2. Це призводить до похибки у часі Δt та у фазі - ωΔt. Звичайними засобами точно компенсувати заваду неможливо. Тому пропонується використати незмінність у часі точки 3 при будь-якому впливі такої завади. її можна розрахувати методом «виделки», тобто відмітивши точки 2 та 4 поділеною частотою. Знаючи точку 3, можна визначити точку 1, якщо з інтервалу з 0 по 3 відняти інтервал від 1 по 3, який відповідає значенню 50 55 . Точка 1 відповідає сигнальному імпульсу на виході формувача 2 сигнальних імпульсів, тобто моменту закінчення виміру, якщо б не було завади. Начало координат відповідає опорному імпульсу. На виході формувача сигнальних імпульсів 2 є позитивні та негативні імпульси. Алгоритм детектору наступний. Імпульс формувача опорних імпульсів 4 опрокидує перший тригер 12 та відкриває першу схему «І» 3 для проходження рахункових імпульсів з генератору 1 через комутатор 5 на лічильник 7 в обхід дільника частоти 6 до тих пір, поки не з'явиться перший сигнальний імпульс з формувача сигнальних імпульсів 2. Заодно імпульс формувача опорних імпульсів 4 запускає блокінг-генератор 8 з довжиною імпульсу π+Δ та відкриває третю схему «І». Якщо першим у часі після опорного імпульсу (у момент 2 фіг. 2б) буде позитивний імпульс сигналу з формувача сигнальних імпульсів 2, то він поступає на комутатор 5, який переключає вихід через дільник частоти 6 на лічильник (фіг. 2в). У момент 4 (фіг. 2б) формувачем сигнальних імпульсів 2 формується негативний імпульс закриття рахунку через другу схему «І» 1 UA 68130 U 11. Оскільки частота рахунку імпульсів удвічі менша, у лічильнику 7 накопичувалось число імпульсів відповідне інтервалу від 0 до 3. Якщо з числа, відповідного інтервалу від 0 по 3 відняти 5 10 15 Тобто, якби не було завад. Якщо першим у часі після опорного імпульсу буде негативний імпульс, то схема спрацьовує таким чином. Наприклад, опорний імпульс буде у момент 3 (фіг. 2б). Негативний імпульс від формувача сигнальних імпульсів 2 через відкриту на час +Δ третю схему «І» 9 опрокидує другий тригер 10, що закриває другу схему «І» 11. Тому затриманий лінією затримки 13 негативний імпульс не проходить до першого тригера 12 та не закриває рахування рахункових імпульсів першою схемою «І» 3. Рахування лічильником 7 продовжується у такому ж алгоритмі, поки не прийде другий негативний сигнальний імпульс. Другий негативний імпульс з формувача сигнальних імпульсів 2 проходить через діод 14, лінію затримки 13 і через другу схему «І» 11 для закриття рахування на перший тригер 12, тому що з виходу діода трохи раніше цей імпульс пройшов через третю схему «1» 9, опрокинув удруге другий тригер 10, який відкрив другу схему «І» 11. Затримка на один-два періоду рахункових імпульсів не заважає вимірюванням, тому що з лічильника знімається результат без молодшого розряду. Параметр Δ вибирається з формули: sin 20 25 30 , то у лічильнику зостанеться число імпульсів відповідне інтервалу від 0 по моменту 1. 2 1 , де q - відношення сигнал/завада. q ФОРМУЛА КОРИСНОЇ МОДЕЛІ Завадостійкий цифровий фазовий детектор, що містить генератор рахункових імпульсів, першу схему "І", електронний комутатор, дільник частоти рахункових імпульсів на 2, лічильник імпульсів, формувач сигнальних імпульсів, формувач опорних імпульсів, який відрізняється тим, що він додатково містить послідовно з'єднані з формувачем сигнальних імпульсів діод, схему затримки, другу схему "І" та перший тригер, що з'єднаний з першою схемою "І", послідовно з'єднані з формувачем опорних імпульсів блокінг-генератор, третю схему "І", другий тригер, з'єднаний з другою схемою "І", причому вихід першого тригера підключений до лічильника для виводу результату та для його обнулення, вихід формувача опорних імпульсів підключений до першого тригера, вихід діода підключений до входу третьої схеми "І", а вхід - до управляючого входу комутатора. 2 UA 68130 U Комп’ютерна верстка В. Мацело Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 3

ДивитисяДодаткова інформація

Назва патенту англійськоюNoise-immune digital phase detector

Автори англійськоюAlioshyn Hennadii Vasyliovych, Boiko Denys Oleksandrovych, Prykhodko Serhii Ivanovych

Назва патенту російськоюПомехоустойчивый цифровой фазовый детектор

Автори російськоюАлёшин Геннадий Васильевич, Бойко Денис Александрович, Приходько Сергей Иванович

МПК / Мітки

МПК: H03D 3/00

Мітки: фазовий, цифровий, детектор, завадостійкий

Код посилання

<a href="https://ua.patents.su/5-68130-zavadostijjkijj-cifrovijj-fazovijj-detektor.html" target="_blank" rel="follow" title="База патентів України">Завадостійкий цифровий фазовий детектор</a>

Попередній патент: Глибоководний автономний піднімальний пристрій

Наступний патент: Електронна система пожежно-охоронної сигналізації

Випадковий патент: Спосіб комутації відеосигналів у пристроях охоронного телебачення