Завадостійкий цифровий фазовий детектор

Номер патенту: 79773

Опубліковано: 25.04.2013

Автори: Індик Сергій Володимирович, Альошин Геннадій Васильович, Приходько Сергій Іванович

Формула / Реферат

Завадостійкий цифровий фазовий детектор, що містить послідовно включені генератор рахункових імпульсів, першу схему "І", електронний комутатор, дільник надвоє частоти рахункових імпульсів, лічильник, формувач сигнальних імпульсів, послідовно з'єднаний з діодом, схемою затримки, другою схемою "І" та з першим тригером, вихід формувача опорних імпульсів через перший тригер, з'єднаний зі входом першої схеми "І" і послідовно з'єднаний з блокінг-генератором, третьою схемою "І", другим тригером і другою схемою "І", вихід формувача сигнальних імпульсів підключений до управляючого входу комутатора, а вихід діода підключений до третьої схеми "І", причому вихід першого тригера підключений до лічильника для виводу результату та для його обнуління, який відрізняється тим, що для усунення затримки фази, впливаючої на точність обчислень, спрощення аппаратури та підвищення надійності її роботи, він додатково вміщує другий діод, підключений від виходу формувача сигнальних імпульсів до входу комутатора, замість блокінг-генератора підключений третій тригер входом до виходу формувача опорних імпульсів і виходом - до входу третьої схеми "I", усувається схема затримки таким чином, щоб був з'єднаний вихід першого діода зі входом другої схеми "І", для обнуління лічильника та тригерів використовується імпульс з виходу другої схеми "І".

Текст

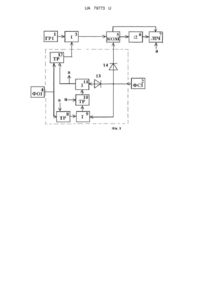

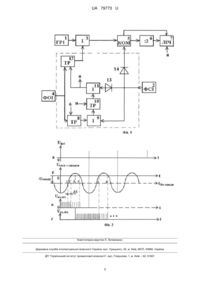

Реферат: UA 79773 U UA 79773 U 5 10 15 20 25 30 35 40 45 50 55 60 Завадостійкий цифровий фазовий детектор належить до фазових вимірювачів, який здатний усунути вплив корельованих завад та кодозалежного джитеру на точність фазових вимірювань або скоротити час вимірювань фази і входження у синхронізм, і може використовуватись в когерентних системах та системах синхронізації. Розширюються межі застосування та функціональні можливості такого детектора. Крім переваг у завадостійкості та оперативності він може використовуватись у цифрових ФАПЧ, у модуляторах та демодуляторах кутової модуляції, для сертифікації фазових детекторів та для інших потреб метрології. Заявлена корисна модель - завадостійкий цифровий фазовий детектор - належить до фазових вимірювачів і може використовуватись у когерентних системах, системах синхронізації ліній зв'язку та у метрології. Відомий цифровий фазовий детектор (Альошин Г.В., Урвачєв В.И. Цифровий фазовий детектор. А.С. СРСР № 464858, Бюл. № 11 від 25.03.75 р.) компенсує дію низькочастотних завад та дрейф нуля у підсилювачах, які погано згладжуються та впливають на результат вимірювань фази сигналу. Недоліком цифрового фазового детектора є те, що він працює лише в обмеженому діапазоні різниць фаз, або в нециклічному режимі. Як найближчий аналог вибрано відомий цифровий фазовий детектор (Альошин Г.В., Бойко Д.О., Приходько С.І. Завадостійкий цифровий фазовий детектор. - Патент на корисну модель № 68130, бюл. № 5 від 12.03.2012), який розширює діапазон вимірюваних затримок фази сигналу. Недоліками найближчого аналога цифрового фазового вимірювача є необхідність врахування при обчислюванні вимірюваної фази сигналу внесеної затримки з боку схеми затримки, ненадійність роботи комутатора при негативному імпульсі з формувача сигнальних імпульсів та недоліки використання схем затримки. Задачею створення запропонованого завадостійкого цифрового фазового детектора є усунення затримки фази, впливаючої на точність обчислень, спрощення апаратури та підвищення надійності її роботи. В основу корисної моделі, завадостійкого цифрового фазового вимірювача, поставлена задача такого удосконалення відомого цифрового фазового детектора, при якому є можливість усунення використання схеми затримки з її недоліками, заміни блокінг-генератора тригером та підвищення надійності спрацювання комутатора за рахунок використання селекції позитивних імпульсів з формувача сигнальних імпульсів. Поставлена задача вирішується тим, що завадостійкий цифровий фазовий детектор, що містить послідовно включені генератор рахункових імпульсів, першу схему "І", електронний комутатор, дільник надвоє частоти рахункових імпульсів, лічильник, формувач сигнальних імпульсів, послідовно з'єднаний з діодом, схемою затримки, другою схемою "І" та з першим тригером, вихід формувача опорних імпульсів через перший тригер з'єднаний зі входом першої схеми "І" і послідовно з'єднаний з блокінг-генератором, третьою схемою "І", другим тригером і другою схемою "І", вихід формувача сигнальних імпульсів підключений до управляючого входу комутатора, а вихід діода підключений до третьої схеми "І", причому, вихід першого тригера підключений до лічильника для виводу результату та для його обнуління, додатково містить другий діод, підключений від виходу формувача сигнальних імпульсів до входу комутатора, замість блокінг-генератора підключений третій тригер входом до виходу формувача опорних імпульсів і виходом - до входу третьої схеми "І", усувається схема затримки таким чином, щоб був з'єднаний вихід першого діода зі входом другої схеми "І", для обнуління лічильника та тригерів використовується імпульс з виходу другої схеми "І". На фіг. 1 представлені елементи завадостійкого цифрового фазового детектора: 1) генератор рахункових імпульсів, 2) формувач сигнальних імпульсів, 3) перша схема "І", 4) формувач опорних імпульсів, 5) електронний комутатор, 6) дільник частоти надвоє, 7) лічильник, 8) третій тригер, 9) третя схема "І", 10) другий тригер, 11) друга схема "І", 12) перший тригер, 13) перший діод, 14) другий діод. На фіг. 2 - часова діаграма роботи завадостійкого цифрового фазового детектора. Принцип дії завадостійкого цифрового фазового детектора у наступному. На фіг. 2а зображена послідовність імпульсів на виході формувача опорних імпульсів. На фіг. 2б зображений сигнал на вході формувача сигнальних імпульсів з негативною на даний момент часу завадою. Очевидно, що вузькосмугова (корельована) в даний момент негативна завада як би зміщує сигнал униз, так що точки перетину осі зміщуються з моменту 1 до моменту 2. Це призводить до похибки у часі t та у фазі - t . Звичайними засобами точно компенсувати заваду неможливо. Тому пропонується використати незмінність у часі точки 3 при будь-якому впливі корельованої завади. Її можна розрахувати методом "виделки", тобто відмітивши точки 2 1 UA 79773 U 5 10 15 20 25 30 35 40 45 50 55 та 4 поділеною частотою. Знаючи точку 3, можна визначити точку 1, якщо з інтервалу з 0 по 3 відняти інтервал від 1 по 3, який відповідає значенню 2 . Точка 1 відповідає сигнальному імпульсу на виході формувача сигнальних імпульсів, тобто моменту закінчення виміру, якщо б не було завади. Початок координат відповідає опорному імпульсу. На виході формувача сигнальних імпульсів 2 є позитивні та негативні імпульси. Алгоритм дії завадостійкого цифрового фазового детектора наступний. Імпульс формувача опорних імпульсів 4 перекидає перший тригер 12, який відкриває першу схему "І" 3 для проходження рахункових імпульсів з генератора 1 через комутатор 5 на лічильник 7 в обхід дільника частоти надвоє 6 до тих пір, поки не з'явиться перший позитивний сигнальний імпульс з формувача сигнальних імпульсів 2. Заодно з відкриттям першої схеми "І" імпульс формувача опорних імпульсів 4 перекидає тригер 8 та відкриває третю схему "І". Якщо першим у часі після опорного імпульсу (у момент 2 фіг. 2б) буде позитивний імпульс сигналу з формувача сигнальних імпульсів 2, то він надходить на комутатор 5, який переключає вихід через дільник частоти надвоє 6 на лічильник 7 (фіг. 2в), та до третьої схеми "І" для перекидання другого тригера 10, який відкриває другу схему "І" для наступного негативного імпульсу із формувача сигнальних імпульсів 2. У момент 4 (фіг. 2б) формувачем сигнальних імпульсів 2 формується негативний імпульс для закриття через перший діод 13, першу схему "І" 11 і перший тригер 12 рахунку рахункових імпульсів. Оскільки частота рахунку імпульсів удвічі менша, у лічильнику 7 накопичувалось число імпульсів відповідне інтервалу від 0 до 3 (фіг. 2б). Якщо з числа, відповідного інтервалу від 0 по 3 відняти 2 , то у лічильнику залишиться число імпульсів відповідне інтервалу від 0 по моменту 1 (фіг. 2в). Тобто, якби не було будь-яких завад. Якщо першим у часі після опорного імпульсу буде негативний імпульс з формувача сигнальних імпульсів 2, то схема спрацьовує таким чином. Наприклад опорний імпульс буде у момент 3 (фіг. 2б). Негативний імпульс від формувача сигнальних імпульсів 2 не відкриває третю схему "І" 9, тобто не перекидає другий тригер 10, який держить закритою другу схему "І" 11. Тому негативний імпульс через діод 13 не проходить до першого тригера 12 та не закриває рахування рахункових імпульсів першою схемою "І" 3. Рахування лічильником 7 продовжується у такому ж алгоритмі, поки не прийде спочатку позитивний, а потім другий негативний імпульс - сигнальний імпульс (фіг. 2г). Тобто, у будь-якому разі тільки спочатку попередній позитивний імпульс та наступний негативний імпульс з формувача сигнальних імпульсів 2 дозволяють вимірювання. Ефективність запропонованого цифрового фазового детектора у наступному: 1) усунення схеми затримки дозволяє точніше обчислювати фазу сигналу, спрощує та здешевлює апаратуру, 2) для чіткої роботи детектора блокінг-генератор замінено на тригер, який держить дозвіл на відкриття схеми третьої "І" до самого приходу позитивного імпульсу формувача сигнальних імпульсів 2, 3) щоб не було непотрібних запусків комутатора від негативних імпульсів з формувача сигнальних імпульсів 2, додається діод 14 з прямим пропусканням для позитивного імпульсу. ФОРМУЛА КОРИСНОЇ МОДЕЛІ Завадостійкий цифровий фазовий детектор, що містить послідовно включені генератор рахункових імпульсів, першу схему "І", електронний комутатор, дільник надвоє частоти рахункових імпульсів, лічильник, формувач сигнальних імпульсів, послідовно з'єднаний з діодом, схемою затримки, другою схемою "І" та з першим тригером, вихід формувача опорних імпульсів через перший тригер, з'єднаний зі входом першої схеми "І" і послідовно з'єднаний з блокінг-генератором, третьою схемою "І", другим тригером і другою схемою "І", вихід формувача сигнальних імпульсів підключений до управляючого входу комутатора, а вихід діода підключений до третьої схеми "І", причому вихід першого тригера підключений до лічильника для виводу результату та для його обнуління, який відрізняється тим, що для усунення затримки фази, впливаючої на точність обчислень, спрощення аппаратури та підвищення надійності її роботи, він додатково вміщує другий діод, підключений від виходу формувача сигнальних імпульсів до входу комутатора, замість блокінг-генератора підключений третій тригер входом до виходу формувача опорних імпульсів і виходом - до входу третьої схеми "I", усувається схема затримки таким чином, щоб був з'єднаний вихід першого діода зі входом другої схеми "І", для обнуління лічильника та тригерів використовується імпульс з виходу другої схеми "І". 2 UA 79773 U Комп’ютерна верстка Л. Литвиненко Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 3

ДивитисяДодаткова інформація

Назва патенту англійськоюNoise-proof digital phase detector

Автори англійськоюAlioshyn Hennadii Vasyliovych, Prykhodko Serhii Ivanovych, Indyk Serhii Volodymyrovych

Назва патенту російськоюПомехоустойчивый цифровой фазовый детектор

Автори російськоюАлешин Геннадий Васильевич, Приходько Сергей Иванович, Индик Сергей Владимирович

МПК / Мітки

Мітки: завадостійкий, детектор, фазовий, цифровий

Код посилання

<a href="https://ua.patents.su/5-79773-zavadostijjkijj-cifrovijj-fazovijj-detektor.html" target="_blank" rel="follow" title="База патентів України">Завадостійкий цифровий фазовий детектор</a>

Попередній патент: Спосіб закріплення тензодатчика усередині сталебетонного елемента

Наступний патент: Спосіб діагностики патології нирок

Випадковий патент: Лічильник електроенергії