Пристрій для перетворення адреси

Номер патенту: 82301

Опубліковано: 25.07.2013

Автори: Козелкова Катерина Сергіївна, Гавриленко Валерій Володимирович, Одноралов Ігор Васильович, Шульга Олександр Васильович

Формула / Реферат

Пристрій для перетворення адреси, що містить тригери, суматор, адресний вхід та адресний вихід, який відрізняється тим, що до складу пристрою додатково введено дешифратор, шифратор, елементи "ТА", при цьому адресний вхід пристрою з'єднано із входом суматора, вихід якого з'єднано з входом дешифратора, виходи якого з'єднано з відповідними входами шифратора, вихід якого є адресним виходом пристрою, вихід і-того тригера з'єднано з першим входом і-того елемента "ТА", перший вхід та вихід якого з'єднано відповідно з і-тим входом дешифратора та і-тим входом суматора.

Текст

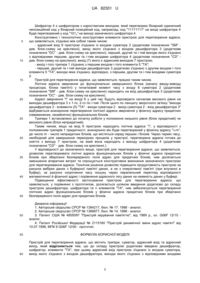

Реферат: Пристрій для перетворення адреси містить тригери, суматор, адресний вхід та адресний вихід, причому до складу пристрою додатково введено дешифратор, шифратор, елементи "ТА", при цьому адресний вхід пристрою з'єднано із входом суматора, вихід якого з'єднано з входом дешифратора, виходи якого з'єднано з відповідними входами шифратора, вихід якого є адресним виходом пристрою, вихід і-того тригера з'єднано з першим входом і-того елемента "ТА", перший вхід та вихід якого з'єднано відповідно з і-тим входом дешифратора та і-тим входом суматора. UA 82301 U (12) UA 82301 U UA 82301 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до галузі автоматики та обчислювальної техніки, зокрема до приладів та пристроїв обчислювальної техніки, а саме до пристроїв для перетворення адреси, та може бути застосована для перетворювання логічної адреси звернення у фізичну адресу у резервованих електронно-обчислювальних машинах. Відомий пристрій для адресації блоків пам'яті, що містить групу перемикачів, першу та другу групу елементів "ТА", групу регістрів, групу схем порівняння, лічильник, регістр зсуву та групу елементів "АБО" [1]. Недоліками відомого аналога є складність його конструктивного виконання та великі апаратні витрати на здійснення операцій. Відомий пристрій для адресації блоків пам'яті, що містить групу перемикачів, регістр адреси, дешифратор адреси, групу елементів "АБО" та дві групи елементів комунікації, що утворюють трикутну матрицю [2]. Недоліком відомого технічного рішення є складність його конструктивного виконання та великі апаратні витрати на здійснення операцій. Відомий пристрій для адресації пам'яті, що містить групу перемикачів, групу елементів порівняння, групу суматорів, при цьому входи групи елементів порівняння приєднано до виходів пристрою для підключення до виходів вибірки блоків пам'яті [3]. Недоліками відомого пристрою для адресації пам'яті є великі апаратні витрати, пов'язані з нераціональним використанням суматорів, які здійснюють складання з числа непридатних блоків (у тій чи іншій формі) з потрібною адресою, а, по суті, є лише ланцюгом передачі адреси, що змінюється з довжиною ланцюга адреси. Відомий пристрій керування пам'яттю, що містить блок центрального управления, шинний формувач, блок сполучення з оперативною пам'яттю, блок керування адресами даних, що містить регістр адреса, два дешифратора, накопичувач математичних адрес, накопичувач фізичних адрес, блок запису та два блоки керування [4]. До недоліків відомого пристрою належить те, що він має слабку гнучкість керування адресним простором. Найбільш близьким технічним рішенням, як за суттю, так і за задачею, яке вибрано за найближчий аналог (прототип), є пристрій для перетворення адреси, що містить тригери, суматор, адресний вхід та адресний вихід [5]. До недоліків відомого пристрою для перетворення адреси належить те, що не забезпечується якість передача адреси, а конструктивне виконання не забезпечує гнучкість керування адресним простором. В основу корисної моделі поставлено задачу шляхом введення до складу пристрою для перетворення адреси додаткових елементів - дешифратора, шифратора та елементів "ТА", забезпечити підвищення ефективності роботи пристрою та, при цьому, підвищення якості передачі адреси. Суть корисної моделі у пристрої для перетворення адреси, що містить тригери, суматор, адресний вхід та адресний вихід, полягає у тому, що до складу пристрою додатково введено дешифратор, шифратор, елементи "ТА", при цьому адресний вхід пристрою з'єднано із входом суматора, вихід якого з'єднано з входом дешифратора, виходи якого з'єднано з відповідними входами шифратора, вихід якого є адресним виходом пристрою, вихід і-того тригера з'єднано з першим входом і-того елемента "ТА", перший вхід та вихід якого з'єднано відповідно з і-тим входом дешифратора та і-тим входом суматора. Рішення поставленої задачі дійсно можливе тому, що до складу пристрою для перетворення адреси додатково введено дешифратор, шифратор та n елементів "ТА". Позитивним ефектом при цьому є те, що нова конструкція пристрою дозволяє істотно скоротити обсяг обладнання, оскільки у пристрої, що заявляється, передача адреси відбувається не по довгому ланцюгу суматорів, як у відомих аналогів, а на єдиному суматорі відбувається його перетворення шляхом складання його з числом непридатних блоків. Таким чином пристрій для перетворення адреси, що заявляється, відповідає критерію корисної моделі "новизна". Суть корисної моделі пояснюється за допомогою креслення, де показано функціональну схему пристрою для перетворення адреси, що заявляється. Пристрій для перетворення адреси, що заявляється, містить (як варіант конструктивного виконання - див. блок-схему на кресленні) тригери 1, суматор 2, дешифратор 3, шифратор 4, елементи (5) "ТА", адресний вхід 6 та адресний вихід 7 пристрою. Дешифратор 3 є дешифратором з наростаючим виходом, який перетворює бінарний позиційний код у бінарний одиничний непозиційний код, наприклад, код "101 2" на вході дешифратора 3 буде перетворений у код "11111" на виході зазначеного дешифратора 3. 1 UA 82301 U 5 10 15 20 25 30 35 40 45 Шифратор 4 є шифратором з наростаючим виходом, який перетворює бінарний одиничний непозиційний код у бінарний позиційний код, наприклад, код "11111111" на вході шифратора 4 буде перетворений у код "1012" на виході зазначеного шифратора 4. Конструктивно і технологічно конструктивні елементи пристрою для перетворення адреси, що заявляється, з'єднано між собою таким чином: - адресний вхід 6 пристрою з'єднано із входом суматора 2 (додаткове позначення "SM" див. блок-схему на кресленні), вихід якого з'єднано з входом дешифратора 3 (додаткове позначення "DC" - див. блок-схему на кресленні), перший, другий та і-тий виходи якого з'єднано з відповідними першим, другим та і-тим входами шифратора 4 (додаткове позначення "CD" див. блок-схему на кресленні), вихід (7) якого є адресним виходом 7 пристрою; - вихід і-того тригера 1 з'єднано з першим входом і-того елемента 5 "ТА"; - перший, другий та і-тий виходи дешифратора 3 додатково з'єднано з другим входом і-того елемента 5 "ТА", виходи яких з'єднано, відповідно, з першим, другим та і-тим входами суматора 2. Пристрій для перетворення адреси, що заявляється, працює таким чином. Логічна адреса звернення до функціонально завершеного блока (каналу вводу-виводу процесора, блока пам'яті) у початковий момент часу з входу 6 суматора 2 (додаткове позначення "SM" - див. блок-схему на кресленні) надходить на вхід дешифратора 3 (додаткове позначення "DC" - див. блок-схему на кресленні). Адресі звернення "i" на вході 6 у цей час будуть відповідати сигналам високого рівня на виходах дешифратора 3 з 1-го, 2-го по і-тий. Після цього по ланцюгу зворотного зв'язку "виходи дешифратора 3 - елементи (5) "ТА" - входи суматора 2 - вихід суматора 2 - вхід дешифратора 3" відбувається асинхронне перетворення логічної адреси звернення у фізичну адресу придатних (невимкнених, незайнятих) функціональних блоків. Тригери 1 встановлено до початку роботи у положення низького рівня (блок придатний) чи високого рівня (блок непридатний). Таким чином, якщо на вхід 6 пристрою надходить логічна адреса "i", у відповідності з положенням тригерів 1 придатності, асинхронно він буде перетворений у фізичну адресу "i+m", де число m - число непридатних блоків, що містяться серед перших і блоків. Через термін часу, необхідний для завершення перехідних процесів у пристрої, перетворена адреса готова до зняття з виходу 7 пристрою, на який вона надходить з виходу шифратора 4 (додаткове позначення "CD" - див. блок-схему на кресленні.). У відповідності до зазначеного вище, пристрій для перетворення адреси, що заявляється, дозволяє перетворювати логічні адреси функціональних блоків у фізичні адреси придатних блоків при зберіганні безперервного поля адрес для придатних блоків, чим досягається зменшення апаратних витрат та спрощується конструктивне виконання зазначеного пристрою для перетворювання адреси. Технічне рішення дозволяє підвищити продуктивність пристрою за рахунок вибірки даних з буферної пам'яті даних, а не з оперативної пам'яті (при влученні в буфер), за рахунок скорочення часу пошуку через паралельний перегляд відповідності математичної й фізичної адрес і порівняння адресного тегу даних на наявність даних у буфері. Підвищення ефективності застосування пристрою для перетворення адреси, що заявляється, у порівнянні з прототипом, досягається шляхом введення додатково до складу пристрою дешифратора, шифратора та n елементів "ТА", чим забезпечується перетворення логічних адрес функціональних блоків у фізичні адреси придатних блоків при зберіганні безперервного поля адрес для придатних блоків. 50 Джерела інформації: 1. Авторське свідоцтво СРСР № 1394217, бюл. № 17, 1988 - аналог, 2. Авторське свідоцтво СРСР № 1388877, бюл. № 14, 1988 - аналог. 3. Патент США № 4805097 "Пристрій керування пам'яттю", від 1989 р., кл. G06F 12/10 аналог. 4. Патент Російської Федерації № 2115160 "Пристрій динамічної зміни адрес пам'яті" від 10.07.1998, МПК 6 G06F 12/00 - прототип. 55 ФОРМУЛА КОРИСНОЇ МОДЕЛІ 60 Пристрій для перетворення адреси, що містить тригери, суматор, адресний вхід та адресний вихід, який відрізняється тим, що до складу пристрою додатково введено дешифратор, шифратор, елементи "ТА", при цьому адресний вхід пристрою з'єднано із входом суматора, вихід якого з'єднано з входом дешифратора, виходи якого з'єднано з відповідними входами 2 UA 82301 U шифратора, вихід якого є адресним виходом пристрою, вихід і-того тригера з'єднано з першим входом і-того елемента "ТА", перший вхід та вихід якого з'єднано відповідно з і-тим входом дешифратора та і-тим входом суматора. Комп’ютерна верстка М. Мацело Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 3

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for address resolution

Автори англійськоюOdnoralov Ihor Vasyliovych, Kozelkova Kateryna Serhiivna, Havrylenko Valerii Volodymyrovych, Shulha Oleksandr Vasyliovych

Назва патенту російськоюУстройство для преобразования адреса

Автори російськоюОдноралов Игорь Васильевич, Козелкова Екатерина Сергеевна, Гавриленко Валерий Владимирович, Шульга Александр Васильевич

МПК / Мітки

МПК: G06F 12/00

Мітки: адреси, пристрій, перетворення

Код посилання

<a href="https://ua.patents.su/5-82301-pristrijj-dlya-peretvorennya-adresi.html" target="_blank" rel="follow" title="База патентів України">Пристрій для перетворення адреси</a>

Попередній патент: Пристрій для контролю бінарного коду на парність

Наступний патент: Сигнатурний аналізатор

Випадковий патент: Ендопротез п'ясно-фалангового суглобу